# People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

**University M'Hamed BOUGARA – Boumerdes**

# Institute of Electrical and Electronic Engineering Department of Power and Control

Final Year Project Report Presented in Partial Fulfilment of the Requirements for the Degree of

# MASTER

In Electrical and Electronic Engineering Option: Power Engineering

Title:

**FPGA based control of single phase SVC**

Presented by:

- KAMEL Tayeb Djamel Eddine

- BOUDJOURAF Walid

Supervisors:

Dr. KHELDOUN Aissa Dr. METIDJI Brahim

Registration Number:...../2016

# **Dedication**

I would like to dedicate my work to all those who helped me to succeed in my studies specially my parents, my sisters, my grandmother, my family, my friends, my teachers and all who love me and care about me, without forgetting all dears who left this life.

KAMEL Tayeb Djamel Eddine

I dedicate this modest work to:

My Mother and Father.

My brothers.

All my family.

All my dear friends and university mates.

All department's teachers, students and administrative staff and

Whoever helped to achieve this work.

**BOUJOURAF** Walid

# Acknowledgement

We would like to express our deepest appreciation to all those who provided us the possibility to complete this project. A special gratitude we give to our final year project supervisors, Mr. KHELDOUN Aissa & Mr METIDJI Brahim, whose contribution in stimulating suggestions and encouragement, helped us to coordinate our project especially in implementation.

Furthermore we would also like to acknowledge with much appreciation the crucial role of the staff of our institute laboratory responsible, who gave the permission to use all required equipment and the necessary materials to complete the task.

# Abstract

Power quality is one of the most important indicator in electrical engineering. Variations in the impedance should be noticed for any external disturbance or change in the parameters of the electrical systems. These variation affect the reactive power hence the power factor. The use of capacitors and inductors is the classical method to compensate the reactive power but still slow to operate and decreases the power quality.

Flexible AC transmission systems (FACTS) are compensators that uses a control unit and power electronic switches to vary the impedance of the systems. The idea of this work is to change the switching and the control method of the static VAr compensator (SVC).

Classical SVCs are based on thyristors for switching and using a simple control unit. Our method is to change the control unit by using an FPGA and a bidirectional switch to enhance the power quality and increase the speed of switching.

# Contents

| Dedication1                                                          |  |  |  |  |  |  |

|----------------------------------------------------------------------|--|--|--|--|--|--|

| Acknowledgement                                                      |  |  |  |  |  |  |

| Abstract                                                             |  |  |  |  |  |  |

| Contents                                                             |  |  |  |  |  |  |

| List of tables                                                       |  |  |  |  |  |  |

| List of figures                                                      |  |  |  |  |  |  |

| General introduction                                                 |  |  |  |  |  |  |

| Chapter I                                                            |  |  |  |  |  |  |

| 1 .Compensation concepts                                             |  |  |  |  |  |  |

| 1.1 Series compensation                                              |  |  |  |  |  |  |

| 1.1.1 Advantages of Series Compensation                              |  |  |  |  |  |  |

| 1.1.2 Disadvantages of series compensation                           |  |  |  |  |  |  |

| 1.2 Shunt compensation                                               |  |  |  |  |  |  |

| 1.3 Selection of Shunt or series compensation                        |  |  |  |  |  |  |

| 1.4 Conventional compensation                                        |  |  |  |  |  |  |

| 1.4.1   Synchronous generators                                       |  |  |  |  |  |  |

| 1.4.2 Regulating power transformers                                  |  |  |  |  |  |  |

| 1.4.3 Shunt capacitors                                               |  |  |  |  |  |  |

| 1.4.4 Shunt reactors                                                 |  |  |  |  |  |  |

| 1.5   Flexible AC transmission systems                               |  |  |  |  |  |  |

| 1.5.1FACTS composition & properties21                                |  |  |  |  |  |  |

| 1.5.2Types of FACTs based on controllers22                           |  |  |  |  |  |  |

| Chapter II                                                           |  |  |  |  |  |  |

| 2 . Static Var Compensator                                           |  |  |  |  |  |  |

| 2.1 Introduction                                                     |  |  |  |  |  |  |

| 2.2 SVC Thyristor controlled reactor -fixed capacitor based (TCR FC) |  |  |  |  |  |  |

| 2.3 SVC Thyristor switched capacitor (TSC)                           |  |  |  |  |  |  |

| 2  | 2.4   | SVC    | C (TCR-TSC)                                          | 27 |

|----|-------|--------|------------------------------------------------------|----|

|    | 2.5   | SVC    | C IGBT based                                         | 28 |

|    | 2.5.  | .1     | Circuit development:                                 | 29 |

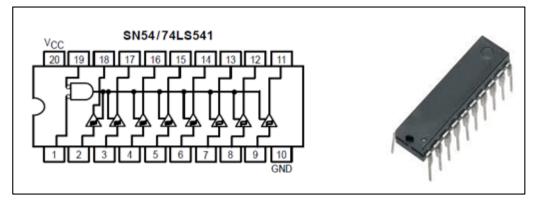

|    | 2.5.  | .2     | Voltage buffer                                       | 29 |

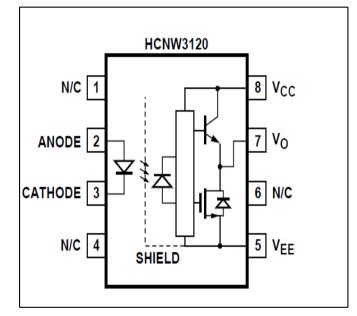

|    | 2.5.  | .3     | Optical isolation                                    | 30 |

|    | 2.5.  | .4     | MOSFET and IGBT technology                           | 30 |

|    | 2.5.  | .5     | Opt driver                                           | 31 |

|    | 2.5.  | .6     | Compensation using bidirectional switch (AC chopper) | 33 |

| Ch | apter | III    |                                                      | 36 |

| 3  | .FP   | GA ir  | nplementation                                        | 36 |

|    | 3.1   | FPC    | 3A                                                   | 37 |

|    | 3.2   | FPC    | SA cyclone V DE0 Nano soc board                      | 37 |

|    | 3.3   | Proj   | ect implementation on DE0 board                      | 38 |

|    | 3.3.  | .1     | ADC LTC 2308                                         | 39 |

|    | 3.3.  | .2     | Pulse Width Modulation signal                        | 41 |

|    | 3.3.  | .3     | Finite state machine FSM                             | 42 |

|    | 3.4   | DE     | ) implementation                                     | 44 |

|    | 3.5   | Disc   | cussion                                              | 47 |

| Ch | apter | IV:    |                                                      | 48 |

| 4  | .Sin  | nulati | on and implementation                                | 48 |

| 2  | 4.1   | Sim    | ulation                                              | 49 |

|    | 4.1.  | .1     | Simulation outputs                                   | 51 |

| 2  | 4.2   | Sim    | ulation results and Discussion                       | 53 |

| ۷  | 4.3   | Imp    | lementation                                          | 54 |

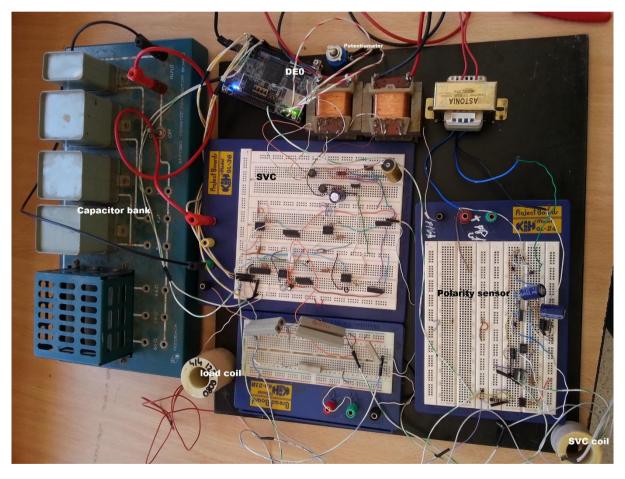

|    | 4.3.  | .1     | Component                                            | 54 |

|    | 4.3.  | .2     | Current sensor equipment                             | 58 |

| 2  | 1.4   | Circ   | cuit interconnection                                 | 59 |

|    | 4.4.  | .1     | AC chopper                                           | 59 |

|    | 4.4.  | .2     | Polarity current sensor                              | 60 |

| 4.4.3        | Implementation results  | 60 |

|--------------|-------------------------|----|

| 4.5 Imp      | plementation Discussion | 66 |

| General Conc | lusion                  | 67 |

| References   |                         | 68 |

# List of tables

Table 1: switching states for inductive to capacitive compensation positive and negative current ..... 34 Table 2: : switching states for inductive to capacitive compensation positive and negative current ... 34

# List of figures

| Figure 1-1: Type of compensation methods                                            | 14 |

|-------------------------------------------------------------------------------------|----|

| Figure 1-2: Simplified model of a power transmission system.                        | 15 |

| Figure 1-3: Power versus                                                            | 16 |

| Figure 1-4: Series compensated transmission line and phasor diagram                 | 16 |

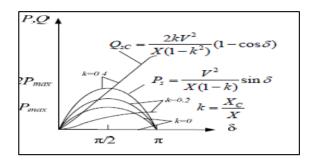

| Figure 1-5: Power angle curve.                                                      | 17 |

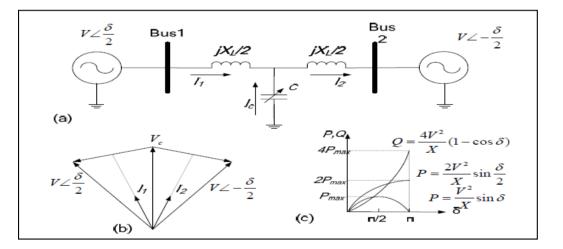

| Figure 1-6: Voltage magnitudes of the two buses and power angle curve               | 19 |

| Figure 1-7: SMSC steady state model                                                 | 22 |

| Figure 1-8: SVC steady state model                                                  | 23 |

| Figure 1-9: STATCOM steady state model                                              | 24 |

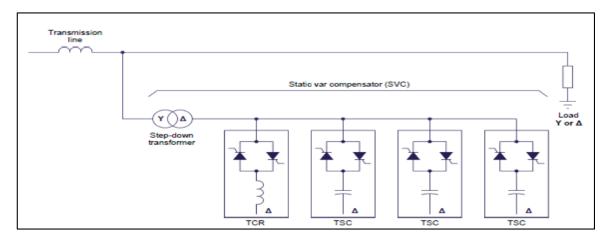

| Figure 2-1: Simplified single wire circuit diagram of an SVC of the TCR-FC type [3] | 26 |

| Figure 2-2: Bidirectional thyristor SVC                                             | 27 |

| Figure 2-3: Simplified single wire circuit diagram of an SVC of the TCR-TSC [3].    | 27 |

| Figure 2-4: Initial design of SVC IGBT based                                        | 28 |

| Figure 2-5: Buffer circuit [5]                                                      | 29 |

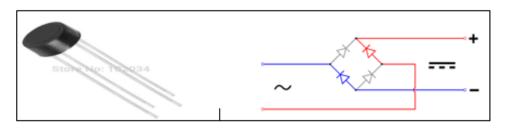

| Figure 2-6: 4N34 opt coupler                                                        | 30 |

| Figure 2-7: Cross section N-Channel MOSFET [6]                                      | 31 |

| Figure 2-8: HCPL 3120 [7]                                                           | 32 |

| Figure 2-9: Series conduction mode AC chopper [8]                                   | 33 |

| Figure 2-10: Parallel conduction mode [8]                                           | 33 |

| Figure 2-11: SVC based on FPGA control and AC chopper switching                     | 35 |

| Figure 3-1: Component of DE0 board upper side                                       | 38 |

| Figure 3-2: Implementation on FPGA                                                  | 39 |

| Figure 3-3: LTC 2308 ADC block diagram [10]                                         | 40 |

| Figure 3-4: SPI ADC configuration [10]                                              | 41 |

| Figure 3-5: PWM triangular carrier signal [10]                                      | 42 |

| Figure 3-6: FSM block diagram                                                       | 43 |

| Figure 3-7: Pins assignment                                                         | 44 |

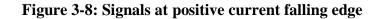

| Figure 3-8: Signals at positive current falling edge                                | 44 |

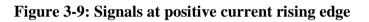

| Figure 3-9: Signals at positive current rising edge                                 | 45 |

| Figure 3-10: Signals at negative current rising edge                                | 45 |

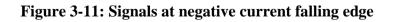

| Figure 3-11: Signals at negative current falling edge                               | 45 |

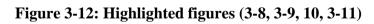

| Figure 3-12: Highlighted figures (3-8, 3-9, 10, 3-11)                               | 46 |

| Figure 4-1: Link between MATLAB & Model sim                                         | 49 |

| Figure 4-2: Setting inputs & outputs on MATLAB                                      | 50 |

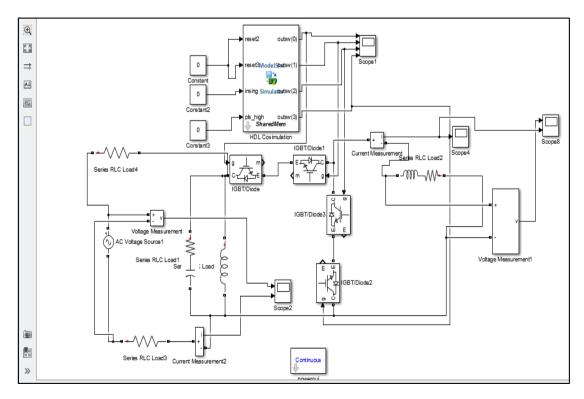

| Figure 4-3: Circuit design on MATLAB Simulink                                       | 50 |

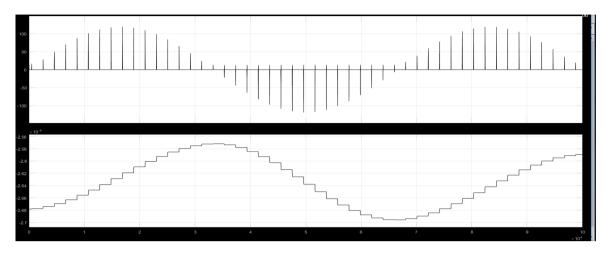

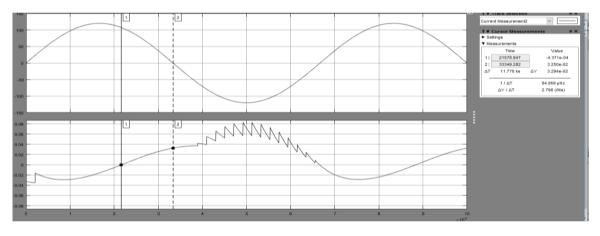

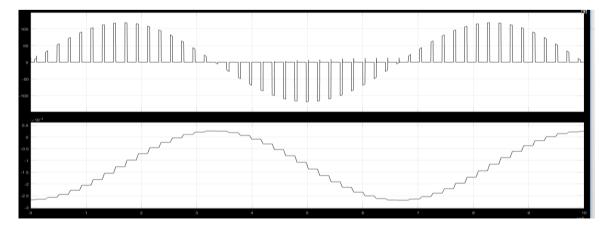

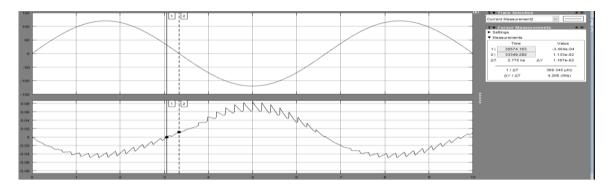

| Figure 4-4: AC chopper voltage & coil current at 0% duty cycle             |

|----------------------------------------------------------------------------|

| Figure 4-5: Voltage source and current signals at 0% duty cycle            |

| Figure 4-6: AC chopper voltage & coil current at 20% duty cycle            |

| Figure 4-7: Voltage and current signals at 20% duty cycle                  |

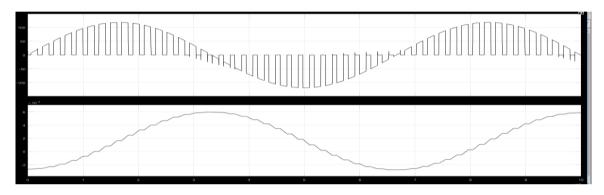

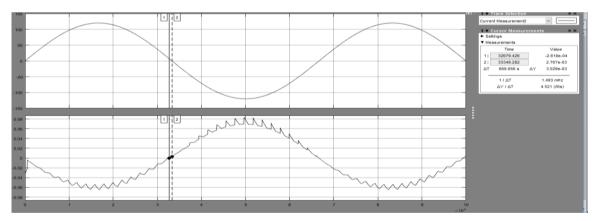

| Figure 4-8: AC chopper coil voltage & coil current outputs 50% duty cycle  |

| Figure 4-9: Voltage and current signals at 50% duty cycle                  |

| Figure 4-10: Single phase transformer                                      |

| Figure 4-11: SEP rectifier bridge                                          |

| Figure 4-12: Voltage regulator                                             |

| Figure 4-13: Buffer                                                        |

| Figure 4-14: Buffer operation mode                                         |

| Figure 4-15: Gate drive optocoupler                                        |

| Figure 4-16: Insulated gate bipolar transistor                             |

| Figure 4-17: Selection of switch                                           |

| Figure 4-18: Operation amplifier [12]                                      |

| Figure 4-19: 4n35 opt coupler [13]                                         |

| Figure 4-20: AC chopper output for 50% and 0%                              |

| Figure 4-21: Coil current and polarity sensor                              |

| Figure 4-22: The realization circuit of SVC                                |

| Figure 4-23: Coil voltage and current 100% duty cycle                      |

| Figure 4-24: The output of the coil 50 % and 100% with SVC effect          |

| Figure 4-25: Coil current and voltage                                      |

| Figure 4-26: Effect of capacitor of 2µF                                    |

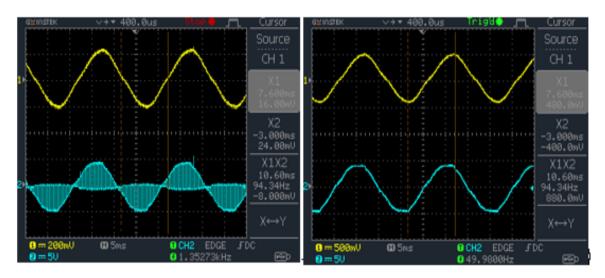

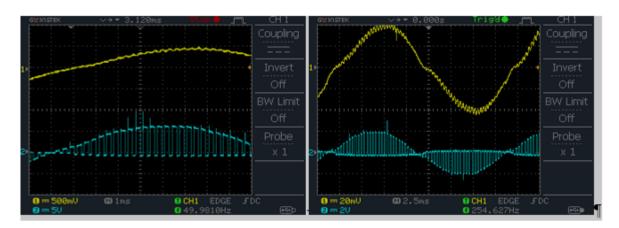

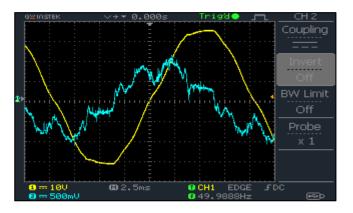

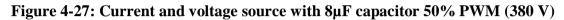

| Figure 4-27: Current and voltage source with 8µF capacitor 50% PWM (380 V) |

| Figure 4-28: The effect of 4µF cap                                         |

| Figure 4-29: 8µF cap                                                       |

# General introduction

One of the great engineering achievements of the last century has been, the evolution of large alternative current (AC) power grids, in which all the interconnected systems maintain the same precise electrical frequency. Today, the conventional electric power system is composed of three main level which are: generation, consummation, transmission and distribution.

In each electric power grid, some parameters must be maintained to insure a good service to the consumer. This parameters are frequency "50 Hz", voltage, and the sinusoidal shape of the voltage.

When the load is inductive or capacitive, it may causes a reactive power perturbation that affect the power factor and the voltage which are the major problems in network especially in distribution level. Compensation is a method to control the reactive power in the network where the voltage or the power factor is out of range.

There exists modern and classical methods to compensate the reactive power which are, reactors and bank of capacitors that represent classical methods and static advanced method as a current voltage injection or variable impendences that requires a control of switching modules.

Static var compensator is a variable impedance compensator based on control signal that Triger the switches to move from inductive state to capacitive or reverse way, thyristors power electronic devices are mostly used on switching because of their ability to resist to high current, but still have slow switch off that may cause short circuit when more than one thyristor are used and steal slow to operate.

Thinking of an idea to have more safe and fast switching is not impossible due to the existence of fast switching semiconductors such us MOSFETs. The solution proposed in the project is to keep the same principle but, change the switching and control method using FPGA as a control device and IGBTs as switches.

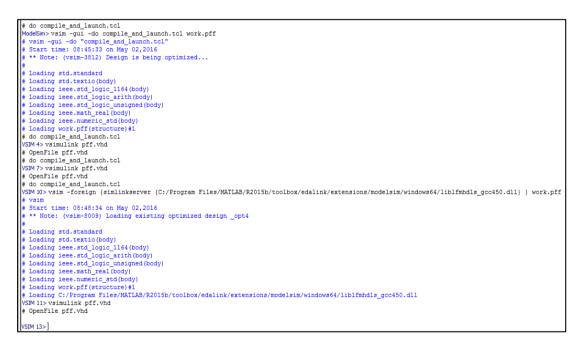

The project starts with a simulation of the SVC using MATLAB Simulink and in order to induce FPGA-real time control, modelsim must be employed together with MATLAB Simulink.

An exchange of data should be done between Matlab and model sim in such away Matlab brings FPGA block from model sim, then generates a clock that should be sent to model sim with inputs data set on Matlab. Both software should simulate the data which is called cosimulation. The idea was implemented following the simulation steps, signals are generated from DE0 board using hardware method, then buffered toward a combination of four switches called AC chopper placed between an inductor and a capacitor.

Our implementation of SVC should compensate the reactive power in the test is made from source in parallel with an inductive load. The change of current sign is important so that PWM at the input should provide a switching method arranged by the FPGA to make the absorption and injection of reactive power very fast and makes the switching more safe.

# Chapter I

# 1.Compensation concepts

During the past few years, the demand of electrical energy has highly increased. More power plants, substations, and transmission lines need to be constructed. However, the Inductive load or step up transformer that increases the voltage hence more power transfer capability especially in transmission line creates a reactive power disturbance, which results an under/over voltage disturbance.

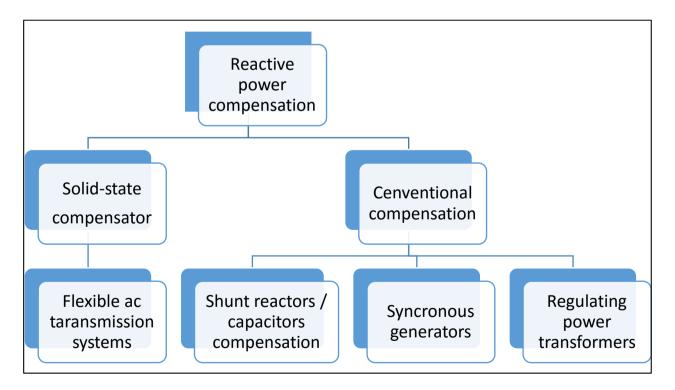

Reactive power Compensation was the solution to solve the problems of reactive power and helping generators to improve the power quality. Reactors, capacitors, and other classical method are used as first level reactive power compensation to absorb/ inject reactive power. However, long switching periods, discrete operation and harmonics injection Ferro-resonance and coast are the major problems found in classical compensation. These drawbacks have motivated the development of static compensators based on power electronics methods. Figure (1-1) shows the different compensation methods.

Static compensation still have some problems of the classical one, to minimize these drawbacks, large operational margins and redundancies are maintained to protect the system from dynamic variation and recover reactive power.

Figure 1-1: Type of compensation methods

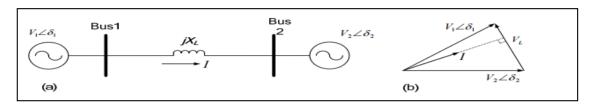

The corresponding phasor diagrams shown in figure (1-2)(b)

Figure 1-2: Simplified model of a power transmission system.

The magnitude of the current in the transmission line is given by

$$I = \frac{V_L}{X_L} = \frac{|V_1 \angle \delta_1 - V_2 \angle \delta_2|}{X_L} \tag{1}$$

Reactive components of the current flow at bus 1 are given by

$$I_{p1} = \frac{V_2 \sin \delta}{X_L} \tag{2}$$

$$I_{q1} = \frac{V_1 - V_2 \cos \delta}{X_L} \tag{3}$$

The active and reactive power at bus 1:

$$Q_{1} = V_{1} \cdot \frac{(V_{1} - V_{2} \cos \delta)}{X_{L}}$$

(4)

$$P_1 = V_1 \cdot \frac{V_2 \sin \delta}{X_L} \tag{5}$$

Similarly for the second bus we may have the same equations:

$$I_{p2} = \frac{V1 \, \sin \delta}{XL} \tag{6}$$

$$I_{q2} = \frac{V_2 - V_1 \cos \delta}{X_L} \tag{7}$$

$$Q_2 = V_2 \cdot \frac{V_2 - V_1 \cos \delta}{X_L} \tag{8}$$

$$P_2 = V_1 \cdot \frac{V_2 \sin \delta}{X_L} \tag{9}$$

These equations indicate that the active and reactive power/current flow can be regulated by controlling the voltages, phase angles and line impedance of the transmission system.

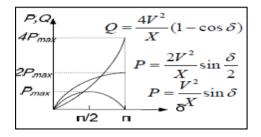

From the power angle curve shown in figure (1-3), the active power flow will reach the maximum when the phase angle  $\delta$  is 90°. In practice, a small angle is used to keep the system stable from the transient and dynamic oscillations. Two main groups in compensation are distinguished, which are series and shunt.

**Figure 1-3: Power versus**

### 1.1 Series compensation

Series capacitors are used to cancel a portion of the inductive reactance of the transmission line. This compensation, can improve the power transmission capability of the line. It has been applied to long transmission lines and other locations where the transmission distances are great and where large power transfers over long distances are required. Modern HV transmission lines are series compensated to improve power system performance.

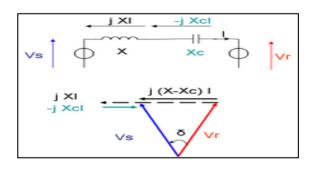

Figure 1-4: Series compensated transmission line and phasor diagram

Figure 1-5: Power angle curve.

Let the capacitance of C to be a portion of the line reactance then

$$Xc = k.X_l \tag{10}$$

$$X = X_l - Xc \tag{11}$$

$$X = (1 - k).X_l$$

(12)

The active power should be

$$P = V^2 \cdot \frac{\sin \delta}{(1-k) \cdot X_l} \tag{13}$$

And the reactive power supplied by the capacitor is

$$Q_{c} = 2. V^{2} \cdot \frac{k \cdot (1 - \cos \delta)}{(1 - k)^{2} \cdot X_{l}}$$

(14)

Under short circuit condition, the produced high voltage may damage the capacitor and so series capacitor has to be protected using a spark gap with a high speed contactor. The use of series compensation introduces few problems like: Sub-synchronous resonance, Ferroresonance and high recovery voltage.

# 1.1.1 Advantages of Series Compensation

## 1.1.1.1 Increase in transmission capacity

The power transfer capacity of a line is given by

$$P = \frac{E.V}{X} \sin \delta \tag{15}$$

#### .Compensation concepts

To see the difference between the compensated and uncompensated we have to calculate the ratio:

$$P_1 = \frac{E.V}{X_L} \sin \delta \tag{16}$$

$$P_2 = \frac{E.V}{(X_L - X_C)} \sin \delta \tag{17}$$

$$\frac{P_2}{P_1} = \frac{X_L}{(X_L - X_C)} = \frac{1}{(1 - X_C / X_L)} = \frac{1}{1 - K}$$

(18)

The economic degree of compensation K lies in the range of 0.4-0.7

# 1.1.2 Disadvantages of series compensation

- 1. Increase in fault current.

- 2. Bad operation of distance relay if the degree of compensation and location is not proper.

- 3. High recovery voltage of lines- across the circuit breaker contacts and is harmful.

4. Problems of Ferro-resonance: When an unloaded or lightly loaded transformer is energized through a series compensated line, Ferro-resonance may occur. It is produced due to resonance occurred in between the iron-created and in the reactance of the compensated line. This will cause a flow of high current.

5. Problems due to sub-synchronous resonance: The series capacitors introduces a subsynchronous frequency (proportional to the square-root of the compensation) in the system.

### 1.2 Shunt compensation

Shunt reactive compensation has been widely used in transmission system to regulate the voltage magnitude, it improves the voltage quality, and enhance the system stability. Shunt-connected reactors are used to reduce the line over-voltages by consuming the reactive power, while shunt-connected capacitors are used to maintain the voltage levels by compensating the reactive power to transmission line.

Figure (1-6 a) shows the voltage magnitudes of the two buses assumed to be equal **V**, and the phase angle between them is  $\delta$ . The transmission line is assumed lossless and represented by the reactance  $X_L$ . At the midpoint of the transmission line, a controlled shunt capacitor C connected. The voltage magnitude at the connection point is maintained constant and equal.

From the power angle curve shown in figure (1-6)(c), the transmitted power can be significantly increased, and the peak point shifts from  $\delta=90^{\circ}$  to  $\delta=180^{\circ}$ . The operation margin and the system stability are increased by the shunt compensation.

The active power at bus one & two is given by:

$$P2 = P1 = 2\frac{V^2}{XL}\sin\frac{\delta}{2}$$

(19)

The reactive power injected by the capacitor

$$Qc = 4. V^2. \frac{(1 - \cos \delta/2)}{Xl}$$

(20)

### 1.3 Selection of Shunt or series compensation

• To maintain constant load voltage, performs better the series capacitor arrangement.

• Shunt capacitive arrangement reduces the total active power loss while series capacitive one does not.

• Series capacitive arrangement reduces the total reactive power loss by far as compared to Shunt-capacitive arrangement.

• Shunt capacitive arrangement improves the system power factor by far compared to Series capacitive one.

• Load power factor remains always constant with and without any compensation.

• When a system is to be extended by the addition of a new line or when one of the existing circuits is to be adjusted for parallel operation, series compensation is preferable to achieve maximum power transfer or minimize losses.

# 1.4 Conventional compensation

Reactive power demand changes, and consequently the voltage fluctuates on the line. In order to control and correct the voltage fluctuations, there are several voltage regulating devices that are used in the power system; which are briefly described as follows:

## 1.4.1 Synchronous generators

Can be used for both generation and consumption of reactive power. When they are in overexcitation mode, they deliver reactive power to the power system; while they absorb reactive power from the grid when working in under excitation mode.

# 1.4.2 **Regulating power transformers**

It is possible to change a power transformer's voltage ratio by using tap-changer which consequently affects the voltage level. But this method is limited particularly when the transformer is connected with many lines which have different load, it can cause a violation in certain lines.

# 1.4.3 Shunt capacitors

Capacitors generate reactive power to power system to which are connected, they do increase the voltage level. Typically they are used during heavy load conditions.

# 1.4.4 Shunt reactors

There are two main applications for Shunt Reactors. First, Shunt Reactors can be used for stability reasons especially on long transmission lines (EHV and HV lines/cables); For the purpose of voltage control, they can only switched in during light loaded conditions.

# 1.5 Flexible AC transmission systems

The electricity supply industry is undergoing a profound transformation worldwide. Market forces, depleting natural resources, and an ever-increasing demand for electricity are some of the drivers responsible for such unprecedented change.

The ability of the transmission system to transmit power becomes impaired by one or more of the following steady state and dynamic limitations:

-Angular stability;

- Voltage magnitude;

- Thermal limits;

- Transient stability;

- Dynamic stability.

These limits define the maximum electrical power to be transmitted without causing damage to transmission lines and electrical equipment. In principle, limitations on power transfer can always be relieved by the addition of new transmission lines and generation facilities.

Alternatively, Flexible Alternating Current Transmission System (FACTS) controllers can enable the same objectives to be met with no major alterations to power system layout. FACTS are alternating current transmission systems incorporating power electronic-based and other static controllers to enhance controllability and increase power transfer capability.

## 1.5.1 FACTS composition & properties

The FACTS concept is based on the substantial incorporation of power electronic devices and methods into the high-voltage side of the network, to make it electronically controllable. FACTS controllers aim at increasing the control of power flows in the high-voltage side of the network during both steady state and transient conditions.

This interest has led to significant technological developments of FACTS controllers. Several kinds of FACTS controllers have been commissioned in various parts of the world.

Popular FACTs are: load tap changers, phase-angle regulators, static VAR compensators, thyristors controlled series compensators, interphase power controllers, static compensators, and unified power flow controllers.

The main objectives of FACTS controllers are the following:

- Regulation of power flows in prescribed transmission routes.

- Secure loading of transmission lines nearer to their thermal limits.

- Prevention of cascading outages by contributing to emergency control.

- Damping of oscillations that can threaten security or limit the usable line capacity.

# 1.5.2 Types of FACTs based on controllers

FACTS technology consists of number of devices. Some of the FACTS devices are:

- Static Synchronous Compensator (STATCOM).

- Static Var Compensator (SVC).

- Unified Power Flow Controller (UPFC).

- Inter-phase Power Flow Controller (IPFC).

- Static Synchronous Series Controller (SSSC).

- Thyristor Controlled Series Compensator (TCSC).

- Super Conducting Magnetic Energy Storage (SMES). [2]

# 1.5.2.1 Shunt Mechanically-Switched Capacitors (SMSC):

An SMSC typically consist of a set of capacitor banks that control the voltage magnitude at a remote bus or at the bus at which they are connected.

The capacitor banks, which are defined in terms of their nominal reactive power, are switched on one at a time when the controlled-bus voltage magnitude reaches a minimum value, and they are switched off when the voltage reaches a maximum value.

Hence, these controllers can be readily modelled in steady state as depicted in figure (1-7).

Figure 1-7: SMSC steady state model

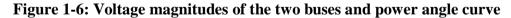

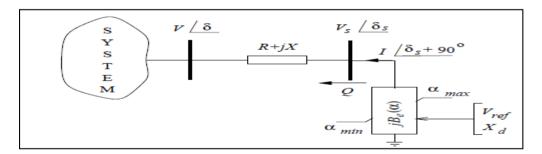

# 1.5.2.2 Static var compensator (SVC)

The model shown in figure (1-8) is model where the controller is modelled as a variable susceptance controlled by the firing angle of the thyristor-controlled reactor of the SVC. Hence, control limits in this case are directly represented in the firing angle; however, given the one-to one correspondence between this firing angle and the corresponding equivalent susceptance value, one could assume that these limits directly correspond to limits on this susceptance, as it is typically done in most power system analysis tools. [2]

$$V = V_{ref} - X_d I \tag{21}$$

$$B_e(\alpha)V_s = I \tag{22}$$

$$B_e(\alpha) = \frac{1}{\pi X_L} \left[ 2\alpha - \sin 2\alpha - \pi \left(2 - \frac{X_L}{X_c}\right) \right]$$

(23)

Where V is the voltage magnitude at the bus being controlled; Vref is the desired voltage setting; I is the capacitive current of the SVC, which becomes negative when the controller is operating in inductive mode;  $X_d$  stands for the controller droop; Be represents the equivalent susceptance of the SVC controller which is a function of the firing angle  $\alpha$ ; and  $X_c$  and  $X_L$  are the SVC's capacitor and inductor reactance. In this case, the last equation is not explicitly considered in the solution process; this equation is only used to determine the control limits.

Figure 1-8: SVC steady state model

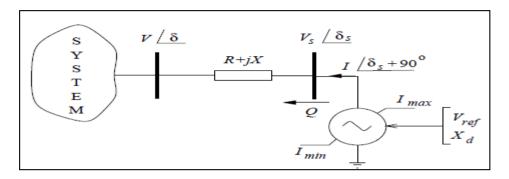

# 1.5.2.3 Static synchronous compensator (STATCOM):

The STATCOM model in figure (1-9) is a model based on an active power balance between the ac side and dc side of the Static Synchronous Compensator (STATCOM).

#### Figure 1-9: STATCOM steady state model

Voltage-sourced converter (VSC), is the main element of a STATCOM. If dc losses in the STATCOM are neglected, as these are typically not very significant, this model can be viewed as a reactive power voltage source model Thus, the STATCOM can be modelled in steady state by means of the following equations when delivering reactive power (operating in capacitive mode):

$V = Vref - X_d I \& I = Q/Vs$

$$V_s^2 G - V_s V \cdot G \cos(\delta_s - \delta) - V_s \cdot V \cdot Bsin(\delta_s - \delta) = 0$$

<sup>(24)</sup>

$$-V_s^2 B - V_s V \cdot B \cos(\delta_s - \delta) - V_s \cdot V \cdot B \sin(\delta_s - \delta) = Q$$

<sup>(25)</sup>

where  $G+jB = (R+jX)^{-1}$  represents the step-down STATCOM transformer plus ac active and reactive power losses associated with the solid-state switches operation, which can be significant in PWM control;  $V \angle \delta$  and  $V \angle \delta$  are the voltage phasors at the bus being controlled and the VSC ac bus, respectively; Vref is the desired voltage setting; I is the capacitive current of the STATCOM, which becomes negative when the controller is operating in inductive mode; and X<sub>d</sub> stands for the controller droop. Observe that this model is similar to the typical voltage source (synchronous condenser) model used to represent STATCOMs in power flow analysis, since a transformer/line model can be used to represent the R + jX impedance. [2]

# Chapter II

# 2 . Static Var Compensator

# 2.1 Introduction

SVC is an automated impedance matching device, providing fast acting reactive power on high voltage electricity transmission network, it is a part of flexible AC transmission system (FACTs), regulating the voltage, power factor and stabilizing the system.

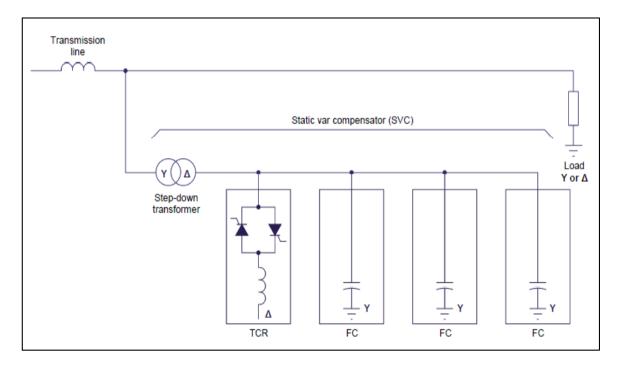

# 2.2 SVC Thyristor controlled reactor -fixed capacitor based (TCR FC)

The SVC of the TCR-FC type consist of a TCR, which absorbs reactive power from the ac power system to which the SVC is connected, and several FCs, which supply reactive power to the system of the TCR-FC type is illustrated in figure(2-1) below.

# Figure 2-1: Simplified single wire circuit diagram of an SVC of the TCR-FC type [3].

When the SVC has to supply reactive power to compensate the voltage in the ac power system (when the system absorbs reactive power), the TCR firing angle is increased so that the amount of reactive power absorbed by the TCR decreases. The lower the reactive power which the TCR absorbs, the higher the reactive power which the SVC supplies. When the TCR is set to the non-conducting state, the amount of the reactive power supplied by the SVC is maximal. The maximal amount of the reactive power which an SVC of the TCR-FC type can supply is equal to the rated reactive power.

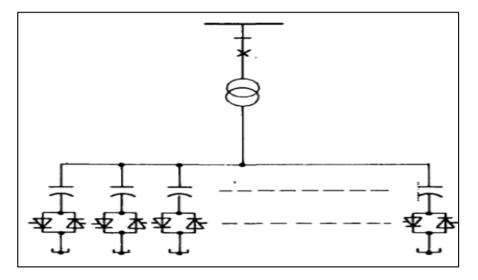

# 2.3 SVC Thyristor switched capacitor (TSC)

The shunt-capacitor bank is split up into small steps, by using bidirectional thyristor switches. It can be made switched in and out individually. Fig (2-2), shows the single-phase branch, consists of capacitor C and the thyristor switch and a minor component. The reactor L, which is used to limit the rate of rise of the current through the thyristors and also to prevent resonance with the network. The capacitor is switched out through the suppression of the gate trigger pulses of the thyristors.

Figure 2-2: Bidirectional thyristor SVC

# 2.4 SVC (TCR-TSC)

The TCR-TSC type consists of a TCR, which absorbs reactive power from the ac power system connected to the SVC, and several TSCs, which supply reactive power to the ac power system connected to the SVC.

Figure 2-3: Simplified single wire circuit diagram of an SVC of the TCR-TSC [3].

In the thyristor switched capacitor scheme the total reactive power is split into a number of parallel-capacitor banks. The reactive power from the compensator follows the load or terminal voltage variations in a step. Combined TSC and TCR type are characterized by the following properties:

- Continuous control

- Practically no transients

- Low generation of harmonics

- Low losses

- Flexibility in control and operation.

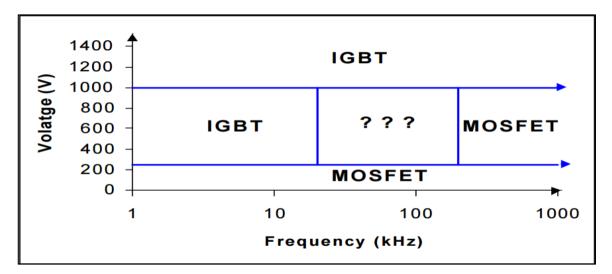

# 2.5 SVC IGBT based

The SVC treated previously based on thyristor which are hard to turn on and off without forgetting the low order harmonics injected, so we can think on faster low harmonic and more efficient switching method based on hardware design, or in other term we can switch and control in low power.

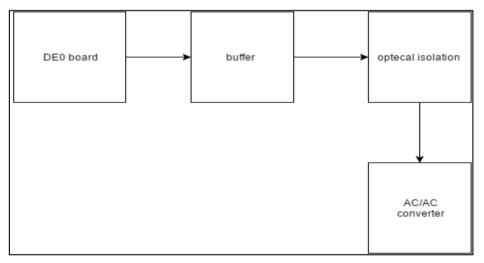

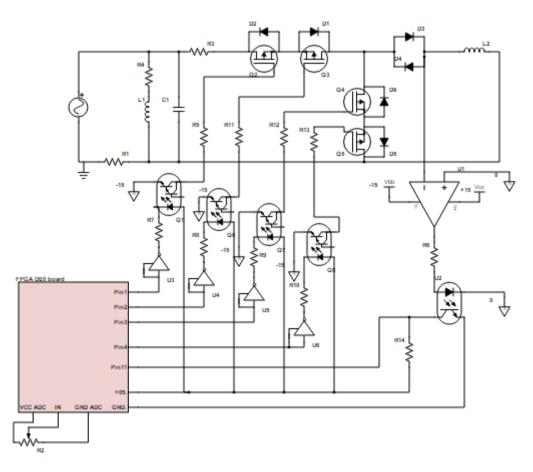

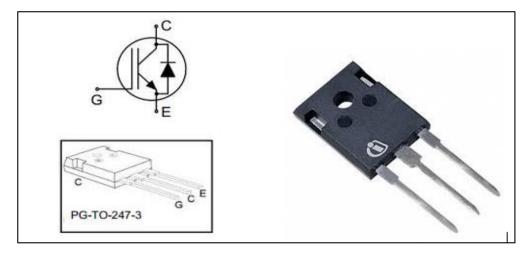

In this project IGBTs are as switch due to its fastness and resisting to a high power, the figure (2-4) shows a diagram of switching methodology which should be implemented.

# Figure 2-4: Initial design of SVC IGBT based

DE0 board being used to generate the signals which are buffered to an optical isolation which drives the IGBTs of AC /AC converter.

# 2.5.1 Circuit development:

The electronics hardware design based on FPGA board allow to control AC/AC converters by generating signals to switch on or off the IGBTs. The choice of the FPGA comes from it ability to replace the IC's and allow us to create fast low level logic devices with a high speed, Compared to other boards, the FPGAs are more precise, high speed interface. Also a hardware implementation could be done compared to "µcontroller ....." More details on this board are mentioned on the next chapter.

The signals coming from the FPGA cannot be sent directly to the IGBTs gate, therefore signal conditioning circuit must be added.

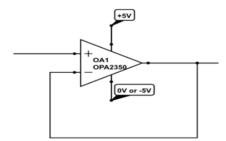

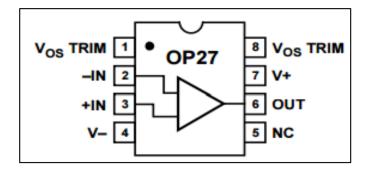

## 2.5.2 Voltage buffer

A circuit which transfers a voltage from a circuit with high output impedance to a circuit with low input impedance is called a voltage buffer.

The voltage buffer connected between these two circuits prevents the low input impedance circuit from loading the first one. Absolute linearity, high speed are the features of an ideal voltage buffer.

If the voltage is transferred from the first circuit to the second one without any change in amplitude, then such a circuit is called unity gain voltage buffer or voltage follower.

Voltage follower implemented using opamp is shown in Figure (2-5). by connecting the output pin to the inverting input pin. So the equation for gain is given in Eq (26).

$$Av = 1 + (Rf/R1)^2$$

(26)

Figure 2-5: Buffer circuit [5]

Since output and inverting input are shorted, Rf=0, and R1 is not connected to ground, it can be considered as an open circuit and so R1 = $\infty$  Therefore (Rf/R1) = (0/ $\infty$ ) = 0 and the gain is one. [4]

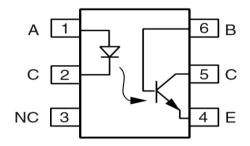

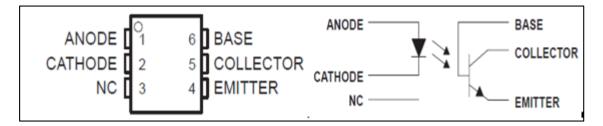

# 2.5.3 Optical isolation

It is done by isolating the primary input voltage from the secondary output voltage or the command input side from the load output side by using just light using a very common and valuable electronic component called an Opt coupler.

Opt couplers, "Opt-isolator or Photo-coupler", are an electronic components that much two separate electrical circuits by an infra-red light.

The basic design of an opt coupler consists of a LED that produces infra-red light and a photo-sensitive semiconductor device that is used to detect the emitted infra-red beam.

When a current between 6 mA and 25 mA enters the anode of the infra-red diode, the latter is activated and delivers a light beam, which turns on to the semiconductor in the other side of the opt coupler. The revers operation cannot take place.

Figure 2-6: 4N34 opt coupler

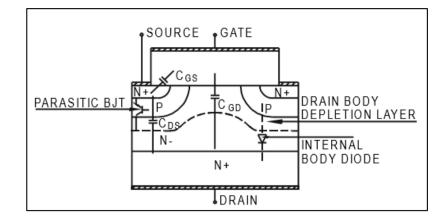

# 2.5.4 MOSFET and IGBT technology

Today's Power Electronics uses MOSFETs and IGBTs in most applications for switching, driving ..... ect. The most important advantage of MOSFETs is the high frequency switching. Its limit factors are: transit time of electrons across the drift region and the time required to charge and discharge the input Gate and 'Miller' capacitances.

The main advantage of IGBT is an injecting region on its Drain side to provide conductivity of the Drain drift region which reduces the losses, when compared to an equally rated high voltage MOSFET.

When using IGBTs or MOSFETs, driving circuit is required to control the turning-on\off. Driver circuits designed for driving MOSFET can be used to drive an IGBT.

Figure 2-7: Cross section N-Channel MOSFET [6]

The IGBT driver serves to charge the gate of the power electronic device with a sufficient power to turn it on the switch or discharge to turn it off. The power required is calculated as shown in Eq (27)

$$P_G = Q_G * F_{IN} * \Delta V_{Gate} + C_{GE} * F_{IN} * \Delta V_{Gate}^2$$

(27)

Where:  $F_{IN}$ : is the switching frequency.

$P_G$ : is the switching power.

$Q_G$ : is the Gate charge.

$\Delta V_{Gate}$ : is the swing voltage.

$C_{GE}$ : is the capacitance between gate and emitter to be charged and discharged during a cycle.

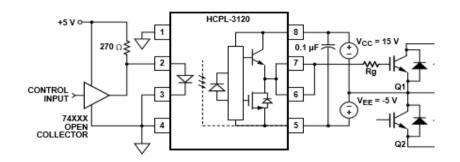

# 2.5.5 Opt driver

The opt diver is the most used because it provides an isolation between the command side and high power side which is the case in our project., it is LED diode that activate with a current in between 6mA and 25 mA at the input side, and half bridge of two p-channel transistors at the output side with common input that comes from the light receiver diode, when the input diode is on the upper transistor is on and delivers 15 V brought from source to the IGBTs gate and charge gate-emitter capacitor and the lower is off that's ON state. When the input LED is OFF, the lower transistor is activated and the upper remain off that provide a short from gate emitter terminal through the gate resistor. One can add a source of - 5 to -15 to speed up the switching OFF and keep OFF state when needed. The two transistors are never gated at the same time. Figure (2-8)

Figure 2-8: HCPL 3120 [7]

# 2.5.6 Compensation using bidirectional switch (AC chopper)

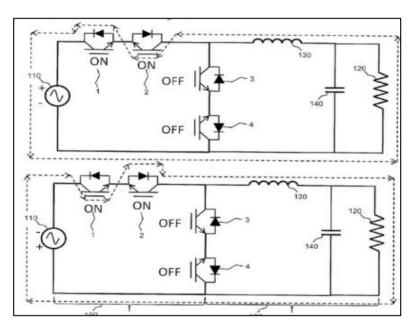

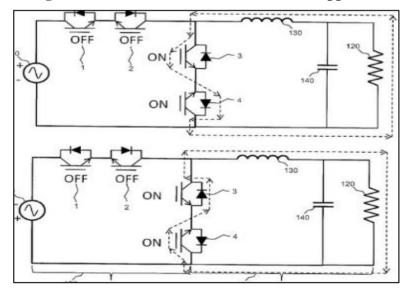

Single phase AC choppers is a power electronics converter with four switches used to control the current and voltage, in this project, it is used to control the voltage and current as switch between an inductor and capacitor to compensate the phase shift between them.

As shown figures (2-9, 2-10) it is composed of series arm and parallel one. Each arm has a two IGBTs emitter to emitter connected in away to provide bidirectional switching. IGBTs of both arms are switched on and off such that no short circuit is provided in the circuit.

Figure 2-9: Series conduction mode AC chopper [8]

Figure 2-10: Parallel conduction mode [8]

In figure (2-11) Taking an initial state and compensation is required, a switching mode through a specified states is required, otherwise a short circuit is provided. In our case we have two initial states with the direction of current must be taken into consideration. Inductive or capacitive initial states, and negative or positive current. And the time of compensation depends on the duty cycle of the generated PWM.

# Inductive to capacitive:

# Table 1: switching states for inductive to capacitive compensation positive and negativecurrent

|         | Positive current |       |       |       | Negative current |       |       |       |

|---------|------------------|-------|-------|-------|------------------|-------|-------|-------|

|         | IGBT1            | IGBT2 | IGBT3 | IGBT4 | IGBT1            | IGBT2 | IGBT3 | IGBT4 |

| State 1 | ON               | ON    | OFF   | OFF   | ON               | ON    | OFF   | OFF   |

| State 2 | ON               | OFF   | OFF   | OFF   | OFF              | ON    | OFF   | OFF   |

| State 3 | ON               | OFF   | OFF   | ON    | OFF              | ON    | ON    | OFF   |

| State 4 | OFF              | OFF   | OFF   | ON    | OFF              | OFF   | ON    | OFF   |

| State 5 | OFF              | OFF   | ON    | ON    | OFF              | OFF   | ON    | ON    |

#### **Capacitive to inductive:**

# Table 2: : switching states for inductive to capacitive compensation positive and negativecurrent

|         | Positive current |       |       |       | Negative current |       |       |       |

|---------|------------------|-------|-------|-------|------------------|-------|-------|-------|

|         | IGBT1            | IGBT2 | IGBT3 | IGBT4 | IGBT1            | IGBT2 | IGBT3 | IGBT4 |

| State 1 | 0FF              | 0FF   | ON    | ON    | 0FF              | 0FF   | ON    | ON    |

| State 2 | OFF              | OFF   | ON    | OFF   | OFF              | OFF   | OFF   | ON    |

| State 3 | OFF              | ON    | ON    | OFF   | ON               | OFF   | OFF   | ON    |

| State 4 | OFF              | ON    | OFF   | OFF   | ON               | OFF   | OFF   | OFF   |

| State 5 | ON               | ON    | OFF   | OFF   | ON               | ON    | OFF   | OFF   |

The switching states are built to avoid any short circuit. Taking into consideration the current direction on principle of switching off the IGBT which has an conductive diode in the same direction with present current for the conductive arm first, then switch on the main IGBT that has reversed diode in the other arm to insure the flow of current, after that switch OFF the other IGBT in the main arm and finally switch the last IGBTS.

#### **Operation principle**

Beginning by the analogue input that enters the FPGA board then converted to a digital data which represent the signal that must be compared with the carriers signal in the PWM code.

When the PWM signal is generated means that the desired reactive power is adjusted and here comes the AC choppers turn by switching between the inductor and the coil without forgetting the direction of current that should be return from the end of the AC chopper to the FPGA to select the state switching as seen in the tables.

The final circuit: figure (2-11)

Figure 2-11: SVC based on FPGA control and AC chopper switching

## Chapter III

# 3 .FPGA implementation

As seen in the previous chapter, the project requires PWM generation and signals and control the AC chopper switches.

The embedded systems is one of the precise and accurate method to generate our control signals using a programmable board like FPGA Altera board.

FPGA can replace the IC's and allow to create fast low level logic devices with a high speed, Compared to the other boards, FPGAs are more precise, high speed interfaces "RAM, HDMI, ADC......", Soft core can be implemented " $\mu$ controller ....." using the logic FPGA. The total control of the board means we can create & implement the process we want then send it to the desired pin on our board without any limitation compared to the  $\mu$ controller.

#### 3.1 **FPGA**

Field Programmable Gate Array are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing.

This feature distinguishes FPGAs from Application Specific Integrated Circuits (ASICs), which are custom manufactured for specific design tasks.

Although one-time programmable (OTP) FPGAs are available, the dominant types are SRAM based which can be reprogrammed as the design evolves.

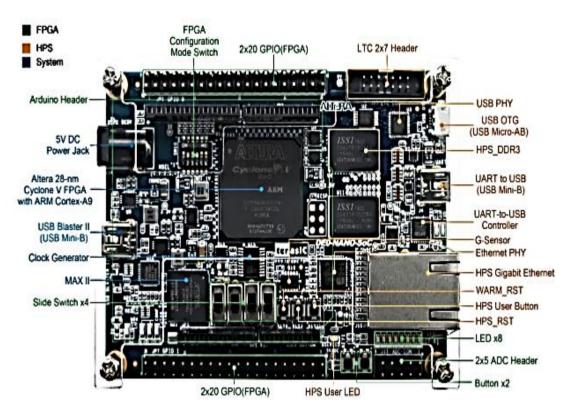

#### 3.2 FPGA cyclone V DE0 Nano soc board

The Atlas-SoC Software Development Kit presents a robust hardware design built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility. Users can now leverage the power of tremendous re-configurability paired with a highperformance, low-power processor system.

Altera's SoC integrates an ARM-based hard processor system (HPS) consisting of processor, peripherals and memory interfaces tied seamlessly with the FPGA fabric using a high-bandwidth interconnect backbone.

The Atlas-SoC development board is equipped with high-speed DDR3 memory, analogue to digital capabilities, Ethernet networking, and much more that promise many exciting applications. [9]

37

Figure 3-1: Component of DE0 board upper side 3.3 **Project implementation on DE0 board**

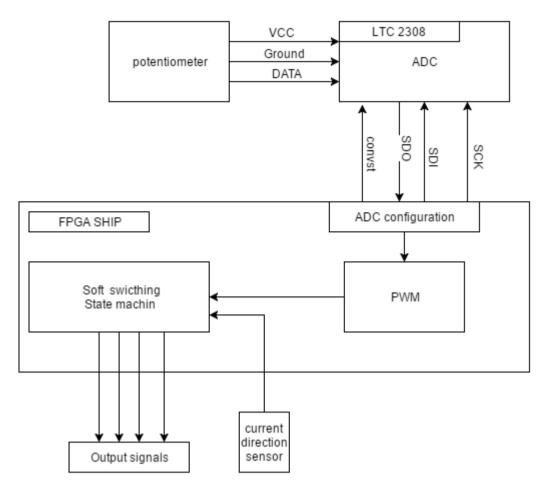

The implementation was made by programing and configuration the component on the board to generate the main signals to switch on our IGBTS, meaning a hardware design.

At the beginning the implementation was an open loop control, consisting on an analogue input varied with potentiometer at the input terminals of the LTC 2308 analogue to digital converter then the digital data should be sent to the PWM code in the FPGA unit to generate the PWM signal.

after that the PWM signal should pass to the state machine for having the four main signals in case of single phase regulation to control the four switches of our AC chopper. Figure 3-2 shows hardware design on DE0 board.

#### 3.3.1 ADC LTC 2308

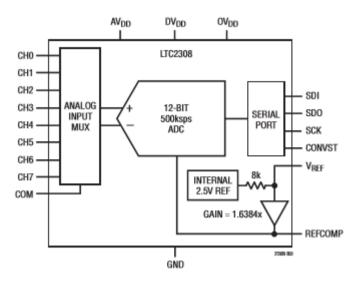

The LTC 2308 is a low noise, 500ksps, 8-channel, 12-bit ADC with a Serial Peripheral Interface (SPI) MICROWIRE compatible serial interface. This ADC includes an internal reference and a fully differential sample-and-hold circuit to reduce common mode noise.

The internal conversion clock allows the external serial output data clock (SCK) to operate at any frequency up to 40MHz. The LTC2308 operates from a single 5V supply and draws just 3.5mA at a sample rate of 500ksps. The auto-shutdown feature reduces the supply current to 200µA at a sample rate of 1ksps.

The LTC2308 is packaged in a small 24-pin 4mm × 4mm QFN. The internal 2.5V reference and 8-channel multiplexer further reduce PCB board space requirements.

The low power consumption and small size make the LTC2308 ideal for battery operated and portable applications, while the 4-wire SPI compatible serial interface makes this ADC a good match for isolated or remote data acquisition systems. Figure (3-3). [10]

Figure 3-3: LTC 2308 ADC block diagram [10]

AVDD: 5V Analog Supply. The range of AVDD is 4.75V to 5.25V. Bypass AVDD to GND with a  $0.1\mu$ F ceramic and a  $10\mu$ F tantalum capacitor in parallel, Pins 12, 13 on the FPGA.

OVDD: Output Driver Supply, Bypass OVDD to GND with a  $0.1\mu$ F ceramic capacitor close to the pin. The range of OVDD is 2.7V to 5.25V, Pin 19 on the FPGA.

DVDD: 5V Digital Supply, The range of DVDD is 4.75V to 5.25V. Bypass DVDD to GND with a 0.1  $\mu$ F ceramic and a 10 $\mu$ F tantalum capacitor in parallel, Pin 21.

CH0-CH2: Channel 0 to Channel 2 Analog Inputs, can be configured as single ended or differential input channels, Pins 22, 23, 24.

GND: Exposed Pad Ground, Must be soldered directly to ground plane, Pin 25 on the FPGA.

CONVST: (Conversion Start) A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends, Pin 14.

SDI : Serial Data Input. The SDI serial bit stream configures the ADC and is latched on the rising edge of the first 6 SCK pulses, Pin 15.

SCK: Serial Data Clock, SCK synchronizes the serial data transfer, The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK, Pin 16. [10]

## 3.3.1.1 ADC functionality

The LTC 2308 doesn't need any ADC code because it is implemented hardware on the chip but it must be configured via a code from the FPGA.

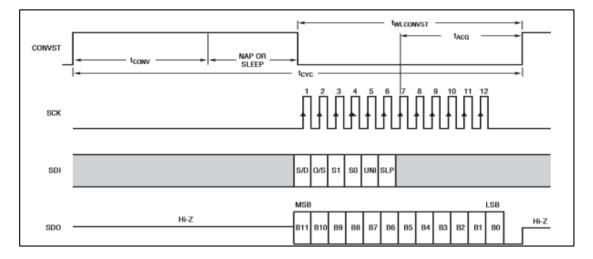

Figure 3-4: SPI ADC configuration [10]

The required configuration must respect the timing seen on Figure (3-4) the data conversion starts when the CONVST signal remains high, once the high edge comes, new data cannot be converted intel the current conversion is completed, this signal should be high during the conversion time which is the SLP bit that must be stet to a logic 1 in this case of configuration and nap time when SLP set to 0 the nap mode between conversions, thereby reducing the average power dissipation as the sample rate decreases.

Once the MSB appears on SDO pin 12 clock are generated from SCK pin and her comes the data exchange between the FPGA and the ADC bit per bit serially at each SCK clock or when the edge appears a configuration is sent and a data is received, Finite State Machine is used to generate the configuration code in our case.

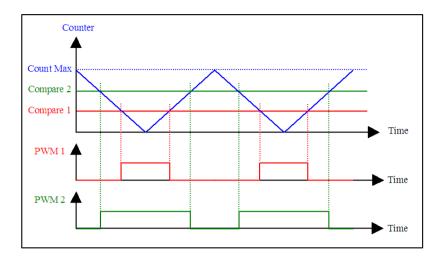

## 3.3.2 **Pulse Width Modulation signal**

Is the control signal and the variation depends on the analogue input converted to digital by ADC that gives data from 0 to 255, which are compared to carrier signal of 255 "11111111".

This signal is generated by a code which consists on an up and down counter increases at each clock edge, and when it reaches the maximum "255" value, start decreasing one number each clock cycle until it reaches zero and the pattern repeats again. This will give a triangle waveform. This triangular carrier signal is compared with data brought from the ADC.

Figure 3-5: PWM triangular carrier signal [10]

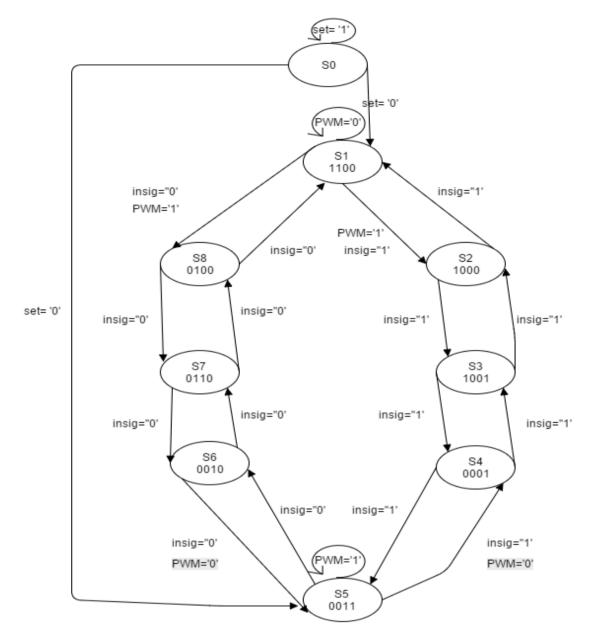

## 3.3.3 **Finite state machine FSM**

The PWM generated signal cannot control four switches at once in single phase case, due to the current direction signal so we must extract four signal from the PWM treating the cases when the PWM is up and down and taking the direction of current into account.

FSM is sequential logic operation, it uses memory logic and the input change to make transition each clock cycle which makes it very fast. Its structure also makes it less difficult and more optimum.

Finite state machine must be used in this code due to the presence of state transition to make the code smaller and easier to manage. Figure (3-6) shows structural diagram of our FSM.

Figure 3-6: FSM block diagram

The S0 state doesn't have an output, it is made to detect our initial state of the switches S1 or S5. We must verify the two transition conditions which are in our case PWM & direction of current to choose our state transition to avoid short circuit.

- For S1 to be an initial state If PWM='0' it keep in S1 until PWM changes to '1'.

- For S1 to be an initial state If PWM='1' & insig='0' path is {S1, S8, S7, S6, S5}.

- For S1 to be an initial state If PWM='1' & insig='1' path is {S1, S2, S3, S4, S5}.

- For S5 to be an initial state If PWM='1' it keep in S1 until PWM changes to '0'.

- For S5 to be an initial state If PWM='0' & insig='0' path is {S5, S4, S3, S2, S1}.

- For S5 to be an initial state If PWM='1' & insig='1' path is {S5, S6, S7, S8, S1}.

## 3.4 **DE0 implementation**

As defined previously the codes written in form of one component then compile, assign the pins PWM & switches signals to the GPIO\_0 pins and connect the potentiometer at the terminals of ADC.

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •           | 2 🗳 🗳 🚸 👔    | D 🕨 🖌 🤘 🚫       | 👃 🔌 🛃    |                 |        |         |     |         |          |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------------|----------|-----------------|--------|---------|-----|---------|----------|--|

| 4  | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | MOST.vhd     | ×               | ¥        | Assignment Edit | or     | ×       |     |         |          |  |

| << | new>> •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Filter on n | ode names: * |                 |          |                 |        |         |     | ~ Categ | ory: All |  |

|    | Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | From        | То           | Assignment Name | Value    | Enabled         | Entity | Comment | Tag |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | ADCST_c      | Location        | PIN_U9   | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | Le cike      | Location        | PIN_V11  | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | insing       | Location        | PIN_L10  | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[7]    | Location        | PIN_AA23 | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[6]    | Location        | PIN_Y16  | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[5]    | Location        | PIN_AE26 | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[4]    | Location        | PIN_AF26 | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[3]    | Location        | PIN_V15  | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[2]    | Location        | PIN_V16  | Yes             |        |         |     |         |          |  |

| )  | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[1]    | Location        | PIN_AA24 | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | PulseC[0]    | Location        | PIN_W15  | Yes             |        |         |     |         |          |  |

| 2  | <ul> <li>Image: Image: Ima</li></ul> |             | in_ reset1   | Location        | PIN_L9   | Yes             |        |         |     |         |          |  |

| 3  | <ul> <li>Image: Image: Ima</li></ul> |             | in_ reset2   | Location        | PIN_H6   | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | in_ reset3   | Location        | PIN_H5   | Yes             |        |         |     |         |          |  |

| ;  | <ul> <li>Image: Image: Ima</li></ul> |             | ADC_SCK_c    | Location        | PIN_V10  | Yes             |        |         |     |         |          |  |

| 5  | 🖌 📗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | ADC_SDI_c    | Location        | PIN_AC4  | Yes             |        |         |     |         |          |  |

| 7  | <ul> <li>Image: Image: Ima</li></ul> |             | incomp       | Location        | PIN_AD4  | Yes             |        |         |     |         |          |  |

| 3  | <ul> <li>Image: Image: Ima</li></ul> |             | outsw[3]     | Location        | PIN_V12  | Yes             |        |         |     |         |          |  |

|    | <ul> <li>Image: Image: Ima</li></ul> |             | outsw[2]     | Location        | PIN_AF7  | Yes             |        |         |     |         |          |  |

| )  | <ul> <li>Image: Image: Ima</li></ul> |             | outsw[1]     | Location        | PIN_W12  | Yes             |        |         |     |         |          |  |

| 1  | <ul> <li>Image: A second s</li></ul> |             | outsw[0]     | Location        | PIN_AF8  | Yes             |        |         |     |         |          |  |

| 2  | <ul> <li>Image: Image: Ima</li></ul> |             | Pulse_C      | Location        | PIN_W8   | Yes             |        |         |     |         |          |  |

Figure 3-7: Pins assignment

As discussed previously the figure below shows the switches signals:

a) Positive current:

#### Falling edge PWM:

| Start        | ▲<br>▼      | +4 µs | +5 µs | +6 µs | +7 µs | +8 µs |

|--------------|-------------|-------|-------|-------|-------|-------|

| 00 PWM       | 🔅 +5        |       |       |       |       |       |

|              |             |       |       |       |       |       |

| 02 out SW(4) | <b>*</b> +5 |       |       |       |       |       |

| 03 out SW(3) | +           |       |       |       |       |       |

| 04 out SW(2) | +5          |       |       |       |       |       |

| 05 out SW(1) | <b>()</b>   |       |       |       |       |       |

## **Rising edge:**

|     | <b>0</b> · · · ·  |              |    |       |       |       |       |       |

|-----|-------------------|--------------|----|-------|-------|-------|-------|-------|

|     | Start             | ~            | μs | +3 µs | +4 µs | +5 µs | +6 µs | +7 µs |

| D   | 0 PWM             | 🔅 +f         |    |       |       |       |       |       |

|     |                   |              |    |       |       |       |       |       |

| :   | ::                |              |    |       |       |       |       |       |

|     | 2 out SW(4)       | 🔅 +F         |    |       |       |       |       |       |

| 1   | 2 out SW(4)<br>:: | تانعا        |    |       |       |       |       |       |

| þ   | 3 out SW(3)       | 🔅 +F         |    |       |       |       |       |       |

| ÷   |                   |              |    |       |       |       |       |       |

| )   | 4 out SW(2)       | 🌣 +F         |    |       |       |       |       |       |

| -   |                   | <b>\$</b> +5 |    |       |       |       |       |       |

| 1   | 5 out SW(1)<br>:: |              |    |       |       |       |       |       |

| - 1 |                   |              |    |       |       |       |       |       |

### b) Negative current:

## **Rising PWM edge:**

|        | Chavb  |          |        |       |       |       |

|--------|--------|----------|--------|-------|-------|-------|

|        | Start  | <b>_</b> | +8 I 🗚 | +9 μs | +1 μs | +2 μs |

| 00 PWI | M      | 🌣 +f     |        |       |       |       |

|        |        |          |        |       |       |       |

| ::::   |        |          |        |       |       |       |

|        |        |          |        |       |       |       |

| 02 out | SW(4)  | 🌣 +f     |        |       |       |       |

| 02 out | 511(1) |          |        |       |       |       |

|        |        |          |        |       |       |       |

| 03 out | SW(3)  | 🔅 +f     |        |       |       |       |

| ****   |        |          |        |       |       |       |

| 04 out | SM(2)  | 🔅 +f     |        |       |       |       |

| 04 out | 511(2) |          |        |       |       |       |

|        |        |          |        |       |       |       |

| 05 out | SW(1)  | 🌣 +f     |        |       |       |       |

| 05 out |        |          |        |       |       |       |

|        |        |          |        |       |       |       |

## Figure 3-10: Signals at negative current rising edge

## Falling PWM edge:

| Start        | ~                  | +3 μs | +4 μs | +5 μs | +6 µs | +7 μs |

|--------------|--------------------|-------|-------|-------|-------|-------|

| 00 PWM       | 🔅 +f               |       |       |       |       |       |

|              |                    |       |       |       |       |       |

| 02 out SW(4) | ¢ +F               |       |       |       |       |       |

| 03 out SW(3) | <b>↔</b> + <u></u> |       |       |       |       |       |

| 04 out SW(2) | ¢ +F               |       |       |       |       |       |

| 05 out SW(1) | 🔅 +F               |       |       |       |       |       |

| 0       PVM       0       0         0       ctfSW(4)       0       0         0       ctfSW(2)       0       0         0       ctfSW(2)       0       0         0       ctfSW(2)       0       0         0       ctfSW(4)       0       0         0       ctfSW(2)       0       0         0       ctfSW(2)       0       0         1       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | +7 µs |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

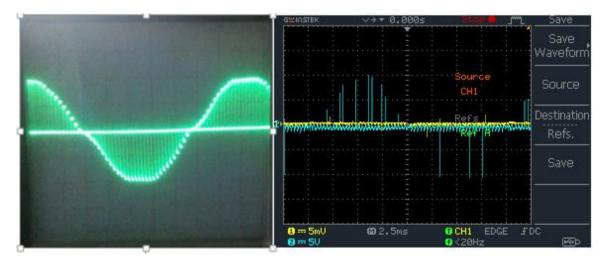

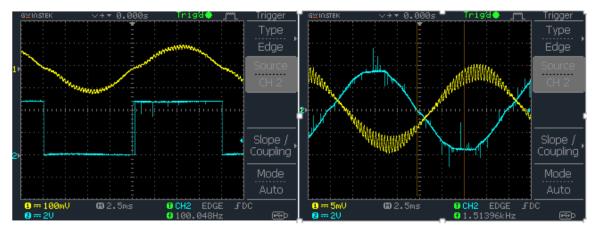

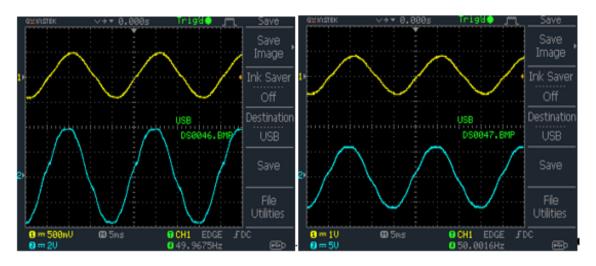

| v       ot1SW(4)       Image: Start               | +7 µs |