People's Democratic Republic of Algeria

# Ministry of Higher Education and Scientific Research University M'Hamed BOUGARA – Boumerdes

# Institute of Electrical and Electronic Engineering Department of Electronics

Final Year Project Report Presented in Partial Fulfilment of the Requirements for the Degree of

# **MASTER**

In Power Engineering

**Option: Power Engineering**

Title:

Study and Implementation of Real-Time Testing with Hardware in the Loop for Protection Relays and Power Meters

Presented by:

- Yazid BENTAYEB

Supervisor:

**Dr. Mohammed BOUCHAHDANE**

Registration Number:...../2020

# **Abstract**

Due to increasing need for power system protection functioning insurance and compliance to system needs for electrical devices protection, and their effect on the power system stability and customer services, protective relays and power meters needs to be tested to ensure compliance of the devices with the power system needs. Real-time simulator-based factory acceptance tests (FAT) are by now a necessary and well-established part of the process of developing and implementing new protection schemes by electric power utilities.

This thesis presents hardware implementation of adaptive protection relay and power meters testing models based on real time simulators. The simulation tool used was Opal-RT OP5600 real time digital simulator. To emulate the actual environment where the test model could be used, a complete phasor network setup is established using actual devices, such as protection relays, power meters and current and voltage amplifier.

A simulation models based on MATLAB/Simulink software were designed to perform real time simulation testing of the protective relays and power meters.

The obtained test results describe the functional states of the tested devices. The results are compared to the standards expected results and limitations.

# **Dedication**

I have a great pleasure to dedicate this modest work

To my Beloved Mother, my Dear Father

To my Dear Brothers, Uncles, Aunts and Cousins

To all my Friends

And to all with whom I spent wonderful moments

Yazid BENTAYEB

# Acknowledgement

In the name of Allah, the Most Gracious and the Most Merciful Alhamdulillah, all praises to Allah for the strengths and His blessing in completing this project.

I would like to express my deepest and sincere gratitude to my project Supervisor Dr.

Mohammed BOUCHAHDANE. It was a great privilege and honor to work and study under your supervision. Thank you very much.

Last but not least, I am infinitely grateful to my family members, particularly my parents for their patience, unwavering support, continuous encouragement, and belief in me throughout my whole life. I would have never made it this far without them beside me in every step of the way.

# **Table of Contents**

| Abst | tract     |          | • • • • • • • • • • • • • • • • • • • • |                                                | 1      |

|------|-----------|----------|-----------------------------------------|------------------------------------------------|--------|

| Dedi | ication   |          |                                         |                                                | ii     |

| Ack  | nowledg   | gement.  |                                         |                                                | iii    |

| Tabl | le of Co  | ntents   |                                         |                                                | iv     |

| List | of Table  | es       |                                         |                                                | vii    |

| List | of Figu   | res      |                                         |                                                | viii   |

| List | of Abbr   | eviation | ns & Acrony                             | ms                                             | xi     |

| Gen  | eral intr | oductio  | n                                       |                                                | 1      |

| Cha  | pter 1:   | Real Tir | me Simulation                           | n Software and Hardware                        | 3      |

| 1    | Introd    | luction. |                                         |                                                | 3      |

|      | 1.1       | Softw    | are                                     |                                                | 3      |

|      |           | 1.1.1    | MATLAB S                                | Simulink®                                      | 3      |

|      |           | 1.1.2    | RT-LAB®:                                |                                                | 3      |

|      |           | 1.1.3    | AcSELerato                              | or QuickSet®                                   | 4      |

|      |           | 1.1.4    | AcSELerato                              | or Analytic Assistant & SEL SynchroWAVe Event. | 4      |

|      |           | 1.1.5    | F6 Multiple                             | Amplifier Configurator v5.0.0                  | 5      |

|      |           | 1.1.6    | TeamViewe                               | er                                             | 5      |

|      | 1.2       | Hardv    | vare                                    |                                                | 6      |

|      |           | 1.2.1    | Opal-RT rea                             | al time simulators                             | 6      |

|      |           |          | <b>1.2.1.1</b> Ove                      | rview                                          | 6      |

|      |           |          | <b>1.2.1.2</b> OP5                      | 600 simulator platform                         | 7      |

|      |           |          | <b>1.2.1.3</b> Hard                     | lware architecture and components              | 8      |

|      |           |          | i)                                      | OP5600 exploded view                           | 8      |

|      |           |          | ii)                                     | Spartan-3 FPGA (Field-Programmable Gate Arr    | ay)8   |

|      |           |          | iii)                                    | Target Computer – x86 Architecture Platform    | 8      |

|      |           |          | iv)                                     | I/O Modules                                    | 9      |

|      |           |          | v)                                      | Front and back views                           | 10     |

|      |           | 1.2.2    | Doble F635                              | 0 Current / Voltage Amplifier                  | 11     |

|      |           | 1.2.3    | Schweitzer                              | Engineering Laboratories SEL-487E and SEL      | ـ-411L |

|      |           |          | relays                                  |                                                | 12     |

|      |           |          | i)                                      | SEL-487E relay                                 | 12     |

|      |           |          | ii)                                     | SEL-411L relay                                 | 13     |

|      |          | 1.2.4    | Schw                                       | veitzer Engineering Laboratories SEL-735 Power Qua | ality and |  |  |

|------|----------|----------|--------------------------------------------|----------------------------------------------------|-----------|--|--|

|      |          |          | Reve                                       | nue Meter                                          | 15        |  |  |

|      | 1.3      | Concl    | usion.                                     |                                                    | 16        |  |  |

| Chap | ter 2: I | Real Tim | ne Simi                                    | ulation Models For RT-LAB Projects                 | 17        |  |  |

|      | 2.1      | Introd   | uction                                     |                                                    | 17        |  |  |

|      | 2.2      | Creati   | Creating Simulink models for relay testing |                                                    |           |  |  |

|      |          | 2.2.1    | Gene                                       | ral relay testing model                            | 17        |  |  |

|      |          | 2.2.2    | Gene                                       | ral overview of Opal RT simulator's model          | 18        |  |  |

|      |          | 2.2.3    | Relay                                      | y testing model top-level                          | 19        |  |  |

|      |          |          | i)                                         | ARTEMIS Guide and Powergui blocks                  | 20        |  |  |

|      |          |          | ii)                                        | Model Initialisation block                         | 21        |  |  |

|      |          | 2.2.4    | Relay                                      | y testing model computation subsystem              | 22        |  |  |

|      |          |          | i)                                         | Power system circuit                               | 22        |  |  |

|      |          |          | ii)                                        | Fault initiation circuit                           | 22        |  |  |

|      |          |          | iii)                                       | Inputs/outputs card programming circuit            | 24        |  |  |

|      |          |          | iv)                                        | Voltages and Currents injection circuit            | 25        |  |  |

|      |          |          | v)                                         | Trip and signals receiving circuit                 | 26        |  |  |

|      |          |          | vi)                                        | Data acquisition circuit                           | 27        |  |  |

|      |          | 2.2.5    | Relay                                      | y testing model GUI subsystem                      | 28        |  |  |

|      |          |          | i)                                         | Fault timing control circuit                       | 28        |  |  |

|      |          |          | ii)                                        | Graphical user interface circuit                   | 28        |  |  |

|      | 2.3      | Imple    | mentin                                     | g distance Mho function in Simulink model          | 29        |  |  |

|      |          | 2.3.1    | Mho                                        | distance protection theory                         | 29        |  |  |

|      |          | 2.3.2    | Mho                                        | model "SC_NETWORK" computation subsystem           | 31        |  |  |

|      |          |          | i)                                         | Power system and fault initiation circuits         | 32        |  |  |

|      |          |          | ii)                                        | Harmonics removal and filters circuit              | 32        |  |  |

|      |          |          | iii)                                       | Fault detection circuit                            | 35        |  |  |

|      |          |          | iv)                                        | Fault type and zone selection logic circuit        | 37        |  |  |

|      |          | 2.3.3    | Mho                                        | model "SC_MhoConsole" GUI subsystem                | 39        |  |  |

|      | 2.4      | Imple    | mentin                                     | g Time overcurrent Function in Simulink model      | 39        |  |  |

|      |          | 2.4.1    | Time                                       | Overcurrent (TOC) protection theory                | 39        |  |  |

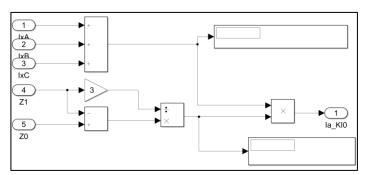

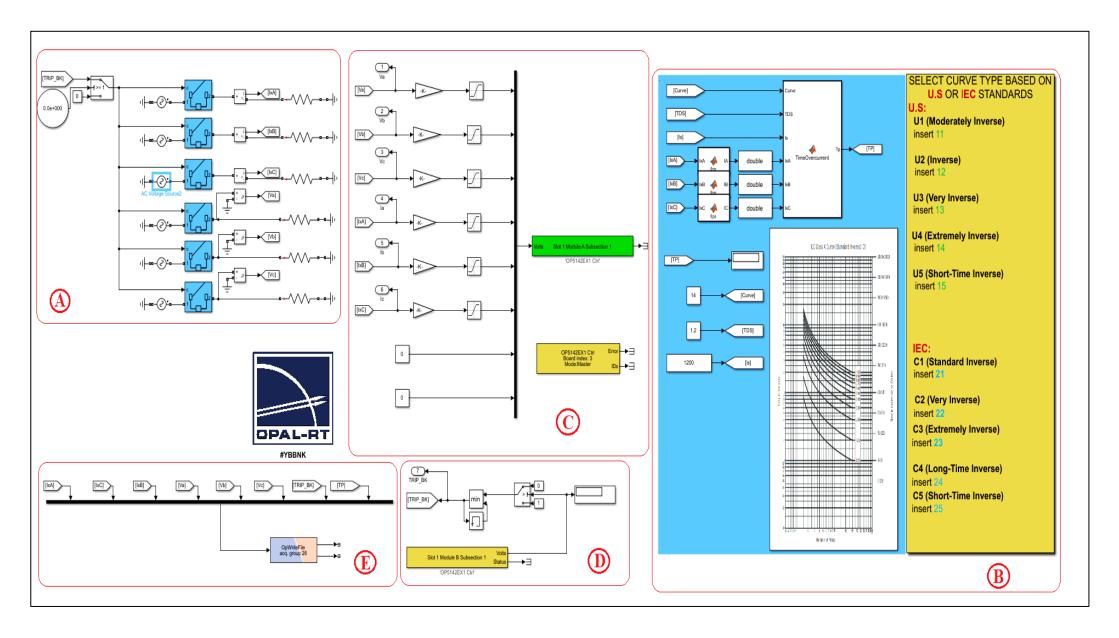

|      |          | 2.4.2    | TOC                                        | model "SM_DirectInj" computation subsystem         | 42        |  |  |

|      |          |          | i)                                         | Voltages and Currents selection circuit            | 42        |  |  |

|      |          |          | ii)                                        | TOC function block                                 | 44        |  |  |

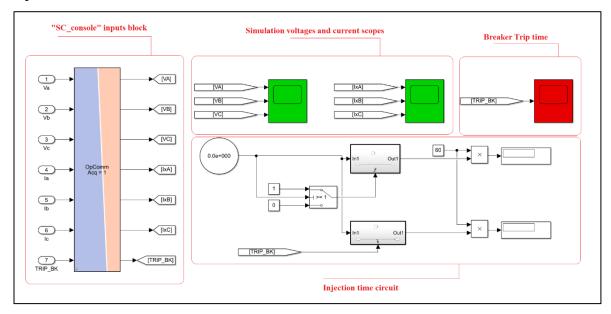

|      |          | 2.4.3    | TOC                                        | model "SC_TOCconsole" GUI subsystem                | 45        |  |  |

|      |          |          |                                            | ·                                                  |           |  |  |

|      | 2.5      | Creati      | ng Sim   | nulink models for Power Meters testing                | 45 |  |

|------|----------|-------------|----------|-------------------------------------------------------|----|--|

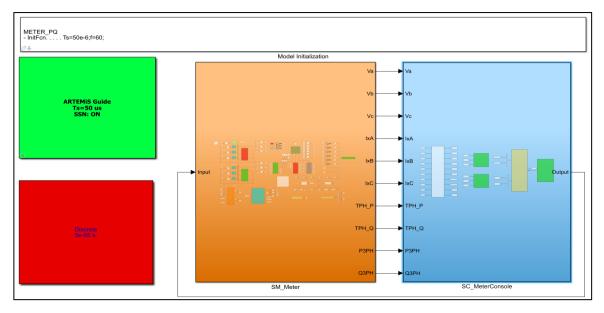

|      |          | 2.5.1       | Gene     | ral overview of Power meters model                    | 45 |  |

|      |          | 2.5.2       | Meter    | r testing model "SM_Meter" computation subsystem      | 46 |  |

|      |          |             | i)       | ANSI/IEC standards test block                         | 48 |  |

|      |          |             | ii)      | Phase shift applying circuit                          | 49 |  |

|      |          |             | iii)     | Test Voltages and Currents selection circuit          | 50 |  |

|      |          |             | iv)      | Three phase real and reactive power calculation block | 50 |  |

|      |          | 2.5.3       | Meter    | r testing model "SC_MeterConsole" GUI subsystem       | 50 |  |

|      |          | 2.5.4       | Conc     | lusion                                                | 51 |  |

| Chap | ter 3: I | Experin     | nental I | Results and Discussion                                | 52 |  |

|      | 3.1      | Introd      | uction   |                                                       | 52 |  |

|      | 3.2      | Confi       | guratio  | n phase                                               | 52 |  |

|      |          | 3.2.1       | Confi    | guration of SEL-411L                                  | 54 |  |

|      |          | 3.2.2       | Confi    | iguration of SEL-487E                                 | 54 |  |

|      |          | 3.2.3       | Confi    | iguration of Doble F6350 Current / Voltage Amplifier  | 54 |  |

|      | 3.3      | Editio      | n phas   | e                                                     | 54 |  |

|      | 3.4      | Prepar      | ration p | phase                                                 | 55 |  |

|      | 3.5      | Comp        | ilation  | phase                                                 | 56 |  |

|      | 3.6      | Execu       | ition ph | ase                                                   | 57 |  |

|      | 3.7      | Collec      | ction pl | hase                                                  | 58 |  |

|      | 3.8      | Simul       | ation to | ests and results                                      | 60 |  |

|      |          | 3.8.1       | Mho      | model test results                                    | 60 |  |

|      |          | 3.8.2       | TOC      | model test results                                    | 65 |  |

|      |          | 3.8.3       | Mete     | r model test results                                  | 66 |  |

|      |          | 3.8.4       | Test 1   | results Discussion                                    | 68 |  |

|      | 3.9      | Concl       | usion    |                                                       | 69 |  |

| Chap | ter 4: C | General     | Conclu   | sion & Future Work                                    | 70 |  |

|      | 4.1      | Gener       | al Con   | clusion                                               | 70 |  |

|      | 42       | Future Work |          |                                                       |    |  |

# **List of Tables**

| Table.1.1: Simulator Platforms comparison.                                  | 6  |

|-----------------------------------------------------------------------------|----|

| <b>Table 1.2:</b> Features and protection functions of SEL-487E relay       | 13 |

| <b>Table 1.3:</b> Features and protection functions of SEL-411L relay       | 14 |

| <b>Table 2.1:</b> Fault Impedance Calculation on different fault situations | 30 |

| Table 2.2: U.S. Time-Overcurrent Equations.                                 | 41 |

| Table 2.3: IEC. Time-Overcurrent Equations                                  | 41 |

| Table 3.1: Distance relay protection function tests                         | 60 |

| Table 3.2: Distance relay protection function test results                  | 60 |

| Table 3.3: TOC relay protection function tests.                             | 65 |

| Table 3.4:    Meter model test values and meter readings                    | 66 |

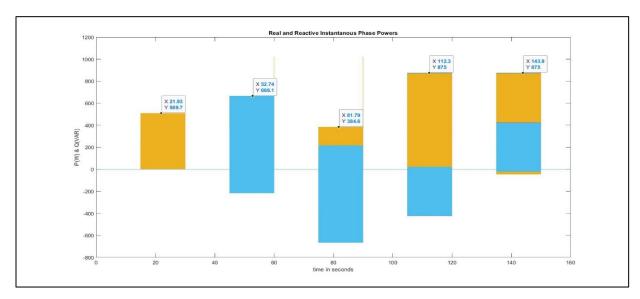

| Table 3.5: Per-phase real powers                                            | 67 |

| Table 3.6: Per-phase reactive powers                                        | 67 |

# **List of Figures**

| Figure 1.1: Target Simulator to host computer connection                            | 7   |

|-------------------------------------------------------------------------------------|-----|

| Figure 1.2: OP5600 simulator exploded view.                                         | 8   |

| Figure 1.3: Target computer components.                                             | 8   |

| Figure 1.4: OP5600 analog Inputs/outputs cards.                                     | 9   |

| Figure 1.5: OP5600 digital Inputs/outputs cards                                     | 10  |

| Figure 1.6: OP5600 front view.                                                      | 10  |

| Figure 1.7: OP5600 back view.                                                       | 10  |

| Figure 1.8: Doble F6350 amplifier.                                                  | 11  |

| <b>Figure 1.9:</b> Typical test setup utilizing one F6350                           | 12  |

| Figure 1.10: SEL-487E relay's front panel.                                          | 12  |

| Figure 1.11: SEL-411L relay's front panel.                                          | 14  |

| Figure 1.12: SEL-735 Meter front and rear panels                                    | 15  |

| Figure 2.1: Opal RT simulator's model subsystems.                                   | 18  |

| Figure 2.2: Top level view of the relay testing model                               | 19  |

| Figure 2.3: "Powergui" block settings                                               | 20  |

| Figure 2.4: "ARTEMIS Guide" block settings                                          | 20  |

| Figure 2.5: "Model Initialisation" block settings                                   | 21  |

| Figure 2.6: "ssn_distgridA1_init.m" file settings.                                  | 21  |

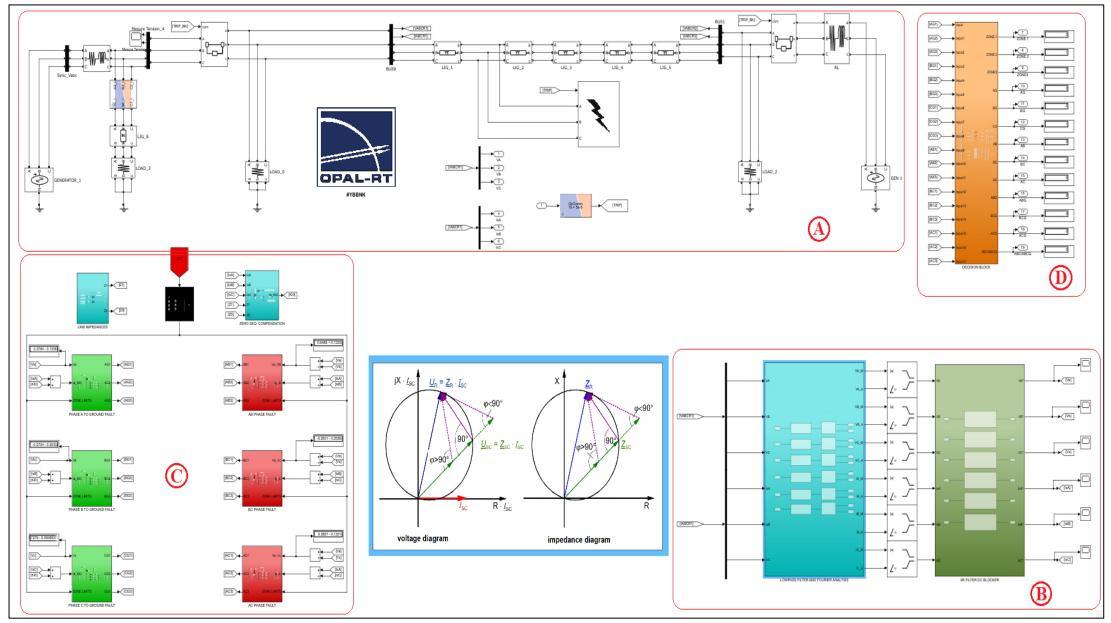

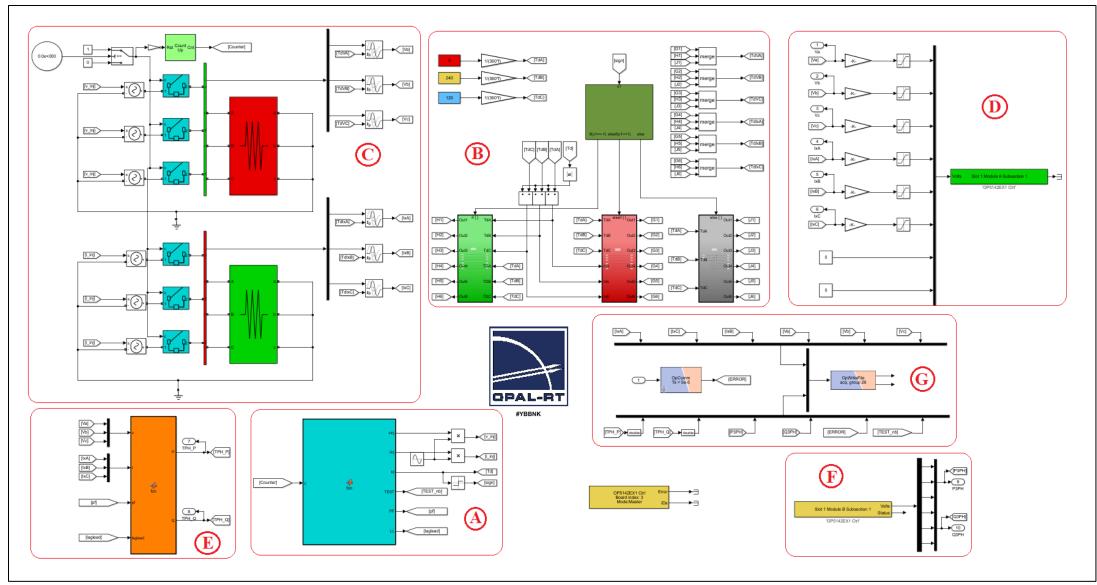

| Figure 2.7: "Sm_NETWORK" computation block                                          | 23  |

| Figure 2.8: "Three-phase fault" block settings for BC fault type                    | 24  |

| Figure 2.9: Build error report with wrong board ID and Bitstream FileName settings  | 24  |

| Figure 2.10: ".bin" and ".conf" files.                                              | 25  |

| Figure 2.11: A) ".conf" file configurations. B) "OpCtrlOP5142EX1" settings          | 25  |

| Figure 2.12: "OpWriteFile" block settings.                                          | 27  |

| Figure 2.13: A) Fault timing control circuit. B) Graphical user interface circuit   | 28  |

| Figure 2.14: A) mho circle voltage diagram. B) mho circle impedance diagram         | 31  |

| Figure 2.15: Mho model top-level view.                                              | 31  |

| Figure 2.16: A) Power system and fault initiation circuits. B) Harmonics removal    | and |

| filters circuits. C) Fault detection circuit. D) Fault type selection logic circuit | 33  |

| Figure 2.17: low pass filter settings.                                              | 34  |

| Figure 2.19: Fourier analysis block settings.                                       | 34  |

| <b>Figure 2.18:</b> low pass filter phase and magnitude response                    | 34  |

| <b>Figure 2.20:</b> "DC blocker" block settings                                     | 35          |

|-------------------------------------------------------------------------------------|-------------|

| Figure 2.21: Fault detection circuit.                                               | 35          |

| Figure 2.22: Phase A to ground fault detection circuit.                             | 36          |

| Figure 2.23: positive and zero sequence impedances calculation                      | 36          |

| Figure 2.24: Mho model zone limits                                                  | 37          |

| Figure 2.25: Zero sequence compensation circuit.                                    | 37          |

| <b>Figure 2.26:</b> Fault type and zone selection logic circuit.                    | 38          |

| <b>Figure 2.27:</b> "SC_MhoConsole" GUI subsystem                                   | 39          |

| <b>Figure 2.28:</b> Inverse time overcurrent characteristic curve                   | 40          |

| Figure 2.29: TOC model top-level view.                                              | 42          |

| Figure 2.30: A) Voltages and Currents selection circuit. B) TOC function block. C   | )Voltages   |

| and Currents injection circuit. D) Trip signal receiving circuit. E) Data ac        | equisition  |

| circuit                                                                             | 43          |

| Figure 2.31: "SC_TOCconsole" GUI subsystem                                          | 45          |

| <b>Figure 2.32:</b> Meter test model top-level view                                 | 46          |

| Figure 2.33: A) ANSI/IEC standards tests block. B) Phase shift applying circuit     | t. C) Test  |

| Voltages and Currents selection circuit. D) Test Voltages and Currents injection of | circuit. E) |

| Three phase real and reactive power calculation block. F) Three phase meter's power | er reading  |

| circuit. G) Data acquisition circuit.                                               | 47          |

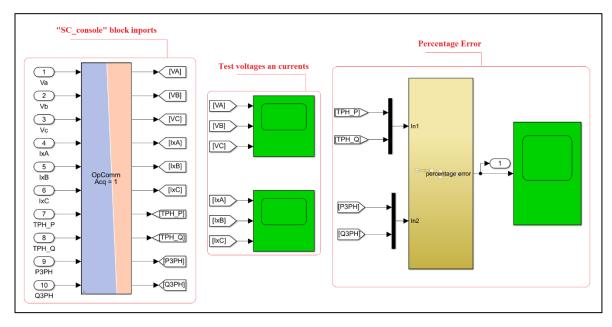

| <b>Figure 2.34:</b> "SC_MeterConsole" GUI subsystem                                 | 51          |

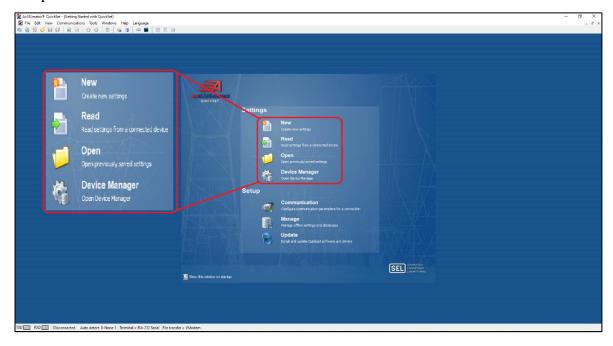

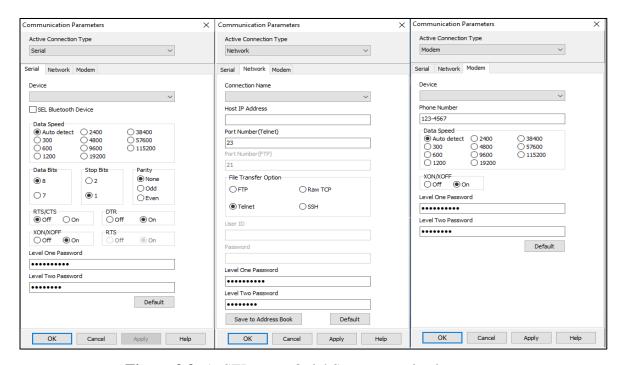

| Figure 3.1: A) AcSELerator QuickSet software icon. B) starting window               | 52          |

| <b>Figure 3.2:</b> AcSELerator QuickSet Home page.                                  | 53          |

| Figure 3.3: AcSELerator QuickSet communication types.                               | 53          |

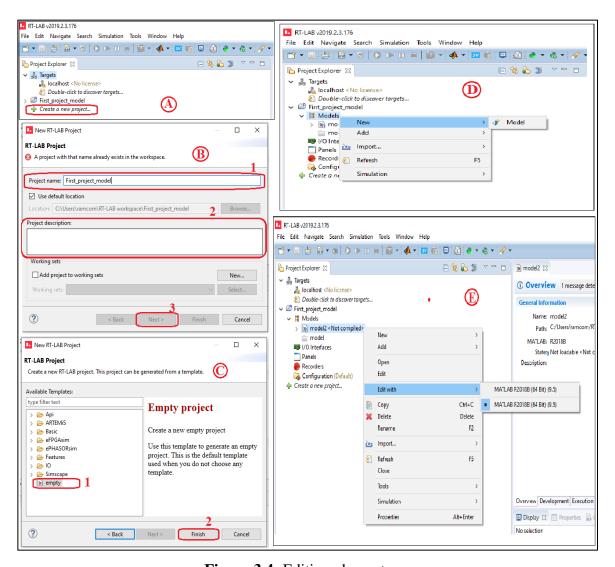

| <b>Figure 3.4:</b> Edition phase steps.                                             | 55          |

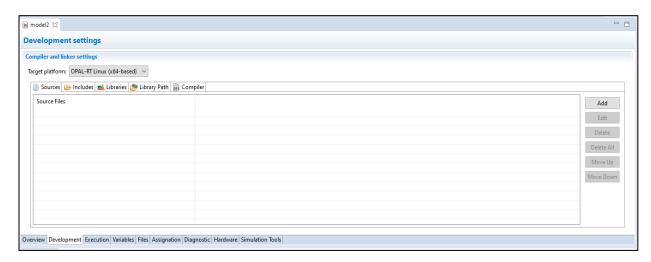

| <b>Figure 3.5:</b> Development settings window.                                     | 56          |

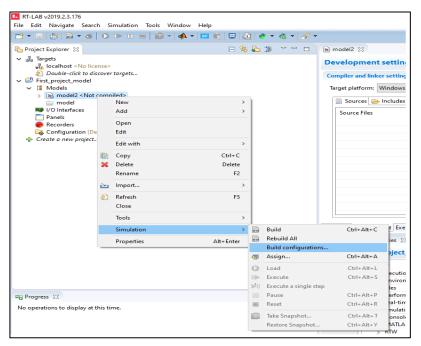

| <b>Figure 3.6:</b> Building the model                                               | 56          |

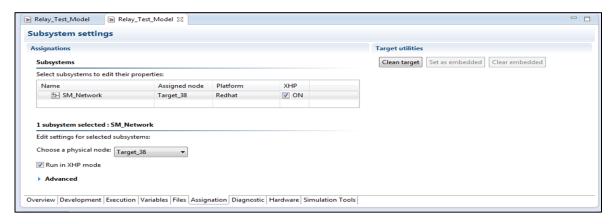

| <b>Figure 3.7:</b> Assignation window settings.                                     | 57          |

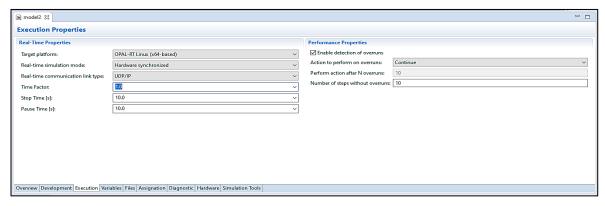

| Figure 3.8: Execution window settings.                                              | 57          |

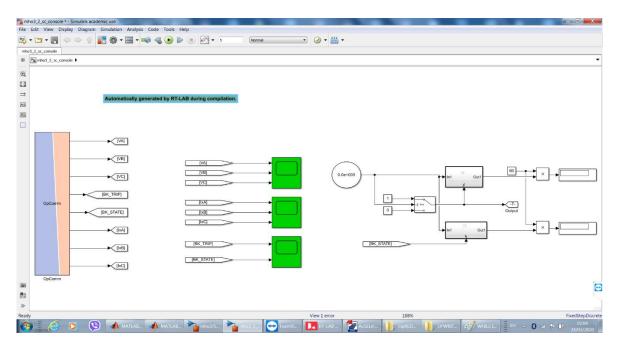

| Figure 3.9: "SC_console" GUI subsystem displayed at the end of load process         | 58          |

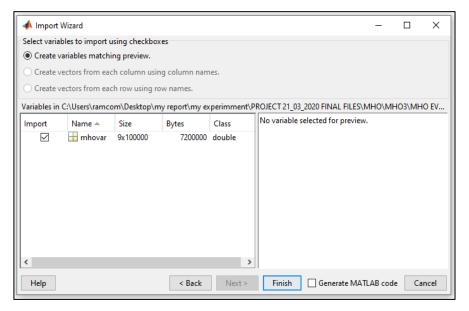

| <b>Figure 3.10:</b> "OpWrite" file opened with MATLAB                               | 59          |

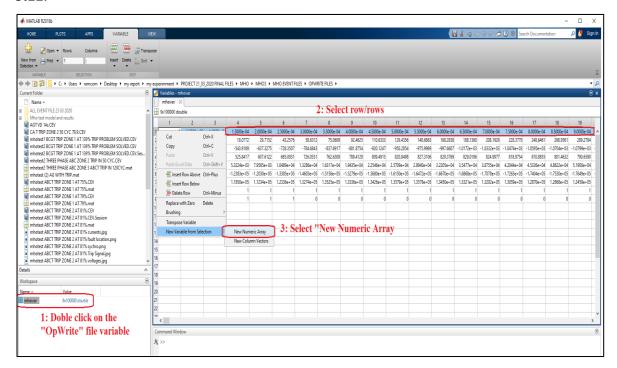

| Figure 3.11: Variable creation step from MATLAB variable                            | 59          |

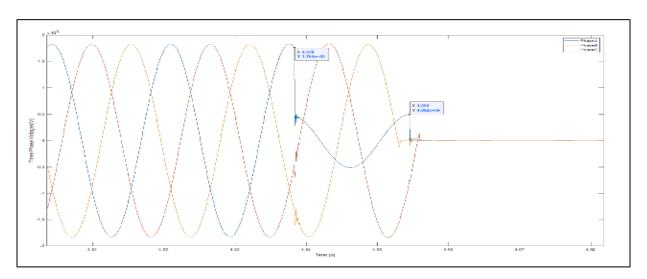

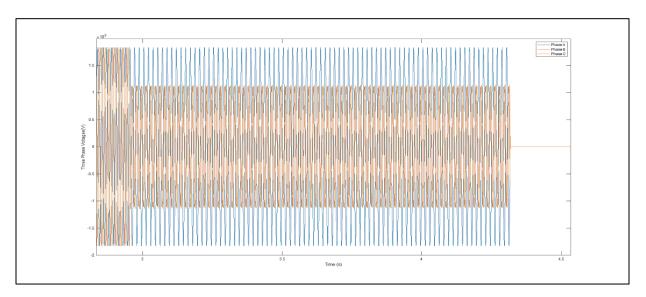

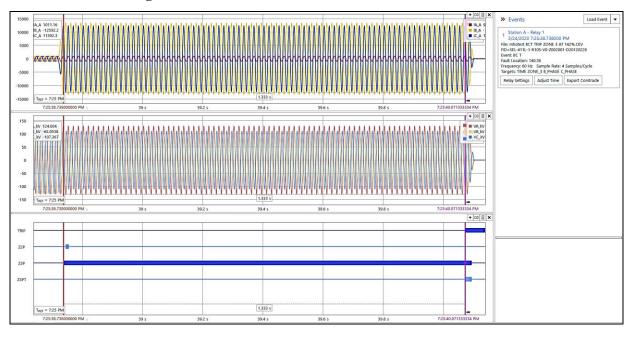

| Figure 3.12: Phase A-Ground zone 1 fault Voltages                                   | 61          |

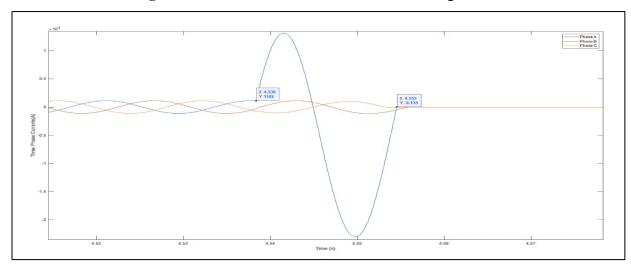

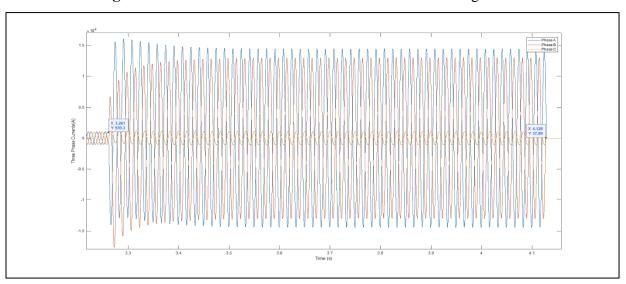

| Figure 3.13: Phase A-Ground zone 1 fault Currents                                   | 61          |

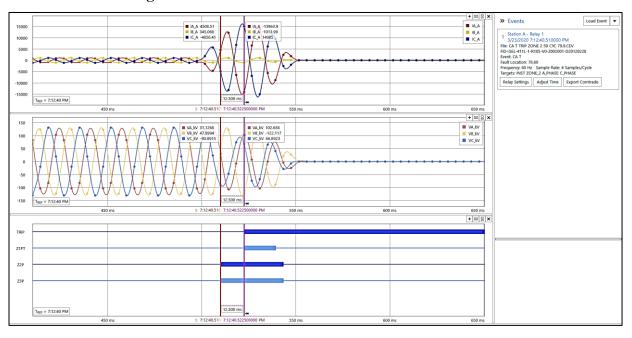

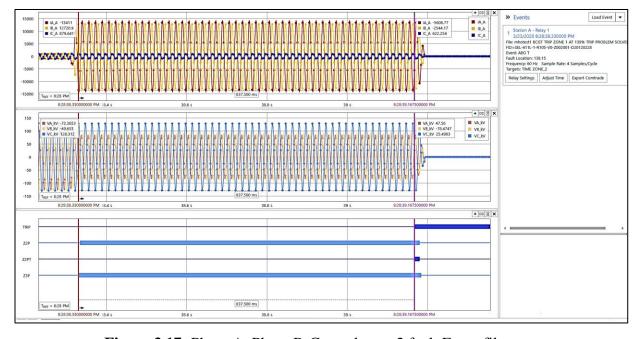

| <b>Figure 3.14:</b> Phase A-Ground zone 1 fault Event file                          | 61          |

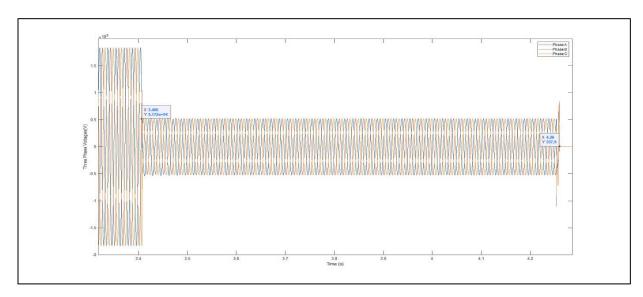

| <b>Figure 3.15:</b> Phase A–Phase B-Ground zone 2 fault Voltages.                   | 62          |

| Figure 3.16 Phase A–Phase B-Ground zone 2 fault Currents                    | 62 |

|-----------------------------------------------------------------------------|----|

| Figure 3.17: Phase A–Phase B-Ground zone 2 fault Event file                 | 62 |

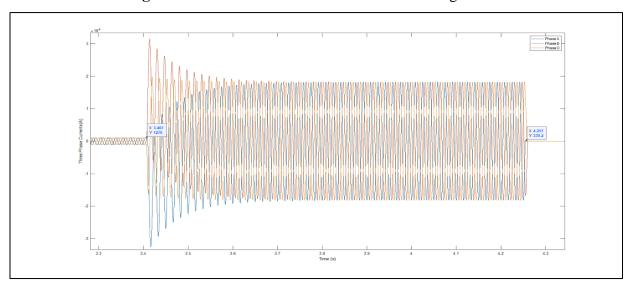

| Figure 3.18: Phase B–Phase C zone 3 fault Voltages                          | 63 |

| Figure 3.19: Phase B-Phase C zone 3 fault Currents                          | 63 |

| Figure 3.120: Phase B—Phase C zone 3 fault Event file                       | 63 |

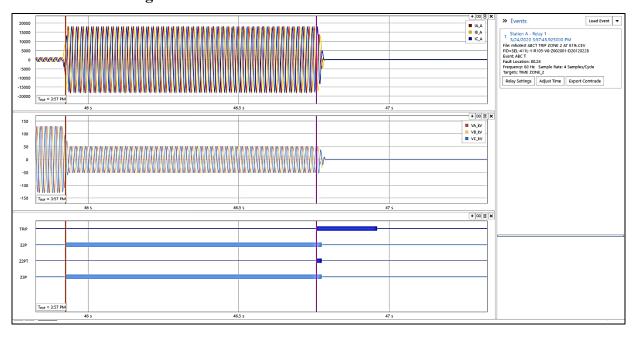

| Figure 3.21: Three Phase ABC zone 2 fault Voltages                          | 64 |

| Figure 3.22: Three Phase ABC zone 2 fault Currents                          | 64 |

| Figure 3.23: Three Phase ABC zone 2 fault Event file                        | 64 |

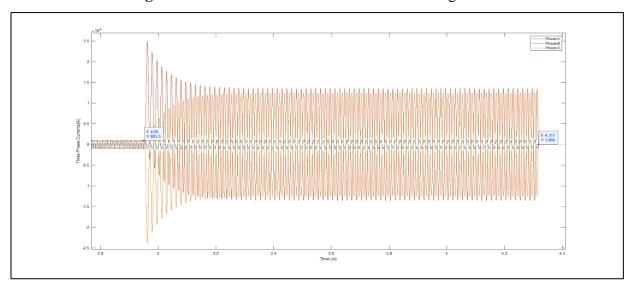

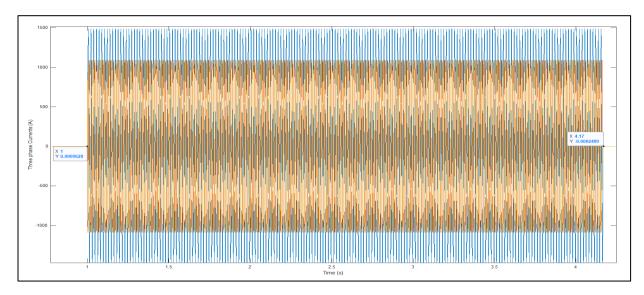

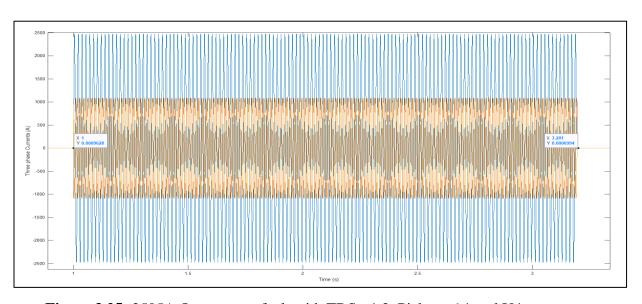

| Figure 3.24: 1505A Overcurrent fault with TDS= 1.2, Pickup=6.1 and U1 curve | 65 |

| Figure 3.25: 2505A Overcurrent fault with TDS= 1.2, Pickup=6.1 and U4 curve | 65 |

| Figure 3.26: 2505A Overcurrent fault with TDS= 1, Pickup=6.1 and U4 curve   | 66 |

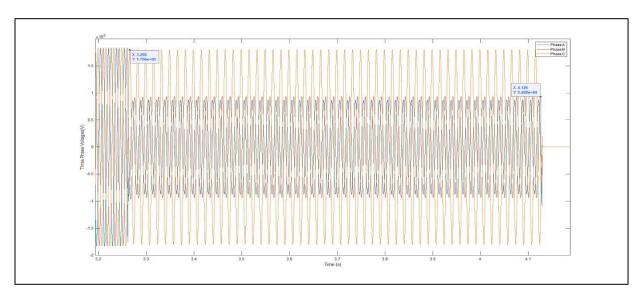

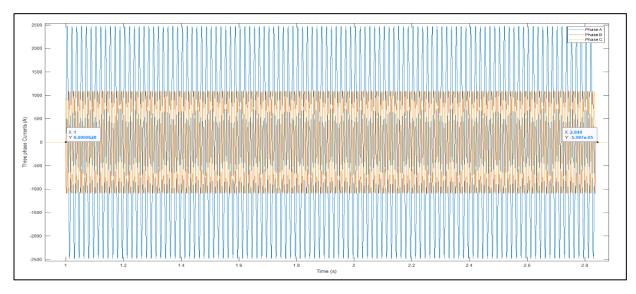

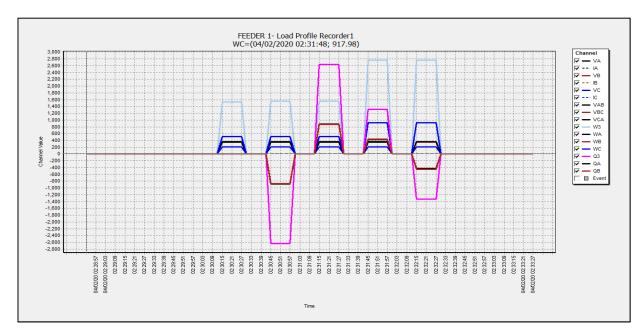

| Figure 3.27: Simulator three phase currents and voltages                    | 67 |

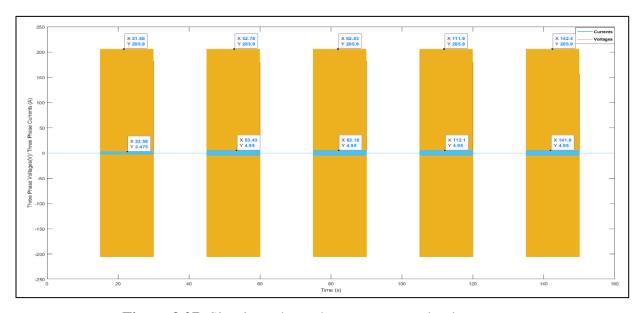

| Figure 3.28: Simulator instantaneous real and reactive powers               | 68 |

| Figure 3.29: LDP file plot from meter HMI                                   | 68 |

# **List of Abbreviations & Acronyms**

ANSI, American National Standards Institute.

FPGA, Field Programmable Gate Arrays.

HIL, Hardware-In-the-Loop.

HMI, Human Machine Interface.

IEC, International Electrical Commission.

I/O, Input and Output.

LDP, Load Power.

RT-LAB, Real Time Laboratory.

SEL, Schweitzer Engineering Laboratories.

TDS, Time Dial Settings.

TOC, Time Overcurrent.

U.S, United States.

XHP, eXtreme High Performance.

# **General introduction**

Electric system utilities push power systems to operate close to their limits due to the rapid expansion of the power system and to meet the increased consumers demand and with the economic and environmental restrictions. Consequently, system wide disturbances that may lead to outages and blackouts become more likely. At the same time, nature accidents or human-errors causes, such as lightnings, wind damage, ice loading, falling trees, vehicle and bird accidents, human errors, digging into underground cable and many others can initiate system imbalance and lead to disturbances that may lead to system blackouts. Thus, the utilities demand higher reliability and security of the electric service to preserve a stable and secure electric power system. Although it may not be possible to completely prevent the system blackouts due to economical and technological restrictions. It is possible to limit their frequency and intensity with the aid of system control and protection strategies, by developing and testing power system schemes. Today, the major challenging task for an electrical engineer is ensuring a high level of continuity of service to customers even under system disturbance.

The power system protection schemes use protection relays to ensure the protection of the power grids and system equipment's. The protection relays are electrical device that are designed to respond to input conditions in a prescribed manner and, after specified conditions are met, to cause contact operation to trip circuit breaker and isolate fault part of the power system. Hence, ensuring full functionality of the protective relays leads to ensure healthy power transmission and distribution.

The electric system utilities are companies in the electric power industry (often a public utility) that engages in electricity generation and distribution of electricity for sale generally in a regulated market. These companies need to compute the delivered power to the customer for the sale purpose. The power and quality revenue meters are used to perform system's power flow computations. Besides to the Protective relays, meters must be tested to ensure compliance of the device to be used.

This report is divided into four chapters:

- **Chapter 1:** introduces software and hardware used for testing Protective relays and power meters with real time simulators.

- **Chapter 2:** presents theory for the experiment of testing protective relays and power meters using Opal-RT OP5600 real time simulator.

- **Chapter 3:** presents the experimental procedures followed for real time simulation test with hardware in the loop method.

- **Chapter 4:** presents conclusion and Future work.

# Chapter 1: Real Time Simulation Software and Hardware

#### 1.1 Introduction:

This chapter introduces the software and hardware used for realising this master thesis. Opal RT-LAB simulator platforms uses MALAB Simulink based models for simulation. Opal RT Technologies integrates RT-Lab software with MATLAB Simulink so that it you can access to Simulink through RT-LAB software. Opal RT simulator platform outputs are used for low-level interface, for tests with high voltage we use amplifiers. F6 Multiple Amplifier Configurator is used to configure F6350 Doble amplifier. Configuration of SEL relays and meters are done through AcSELerator QuickSet software.

#### 1.2 Software:

#### 1.1.1 MATLAB Simulink®:

Simulink is a MATLAB-based graphical programming environment for modelling, simulating and analysing multidomain dynamical systems. Its primary interface is a graphical block diagramming tool and a customizable set of block libraries. It offers tight integration with the rest of the MATLAB environment and can either drive MATLAB or be scripted from it. Simulink is widely used in automatic control and digital signal processing for multidomain simulation and model-based design. In this project Simulink is used for building and simulating the experimental circuit.

#### 1.2.2 **RT-LAB®**:

RT-LAB is OPAL-RT's real-time simulation software combining performance and enhanced user experience. Fully integrated with MATLAB/Simulink®, RT-LAB offers the most complex model-based design for interaction with real-world environments. It provides the flexibility and scalability to achieve the most complex real-time simulation applications in the automotive, aerospace, power electronics, and power systems industries. RT-LAB handles everything, including code generation, with an easy-to-use interface. With just a few clicks of the mouse, a Simulink® model becomes an interactive real-time simulation application.

RT-LAB's acquisition system acts like a virtual oscilloscope, by allowing the user to visualize waveforms in real-time without glitches and data loss. It can run continuously or based on user-configured triggers to capture specific events. Its core engine provides the accuracy and the bandwidth for the most demanding real-time applications with hundreds of channels and microsecond precision. With the possibility of recording thousands of

measurement points, RT-LAB provides users with a complete data history. The format is compatible with other simulation and post-processing software. These advanced acquisition features are done without disturbing the real-time simulation and by keeping a maximal availability for executing the user's model.

#### 1.2.3 AcSELerator QuickSet® [12]:

AcSELerator QuickSet® SEL-5030 Software is a tool for engineers and technicians to quickly and easily design, deploy, and manage devices for power system protection, control, metering, and monitoring. Through use of this software, you can perform the following:

- ➤ Configure settings for supported devices. For most SEL devices, QuickSet has smart drivers that automatically verify if settings are within an acceptable range. A legacy grid editor driver supports legacy devices.

- ➤ Organize devices in the QuickSet Device Manager. The Device Manager plugin provides a straightforward way to organize devices and to associate connection parameters, documents, device settings, and device parameters.

- ➤ Create and implement Design Templates. The optional Design Templates allow for consistent setup and reduced configuration time. Lock settings so they match your standards, or lock and hide unused settings to reduce entry error.

- ➤ View operational status or device history at your convenience. The customizable human-machine interface (HMI) displays pertinent device data locally or remotely so that verifying and analysing device performance becomes easier.

With the AcSELerator QuickSet Human-Machine Interface (HMI) you are able to obtain pertinent device data locally or remotely with the customizable HMI. Automatic live updates provide fast visual information and eliminate the need to rely on command line inputs. View operational status or history at your convenience, and make adjustments as needed. Verify and analyse device performance with a graphical representation of digital and analog information. HMI interfaces are specific to each device.

#### 1.2.4 AcSELerator Analytic Assistant & SEL SynchroWAVe Event:

AcSELerator Analytic Assistant and SEL-5601-2 synchroWAVe Event Software helps engineers to diagnose a protective relay's behaviour during a power system fault. It is

a powerful yet easy-to-use solution for displaying and analysing SEL relay event reports from SEL devices and COMTRADE files.

The SEL-5601-2 SYNCHROWAVE® Event Software provides the following components and capabilities:

#### Basic and advanced:

- ➤ Analog and digital charts.

- ➤ Harmonic and spectral analysis.

- ➤ Phasor value derivation and display.

- ➤ Automatic calculation of symmetrical components.

- ➤ Reconfigurable display.

- ➤ ACB or ABC phase rotation support.

- ➤ Searchable signal lists and relay settings.

- ➤ View COMTRADE and SEL ASCII format event reports.

## **1.2.5** F6 Multiple Amplifier Configurator v5.0.0:

F6 Multiple Amplifier Configurator is a software for configuring and controlling several F6 amplifiers (F6350/e and F6300/e). The software is hosted on one computer and can control/configure up to 16 amplifiers. Configuration of amplifiers is required to enable correct amplification of the low-level signals that are provided by a host simulator. The amplified signal must be of the correct magnitude, based on conversion factors that are selected as part of the configuration process. The configuration software configures both the AC analog outputs of the amplifiers and also the battery output of the F6350s. This software can run on both Windows 7 and Windows XP operating systems.

#### 1.2.6 TeamViewer:

TeamViewer is a comprehensive, remote access, remote control and remote support solution that works with almost every desktop and mobile platform, including Windows, macOS, Android, and iOS. TeamViewer lets you remote into computers or mobile devices located anywhere in the world and use them as though you were there.

#### 1.3 Hardware:

# 1.3.1 Opal-RT real time simulators [3]:

#### **1.3.1.1 Overview:**

OPAL-RT TECHNOLOGIES is the leading developer of open Real-Time Digital Simulators and Hardware-In-the-Loop testing equipment for electrical, electro-mechanical and power electronic systems. OPAL-RT Simulators are used by engineers and researchers at leading manufacturers, utilities, universities and research centres around the world.

OPAL-RT offers a wide range of simulator platforms as shown in table **Table.1.1** to meet all current industry needs and forthcoming challenges. All simulators are based on a modular and flexible design, and are fully customizable and expandable for specific I/O requirements.

**Table.1.1**: Simulator Platforms Comparison.

| Simulator platform   | OP4200   | OP4510     | OP5600       | OP5707       | OP5031       |

|----------------------|----------|------------|--------------|--------------|--------------|

| Compatible           | RT-LAB   | RT-LAB     | RT-LAB       | RT-LAB       | RT-LAB       |

| Simulation Systems   | eFPGASIM | HYPERSIM   | HYPERSIM     | HYPERSIM     | HYPERSIM     |

| and Software         |          | eMEGASIM   | eMEGASIM     | eMEGASIM     | eMEGASIM     |

|                      |          | ePHASORSIM | ePHASORSIM   | ePHASORSIM   | ePHASORSIM   |

|                      |          | eFPGASIM   | eFPGASIM     | eFPGASIM     |              |

| CPU                  | ARM      | INTEL XEON | INTEL XEON   | INTEL XEON   | INTEL XEON   |

|                      |          | E3         | E5           | E5           | E5           |

| Number of cores      | 2        | 4          | 4,8,16 or 32 | 4,8,16 or 32 | 4,8,16 or 32 |

| XILINX FPGA          | ZYNQ     | Kintex 7   | Spartan 3    | Virtex 7     | n/a          |

| (standard            | (7030)   | (325T)     |              | (485T)       |              |

| configuration)       |          |            |              |              |              |

| SFP optical          | 2        | 4          | 0            | 16           | n/a          |

| interface            |          |            |              |              |              |

| (GTX 5 Gbits/s)      |          |            |              |              |              |

| I/O modules with 16  | 4        | 4          | 8            | 8            | n/a          |

| analog or 32 digital |          |            |              |              |              |

| signals              |          |            |              |              |              |

| Maximum number       | 128      | 128        | 256          | 256          | n/a          |

| of I/O channels      |          |            |              |              |              |

#### 1.3.1.2 OP5600 simulator platform:

The OP5600 real-time simulator is the most adopted simulation platform by OPAL-RT's users in industry and academia. OP5600 combines the performance, versatility and reliability that is ideal for demanding hardware-in-the-loop applications. Whether working within the power systems, aerospace, automotive, oil and gas or other electro-mechanical industries, the OP5600 has the power to simulate systems, while offering all the I/Os required to get your hardware into the loop.

It has two primary sections: an upper section containing analog and digital I/O signal modules, and a bottom section containing the multi-core processor computer and FPGA capable of running the entire OPAL-RT suite of real-time simulation software.

The OP5600 can be configured with up to 32 Intel Xeon E5 processing cores, and comes with a custom-designed Linux operating system, providing the best real-time performance on the market. The OP5600 also provides the option of user-programmable I/O management, handled by a fast Xilinx® Artix®-7 FPGA.

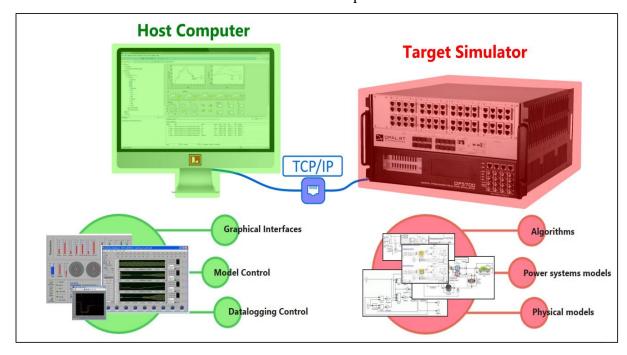

In general, the simulator (target simulator) is connected to a computer (host computer) as illustrated in **Figure 1.1** via ethernet cable with TCP/IP communication protocol. the host computer is supposed to send and control the model, display the graphical results, and receive or read the stored simulation results files in the simulator and some other functions. While the target simulator is supposed to load, build and run the model, during simulation the simulator can store the data without affecting the simulation operation's results and at the end it sends the file to the host computer.

**Figure 1.1:** Target Simulator to host computer connection.

## 1.3.1.3 Hardware architecture and components:

## i) OP5600 exploded view:

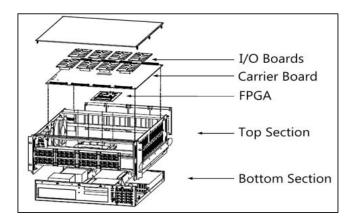

the OP5600 contains five main parts: I/O board, carrier board, FPGA, top section and bottom section as illustrated in **Figure 1.2.**

Figure 1.2: OP5600 simulator exploded view.

## ii) Spartan-3 FPGA (Field-Programmable Gate Array):

- Can connect with up to 8 swappable OPAL-RT I/O boards (Digital or Analog I/O).

- Highly flexible: Many different IO combinations possible.

- Large Capacity: Up to 256 I/O connections available.

- Sampling time: 100 MHz.

## iii) Target Computer - x86 Architecture Platform:

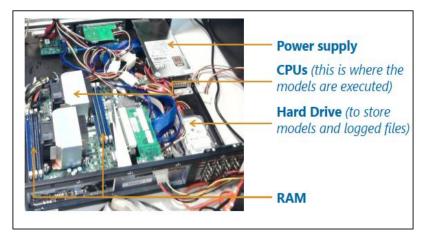

The OP5600 simulator also named the target computer. Its different parts located at the bottom section are shown in **Figure 1.3**.

Figure 1.3: Target computer components.

## iv) I/O Modules:

# (1) Analog Connection Layout:

16 channels per mezzanine card:

■ OP5330: 16 analog outputs.

• OP5340: 16 analog inputs.

# Analog outputs:

• 16 single-ended channels

Resolution 16 bits

■ Voltage range +/- 16 V

- Conversion time: 1 μs

# Analog inputs

• 16 differential channels

Resolution 16 bits

■ Voltage range +/- 20 V

• Conversion time: 0.5 or 2.5

Figure 1.4: OP5600 analog Inputs/outputs cards.

# (2) Digital Connection Layout:

32 channels per Mezzanine Card

• OP5360: 32 digital outputs.

• OP5353: 32 digital inputs.

## **Digital Outputs:**

■ 32 channels.

• Optical isolation.

• User-defined output voltage (5 to 30 V).

Max current +/- 50 mA per channel.

# Digital Inputs:

■ 32 channels

Optical isolation

• Flexible input voltage (4 to 50 V)

■ Input current 3.6 mA

**Figure 1.5:** OP5600 digital Inputs/outputs cards.

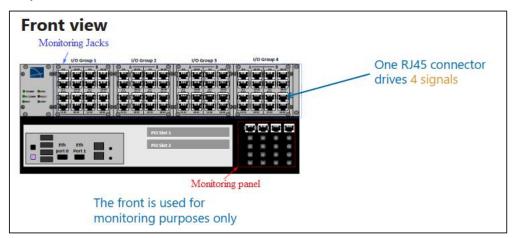

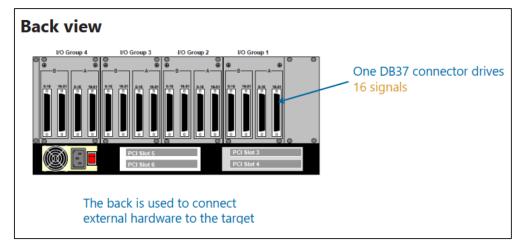

# v) Front and back views:

The front and back views are illustrated in **Figure 1.6** and **Figure 1.7** respectively.

Figure 1.6: OP5600 front view.

Figure 1.7: OP5600 back view.

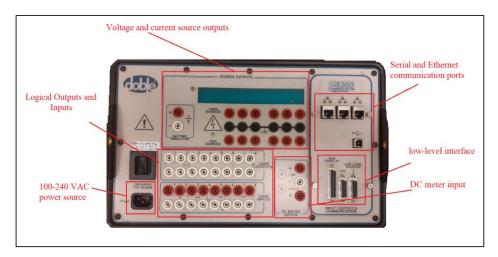

#### 1.3.2 Doble F6350 Current / Voltage Amplifier:

Doble's F6350 shown in **Figure 1.8** is used as current/voltage amplifier as shown above. It receives the low-level signal from the real time simulator and supplies the amplified signals to device under test.

The F6350 is designed to accept a range of low-level signals and the output range is selected to conform linearly to the low-level input signals. A 6.7 V rms low level signal will produce a voltage equal to the high end of voltage range selected for the F6350. For example, if the output range is selected as 75V, 6.7V rms will correspond to 75V. If a range of 150V is selected, the 6.7V rms will generate an output of 150V. The three ranges of voltage outputs are 75V, 150V and 300V.

Similarly, the current channels are designed such that a 3.4V rms low level signal will correspond to the high end of the current range selected for the F6350.

The F6350 supports a transient current output. A low-level signal of 6.8V rms corresponds to a transient current output of 1.5 times the normal current range for 1.5 seconds.

Figure 1.8: Doble F6350 amplifier.

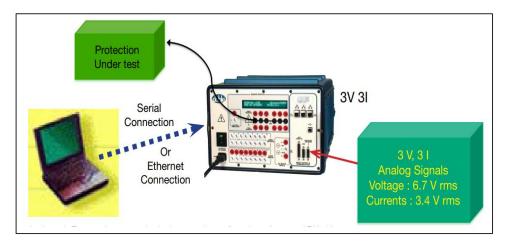

The selection of the ranges and the enabling of the amplifiers are performed via the F6350 software that is installed on the PC. The communication between F6350 and the configuration software is user selectable. This selection is done via the configuration software "F6 Multiple Amplifier Configurator". **Figure 1.9** shows a typical setup using one Doble F6350 Voltage and current amplifier.

**Figure 1.9:** Typical test setup utilizing one F6350.

#### 1.3.3 Schweitzer Engineering Laboratories SEL-487E and SEL-411L relays:

## i) **SEL-487E** relay [6]:

The SEL-487E relay shown in **Figure 1.10**, provides a suite of current and voltage elements for the comprehensive protection of power transformers. In total, the relay consists of 24 analog channels, divided into three groups of analog inputs. The first group consists of 15 channels for phase current inputs that are divided into five groups of three-phase inputs. The second group consists of three channels for single-phase (neutral) current inputs, and the third group consists of six channels for two three-phase voltage inputs.

**Figure 1.10:** SEL-487E relay's front panel.

The SEL-487E contains many protection, automation, and control features. **Table 1.2** presents features and protection functions of the relay.

**Table 1.2:** Features and protection functions of SEL-487E relay.

| ANSI numbers | Function name                                                  |  |

|--------------|----------------------------------------------------------------|--|

| 16SEC        | Access Security (Serial, Ethernet)                             |  |

| 24           | Volts/Hertz                                                    |  |

| 25           | Synchronism Check                                              |  |

| 27           | Undervoltage                                                   |  |

| 32           | Directional Power                                              |  |

| 46           | Current Unbalance                                              |  |

| 49           | Thermal                                                        |  |

| 50BF         | Breaker Failure Overcurrent                                    |  |

| 50N          | Neutral Overcurrent                                            |  |

| 50 (P, G, Q) | Overcurrent (Phase, Ground, Neg. Seq.)                         |  |

| 51N          | Neutral Time-Overcurrent                                       |  |

| 51 (P, G, Q) | Time-Overcurrent (Phase, Ground, Neg. Seq.)                    |  |

| 59           | Overvoltage                                                    |  |

| 67 (P, G, Q) | Directional Overcurrent (Phase, Ground, Neg. Seq.)             |  |

| 81 (O, U)    | Over- and Underfrequency                                       |  |

| 85 RIO       | SEL MIRRORED BITS® Communications                              |  |

| 87 (U, R, Q) | Transformer Differential (Unrestrained, Restrained, Neg. Seq.) |  |

| DFR          | Event Reports                                                  |  |

| ENV          | SEL-2600                                                       |  |

| HMI          | Operator Interface                                             |  |

| LGC          | Expanded SELOGIC® Control Equations                            |  |

| MET          | High-Accuracy Metering                                         |  |

| PMU          | Synchrophasors                                                 |  |

| REF          | Restricted Earth Fault                                         |  |

| RTU          | Remote Terminal Unit                                           |  |

| SER          | Sequential Events Recorder                                     |  |

# ii) **SEL-411L** relay [5]:

SEL-411L relay shown in **Figure 1.11** is a high-speed transmission line differential, distance, and current protection relay featuring single-pole and three-pole tripping and reclosing with synchronism check, circuit breaker monitoring, circuit breaker failure protection, and series-compensated line protection logic. The

relay features extensive metering and data recording including high-resolution data capture and reporting.

Figure 1.11: SEL-411L relay's front panel.

The SEL-411L contains many protection, automation, and control features.

**Table 1.3** presents features and protection functions of the relay.

**Table 1.3:** Features and protection functions of SEL-411L relay.

| ANSI numbers | Function name                                      |

|--------------|----------------------------------------------------|

| 16SEC        | Access Security (Serial, Ethernet)                 |

| 21           | Phase & Ground distance                            |

| 25           | Synchronism Check                                  |

| 27           | Undervoltage                                       |

| 49           | Thermal                                            |

| 50BF         | Breaker Failure Overcurrent                        |

| 50N          | Neutral Overcurrent                                |

| 50 (P, G, Q) | Overcurrent (Phase, Ground, Neg. Seq.)             |

| 51N          | Neutral Time-Overcurrent                           |

| 51 (P, G, Q) | Time-Overcurrent (Phase, Ground, Neg. Seq.)        |

| 59           | Overvoltage                                        |

| 67 (P, G, Q) | Directional Overcurrent (Phase, Ground, Neg. Seq.) |

| 67           | Out-Of-Step trip and/or block                      |

| 79           | Single/Three-pole reclosing                        |

| 85 RIO       | SEL MIRRORED BITS® Communications                  |

| 87L          | Line current differential                          |

| DFR | Event Reports                       |

|-----|-------------------------------------|

| ENV | SEL-2600                            |

| HMI | Operator Interface                  |

| LGC | Expanded SELOGIC® Control Equations |

| MET | High-Accuracy Metering              |

| PMU | Synchrophasors                      |

| REF | Restricted Earth Fault              |

| RTU | Remote Terminal Unit                |

| SER | Sequential Events Recorder          |

Schweitzer Engineering laboratories provides relays with a set of communication ports, analogue/digital inputs and outputs and expanded SELOGIC control Equations and graphical functions designs that allows the user to expand relay's functionality and enhance relay's flexibility and reliability.

# 1.3.4 Schweitzer Engineering Laboratories SEL-735 Power Quality and Revenue Meter [7]:

The SEL-735 Power Quality and Revenue Meter shown in **Figure 1.12** provides high-accuracy revenue metering and power quality metering for electric utilities and industrial applications. The SEL-735 has flexible, user-programmable SELOGIC control equations that include mathematical functions. The metering and control functions are ideal for complete automation applications.

The SEL-735 Power Quality and Revenue Meter Instruction Manual describes common aspects of power quality and revenue meter applications. It includes the necessary information to install, set, test, and operate the meter and more detailed information about settings and commands.

**Figure 1.12:** SEL-735 Meter front and rear panels.

## 1.4 Conclusion:

This chapter has dealt with the main software and hardware used for the implementation of this project. These devices are available at the Tennessee's university laboratory and controlled remotely using TeamViewer software.

In this chapter we presented: MATLAB Simulink, RT-LAB®, AcSELerator QuickSet®, AcSELerator Analytic Assistant & SEL SynchroWAVe Event, F6 Multiple Amplifier Configurator v5.0.0 and TeamViewer, these software are used for the realisation of this project.

In this chapter we presented: OP5600 simulator platform, Doble F6350 Current/Voltage Amplifier, SEL-411L, SEL-487E relays and SEL-735 Meter, these hardware are used for the implementation of this project.

# **Chapter 2: Real Time Simulation Models For RT-LAB Projects**

#### 2.1 Introduction:

This chapter explains the theory for the experiment of testing protective relays and power meters using Opal-RT OP5600 real time simulator and Doble F6350 amplifier. Hardware-In-the-loop method is implemented to interface the hardware directly with the simulation, the calculations and results of the simulation can be injected directly to the connected devices. Another advantage of this method is that in normal testing methods we inject directly a predefined tests values. In reality, the fault currents and voltages differ from these last. For power meters we load all the tests to the model according the ANSII or IEC standards then we run the simulation.

# 2.2 Creating Simulink models for relay testing:

### 2.2.1 General relay testing model:

Testing relays with real time digital simulators using Hardware-In-the-Loop (HIL) method gives rise to three main parts to appear in the experiment. The first part is the simulation part where we simulate the power system protected by the relays, which is the part needed to perform the fault analysis to find power system currents and voltages in the different parts of the faulted circuit.

The second part is used to inject the calculated values from the simulation to the relays, in this part we interface relay with simulator via the analog outputs of the simulator. The simulator's analog outputs can inject up to 16V comparing to the normal values in the secondary of voltage transformers it is too small, so either we need to amplify the injected values or; in such cases if available, we use the low-level interface of the relay which is basically the normal input divided by a factor that can be found in the relay's manual.

The third part receives the relay's word-bit which is the decision token by the relay such as trip or a communication signal. These signals are needed to be sent to the simulator in order to trip circuit breakers where needed in the circuit or to communicate with other relays. The simulator uses the digital inputs to read the relay's outputs to open or close circuit breakers or to communicate with other relays by sending the signals via the simulator's digital outputs. In this manner we are implementing HIL method for testing protective relays.

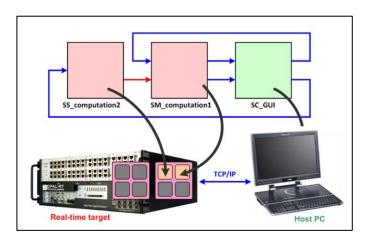

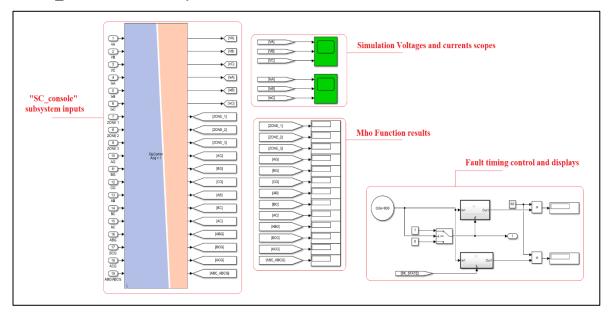

#### 2.2.2 General overview of Opal RT simulator's model [3]:

In general, In RT-LAB platforms, subsystems objectives are to distinguish computation subsystems and graphical user interface (GUI) and Assign computation subsystems to different CPU cores. Opal RT simulator's model consists of two types of subsystems; as shown in **Figure 2.1**, computation and GUI subsystem. A computation subsystem will be executed in real-time on one CPU core of the real-time target, where GUI subsystem will be displayed on the Host PC. The data between the Computation subsystem and GUI subsystem will exchanged asynchronously through the TCP/IP link [3].

Figure 2.1: Opal RT simulator's model subsystems.

The computation elements of the Simulink Model can be split into different computation subsystems. Each of the computation subsystems will be executed on one CPU core of the real-time target and the data between any two of the computation subsystems is exchanged synchronously onboard the simulator.

Only subsystems are allowed at the top-level of the Simulink model. These ones are assigned to the wright role with a prefix added to the block name separated with an underscore in the form XX\_AnyName, the prefix can be either "SC" for GUI subsystem, or "SM" for primary computation subsystem or if only one subsystem is available and "SS" for any additional computation subsystem.

During simulation phase each subsystem will be separated, the communication between subsystems is established with the "OpComm" block, it can be founded in RT-LAB library of the Simulink® library browser, once RT-LAB has been installed. "OpComm" block must be added after creation and naming of the subsystem. All subsystems (SM, SS, SC) inputs must first go through an "OpComm" block before any operations can be done on the signals they are associated with. One "OpComm" block can accept multiple inputs in one subsystem. Double-click on the block to select the number of inputs required.

"Powergui" block is an environment block for Simscape Electrical Specialized Power Systems models allows to choose between one of the different solving methods. "ARTEMIS Guide" also is an environment block from Artemis library they are located on the top-level of the model.

#### 2.2.3 Relay testing model top-level:

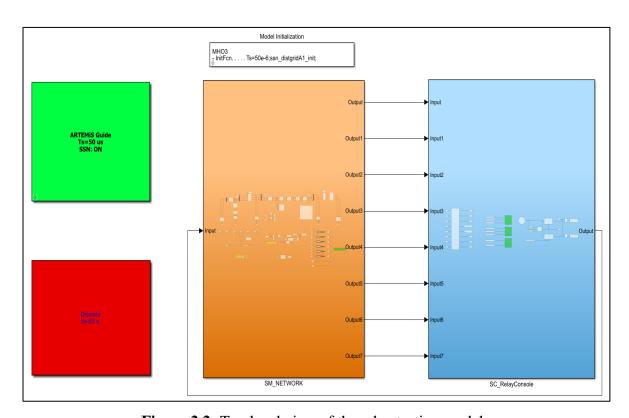

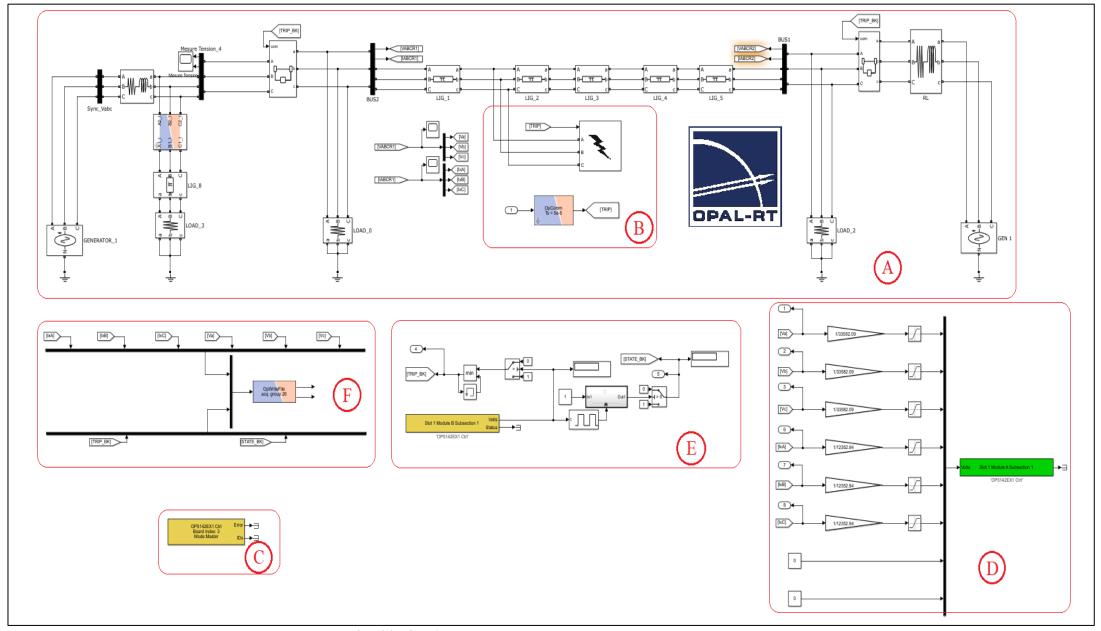

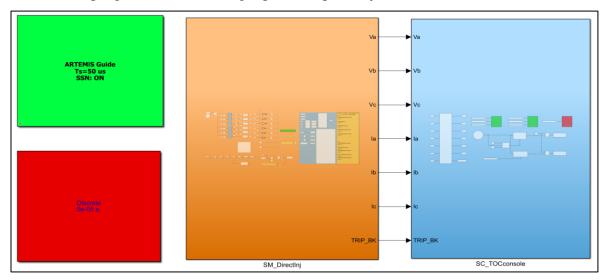

In our experiment and as shown **Figure 2.2**, the model consists of two subsystems; the "SM\_NETWORK", a computation block contains the power system, analog outputs, digital inputs, and some other blocks needed in simulation. While the "SC\_RelayConsole" contains scopes of the signals to be displayed in the host computer during simulation.

**Figure 2.2:** Top level view of the relay testing model.

The two blocks on the left of **Figure 2.2** are the "ARETEMIS Guide" and "Powergui" blocks in green and red colours respectively. The white block is the "Model initialization" block, it is linked to a MATLAB code ".m" file in which such constants and parameters are declared.

Each block must be configured to meet the simulations parameters, in the next parts we are going to introduce the configuration needed for the simulation and for the relays testing. Any non-mentioned parameters can be left as default.

#### i) ARTEMIS Guide and Powergui blocks:

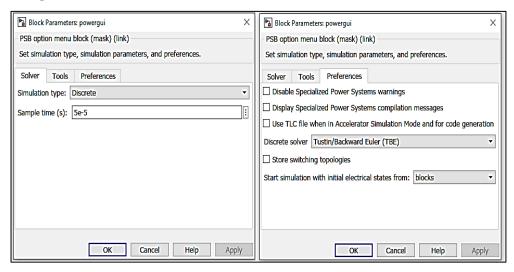

In the "powergui" block, simulation parameters were set with a "Discrete" simulation type, "Tustin/Backward Euler (TBE)" discrete solver type and "5e-5" sample time in seconds (in MATLAB "e-5" tends for ten to the power of minus five) or "Ts" if it is declared before in the "Model Initialisation" block, parameters are shown in **Figure 2.3**.

Figure 2.3: "Powergui" block settings.

In the "ARTEMIS Guide" block, the "art5" state-space discretization method was applied and a sample time of "5e-5" seconds. Parameters are shown in **Figure 2.4**.

Figure 2.4: "ARTEMIS Guide" block settings.

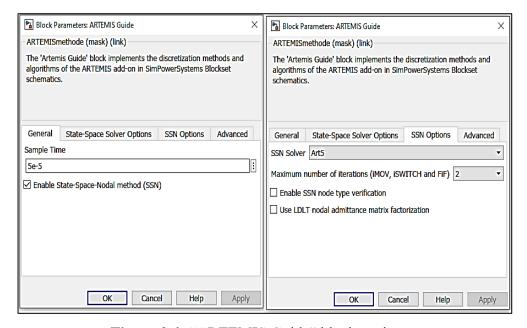

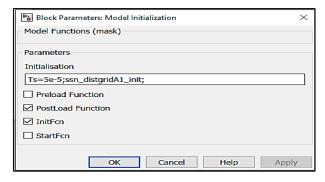

#### ii) Model Initialisation block:

In the "Model Initialisation" block we directly declare constants for example "Ts=5e-5", or we link the block with a ".m" file that contain list of declared constant. The MATLAB code file must be saved in the same location where the models is located and named same as in the "Model Initialisation" block. We should separate each constant or file name with a semicolon. Each time we set a parameter to "Ts" MATLAB assign the value of "5e-5" to that parameter and so on. **Figure 2.5** shows the block parameters used.

Figure 2.5: "Model Initialisation" block settings.

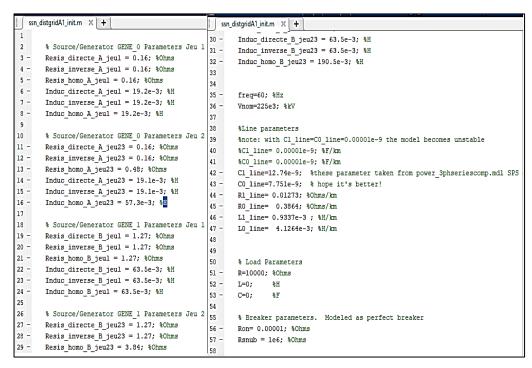

In this block "Ts" is set to "5e-5" and MATLAB code ".m" file named "ssn\_distgridA1\_init" is declared. This file is located in the model folder and named the same, it contains a list of constants and circuit parameters as shown in **Figure 2.6.**

Figure 2.6: "ssn distgridA1 init.m" file settings.

#### 2.2.4 Relay testing model computation subsystem:

The "SM\_NETWORK" computation block shown in **Figure 2.7** can be divided into six (6) parts:

- Power system circuit.

- Fault initiation circuit.

- Inputs/outputs card programming circuit.

- Voltages and Currents injection circuit.

- Trip and signals receiving circuit.

- Data acquisition circuit.

# i) Power system circuit:

The power system used in this simulation has two generators; one at each end and two loads with a transmission line that connects the substations where generators are located. This power system can be found in the RT-Lab Simulink model library named "ssn distributiongrid A1" with the system parameters shown in **Figure 2.6**.

The tested relay is connected at "Bus 2" with distance main protection to protect the transmission line between the two substations and supposed to trip the circuit breaker on the left.

#### ii) Fault initiation circuit:

The "Three-phase fault" block is used to simulate a fault (short circuit) between any phase and the ground. We can simulate any type of fault by selecting the right block. The switching time is set to "External" as shown in **Figure 2.8**, this allows the block to be triggered externally through an input signal. The fault block is controlled by the "SC\_RelayConsole" subsystem, therefore we should use an "OpComm" to establish communication between subsystems during simulation.

Figure 2.7: "Sm\_NETWORK" computation block: A) Power system circuit. B) Fault initiation circuit. C) Inputs/outputs card programming circuit.

D) Voltages and Currents injection circuit. E) Trip and signals receiving circuit. F) Data acquisition circuit.

Figure 2.8: "Three-phase fault" block settings for BC fault type.

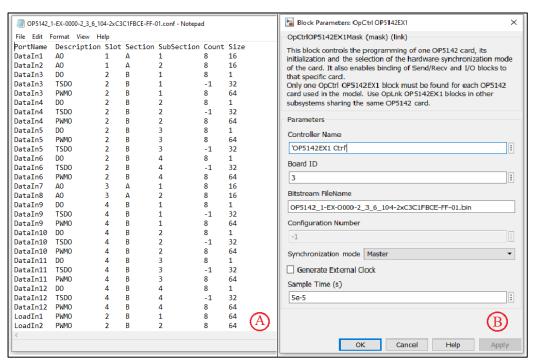

# iii) Inputs/outputs card programming circuit:

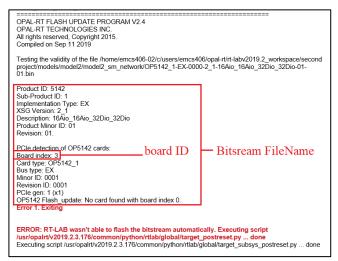

The OP5600 simulator has an OP5142 (**Appendix A**) card with 32 analog inputs, 32 analog outputs, 32 digital inputs and 32 digital outputs, this card needs to be programmed in the model. The RT-LAB I/O library contains a set of blocks for each card type, to configure and control the OP5142 card we must add an "OpCtrlOP5142EX1" block. In this block, "OP5142EX1 Ctrl" controller name was selected, later this name will be used to point input output blocks to this controller. The board ID and Bitstream FileName are manufacturer selected and can be found in the simulator files or can be extracted from simulator during build phase if using a wrong setting, the error shown in **Figure 2.9** will appear and the correct settings can be found in the error report.

**Figure 2.9:** Build error report with wrong board ID and Bitstream FileName settings.

The two files in **Figure 2.10** with ".bin" and ".conf" extensions and having the same name are provided with each card by manufacturer. These files must be copied to the location of the model, their name is used as Bitstream FileName in order to program the input and output cards.

Figure 2.10: ".bin" and ".conf" files.

The ".conf" file contains a table that defines each slot in the simulator's front panel, where its divided into four groups, each one has two sections A and B and each section has two subsections P1 and P2. **Figure 2.11A** shows ".conf" file configurations, settings of the "OpCtrlOP5142EX1" block are shown in **Figure 2.12B**.

**Figure 2.11:** A) ".conf" file configurations. B) "OpCtrlOP5142EX1" settings.

#### iv) Voltages and Currents injection circuit:

Voltages and currents calculated during simulation at "BUS1" are to be injected in the simulator's outputs. The values are too large to be injected from a digital simulator, hence we need to transform each value by a corresponding factor. Since the OP5600 simulator can output +/-16V so we need to map the reading of

currents and voltages to this range. Another limitation is that if the amplifier or low-level interface has a nominal value that should be token in consideration, or as in our case the conversion factors of the amplifier are preselected by manufacturer, then the amplifier can be considered as a step-up transformer with a fixed turns ratio. The solution for this problem is by adding a factor (gain) in the model to correct the total conversion factor of the equipment and a saturation block to make sure that the simulator cannot output any larger value than the selected one in this block. **Figure 2.7D** shows different parts of the circuit.

Calculation of the conversion factor takes in consideration the current transformer (CT) or voltage transformer (VT) ratios, amplifier factor and any other factor can be used in the circuit. Let's consider voltage case, Vp is the primary voltage of the system, PTR is the voltage transformer ratio, Vn/Vs is the amplifier ratio where Vn is the nominal input voltage. Hence, the saturation block must limit the voltage to Vn and the conversion factor CF can be calculated using the formula:

$$CF = \frac{Vs}{PTR \times Vn}$$

Eq.2.1

We use the "OpFcnOP5142EX1AnalogOut" block collected from the "RT-LAB®/I/O/Opal-RT => OP5142EX1" library to transmit to one OP5142 card the voltage values to be applied to the analog output channels. We set the controller name to "OP5142EX1 Ctrl" that is the name of the "OpCtrlOP5142EX1" controller and the Number of AOut channels to 8 out of 32 since we need three voltages and three currents, the other two additional outputs can be connected to a constant "0". And any other settings can be left as default. Once you select the analog output block and enter the proper controller name you can notice the slot info is changed from "Slot 0 Module X Subsection 0" to "Slot 1 Module A Subsection 1" if it is the first block, these information are obtained from ".conf" configurations file.

#### v) Trip and signals receiving circuit:

Once the relay detects a fault the outputs states change either to trip circuit breaker, trigger an alarm, or communicate with other relays. In order to complete the circuit to simulate real case, the simulator must receive the signals through the digital inputs to isolate the faulted part of the system. **Figure 2.7E** describe the tripping circuit of the breaker, an "OpFcnOP5142EX1AnalogIn" block collected from the "RT-LAB®/ I/O/ Opal-RT => OP5142EX1" library is used to return the trip signal to the circuit breaker. We set the controller name to "OP5142EX1 Ctrl" and the

number of Ain channels to 1 out of 32 since we have only one circuit breaker and no communication is configured in the relay. Once you select the analog output block and enter the proper controller name you can notice the slot info is changed from "Slot 0 Module X Subsection 0" to "Slot 1 Module B Subsection 1" if it is the first block, these information are obtained from "conf" configurations file.

# vi) Data acquisition circuit:

A great feature the OP5600 simulator can provide is saving any simulation signal during simulation without affecting the results. Opal RT-LAB simulators contain a hard drive to store the signals and results during simulation, and once the simulation ends it will be sent to the host computer in format ".m" MATLAB file.

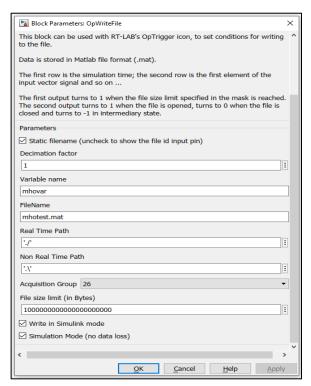

"OpWriteFile" block collected from RT-LAB library is used to save the input signals where the first row is the simulation time, the second row is the first input and so on. We set the FileName to any name followed by ".mat" extension (Name.mat), also we choose Variable name a that will appear in MATLAB workspace when opening the file. Select the Acquisition group to 26, select "Write in Simulink Mode", and set the file size name to any larger value in bytes according to the data stored and simulation time. **Figure 2.12** shows the configuration of the "OpWriteFile" block.

Figure 2.12: "OpWriteFile" block settings.

# 2.2.5 Relay testing model GUI subsystem:

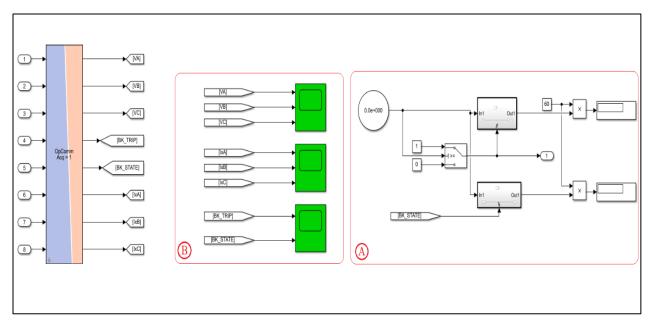

The "SC RelayConsole" shown in **Figure 2.13** can be divided into two parts:

- Fault timing control circuit.

- Graphical user interface circuit.

**Figure 2.13:** A) Fault timing control circuit. B) Graphical user interface circuit.

# i) Fault timing control circuit:

Faults can be delayed in order to simulate three states: prefault, fault and postfault states. These three states give a better experiment for testing relays. The two displays show the time in cycle when the fault start and when the breaker state has changed. In this manner we can notice the response time of the relay.

# ii) Graphical user interface circuit:

During simulation, simulator displays the "SC\_RelayConsole" subsystem on the host computer where you can follow the reading and plots of the different signals during the three states. In this experiment we used scopes to display signals. The "OpComm" block is used to establish communication between the two subsystems.

### 2.3 Implementing distance Mho function in Simulink model:

#### **2.3.1** Mho distance protection theory:

Distance mho protection function is one of the main protections used for transmission lines power system protection. With its impedance plot-based principle it can be implemented in a model to test relay's functionality with respect to theoretical result. This model can be added to the main model in an additional computation subsystem or it can be run in a separate model.

Distance mho function depends on the calculation of fault currents and voltages to find their respective impedance. The impedance is directly proportional to the length of wire, so according to the fault impedance we can deduce the relative fault location in distance units and this explains where the name comes from. It is used as a main or backup function.

Distance protection schemes are mainly designed to protect power system against two types of faults symmetrical and unsymmetrical faults. These two types can be further divided into Line-to-Ground, Line-to-Line-to-Ground, Line-to-Line and Three-Phase faults.

In general, distance protection schemes have six units of fault detection, three units for detection of faults between any two phases, while the other three units detects faults between any phase and ground. Different equations of fault detection are explained in **Table 2.1**. Settings of distance relay are always calculated on the basis of positive sequence impedance [13].

When a phase to ground fault occurs, the single line voltage at the fault location is zero. it would appear that the voltage at the relaying point is the product of the fault current and impedance, this is only true if earth resistance is zero. However, the fault current depends on the number of earthing points, the method of earthing and sequence impedances of the fault loop. [8][9][10] the voltage drop is the sum of the sequence voltage drops between the relaying point to the fault location. The voltage drop to the fault and current in the fault loop are:

$$VA = I1 \times Z1 + I2 \times Z2 + I0 \times Z0$$

Eq.2.2

$IA = I1 + I2 + I0$  Eq.2.3

$$IN = IA + IB + IC = 3I0$$

Eq.2.4

Where 1,2 and 0 are positive, negative and zero sequence components.

By considering Z1=Z2, a constant K where:  $K = \frac{Z0}{Z1}$  and replacing in Eq.2.2:  $VA = Z1\{IA + (IA + IB + IC) \times \frac{K-1}{3}\} = Z1\{IA + I0 \times k\}$  Eq.2.5

Where:  $k = \frac{K-1}{3}$

The impedance seen by the relay comparing IA and VA is:

$$ZR = \frac{VA}{IA} = \left(1 + \frac{K-1}{3}\right) \times Z1 = (1+k) \times Z1$$

Eq.2.6

From equation Eq.2.6 we can notice that the impedance is incorrect due to factor m. to find real value of fault impedance Zf we need to correct the currents and voltages entering relay, this is known as compensation. The compensated current for phase A is

$$IAcompensated = (IA + kI0)$$

Eq.2.7

Hence:

$$ZR = \frac{VA}{IA} = Z1$$

Eq.2.8

Table 2.1: Fault Impedance Calculation on different fault situations

| Faults            | Fault impedance equation |  |  |  |

|-------------------|--------------------------|--|--|--|

| Phase A – Ground  | ZA = VA / (IA + 3 k I0)  |  |  |  |

| Phase B – Ground  | ZB = VB / (IB + 3 k I0)  |  |  |  |

| Phase C – Ground  | ZC = VC / (IC + 3 k I0)  |  |  |  |

| Phase A – Phase B | ZAB = VAB / (IA - IB)    |  |  |  |

| Phase B – Phase C | ZBC = VBC / (IB - IC)    |  |  |  |

| Phase C – Phase A | ZCA = VCA / (IC - IA)    |  |  |  |

Where:

VA, VB, VC and IA, IB, IC are phase voltages and currents respectively.

VAB, VBC and VCA are phase to phase voltages.

k is the zero sequence or residual compensation factor.

I0 is zero sequence current.

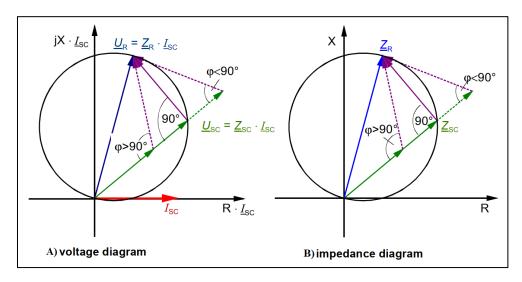

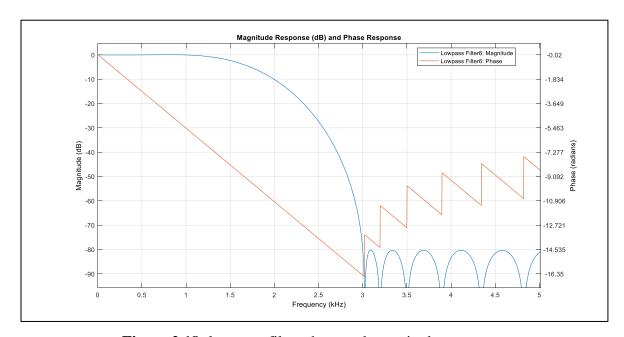

Mho distance scheme apply a circle on an R-X plane; where R-axis is the resistance axis and the X-axis is for reactance, that passes through the reference point with a reach in percentage of the line positive sequence impedance and polarized with its angle. If the fault impedance plot is inside the circle; also named zone, then the relay asserts a trip signal, otherwise the fault does not belong to that protected zone. Relay applies different zones in cascade and delayed to enhance protection scheme reliability and security. **Figure 2.14** shows mho circle diagram, where ZR is zone reach and Zsc short circuit or fault impedance point location on the R-X plane.

Figure 2.14: A) mho circle voltage diagram. B) mho circle impedance diagram.

It can be shown mathematically that the angle between the vector  $\overrightarrow{Zsc}$  and the vector  $(\overline{ZR}-\overline{Zsc})$  defines the location of the point Zsc with respect to the Mho circle, where  $\overrightarrow{Zsc}$  is defined by point Zsc and the plane reference and  $\overrightarrow{ZR}$  is defined by mho zone reach and angle. If  $\varphi > 90^\circ$  then point Zsc is inside the circle, if  $\varphi < 90^\circ$  then Zsc is outside the circle and if  $\varphi = 90^\circ$  then Zsc is on the circle. This logic can be implemented to simulate the mho protection scheme.

# 2.3.2 Mho model "SC\_NETWORK" computation subsystem:

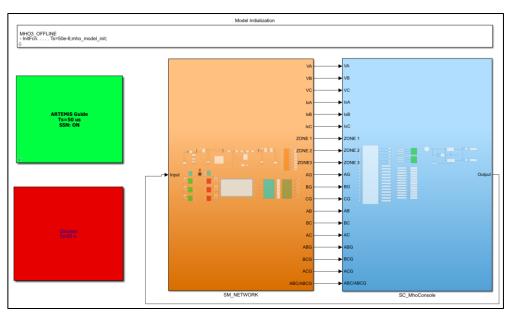

Top-level view of Mho model looks similar to any other RT-LAB model it may differ only in inputs and outputs or number of computation blocks and this is shown in **Figure 2.15**.

Figure 2.15: Mho model top-level view.

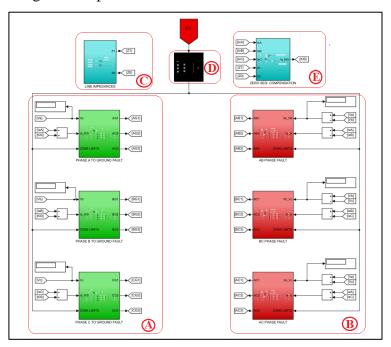

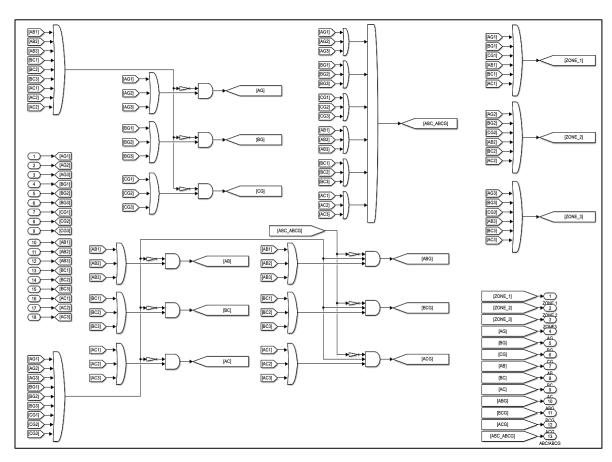

Mho model "SM\_NETWORK" computation subsystem shown in **Figure 2.16** applies the theoretical calculations for fault detections and type selection logic. The results are displayed on the "SC\_MhoConsole" GUI subsystem during simulation. The computation block can be divided into four (04) parts:

- Power system and fault initiation circuits.

- Harmonics removal and filters circuits.

- Fault detection circuit.

- Fault type and zone selection logic circuit.

# i) Power system and fault initiation circuits:

The power system in **Figure 2.16A** is similar to the one used in the previous section for relay testing. This power system can be found in the RT-Lab Simulink model library named "ssn\_distributiongrid\_A1" with the system parameters shown in **Figure 2.6**.

While the fault initiation is controlled by the "SC\_MhoConsole" subsystem and the fault type is select by "Three-phase fault" block.

#### ii) Harmonics removal and filters circuit:

When a fault occurs on a transmission line, currents and voltages are severely distorted due DC decaying components, presence of transient higher order frequencies. So, signals must be filtered to deal with fundamental frequency without affecting it. The filtering block is divided into three parts, Low pass filter, fundamental frequency extractor, and DC component remover.

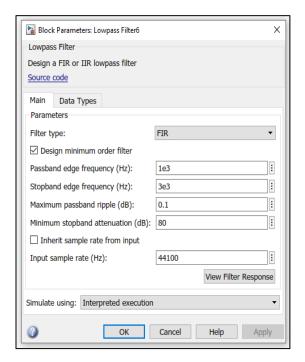

Higher frequency components can be eliminated using low pass filters, with appropriate cut-off frequency. In this experiment a low pass FIR filter is used with settings shown in **Figure 2.17**. the low pass filter response is shown in **Figure 2.18**.

After removal of higher order frequency, we need to extract the fundamental frequency from the lower order frequencies in the distorted signals. One of the best methods for extracting the fundamental frequency is using Fourier analysis. The "Fourier analysis" block can be found in Simulink library. We set the fundamental frequency to 60 Hz, harmonic numbers to 1, since the fundamental frequency is the only needed frequency and the sample time is set to the simulation sample time for discrete-time Fourier analysis. The settings are shown in **Figure 2.19**.

**Figure 2.16:** A) Power system and fault initiation circuits. B) Harmonics removal and filters circuits. C) Fault detection circuit. D) Fault type selection logic circuit.

Figure 2.17: low pass filter settings.

**Figure 2.19:** Fourier analysis block settings.

**Figure 2.18:** low pass filter phase and magnitude response.

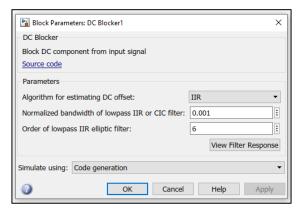

Discrete Fourier Transform (DFT) has immunityfrom harmonic components and has a relatively fast response time for the fundamental component calculation. However, the DFT is not immune from the DC component, the decaying DC component in the fault current can cause undesirable oscillations in the DFT results. To eliminate the DC components we need another stage of filtering, the "DC Blocker" block collected from Simulink library is used to eleminate decaying dc component. The IIR algorithm is set to remove DC offset with a normalized bandwidth of 0.001 and the order of the lowpass IIR eliptic filter is set to 6 as shown in **Figure 2.20**.

Figure 2.20: "DC blocker" block settings.

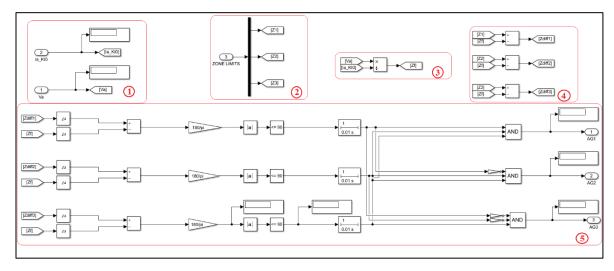

#### iii) Fault detection circuit:

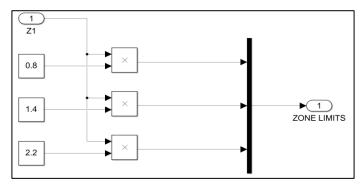

The theory discussed before in the previous section is now applied, six blocks or subsystems, with one for each equation in **Table 2.1**. each block is configured to three zone Mho distance protection, it can be expanded to any n number of zones by simply adding their respective zone reach limits.

Figure 2.21: Fault detection circuit.

In **Figure 2.21** block A contains subsystems for single line to ground fault detection of the three phases. The three blocks are similar since the equations are the same, while they differ only in the phase voltage and compensated current inputs. Each one of the blocks applies one of the equations from **Table 2.1**. the circuit is shown in **Figure 2.22**.

Figure 2.22: Phase A to ground fault detection circuit.

Circuit in **Figure 2.22** can be divided into five parts, part 1 contain input voltage and compensated current. Part 2 inputs the three zones reach or limits. Part 3 calculates the fault impedance seen from the relaying point and using the corresponding equation. Part 4 calculate the vector  $(\overline{ZR-Zsc})$  angle and magnitude as a complex number. While part 5 decides to which zone the fault corresponds. One can notice that if the fault is in zone 1, all higher reach zones will detect the fault. So, in order to select the proper zone, an "AND" gate logic circuit will detect the faulted zone, if the fault is in zone 2 all higher reach zones than zone 2 will detect the fault and any lower reach zones must not detect the fault, hence we can conclude that the fault belongs to zone 2.

Block B (in **Figure 2.21**) contains subsystems for double line fault detection of any two of the three phases. Each subsystem is divided into five parts as in **Figure 2.22**. The difference between the blocks in A and B is in the input voltages and currents. Block B input voltages are line to line voltages, while current are uncompensated phase currents. The same faulted zones detection logic applies.

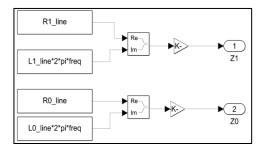

In Block C (in **Figure 2.21**) we declare positive and zero sequence impedances as shown in **Figure 2.23**. since settings of transmission line shown in **Figure 2.6** are in Ohms per Km so we need to multiply the impedances by line length.

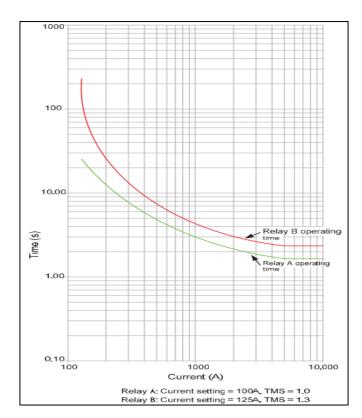

**Figure 2.23:** positive and zero sequence impedances calculation.