### People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

University M'Hamed BOUGARA – Boumerdès

### **Institute of Electrical and Electronic Engineering**

### **Department of Electronics**

Final Year Project Report Presented in Partial Fulfilment of the Requirements for the Degree of

### 'Master'

In Electronics

**Option: Computer Engineering**

Title:

## Hardware/Software Codesign of Real Time Obstacle Detection System using Stereovision

Presented by:

**BENDAHMANE** Meryem

Supervisor:

Pr. KHOUAS Abdelhakim

Registration Number:...../2022

### Abstract

Obstacle detection and localization are crucial abilities for a mobile robot to navigate in an environment. Therefore, a highly developed environment perception system is necessary. Systems based on stereo vision are strongly recommended due to their high resolution, relatively wide range of measurement, and low cost. Such systems generate a disparity map from two stereo images (left and right), the generation process and disparity map quality depend on the stereo matching technique. In this project, we built a software system for a real-time obstacle detection using stereo vision. For the stereo vision module, we used the RANK non-parametric transformation and the Sum of Absolute Differences (SAD) correlation matric to estimate the disparity between the two images, the obstacle detection phase was carried forward using the U-V disparity approach. This approach makes use of the disparity map to build the V-disparity and U-disparity maps, from which obstacles can be easily localized after extracting vertical and horizontal lines from the maps respectively. The software design processes 240×320 pixels images at a rate of 1/3 fps, with a single thread Central Processing Unit (CPU) rate of 667 MHz and a Double Data Rate (DDR) memory running at a frequency of 533 MHz, this result reveals the inefficiency of our system for real-time applications. To overcome this limitation, we involved the hardware/software codesign methodology, where the system is split into hardware and software partitions. The choice of the best partitioning depends on the characteristics required to be present at the final system implementation. For our project, the speed was the main factor to meet the real-time application requirements. In order to get a better partitioning, we used profiling tools to determine the most time-consuming functions in our software system. The profiling shows that the stereo vision module consumes 90% of the total execution time, as a result, we replaced the stereo vision module in our application by a hardware stereo vision module. The software/hardware codesign solution built with the same software characteristics and a hardware stereo vision module running at 7.8 MHz led to a huge improvement in the system's speed, for  $240 \times 320$  pixels images the processing rate reaches 78 fps achieving a 234 times acceleration from the original software design.

## **Dedication**

To my dearest parents

For their endless love, support, and encouragement

To my grandmother and my aunts

Malika, Fazia, Nassira, and Fatma

To my dear cousins

Imene, Lina, and Anais

To my second family

Khawla BOUSSAAD and Farah TAHRI

To special people I had the pleasure of meeting during my years in college

Sara ALILAT, Meriem CHAIB, hadjar HAMDI, and Mohamed Amine TAIB

Thanks for being a part of my journey and making it so special and beautiful.

### Acknowledgement

First and foremost, I would like to praise and thank God, the Almighty, who has granted countless blessing, knowledge, and opportunity to the writer, so that I have been finally able to accomplish the thesis.

I would like to express my deepest appreciation to my primary supervisor Pr. Abdelhakim KHOUAS for his support, guidance, and for allowing me to duly embrace this project under his auspices despite his busy agenda. I am thankful for his confidence and the freedom he gave me throughout the course of this work. In addition, I would like to acknowledge Mr. Taki Eddine SAIDI who has been an ideal mentor. No acknowledgment would be complete without expressing my gratitude to my colleague Karim Yahia for the help and support he has provided.

I am grateful to the members of the jury for taking the time to read and analyze this project report.

My warmest thanks go to the teachers of IGEE for the devotion they have shown and the knowledge they have passed to me.

# **Table of content**

| Abstrac   | t      |                                              | . I |

|-----------|--------|----------------------------------------------|-----|

| Dedicat   | ion    |                                              | II  |

| Acknow    | vledg  | ement                                        | III |

| Table of  | f cont | tentl                                        | [V  |

| List of I | Figure | es                                           | VI  |

| List of 7 | Fable  | sV                                           | III |

| List of A | Abbre  | eviationsl                                   | IX  |

| General   | Intro  | oduction                                     | 1   |

| Chapter   | I: Ol  | bstacle detection using stereo-vision        | 1   |

| I.1       | Intr   | oduction                                     | 3   |

| I.2       | Ster   | eo vision geometry                           | 3   |

| I.2.      | 1      | Pinhole camera model                         | 3   |

| I.2.      | 2      | Camera model with lens                       | 5   |

| I.2.      | 3      | Camera calibration                           | 6   |

| I.2.      | 4      | Epipolar geometry                            | 7   |

| I.2.      | 5      | Image un-distortion and stereo rectification | 7   |

| I.3       | Dep    | oth estimation                               | 8   |

| I.4       | Ster   | eo correspondence                            | 9   |

| I.4.      | 1      | Feature based algorithms                     | 10  |

| I.4.      | 2      | Correlation based algorithms                 | 10  |

| I.5       | Dor    | nain of U-V disparity                        | 12  |

| I.6       | 3D     | planes projection in U-V-disparity           | 14  |

| I.6.      | 1      | U and V disparity maps generation            | 15  |

| I.6.      | 2      | Obstacles detection using UV disparity maps  | 15  |

| I.7       | Sun    | nmary                                        | 16  |

| Chapter   | II: O  | Obstacle detection system design             | 17  |

| II.1      | Intr   | oduction                                     | 17  |

| II.2      | Ove    | erview of the obstacle detection system      | 17  |

| II.3      | Obs    | stacle detection system design               | 18  |

| II.3      | 8.1    | RANK transform                               | 18  |

| II.3      | 3.2    | SAD correlation                              | 19  |

| II.3      | 3.3    | UDM and VDM generation                       | 21  |

| II.3      | 8.4    | Vertical and horizontal lines extraction     | 22  |

| II.3.5                                                                                       | Obstacle detection                                                                                                                                                                                                                                                                                      | 24                                                             |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Chapter I                                                                                    | II: Software implementation and experimental results                                                                                                                                                                                                                                                    |                                                                |

| III.1                                                                                        | Introduction                                                                                                                                                                                                                                                                                            | 26                                                             |

| III.2                                                                                        | Development tools                                                                                                                                                                                                                                                                                       | 26                                                             |

| III.2.                                                                                       | 1 Software and hardware environments                                                                                                                                                                                                                                                                    | 26                                                             |

| III.2.                                                                                       | 2 Zynq Evaluation and Development board (Zedboard)                                                                                                                                                                                                                                                      | 26                                                             |

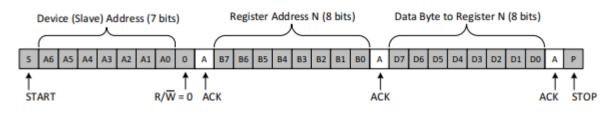

| III.2.                                                                                       | 3 Inter-Integrated Circuit (IIC) protocol                                                                                                                                                                                                                                                               | 27                                                             |

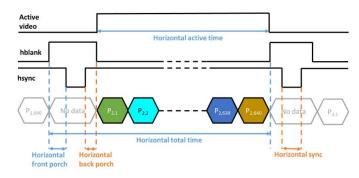

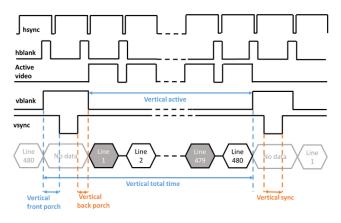

| III.2.                                                                                       | 4 Video signals and timing                                                                                                                                                                                                                                                                              |                                                                |

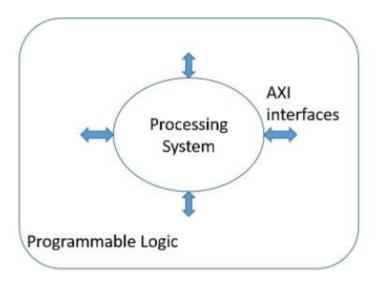

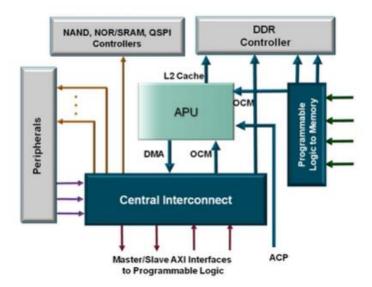

| III.3                                                                                        | Zynq architecture                                                                                                                                                                                                                                                                                       | 29                                                             |

| III.3.                                                                                       | 1 Zynq Processing system (PS)                                                                                                                                                                                                                                                                           |                                                                |

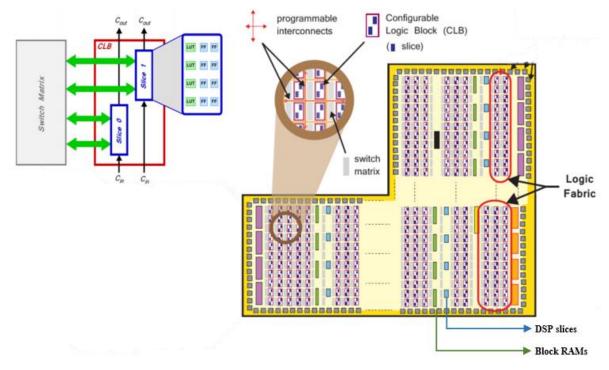

| III.3.                                                                                       | 2 Zynq Programmable logic (PL)                                                                                                                                                                                                                                                                          |                                                                |

| III.3.                                                                                       | 3 Advanced eXtensible Interface (AXI) protocol                                                                                                                                                                                                                                                          | 31                                                             |

| III.4                                                                                        | mplementation of obstacle detection system                                                                                                                                                                                                                                                              | 32                                                             |

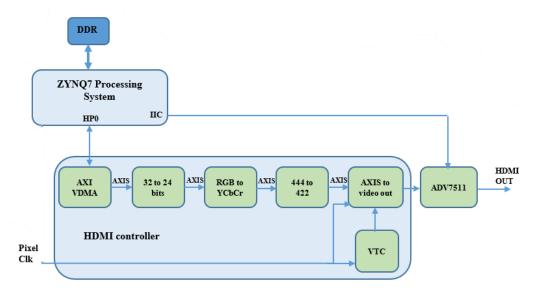

| III.4.                                                                                       | 1 HDMI controller implementation                                                                                                                                                                                                                                                                        | 32                                                             |

| III.4.                                                                                       | 2 Software implementaion of obstacle detection system                                                                                                                                                                                                                                                   | 40                                                             |

| III.5                                                                                        | Experimental results                                                                                                                                                                                                                                                                                    | 15                                                             |

|                                                                                              |                                                                                                                                                                                                                                                                                                         | ·····+J                                                        |

| III.5.                                                                                       | -                                                                                                                                                                                                                                                                                                       |                                                                |

| III.5.<br>III.5.                                                                             | 1 Experimental results of the stereo vision module                                                                                                                                                                                                                                                      | 45                                                             |

| III.5.                                                                                       | 1 Experimental results of the stereo vision module                                                                                                                                                                                                                                                      | 45<br>47                                                       |

| III.5.<br>III.6                                                                              | <ol> <li>Experimental results of the stereo vision module</li> <li>Experimental results of the obstacle detection system</li> </ol>                                                                                                                                                                     | 45<br>47<br>50                                                 |

| III.5.<br>III.6<br>Chapter I                                                                 | <ol> <li>Experimental results of the stereo vision module</li> <li>Experimental results of the obstacle detection system</li> <li>Conclusion</li> </ol>                                                                                                                                                 | 45<br>47<br>50<br>51                                           |

| III.5.<br>III.6<br>Chapter I<br>IV.1                                                         | <ol> <li>Experimental results of the stereo vision module</li> <li>Experimental results of the obstacle detection system</li> <li>Conclusion</li> <li>V: Hardware/Software implementation of obstacle detection system</li> </ol>                                                                       | 45<br>47<br>50<br>51<br>51                                     |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2                                                 | <ol> <li>Experimental results of the stereo vision module</li> <li>Experimental results of the obstacle detection system</li> <li>Conclusion</li> <li>V: Hardware/Software implementation of obstacle detection system</li> </ol>                                                                       | 45<br>47<br>50<br>51<br>51                                     |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3                                         | <ol> <li>Experimental results of the stereo vision module</li> <li>Experimental results of the obstacle detection system</li> <li>Conclusion</li> <li>V: Hardware/Software implementation of obstacle detection system</li> <li>Introduction</li> <li>Hardware/Software codesign methodology</li> </ol> |                                                                |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3                                         | <ol> <li>Experimental results of the stereo vision module</li></ol>                                                                                                                                                                                                                                     |                                                                |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3<br>IV.4                                 | <ol> <li>Experimental results of the stereo vision module</li></ol>                                                                                                                                                                                                                                     |                                                                |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3<br>IV.4<br>IV.4                         | <ol> <li>Experimental results of the stereo vision module</li></ol>                                                                                                                                                                                                                                     |                                                                |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3<br>IV.4<br>IV.4<br>IV.4<br>IV.5         | <ol> <li>Experimental results of the stereo vision module</li></ol>                                                                                                                                                                                                                                     | 45<br>47<br>50<br>51<br>51<br>51<br>51<br>52<br>53<br>53<br>55 |

| III.5.<br>III.6<br>Chapter I<br>IV.1<br>IV.2<br>IV.3<br>IV.4<br>IV.4<br>IV.4<br>IV.5<br>IV.6 | <ol> <li>Experimental results of the stereo vision module</li></ol>                                                                                                                                                                                                                                     |                                                                |

# **List of Figures**

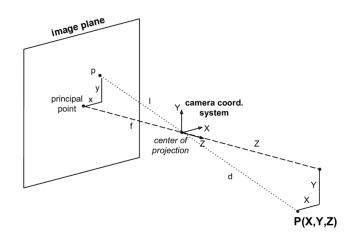

| Figure I.1: Pinhole camera model [3]                                                               | 4        |

|----------------------------------------------------------------------------------------------------|----------|

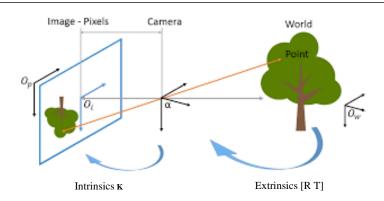

| Figure I.2: Representation of the extrinsic and intrinsic parameters [6]                           | 5        |

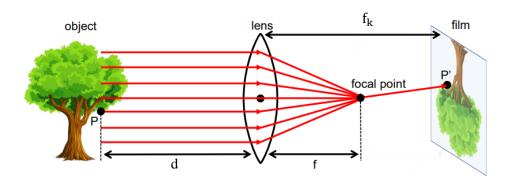

| Figure I.3: light-rays projection through a lens [7].                                              | 6        |

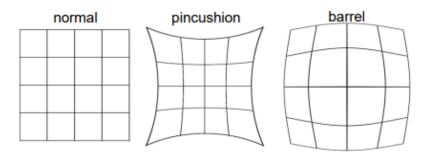

| Figure I.4: Lens distortion effect on image geometry [7].                                          | 6        |

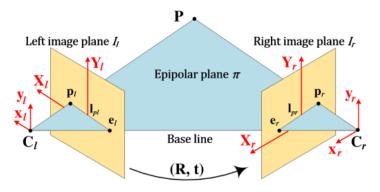

| Figure I.5: Epipolar geometry [9].                                                                 | 7        |

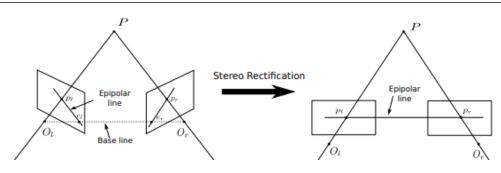

| Figure I.6: Stereo rectification effect [11]                                                       | 8        |

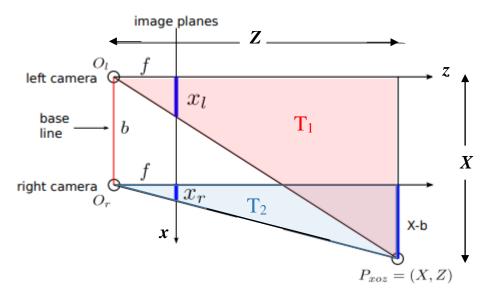

| Figure I.7: 3D triangulation between two parallel, identical cameras [11]                          | 8        |

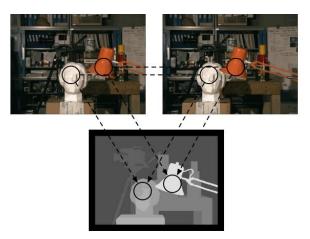

| Figure I.8: Correspondence problem and DM estimation [1].                                          |          |

| Figure I.9: Stereo matching procedures [19]                                                        | 10       |

| Figure I.10: Rank transformation using 3*3 window.                                                 | 11       |

| Figure I.11: Census transformation using 3*3 window                                                | 12       |

| Figure I.12: Hamming Distance principle                                                            | 12       |

| Figure I.13: Stereo vision setup in the world coordinate system [22]                               | 12       |

| Figure I.14: The different plans in WCS [22].                                                      |          |

| Figure I.15: U-V disparity maps generation [21].                                                   | 15       |

| Figure I.16: Obstacle detection using UV disparity. (a) DM. (b) UDM. (c) VDM                       | 16       |

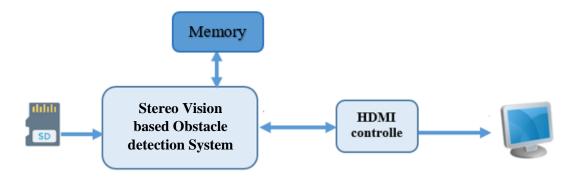

| Figure II.1: Global design of obstacle detection system                                            | 17       |

| Figure II.2: Stereovision-based obstacle detection system design                                   | 18       |

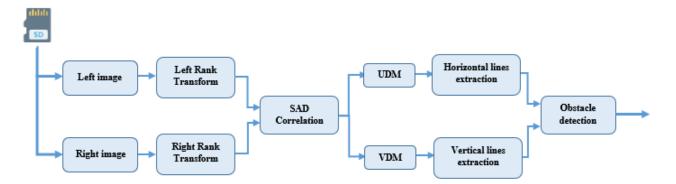

| Figure II.3: Size change in the Rank transform image compared to original image, (a) the original  | inal     |

| image I of size 12×11 pixels, (b) image of rank transform R of size 8×7 pixels using 5*5 wind      | low.     |

|                                                                                                    | 19       |

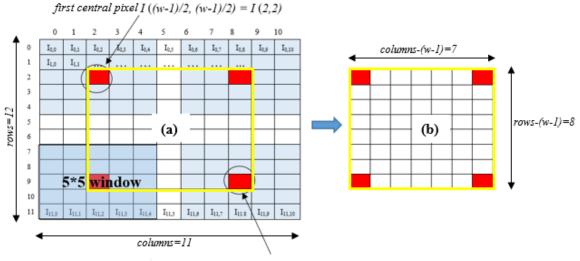

| Figure II.4: Matching cost using SAD of 5*5 window                                                 | 20       |

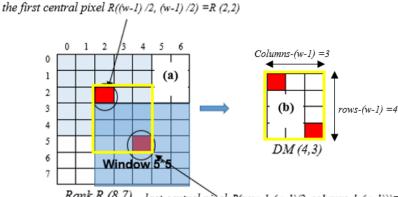

| Figure II.5: Size change in the DM compared to Rank transform image using 5*5 window               | 21       |

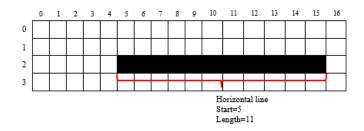

| Figure II.6: Vertical line in VDM array example                                                    | 23       |

| Figure II.7: Horizontal line in UDM array example.                                                 | 24       |

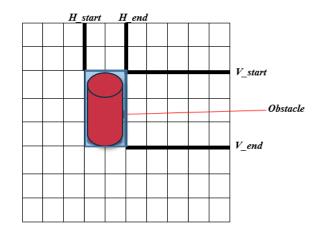

| Figure II.8: Example of obstacle boundaries                                                        | 25       |

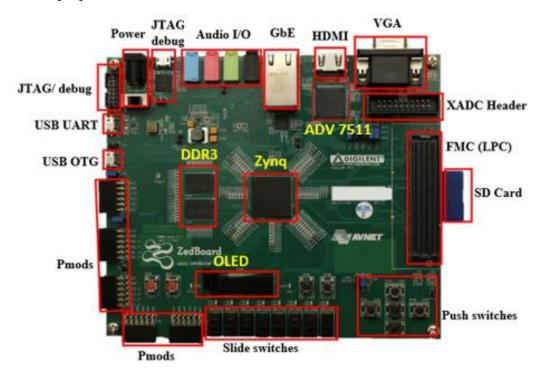

| Figure III.1: Zedboard development board interfaces                                                | 27       |

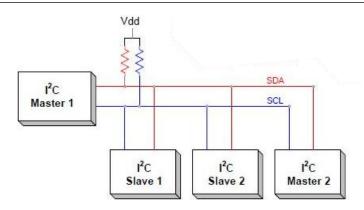

| Figure III.2: Typical I2C protocol bus [27]                                                        |          |

| Figure III.3: I2C write to slave device process [28]                                               |          |

| Figure III.4: Horizontal video timing of second line [29]                                          |          |

| Figure III.5: Vertical video timing [29].                                                          | 29       |

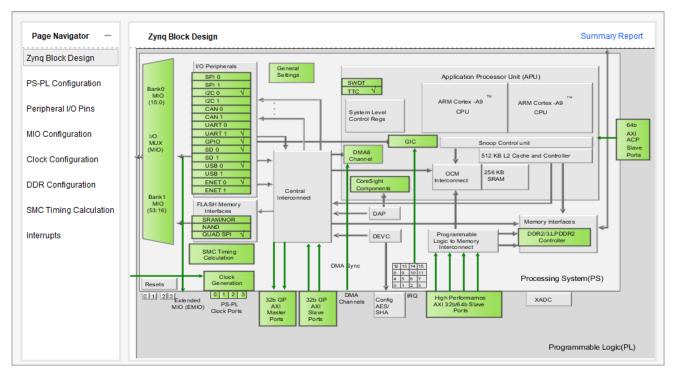

| Figure III.6: Zynq overall view [26].                                                              | 29       |

| Figure III.7: Zynq Processing System architecture [30].                                            | 30       |

| Figure III.8: Arrangement of Zynq PL basic resources [32]                                          | 31       |

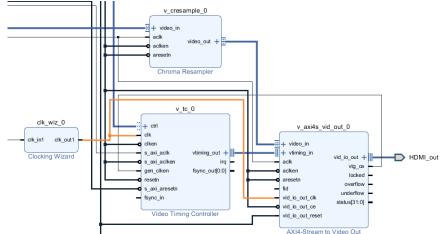

| Figure III.9: Global block diagram of the HDMI Controller.                                         |          |

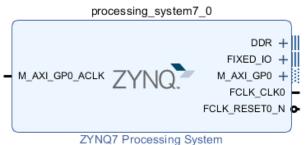

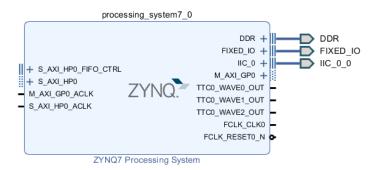

| Figure III.10: Default Zynq SoC PS IP Block.                                                       | 33       |

| Figure III.11: Re-customize IP Dialog Box.                                                         | 33       |

| Figure III.12: Customized Zynq SoC PS IP Block.                                                    |          |

| Figure III.13: Configuration of FCLK_clk0.                                                         | 34       |

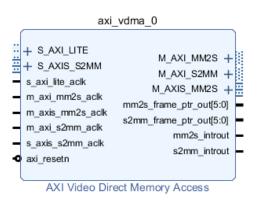

| Figure III.14: AXI VDMA IP core                                                                    |          |

|                                                                                                    | 34       |

| Figure III.15: AXI VDMA configuration.                                                             |          |

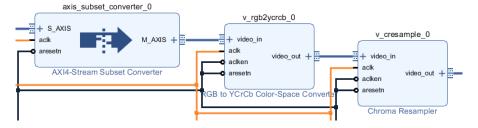

| Figure III.15: AXI VDMA configuration<br>Figure III.16: AXI4 Stream subset converter configuration | 35       |

|                                                                                                    | 35<br>35 |

| Figure III.19: Memory mapping of AXI slaves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

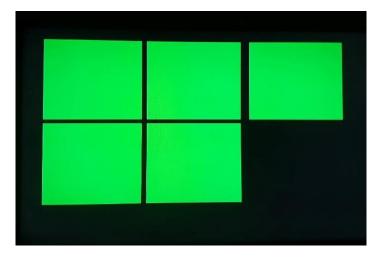

| Figure III.20: HDMI controller test result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

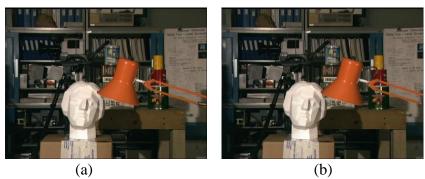

| Figure III.21: Tsukuba stereo images from the Middlebury StereoVision data base,(a) right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| image, (b) left image [34]40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

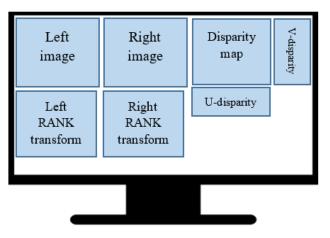

| Figure III.22: Selected regions in frame buffer to display results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

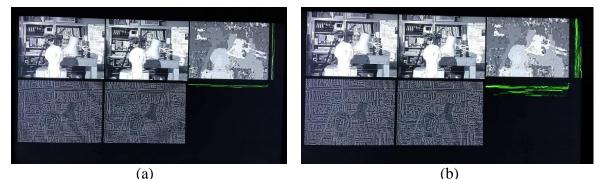

| Figure III.23: HDMI display (a) U-V DM without scaling, (b) U-V DM with scaling42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

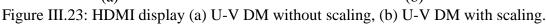

| Figure III.24: HDMI display using noise removal for the UDM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

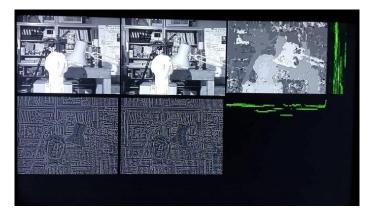

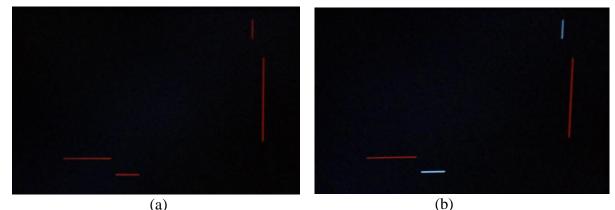

| Figure III.25: (a) Matlab code to reconstruct test VDM sample with 2 lines, (b) the VDM sample.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure III.26: Vertical lines extracted from the VDM sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure III.27:(a) Matlab code to reconstruct test UDM sample with 2 lines, (b) the UDM sample.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure III.28: Horizontal lines extracted from the UDM sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure III.29: Horizontal and Vertical valid lines extracted using the algorithm,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

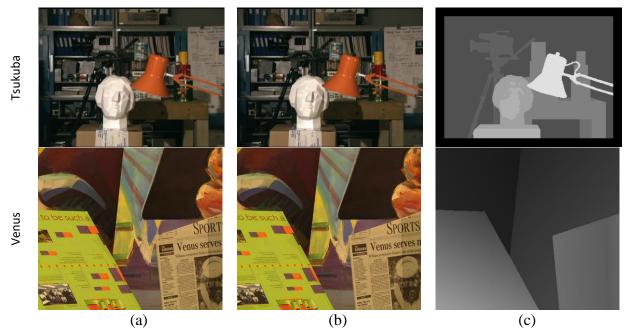

| Figure III.30: Middlebury stereo vision dataset: (a) left images, (b) right images, (c) ground-truth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

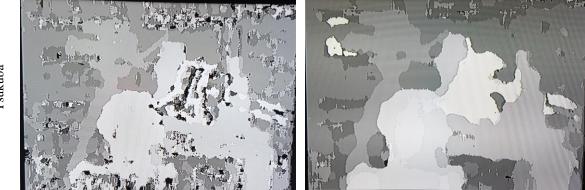

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

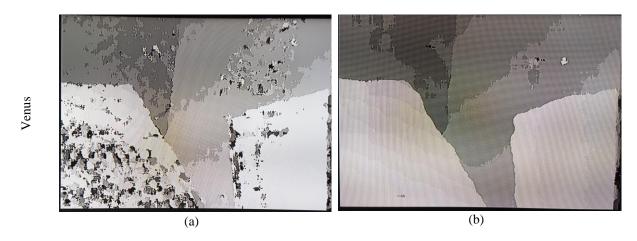

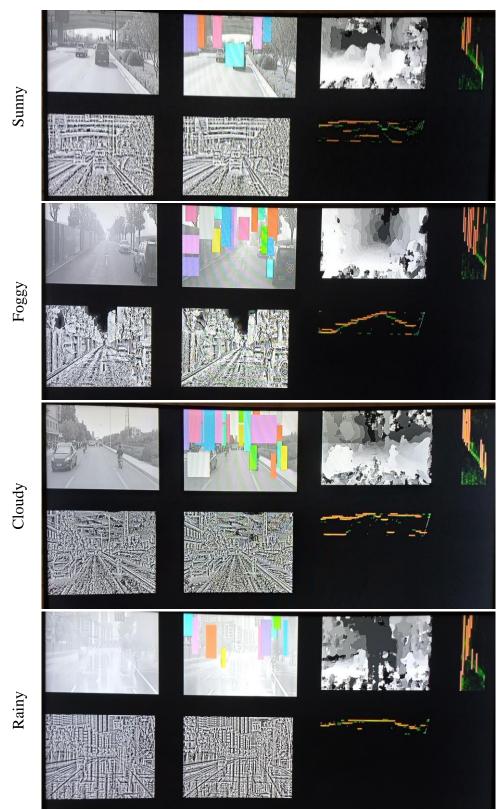

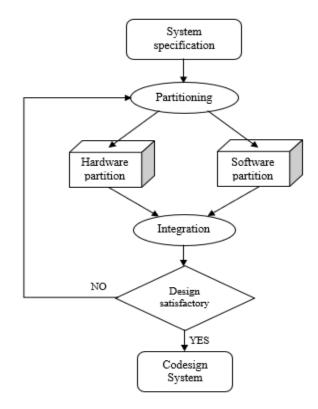

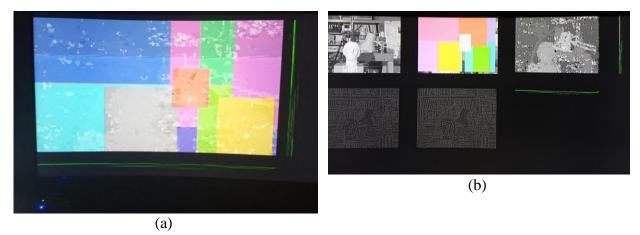

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with         smaller BMP percentage.       47         Figure III.32: Selected stereo pairs from DrivingStereo dataset.       47         Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset48       47         Figure III.34: Obstacle detection system profiling.       49         Figure IV.1: Basic flow of codesign methodology.       51                                                                                                                                                                                                                                              |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

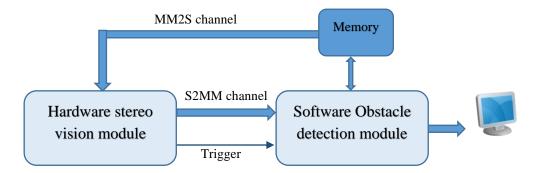

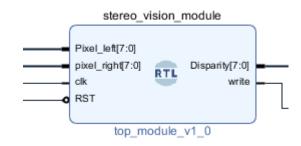

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM withsmaller BMP percentage.47Figure III.32: Selected stereo pairs from DrivingStereo dataset.47Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset48Figure III.34: Obstacle detection system profiling.49Figure IV.1: Basic flow of codesign methodology.51Figure IV.2:Global codesign of obstacle detection system.52Figure IV.3: Hardware stereo vision module block.                                                                                                                                                                                                                    |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM with<br>smaller BMP percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM withsmaller BMP percentage.47Figure III.32: Selected stereo pairs from DrivingStereo dataset.47Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset48Figure III.34: Obstacle detection system profiling.49Figure IV.1: Basic flow of codesign methodology.51Figure IV.2:Global codesign of obstacle detection system.52Figure IV.3: Hardware stereo vision module block.                                                                                                                                                                                                                    |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM withsmaller BMP percentage.47Figure III.32: Selected stereo pairs from DrivingStereo dataset.47Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset48Figure III.34: Obstacle detection system profiling.49Figure IV.1: Basic flow of codesign methodology.51Figure IV.2:Global codesign of obstacle detection system.52Figure IV.3: Hardware stereo vision module block.53Figure IV.4: AXI DMA configuration.                                                                                                                                                                               |

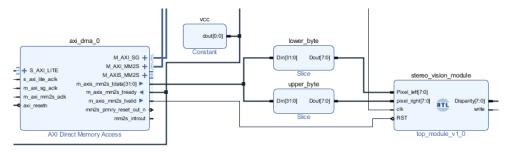

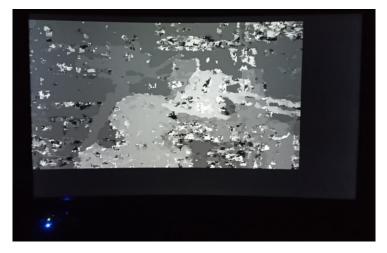

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM withsmaller BMP percentage.47Figure III.32: Selected stereo pairs from DrivingStereo dataset.47Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset4849Figure III.34: Obstacle detection system profiling.49Figure IV.1: Basic flow of codesign methodology.51Figure IV.2:Global codesign of obstacle detection system.52Figure IV.3: Hardware stereo vision module block.53Figure IV.4: AXI DMA configuration.54Figure IV.5:AXI DMA and stereo vision module connection.54Figure IV.6: DM generated by the hardware stereo vision module.56Figure IV.7: ILA results before optimization.56 |

| Figure III.31: Estimated DM, (a) worst DM with higher BMP percentage, (b) best DM withsmaller BMP percentage.47Figure III.32: Selected stereo pairs from DrivingStereo dataset.47Figure III.33: Obstacle detection system results using stereo pairs from DrivingStereo dataset4849Figure III.34: Obstacle detection system profiling.49Figure IV.1: Basic flow of codesign methodology.51Figure IV.2:Global codesign of obstacle detection system.52Figure IV.3: Hardware stereo vision module block.53Figure IV.4: AXI DMA configuration.54Figure IV.5:AXI DMA and stereo vision module connection.54Figure IV.6: DM generated by the hardware stereo vision module.56                                                |

# **List of Tables**

| Table I.1: Projection characteristics of different planes in the U-V disparity map   | 14            |

|--------------------------------------------------------------------------------------|---------------|

| Table III.1: The PL resources per Zynq device type [33].                             | 31            |

| Table III.2: Evaluation results using the percentage BMP measure                     | 46            |

| Table III.3: Execution time of the obstacle detection system using images of size 24 | 0×320 pixels. |

|                                                                                      | 49            |

| Table IV.1: PL resource percentage usage of software design and codesign             | 58            |

# List of Abbreviations

| 2-D            | Two Dimensions                            |

|----------------|-------------------------------------------|

| 2-D<br>3-D     | Three Dimensions                          |

| ACK            | Acknowledgement                           |

| AMBA           | Advanced Microcontroller Bus Architecture |

| ANDA<br>AP SoC |                                           |

| AP SOC<br>APU  | All Programmable System On Chip           |

| -              | Application processor unit                |

| AXI            | Advanced eXtensible Interface             |

| AXIS           | Advanced eXtensible Interface Stream      |

| BMP            | Bad Matched Pixels                        |

| BOM            | Bills Of Material                         |

| BSP            | Board Support Package                     |

| CDT            | C/C++ Development Toolkit                 |

| CLB            | Configurable Logic Blocks                 |

| COE            | Coefficient                               |

| CPU            | Central Processing Unit                   |

| DDR            | Double Data Rate                          |

| DM             | Disparity Map                             |

| DMA            | Direct Memory Access                      |

| DSP            | Digital Signal Processor                  |

| FF             | Flip-Flop                                 |

| FIFO           | First In First Out                        |

| FPGA           | Field Programmable Gate Array             |

| FPU            | floating Point Unit                       |

| GDB            | Gnu DeBugger                              |

| GIC            | General Interrupt Controller              |

| GUI            | Graphical User Interface                  |

| HD             | Hamming Distance                          |

| HDL            | Hardware Description Language             |

| HDMI           | High-Definition Multimedia Interface      |

| HLS            | High-Level Synthesis                      |

| HP             | High-Performance                          |

| I2S            | Inter Integrated Circuit Sound            |

| IDE            | Integrated Development Environment        |

| IIC            | Inter-Integrated Circuit                  |

| ILA            | Integrated Logic Analyzer                 |

| IOP            | Input/ Output peripherals                 |

| IP             | Intellectual property                     |

| JTAG           | Joint Test Action Group                   |

| LPDDR          | Low Power Double Data Rate                |

| LRF            | Laser Range Finder                        |

| LUT            | Look Up Table                             |

| Matlab         | Matrix Laboratory                         |

| MM2S           | Memory Mapped to stream                   |

| MMU            | Memory Management Unit                    |

| OCM            | On Chip Memory                            |

| OLED           | Organic Light Emitting Diodes             |

|                | Open-source Computer Vision               |

| Opencv<br>PCB  | Printed Circuit Board                     |

| rud            | Finned Circuit Doard                      |

| PL       | Programmable Logic                    |

|----------|---------------------------------------|

| PS       | Processing System                     |

| RAM      | Random Access Memory                  |

| RGB      | Red Green Blue                        |

| ROM      | Read Only Memory                      |

| RTS      | Real Time System                      |

| S2MM     | Stream to Memory Mapped               |

| SAD      | Sum of Absolute Differences           |

| SCL      | Serial Clock                          |

| SD card  | Secure Digital card                   |

| SDA      | Serial Data                           |

| SDK      | Software Development Kit              |

| SPDIF    | Sony/Philips Digital Interface        |

| SRL16    | 16-bit Shift Registers                |

| SRL32    | 32-bit Shift Registers                |

| SSD      | Sum of Squared Differences            |

| SWDT     | System Watchdog Timer                 |

| TCF      | Target Communication Framework        |

| TCL      | Tool Command Language                 |

| TTC      | Triple Timer Controller               |

| UDM      | U Disparity Map                       |

| VDM      | V Disparity Map                       |

| VDMA     | Video Direct Memory Access            |

| VTC      | Video Timing Controller               |

| WTA      | Winner Take All                       |

| ZEDBoard | Zynq Evaluation and Development board |

## **General Introduction**

Out of the five senses, vision is undoubtedly the one that humans have come to depend upon above all others, and indeed the one that provides most of the data received. The main feature of the human visual system is the ease and immediate with which interpretation of a scene is carried out, within a fraction of a second. In the present day and age, scientists are trying to get machines to do much of his work. For simple mechanistic application, this is not particularly difficult, but for more complex tasks such as real-time applications and autonomous systems, the machine must be given a sense of vision.

Computer vision is the automated extraction of information from images. Information can mean anything from three-dimensional (3D) models, camera position, object detection and recognition to grouping and searching image content. Sometimes, computer vision aims to mimic the human visual system through stereo vision using one or more cameras set up, where the 3D information is extracted from two or more images taken from different viewpoints. This problem of extracting useful information from images or videos finds application in a variety of fields such as autonomous navigation, obstacle detection and avoidance, remote sensing, etc.

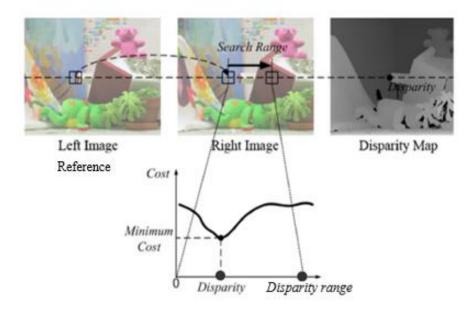

A stereo vision system estimates disparity or the difference in the position of the pixel of a corresponding location in the camera view by finding similarities in the left and right image, which is known as the stereo correspondence. There have been various costs governing the extent of the similarity. Some of them are Sum of Absolute Differences (SAD), Sum of Squared Differences (SSD), which are window-based local approaches where the cost value of a particular window in the left image is compared to the right image window by spanning it along a horizontal axis for a disparity range. Based on the metric measures' disparity selection is mostly performed in the Winner-Takes-All (WTA) strategy, i.e., the disparity with the lowest measurement is chosen. By performing the same process for all pixels, a Disparity Map (DM) is generated, from which the depth can be easily calculated.

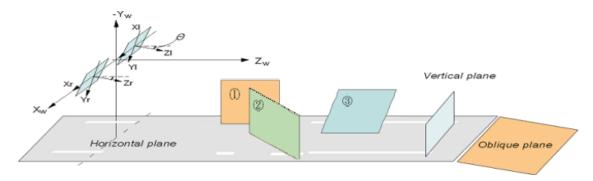

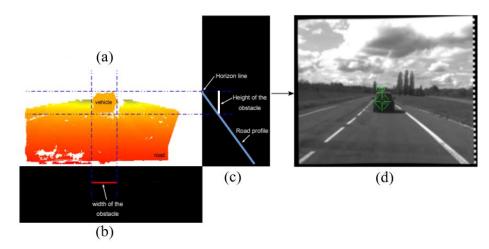

A key part of the construction of a world model is the incorporation of obstacles, to help machines to interact with their environment efficiently, in the stereo vision case, this can be achieved by building the U-V Disparity Maps (UDM and VDM) upon a given DM. the UDM can be considered as a top view of the perceived scene, whereas the VDM is a lateral view of the scene such that the road plane is represented by an oblique line, the obstacles as vertical alignments in VDM, and horizontal alignments in UDM. The VDM is obtained by computing a histogram of each row of the DM, while the UDM is generated by computing a histogram of each column of the DM.

An obstacle detection system based on stereo vision requires a great processing performance in order to accept more data, process all that data, and make an appropriate response, and what is mainly challenging in such systems is that all the processing must happen in real-time. To attain the needed performance, an engineer would take different paths to design the system such as software design, hardware design, or software/hardware codesign. High processing performance in software design can be achieved by a high clock speed of the processor or the usage of a multicore processor. However, this would mean an increase in power consumption, heat and cost. On the other hand, hardware design using FPGA or GPU is more powerful due to its capability to operate in a parallel way, but comes with Bills of Material (BOM) cost, design complexity and potentially increasing the product development time. A better design solution is proposed with the software/hardware codesign, where performance hungry tasks are implemented in hardware while keeping small tasks for software. With the increasing improvements in system on chip (SOC) technology, the codesign development is much easier. Xilinx SoCs are processor-centric platforms that offer software, hardware and I/O programmability in a single chip. Xilinx introduced Zynq products that integrate ARM microprocessors in FPGAs to address the hardware complexity and BOM cost concerns, thus, there is no need to devote engineering resources to optimize a new printed circuit board (PCB) and its chip-to-chip interactions.

The main goal of our work is to see the impact of the design methodology on the performance of a system. In the first stage, we implemented a software design of a stereo-vision module, we evaluated the module based on the window size and disparity range. In addition to an obstacle detection module using the U-V disparity approach. In the second stage, we divided the system into hardware and software partitions, the stereo vision module was the most time-consuming part, therefore we integrated a hardware stereo vision module, preserving the same software obstacle detection module.

The report is organized as follows. In the first chapter, we tackle the theoretical background of stereo vision, including the geometric basis needed to understand the system modeling, and the different techniques for depth estimation, then we discuss the U-V disparity approach for obstacle detection. In the second chapter, we present a global design of the stereo vision-based obstacle detection system with all algorithms implemented. The third chapter is about the software implementation of the system as well as the experimental results and system evaluation. In the fourth chapter, we addressed the implementation of the obstacle detection system using the hardware/software codesign methodology, in addition to the processing performance.

# Chapter I: Obstacle detection using stereovision

#### I.1 Introduction

Autonomous navigation, obstacle avoidance, and off-world exploration, are all applications that have been suggested for intelligent robots; in which an excessive degree of autonomy is required. For the robots to function autonomously in unstructured or unfamiliar environments, a highly developed environment perception system is necessary. The environment perception system would help to deal with the obstacle detection problem; since the robot must be capable to detect the sudden appearance of obstacles in its path. To perform such task, the mobile robot system must be able to self-build a real three-dimensional (3D) of the environment. Stereo vision is one of the perception techniques that simulate the human vision system using two cameras to capture images from different viewpoints. Recent researches show that the stereo-based approach has distinct advantages in that it can sense the environment with a high resolution, precision, and a relatively wide range of measurement and low cost. In this chapter, we will present the theoretical background of stereo vision, including a geometric basis needed to understand the system modeling, different algorithm for depth extraction, then we will discuss the obstacle detection from depth information.

#### I.2 Stereo vision geometry

Stereo-vision is the process of extracting depth information from images recorded from multiple viewpoints. There are different methods to acquire these images:

- Single moving camera: A single camera is moved in space, recording images, thereby

providing images from different viewpoints. This implies a more or less static scene, as

moving objects would lead to errors in the depth map.

- Multiple camera setup: fixed camera array with the same focal length is used to acquire images from different viewpoints, the exact relative positions of all cameras are known. In this method, all images should be captured at the same time to ensure that no errors result from moving objects or movement of the camera array [1].

To understand the basic operation of stereo vision, one must have a basic understanding of cameras and how they perceive the world. There exist two camera models, pinhole model and camera model with lens.

#### I.2.1 Pinhole camera model

The pinhole camera is the simplest and the ideal model of camera function. This kind of camera can be imagined as a box with a pinhole, through which light enters and forms a two-dimensional image on the opposite site [2]. A point P = (X, Y, Z) in the three-dimensional (3-D) XYZ-space is projected to an image-point p = (x, y) in the two-dimensional (2-D) xy-space, as illustrated in Figure I.1. The projection coordinates are given by:

$$y = f \frac{X}{Z} \tag{I.1}$$

$$y = f \frac{X}{Z} \tag{1.2}$$

Where f is the focal length that represent the distance between pinhole and image plane.

Figure I.1: Pinhole camera model [3].

Equations (I.1) and (I.2) describe the mapping in Euclidean space into which a camera plane is embedded. Unfortunately, these two equations are both nonlinear with respect to Z coordinate because of the factor 1/Z. To represent both equations in a linear way, we transform the point (x, y) in the Euclidean plane to a point (x, y, 1) in the projective plane; these coordinates are called homogeneous coordinate [4].

The two equations are combined to generate a simple projection from world to image coordinates called perspective projection which can be written as:

$$\begin{pmatrix} x \\ y \\ 1 \end{pmatrix} = \frac{1}{Z} \begin{pmatrix} fX \\ fY \\ Z \end{pmatrix} = \frac{1}{Z} \begin{pmatrix} f & 0 & 0 & 0 \\ 0 & f & 0 & 0 \\ 0 & 0 & 1 & 0 \end{pmatrix} \begin{pmatrix} X \\ Y \\ Z \\ 1 \end{pmatrix}$$

(I.3)

1 ....

$\widetilde{P}$  is the projection matrix, it is the result of two relationships as illustrated in Figure I.2 :

- 1. Relationship between the world and the camera coordinate system, it is expressed by the extrinsic parameters, that depend on the position of the camera in world coordinate system, it includes rotation matrix R which relates the rotation of the world coordinate system with the camera coordinate system, and a translation vector T containing the translations along the X, Y, and Z axes from the origin of the world coordinate system to the origin of the camera system.

- 2. Relationship between the camera coordinate system and the image coordinates. This relationship is expressed by the intrinsic parameters K; it describes the camera geometry such as the optical center and focal length of the camera [5, 2].

Figure I.2: Representation of the extrinsic and intrinsic parameters [6].

Thus  $\tilde{P}$  can be expressed as:

$$\tilde{P} = K[R \quad T] \tag{I.4}$$

In pinhole model, we assumed that the optical center is at (0,0), the camera is centered at the origin of the 3-D coordinate, i.e., no rotation or translation. Equation (I.4) can be simplified as follow:

$$\tilde{P} = K[I \quad 0] = \begin{pmatrix} f & 0 & 0 & 0 \\ 0 & f & 0 & 0 \\ 0 & 0 & 1 & 0 \end{pmatrix}$$

(I.5)

In general, we may want to have multiple cameras with different poses at the same time, where satisfying those assumptions is impossible. Thus, a more realistic projection representation considering the optical center at  $(u_0, v_0)$ , camera is at  $(t_x, t_y, t_z)$  with rotation matrix R. Then the projection matrix can be written as:

$$\tilde{P} = K[R \quad T] = \begin{pmatrix} f & 0 & u_0 \\ 0 & f & v_0 \\ 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} r_{11} & r_{12} & r_{13} & t_x \\ r_{21} & r_{22} & r_{23} & t_y \\ r_{31} & r_{32} & r_{33} & t_z \end{pmatrix}$$

(I.6)

where  $r_{ij}$  represents rotation parameters.

#### I.2.2 Camera model with lens

Unfortunately, the camera's pinhole through which the light enters is almost infinitely small in the previous model, the smaller the hole, the less light enters the camera and the longer exposure time is needed. In a dynamic environment, this is not possible because the objects in the scene are moving. Thus, in reality, lenses are used to project more light onto the pinhole [4].

Figure I.3 shows how the light rays reflected by an object are projected through a lens. *P* is a point in the real world, *d* is the distance between *P* and the lens, *f* is the focal distance of the lens,  $f_k$  is the effective focal length (distance between the lens and the projected object *P*').

The relation between these parameters can be written in a mathematical form as follow:

$$\frac{1}{d} + \frac{1}{f_k} = \frac{1}{f}$$

(I.7)

Figure I.3: light-rays projection through a lens [7].

A negative effect of using lenses is distortion, which can be described as outwards (barrel distortion) or inwards (pincushion distortion) deviation from the ideal projection considered in pinhole camera model in reference to the center of the lens. Lens distortions are either due to the shape of the lens itself, or to an inaccurate alignment due to improper lens and camera assembly, this has no influence on the quality of the image, but it has a significant influence on the image geometry as shown Figure I.4.

Figure I.4: Lens distortion effect on image geometry [7].

#### I.2.3 Camera calibration

Camera calibration is an offline process of quantifying the internal camera geometric, optical characteristics (intrinsic parameters) and the 3D position and orientation of the camera frame relative to a certain world coordinate system (extrinsic parameters) [8]. These parameters can be used for various computer vision application including removal of lens distortion from an image. The Camera Calibration Toolbox for MATLAB can be used for both single and stereo camera calibrations. Another alternative to this toolbox is to use OpenCV library which is no more than the C implementation of the MATLAB camera calibration toolbox.

#### I.2.4 Epipolar geometry

The stereovision system utilizes a non-canonical stereo camera configuration, sometimes referred to as convergent system, where the optical axis of the two cameras is not parallel with one another. Such configuration is modeled by epipolar geometry.

A general epipolar geometry with two pinhole cameras arranged arbitrarily is shown in Figure I.5, where:

- $I_l$  and  $I_r$  are the image planes of left and right camera respectively.

- $C_l$  and  $C_r$  are projection centers for left and right cameras respectively.

- Baseline: the straight line that connects both cameras optical centers.

- Epipolar plane  $\pi$ : the plane containing the baseline and the corresponding points  $P_l$  and  $P_r$  of the scene point P.

- Epipoles: the points at which the line through the centers of projection intersects the image planes. Let  $e_l$  and  $e_r$  be the left and right epipoles respectively.

- Epipolar line: is the intersection of an epipolar plane with one image plane. All epipolar lines intersect at the epipole. An epipolar plane intersects the left and right image planes in epipolar lines.

Figure I.5: Epipolar geometry [9].

The mathematical interpretation of the epipolar geometry is that, for a corresponding point pair (pl, pr) in homogeneous coordinates, we have [10]:

$$P_l^{\mathsf{T}} F P_r = 0 \tag{I.8}$$

where F is called fundamental matrix and  $F P_r$  describes a line (an epipolar line) on which the corresponding point  $P_l$  must set.

#### I.2.5 Image un-distortion and stereo rectification

The image un-distortion is to compensate the effects of lens distortions, it consists of a transformation from physically distorted image to an ideal image under the pinhole camera model; according to the parameters calculated in the camera calibration step. For every pixel in undistorted image, we have to compute its distorted location [11].

The image rectification is the process of remapping images using the fundamental matrix such that the epipolar lines are horizontal. Thus, the resulting images are row aligned and the points in the left picture of one row to be in the same row of the right picture as shown in Figure I.6.

Figure I.6: Stereo rectification effect [11].

#### I.3 Depth estimation

In ideal situation, where the two stereo images are perfectly rectified and un-distorted as illustrated in Figure I.7, depth Z is easily estimated.

Figure I.7: 3D triangulation between two parallel, identical cameras [11].

In Figure I.7 the world point P = (X, Z) is projected into the left image as  $P_l = (x_l, y_l)$  and into the right image as  $P_r = (x_r, y_r)$ , *f* is the focal length, *b* is the base line. From triangles  $T_1$  and  $T_2$ , we can derive equations (I.9) and (I.10) respectively.

$$\frac{Z}{f} = \frac{X}{x_l} \tag{I.9}$$

$$\frac{Z}{f} = \frac{X-b}{x_r} \tag{I.10}$$

From the above equations, we can write:

$$\frac{X}{x_l} = \frac{X-b}{x_r} \tag{I.11}$$

After distributing terms and dividing by *X* we get:

$$b\frac{x_l}{x} = x_l - x_r \tag{I.12}$$

Replacing  $(\frac{x_l}{x})$  by  $(\frac{f}{z})$  in equation (I.12) we get:

$$Z = f \frac{b}{x_l - x_r} \tag{I.13}$$

The quantity  $(x_l - x_r)$  is referred to as disparity "d", so we can rewrite equation (I.13) as follow:

$$Z = f \frac{b}{d} \tag{I.14}$$

From equation (I.14) we can deduce that:

- Far away objects (large distance from the observer) will move very little between the left and right image thus a small disparity.

- Very close by objects (small distance from the observer) will move quite a bit more means greater disparity.

#### I.4 Stereo correspondence

The previous section showed how to determine depth from disparity, which rely on solving what's known as stereo correspondence or stereo matching problem, where the aim is to identify corresponding points or objects in left and right image. This require a measure of similarity in order to find the point correspondences between the left and right images, for each pixel in the left image, there are a lot of possible candidates in the right image to be evaluated in order to determine the best corresponding pixel [12].

The search of corresponding points becomes even easier using rectified images. Then, corresponding points would have to be on the same horizontal line in both images. Solving the correspondence problem for all pixels, a disparity map (DM) can be built by gathering all the disparity measures in an image. In Figure I.8, two example pairs of corresponding points are indicated, with their position on the disparity map, which is a simple depth map, brighter areas are closer to the foreground and darker areas closer to the background [1].

Figure I.8: Correspondence problem and DM estimation [1].

Note that the disparity map in Figure I.8 is actually the ground truth which is a precise depth map generated using laser range-finder (LRF) and not a disparity map computed by an algorithm. It is important to keep in mind that is not possible to find perfect correspondences. Instead, it's just a matter of finding the most probable correspondences [1]. The stereo correspondence algorithms can roughly be divided into feature-based and correlation-based, also known as region, area and intensity-based.

#### I.4.1 Feature based algorithms

Feature based algorithms extract features (e.g., edges, angles, curves, etc.) from images and try to match them in two or more views [13]. This technique has a lower computational complexity because only features have to be compared, lesser ambiguities due to the smaller number of possible matches and less sensitive comparisons between features are less sensitive to illumination changes [4, 14]. Despite these advantages, features-based technique's main drawback, is that it yields a sparse DM, thus depth values are only known for corresponding features found and not for every pixel. Interpolation can be used to get a denser DM [4].

#### I.4.2 Correlation based algorithms

Correlation based also known as area-based algorithm produces a dense DM, which means that for each pixel of an image the algorithm tries to find its mutual pixel on the other view [13]. In order to find the best match, a pixel to be matched from a reference image (left image); essentially becomes the center of a small window of pixels, is compared to a similarly sized windows in the other image (right image) by spanning it along a horizontal axis for disparity ranges. Correlation metrics are used to provide a numerical measure of the similarity between the two windows [15, 16]. Based on these measures' disparity selection is mostly performed in the Winner-Takes-All (WTA) strategy, i.e., the disparity with the lowest measurement is chosen [17, 18] as illustrated in Figure I.9.

Figure I.9: Stereo matching procedures [19].

#### I.4.2.1 Correlation metrics

Over the years, a large collection of intensity-based correlation metrics has been proposed. The simplest and least computationally intensive methods are Sum of Absolute Differences (SAD) and Sum of Squared Differences (SSD), which are based on the difference in pixel intensity and the assumption that corresponding areas in the two images will be similar in appearance [15]. The SAD and SSD are performed using equation (I.15) and (I.16) respectively:

$$SAD(x, y, d) = \sum_{i=x-n}^{x+n} \sum_{j=y-n}^{y+n} |f_{i,j} - g_{i+d,j}|$$

(I.15)

$$SSD(x, y, d) = \sum_{i=x-n}^{x+n} \sum_{j=y-n}^{y+n} (f_{i,j} - g_{i+d,j})^2$$

(I.16)

Where (x, y) are the central pixel coordinates,  $f_{i,j}$  and  $g_{i,j}$  are the intensity of the pixel at coordinates (i, j) in the reference image (left image) and right image respectively, *n* defines the extend of the block in either direction around the center pixel, the window has therefore width and height 2n + 1. The variable *d* is the disparity range, that represents the distance across which the search for correspondence is conducted.

#### I.4.2.2 Non-parametric transformation

The problem with correlation metrics is that they are sensitive to radiometric distortion [20], and measures are not very distinctive when intensities of different pixels are the same such as in texture-less region. A commonly used approach to solve this problem, is to use larger windows, but this will lead to more false matches and increases the computation time, another approach is based on non-parametric transforms. Non-parametric transforms are applied to images prior to matching, which are based on the relative ordering of pixel intensities within a window, rather than the intensity values themselves. Two non-parametric transforms which are suited to fast implementation are the rank transform and the census transform.

#### 1. Rank transform

The Rank transform of a central pixel p is defined as the number of pixels in the local neighborhood whose intensity is less than the intensity of p, by replacing each pixel in the window as a bit stream, where each pixel with intensity less than the center pixel's intensity is replaced by 1, otherwise it is set to 0, this principal is illustrated in Figure I.10. A pair of rank transformed images are matched using regular correlation metrics like SAD to compute the difference between image regions.

$$Rank \begin{pmatrix} 13 & 89 & 34 \\ 12 & 34 & 23 \\ 11 & 99 & 75 \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 \\ 1 & p & 1 \\ 1 & 0 & 0 \end{pmatrix} = 4$$

Figure I.10: Rank transformation using 3\*3 window.

#### 2. Census transform

The Census transform maps the window surrounding a central pixel p to a bit vector representing the local information about the pixel p and its neighboring pixels. If the intensity value of a neighboring pixel is less than the intensity value of the pixel p, then the corresponding bit is set to 1, otherwise it is set to 0. This principal is illustrated in Figure I.11.

$$Census \begin{pmatrix} 13 & 89 & 34 \\ 12 & 34 & 23 \\ 11 & 99 & 75 \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 \\ 1 & p & 1 \\ 1 & 0 & 0 \end{pmatrix} = 10011100$$

Figure I.11: Census transformation using 3\*3 window

Two Census transformed images (left and right) are compared using Hamming distance (HD), which is a metric for comparing two binary data strings of same length, quantified by the number of bits that differ between the two strings. In stereo correspondence, HD is number the bits that differ between the two Census transformed images, as shown Figure I.12.

Census of left pixel =

$$10011100$$

Census of right pixel =  $11011110$

$HD = 2$

Figure I.12: Hamming Distance principle.

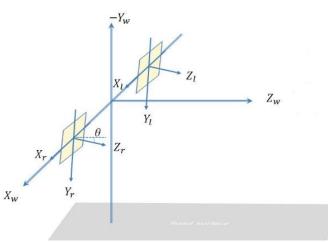

#### I.5 Domain of U-V disparity