# People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research University M'Hamed BOUGARA – Boumerdès

# Institute of Electrical and Electronic Engineering Department of Electronics

Project Report Presented in Partial Fulfilment of the Requirements of the Degree of

### 'MASTER'

In: Electronics

Option: Computer Engineering

Title:

# Design and Implementation of Spiking Neural Networks on FPGA for Event-Based Spatio-Temporal Applications

### Presented By:

- BOUMERZOUG Nadhir

- ZERRARI Dhia Elhak

Supervisor:

Co-Supervisor:

- Prof. CHERIFI Dalila

Prof. KHOUAS Abdelhakim

Registration Number: 2023/2024

# **Abstract**

Inspired by the intricacies of real biological neural systems, Spiking Neural Networks (SNNs) represent an advanced type of artificial neural network. SNNs operate with discrete spikes, closely mimicking the way neurons communicate in the human brain. This unique method of information processing not only enhances the computational efficiency of SNNs but also opens up new possibilities for developing low-power neural network systems. In this work, we proposed a generic hardware design of an SNN based on Field-Programmable Gate Arrays (FPGA). The proposed design was implemented and tested with the event-based benchmark dataset "Neuromorphic-MNIST", and managed to achieve a low power consumption and latency, while requiring very minimal hardware resources, all this for an evaluated accuracy.

#### **Keywords**

Spiking Neural Networks, Neuromorphic Computing, Spatio-Temporal Pattern, FPGA, RTL design, VHDL

# Acknowledgments

First and foremost, we would like to extend our deepest gratitude to God Almighty who provided us with his blessing and the opportunity to successfully conclude our project.

In the successful accomplishment of our final year project titled "Design & Implementation of Spiking Neural Networks on FPGA for Spatio-temporal Applications", we would like to express our deepest gratitude to our supervisor, Prof.CHERIFI Dalila. We are immensely grateful for her valuable advices regarding our research and future career prospects. Her willingness to assist us, steadfast encouragement and continuous support were instrumental in making this project a reality. We deeply appreciate her patience, dedication, and unwavering belief in our abilities.

We would also like to express our appreciation to our co-supervisor, Prof. KHOUAS Abdelhakim for his significant contributions. His expertise and willingness to provide assistance have greatly enhanced the quality of this work.

We would like to thank BOUANANE Mohamed Sadek, for his insightful guidance and help throughout the project duration.

Lastly but not least, we are immensely thankful to our parents and friends for their unwavering support in completing this report. We would like to extend our gratitude to all the individuals who have supported us throughout this journey.

# **Contents**

| <b>A</b> l | bstra             | ct       |                                    | i    |  |  |

|------------|-------------------|----------|------------------------------------|------|--|--|

| A          | Acknowledgments i |          |                                    |      |  |  |

| Li         |                   |          |                                    |      |  |  |

| Li         | st of             | Tables   |                                    | vii  |  |  |

| Li         | st of             | Abbrev   | viations                           | viii |  |  |

| G          | enera             | l Introd | duction                            | 1    |  |  |

| 1          | Ove               | rview (  | on Neuromorphic Computing          | 3    |  |  |

|            | 1.1               | Introd   | luction                            | . 4  |  |  |

|            | 1.2               | Rethir   | nking Computation                  | . 4  |  |  |

|            |                   | 1.2.1    | Power Hungry Embedded AI Systems   | . 4  |  |  |

|            |                   | 1.2.2    | Moore's Law is dead                | . 5  |  |  |

|            |                   | 1.2.3    | Memory bottleneck                  | . 5  |  |  |

|            | 1.3               | Biolog   | gical Neuron                       | . 6  |  |  |

|            | 1.4               | Huma     | nn Visual System                   | . 7  |  |  |

|            | 1.5               | Event-   | -Based Vision Sensors              | . 8  |  |  |

|            | 1.6               | AI Ge    | nerations                          | . 8  |  |  |

|            | 1.7               | Summ     | nary                               | . 9  |  |  |

| 2          | Ove               | erview o | of SNN for Inference Methodologies | 10   |  |  |

|            | 2.1               | Introd   | luction                            | . 11 |  |  |

|            | 2.2               | Artific  | cial Neuron                        | . 11 |  |  |

|            | 2.3               | Spikir   | ng Neuron Models                   | . 12 |  |  |

|            |                   | 2.3.1    | Hodgkin-Huxley Model               | . 12 |  |  |

|            |                   | 2.3.2    | Leaky Integrate-and-Fire (LIF)     | . 13 |  |  |

|            |                   | 2.3.3    | Integrate-and-Fire (IF)            | . 14 |  |  |

|            | 2.4               | Spike    | Train Encoding                     | . 15 |  |  |

|    | 2.5                                           | SNN 7   | Topology                               | 15                              |  |  |  |

|----|-----------------------------------------------|---------|----------------------------------------|---------------------------------|--|--|--|

|    |                                               | 2.5.1   | Input Layer                            | 15                              |  |  |  |

|    |                                               | 2.5.2   | Hidden Layer                           | 16                              |  |  |  |

|    |                                               | 2.5.3   | Output Layer                           | 18                              |  |  |  |

|    | 2.6                                           | Addre   | ess Event Representation               | 18                              |  |  |  |

|    | 2.7                                           | Spatio  | -Temporal Data                         | 19                              |  |  |  |

|    |                                               | 2.7.1   | Conventional MNIST                     | 20                              |  |  |  |

|    |                                               | 2.7.2   | Event-based MNIST                      | 20                              |  |  |  |

|    |                                               | 2.7.3   | Neuromorphic-MNIST                     | 21                              |  |  |  |

|    | 2.8                                           | Nume    | rical Representation                   | 21                              |  |  |  |

|    |                                               | 2.8.1   | Floating-point numbers                 | 22                              |  |  |  |

|    |                                               | 2.8.2   | Fixed-point numbers                    |                                 |  |  |  |

|    | 2.9                                           | Summ    | nary                                   | 23                              |  |  |  |

| 2  | Dasi                                          |         | I Invalence to the Alexander CNN       | 24                              |  |  |  |

| 3  | 3.1                                           | •       | I Implementation of a Hardware SNN     | <ul><li>24</li><li>25</li></ul> |  |  |  |

|    | 3.2                                           |         | luction                                |                                 |  |  |  |

|    | 3.2                                           | Ŭ       |                                        |                                 |  |  |  |

|    |                                               | 3.2.1   | Neuron Model                           | 25                              |  |  |  |

|    |                                               | 3.2.2   | Spike Index Table Design               | 27                              |  |  |  |

|    |                                               | 3.2.3   | Neuron Wrapper Design                  | 28                              |  |  |  |

|    |                                               | 3.2.4   | Output Encoding Module Design          | 29                              |  |  |  |

|    | 2.2                                           | 3.2.5   | Neural Network Design                  | 30                              |  |  |  |

|    | 3.3                                           | -       | mentation                              | 31                              |  |  |  |

|    |                                               | 3.3.1   | Targeted Application                   |                                 |  |  |  |

|    |                                               | 3.3.2   | Tools and Equipment                    |                                 |  |  |  |

|    |                                               | 3.3.3   | Planning and Preliminary Testing       | 33                              |  |  |  |

|    |                                               | 3.3.4   | Hardware Implementation and Simulation | 36                              |  |  |  |

|    | 3.4                                           | Summ    | nary                                   | 44                              |  |  |  |

| 4  | Evaluation of the Hardware SNN Implementation |         |                                        |                                 |  |  |  |

|    | 4.1                                           | Introd  | luction                                | 46                              |  |  |  |

|    | 4.2                                           | Latenc  | cy and Spiking Activity Analysis       | 46                              |  |  |  |

|    | 4.3                                           | Power   | and Resource utilization Analysis      | 46                              |  |  |  |

|    |                                               | 4.3.1   | Data Transfer operation (PC-to-FPGA)   | 47                              |  |  |  |

|    |                                               | 4.3.2   | Weight Memory                          | 51                              |  |  |  |

|    |                                               | 4.3.3   | Results and Discussion                 | 54                              |  |  |  |

|    | 4.4                                           | Summ    | nary                                   | 57                              |  |  |  |

| Ge | enera                                         | l Concl | lusion                                 | 58                              |  |  |  |

# **List of Figures**

| 1.1  | The anatomy of a biological neuron [4]                                  | 6  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Schema of synaptic transmission [4]                                     | 7  |

| 1.3  | Different types of Dynamic Vision Sensors [6]                           | 8  |

| 1.4  | The three generations of neural networks [8]                            | 9  |

| 2.1  | Equivalent electrical circuit of the Hodgkin-Huxley neuron [11]         | 12 |

| 2.2  | Equivalent circuit of the LIF neuron                                    | 14 |

| 2.3  | (A) Typical Artificial neuron pipeline (B) An equivalent Spiking neuron |    |

|      | system [18]                                                             | 17 |

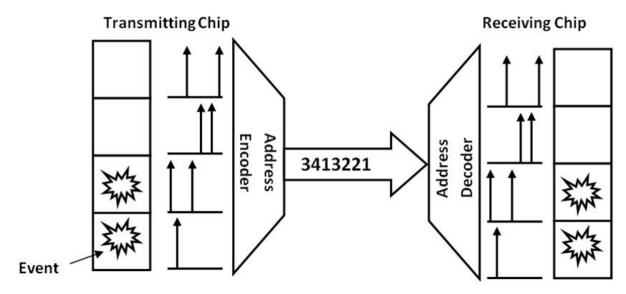

| 2.4  | Address Event Representation for chip-to-chip communication             | 19 |

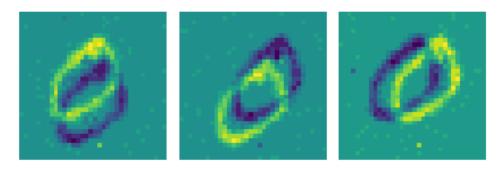

| 2.5  | Digit 0 sample from the N-MNIST dataset                                 | 21 |

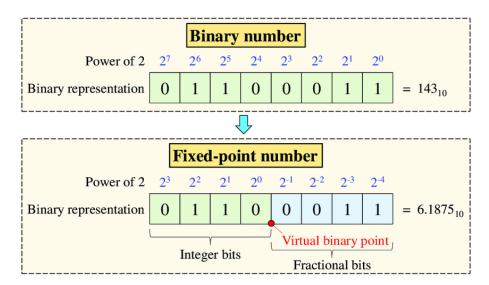

| 2.6  | Example of fixed-point number representation [31]                       | 23 |

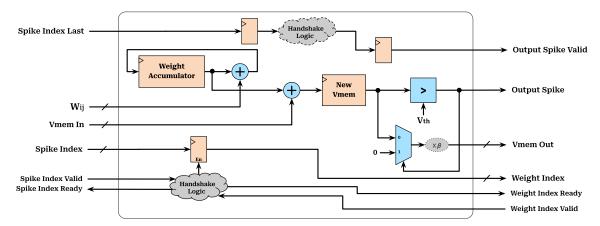

| 3.1  | IF/LIF neuron model architecture                                        | 26 |

| 3.2  | Handshake logic architecture                                            | 26 |

| 3.3  | Spike index table architecture                                          | 28 |

| 3.4  | Neuron wrapper block diagram                                            | 29 |

| 3.5  | Output Encoding Module Diagram                                          | 29 |

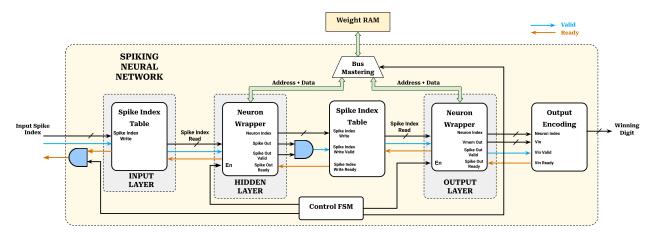

| 3.6  | Network diagram                                                         | 30 |

| 3.7  | Picture of the Sipeed Tang Nano 4K FPGA development board               | 31 |

| 3.8  | Architecture overview of the GW1NSR-4C                                  | 32 |

| 3.9  | N-MNIST pre-processing pipeline                                         | 33 |

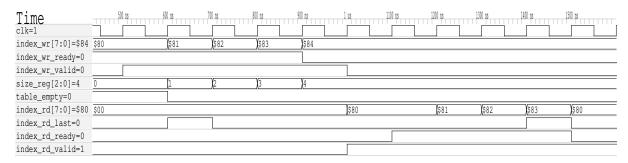

| 3.10 | Spike index table simulation                                            | 37 |

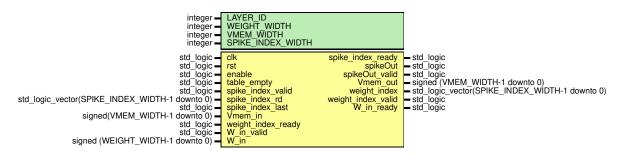

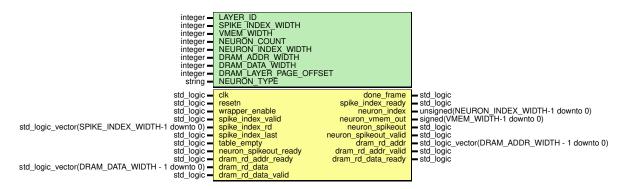

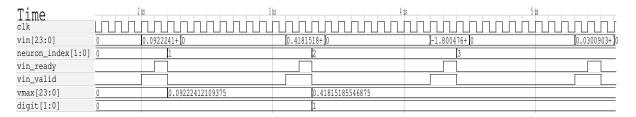

| 3.11 | Neuron model ports and parameters                                       | 37 |

| 3.12 | IF neuron simulation                                                    | 38 |

| 3.13 | LIF neuron simulation                                                   | 39 |

| 3.14 | Neuron wrapper ports and parameters                                     | 40 |

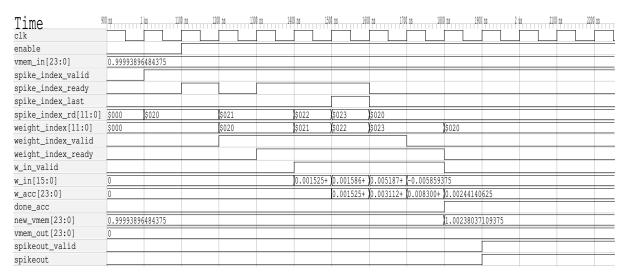

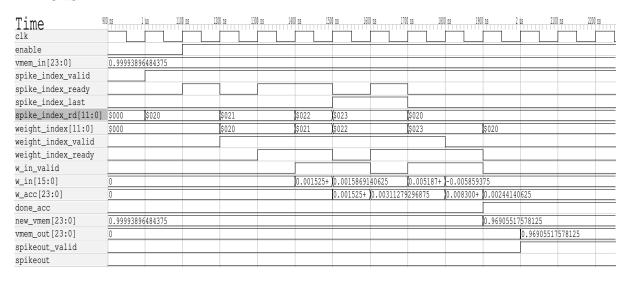

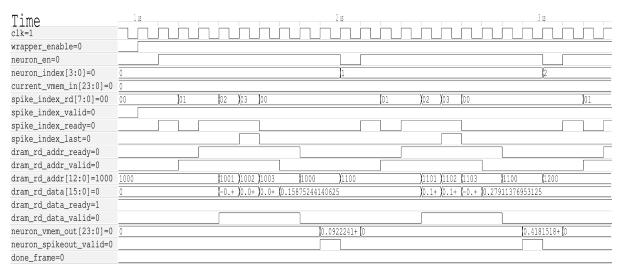

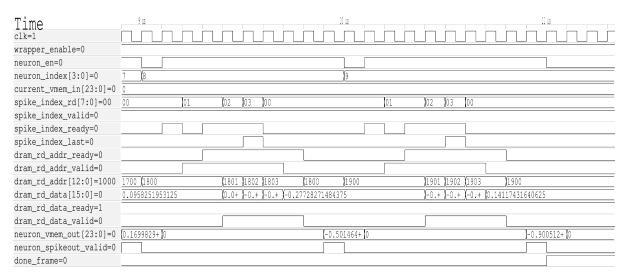

| 3.15 | Neuron wrapper startup                                                  | 40 |

| 3.16 | Neuron wrapper wind-down                                                | 41 |

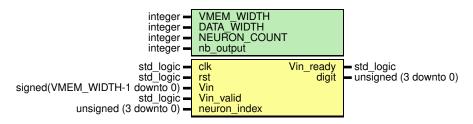

| 3.17 | Output encoder ports and parameters                                     | 42 |

| 3.18 | Output encoder simulation.                                              | 42 |

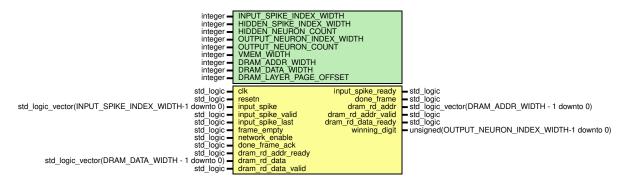

| 3.19 | Network ports and parameters                                          | 42 |

|------|-----------------------------------------------------------------------|----|

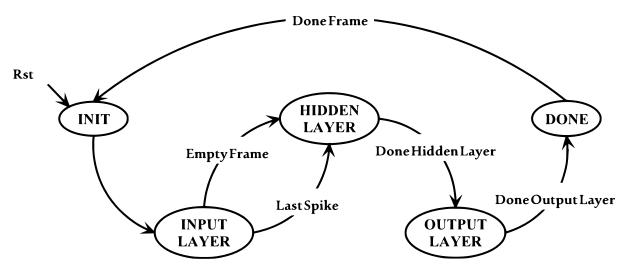

| 3.20 | State diagram of the network's FSM                                    | 43 |

| 3.21 | Network simulation transitioning into the hidden layer state          | 43 |

| 3.22 | Network simulation transitioning into the output layer state          | 43 |

| 3.23 | Network simulation latching the output and preparing for a new frame. | 44 |

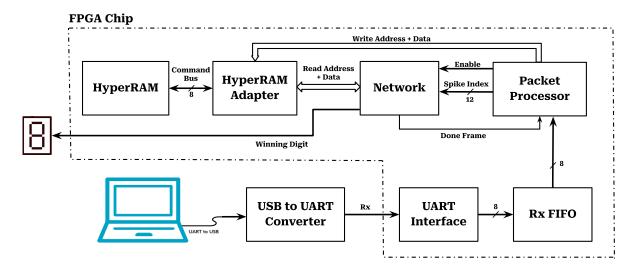

| 4.1  | Overall diagram of the test setup                                     | 47 |

| 4.2  | General format of a UART packet                                       |    |

| 4.3  | ESP32-CAM-MB USB-to-UART converter, and the ESP32-CAM board           | 48 |

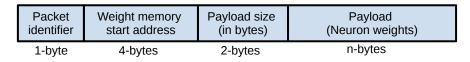

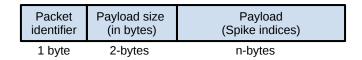

| 4.4  | Weight packet format                                                  | 49 |

| 4.5  | Spike frame packet format                                             | 50 |

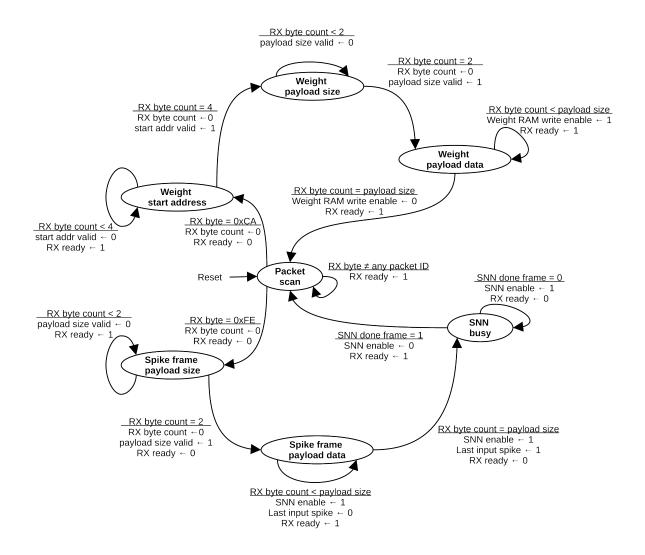

| 4.6  | State diagram of the packet processor FSM                             | 51 |

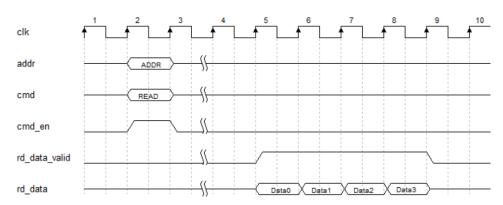

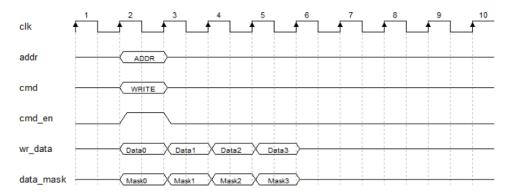

| 4.7  | Burst read transfer using the Gowin HyperRAM IP                       | 52 |

| 4.8  | Burst write transfer using the Gowin HyperRAM IP                      | 53 |

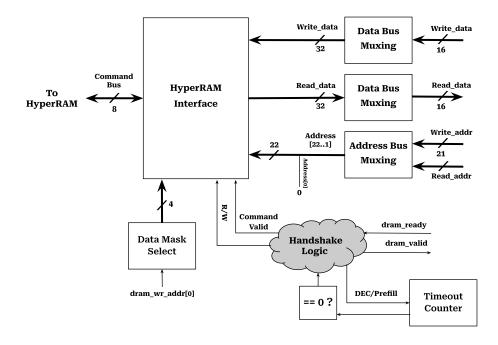

| 4.9  | HyperRAM adapter block diagram                                        | 54 |

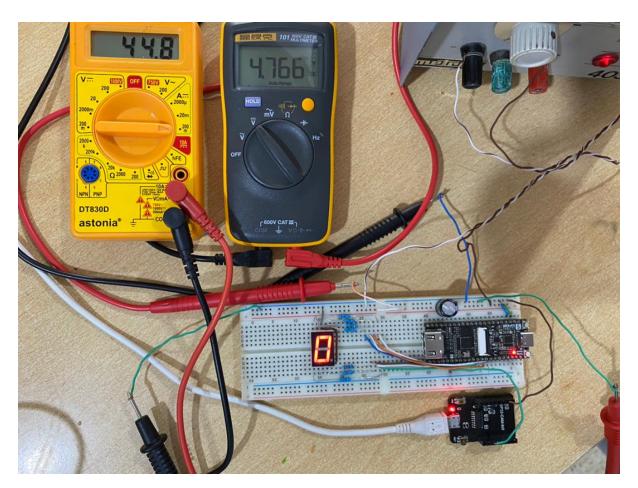

| 4.10 | Experimental Setup                                                    | 55 |

# **List of Tables**

| 3.1 | Accuracy summary for weight conversion | 34 |

|-----|----------------------------------------|----|

| 4.1 | Latency and spiking activity summary   | 46 |

| 4.2 | FPGA resource usage summary            | 56 |

| 4.3 | Power consumption summary              | 56 |

# List of Abbreviations

AI Artificial Intelligence

**ANNs** Artificial Neural Networks

**AER** Address Event Representation

**ASIC** Application-specific integrated circuit

**BRAM** Block RAM

**CNNs** Convolutional Neural Networks

CUBA-LIF Current-Based LIF

DRAM Dynamic RAM

DSP Digital Signal ProcessorDVS Dynamic Vision Sensors

**FIFO** First-In-First-Out

**FPGAs** Field Programmable Gate Arrays

**FSM** Finite State Machine

**GPU** Graphics Processing Unit

GPIO General-Purpose Input/Output

HDL Hardware Description Language

**HDMI** High-Definition Multimedia Interface

**HPC** High-Performance Computing

**IF** Integrate-and-Fire

JTAG Joint Test Action Group

LIF Leaky Integrate-and-Fire

LUT Look Up Table

MAC Multiply-and-ACcumulate operation

MNIST Mixed National Institute of Standard Technology

N-MNIST Neuromorphic MNIST

PCI Peripheral Component Interconnect

PLLs Phase-Locked Loops

RAM Random Access Memory

RNNs Recurrent Neural Networks

RTL Register-Transfer-Level

**SCNN** Spiking Convolutional Neural Networks

**SNNs** Spiking Neural Networks

**SoPC** System-on-Programmable-Chip

**SRAM** Static RAM

TTFS Time-To-First-Spike

**UART** Universal Asynchronous Receiver / Transmitter

VHDL VHSIC HDL

# **General Introduction**

Artificial Neural Networks (ANNs) have garnered significant attention from academia and industry in the last ten years. The abundance of publicly available data and the increased processing power of modern computers have led to a significant increase in interest in ANNs because they have made ANN training and inference very efficient. Particularly deep neural networks have proven to be very effective at tasks like image classification, making them standout instruments in machine learning and artificial intelligence research. However, there are still a lot of obstacles to overcome when it comes to real-time processing on edge devices, like those found in autonomous cars. These difficulties result from traditional hardware implementations' high energy consumption and high cost, which are ill-suited for the computational requirements of artificial neural networks. In contrast, the human brain performs complex cognitive tasks efficiently, using only a few watts of power. Inspired by this biological efficiency, Spiking Neural Networks (SNNs) have emerged as a promising alternative, aiming to achieve energy-efficient machine intelligence by mimicking the brain's neural mechanisms. Despite their potential, there remains a considerable gap in understanding the differences and impacts of various spiking neuron models, particularly concerning their hardware implementation and performance in real-time applications.

This project seeks to address this gap by studying the effect of membrane leakages in different spiking neuron models, which vary in their levels of biological abstraction, on a spatio-temporal classification task. By analyzing metrics such as power consumption, latency, spiking activity, and resource allocation, we aim to provide a comprehensive evaluation of these models' performance on digital hardware. To facilitate this comparative analysis, we propose a generic and efficient digital hardware design for SNN inference. Our focus on inference, rather than training, is driven by the fact that training is highly resource-intensive and not well-suited for hardware implementation. Training a neural network requires substantial computational resources, but this process is only performed once to determine the optimal weights and biases. Once trained, the model can be efficiently deployed for real-time inference on hardware, making this approach more feasible for practical applications.

This report is organized as follows: Chapter 1, introduces the field of neuromorphic computing, discussing the motivations and challenges that have led to the exploration

of SNNs. Chapter 2, provides an overview of existing methodologies for SNN inference and introduces the spiking neuron models used in our project. Chapter 3 details the design and implementation of the various building blocks of the SNN, focusing on their application to the handwritten digit classification task. The design is then evaluated in Chapter 4, where various metrics were collected from two experimental setups.

# **Chapter 1**

# Overview on Neuromorphic Computing

#### 1.1 Introduction

As the need for Artificial Intelligence (AI) applications continues to grow, a critical challenge arises: power consumption. Traditional computing architectures, such as Von Neuman and Harvard architectures, while capable of handling AI tasks, are known for their massive power consumption. This power hunger becomes most noticeable when working with spatio-temporal data, for instance, speech recognition, image detection, and video processing. Furthermore, these applications demand immense computational resources, often pushing conventional hardware to its limits and beyond. Compounding this issue is the slowdown of Moore's law, the principle that has guided semiconductor technology for decades. As transistor sizes approach physical limits, the time of exponential growth in computing power seems to be coming to an end. As a result, the search for alternative computing paradigms has received a lot of attention from scholars in the field in recent decades. Neuromorphic computing, inspired by the structure and function of the human brain, offers a promising approach into addressing the dual concerns of power consumption and resource utilization. By emulating the very complicated connection and interchange of neurons in the human brain, neuromorphic computing offers the potential to revolutionize AI models. These novel models utilize bio-inspired neurons to perform complex tasks with enough higher efficiency. Moreover, they hold the promise of developing new AI Accelerators that are not only less power-hungry but also more suitable at handling spatio-temporal data, known as "Neuromorphic Chips". Field Programmable Gate Arrays (FPGAs), with their reconfigurable hardware architecture, afford us with the flexibility to design and implement bio-inspired based AI accelerators. Their low power demand, reconfigurability, and parallelism makes them an ideal platform for prototyping and deploying neuromorphic AI models.

# 1.2 Rethinking Computation

It is noticeable the rapid advancement in computing systems for the last decades. However, such systems are not really efficient in terms of several factors, highlighting the need to explore new computing primitives to address evolving demands and challenges in the digital landscape.

#### 1.2.1 Power Hungry Embedded AI Systems

The growing use of Artificial Intelligence in embedded systems has resulted in a notable increase in power consumption. For instance, the GPT-3 transformer model, which boasts 175 billion parameters, necessitates a minimum of 350GB of GPU (Graphics

Processing Unit) memory just for inference. This translates to the need for approximately 8 Nvidia A6000 GPUs, which are among the most advanced deep learning-oriented High-Performance Computing (HPC) devices available, such a setup consumes around 2400W of power. This is also noticeable in autonomous applications like surveillance cameras, robots, and drones that rely on machine learning models for their operation. The energy efficiency of these systems is important as they depend most of the time on limited-capacity batteries and solar cells.

Consequently, the energy scalability of Machine Learning is becoming a pressing concern within both scientific circles and the general public. This energy issue is particularly acute in the domain of embedded systems, where power efficiency is paramount.

#### 1.2.2 Moore's Law is dead

Moore's Law, named after Intel co-founder Gordon Moore, posits that the number of transistors on a microchip doubles approximately every two years [1]. This has led to an extraordinary 3,500-fold increase in processor speeds over 30 years—from 1 MHz to 5 GHz. In stark contrast, innovations in architecture only achieved about a 50-fold improvement in the same period. It is worth mentioning that Moore's law is not a law of physics; it is more an empirical observation. Although, this principle has driven the exponential growth of the computer science industry for over half a century, transistors are approaching atomic scales, with the smallest ones commercially available being only 3 nanometers wide, the pace of miniaturization has slowed. For instance, it took Intel five years to progress from 14-nanometer to 10-nanometer technology, rather than the two years predicted by Moore's Law. This has led some, including MIT Professor Charles Leiserson, to declare that Moore's Law has been effectively over since at least 2016 [2].

The growing computational hunger of AI models poses a set of significant challenges, including increasing global carbon emissions and the escalating privatization of AI research. In response to these challenges, the semiconductor industry has been investigating future advancements and finding solutions to the death of Moore's Law.

#### 1.2.3 Memory bottleneck

The Von Neumann bottleneck is a fundamental limitation of the traditional computer architecture design. However, it is important to note that this bottleneck is not just a hardware issue. It is also closely tied to the way software is designed and executed. In the traditional Von Neumann architecture, instructions and data are stored in the same memory and processed sequentially [3]. This means that even if we could infinitely increase the speed of our hardware, the sequential nature of software execution could still limit the overall system performance.

## 1.3 Biological Neuron

The human brain is among the most intricate and complex entities known. It comprises approximately 100 billion neurons and nearly 40 trillion synapses, rendering it one of the most challenging structures to study. Each neuron can form thousands of synaptic connections, resulting in an incredibly dense and interconnected network. This complexity is further enhanced by the diversity of neuronal types, with estimates suggesting the presence of over tens of thousands of distinct types, each contributing uniquely to the brain's functionality.

The brain's ability to perform a vast array of functions with remarkable efficiency is a subject of great scientific interest. Despite its complexity, it operates with minimal power consumption, utilizing approximately 20 watts only. This efficiency is partly due to the brain's sophisticated mechanisms for energy conservation and optimization in neural processing.

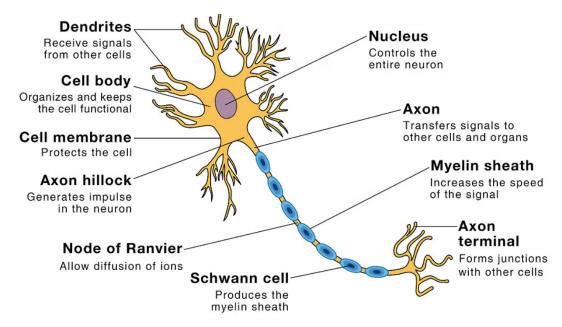

Figure 1.1: The anatomy of a biological neuron [4].

A biological neuron, also known as a nerve cell, is the fundamental building block of the nervous system. Neurons are specialized cells responsible for transmitting and processing information throughout the body, enabling complex functions such as sensation, thought, movement, and homeostasis. They achieve this through electrochemical signaling, which involves the generation and propagation of electrical impulses and the release of neurotransmitters.

Figure 1.1 depicts a simplified anatomy of the biological neuron. Each neuron consists of three main parts: the cell body (soma), dendrites, and an axon. The cell body contains the nucleus and other organelles essential for the neuron's metabolic activities. Dendrites are branched extensions that receive signals from other neurons and convey

them towards the cell body. The axon is a long, slender projection that transmits electrical impulses away from the cell body to other neurons, muscles, or glands. The axon often ends in a series of terminal branches, each of which forms synaptic connections with target cells.

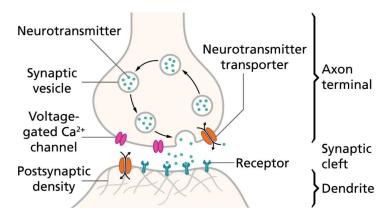

Figure 1.2: Schema of synaptic transmission [4].

As shown in Figure 1.2, Neurons communicate through synapses, specialized junctions where the axon terminal of one neuron comes into close proximity with the dendrite or cell body of another. When an electrical impulse, or action potential, reaches the synaptic terminal, it triggers the release of neurotransmitters into the synaptic cleft. These chemical messengers bind to receptors on the post-synaptic neuron, initiating a response that can either excite or inhibit the generation of a new action potential.

## 1.4 Human Visual System

The human visual system, particularly the retina, is an exemplar of efficient information encoding, reducing input from approximately 125 million photoreceptors to output through just 1 million ganglion cells. This compression is achieved by organizing photoreceptors into receptive fields of various sizes, each connected to a ganglion cell. The structure of these fields, with center and surround cells, allows ganglion cells to convey spatial contrast by comparing the differential firing rates within their receptive field. Ganglion cells can fire independently and maintain a spontaneous firing rate, ensuring continuous transmission of visual information via the optic nerve to the brain. This inherent efficiency and specialization in contrast extraction have inspired the field of neuromorphic engineering, which aims to mimic these biological processes in artificial systems. Pioneered by Carver Mead in the late 1980s, neuromorphic engineering gained significant momentum with Misha Mahowald's creation of the first silicon retina, designed to emulate the human retina's center-surround receptive fields. Subsequent advancements by Tetsuya Yagi and Tobi Delbrück led to the development of refined temporal contrast sensors, known as event cameras.

#### 1.5 Event-Based Vision Sensors

Current cameras acquire frames by reading the brightness value of all pixels at the same time at a fixed time interval, the frame rate, regardless of whether the recorded information has actually changed.

Trying to take inspiration from the way our eyes encode information, neuromorphic cameras capture changes in illuminance over time for individual pixels corresponding to one retinal ganglion cell and its receptive field.

If light increases or decreases by a certain percentage, one pixel will trigger what's called an event, which is the technical equivalent of a cell's action potential. One event will have a timestamp, x/y coordinates and a polarity depending on the sign of the change. Pixels can fire completely independently of each other, resulting in an overall firing rate that is directly driven by the activity of the scene. It also means that if nothing moves in front of a static camera, no new information is available hence no pixels fire apart from some noise. The absence of accurate measurements of absolute lighting information is a direct result of recording change information. This information can be refreshed by moving the camera itself, much like a microsaccade [5].

Figure 1.3: Different types of Dynamic Vision Sensors [6].

#### 1.6 AI Generations

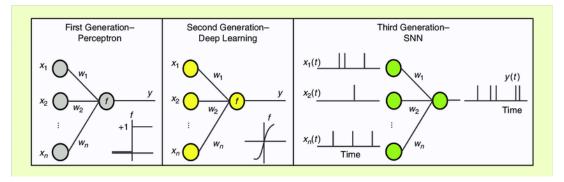

Our brains, with their billions of neurons firing in intricate patterns, have long been a source of wonder and inspiration. Traditional Artificial Neural Networks (ANNs) have attempted to replicate its complexity, but they often fall short in terms of energy efficiency and real-time processing. This yields in introducing the third generation of neural networks, a more bio-inspired neuron based network architecture, known as Spiking Neural Networks (SNNs). Unlike conventional neural networks, which rely on continuous firing rates, SNNs communicate through discrete spikes, similar to the way neurons in our brains function. This biologically mimicking approach holds the potential to revolutionize computing, offering unparalleled efficiency and capabilities [7].

Figure 1.4: The three generations of neural networks [8].

## 1.7 Summary

In this chapter, we discussed the challenges of traditional computing architectures in handling AI tasks, especially regarding power consumption and efficiency. We introduce neuromorphic computing as a promising solution, inspired by the human brain, to address these issues. The chapter covers the limitations of Moore's law, the biological basis of neurons, and the potential of neuromorphic chips and event-based vision sensors in advancing AI technology.

# **Chapter 2**

# Overview of SNN for Inference Methodologies

#### 2.1 Introduction

Existing research suggests that ANNs still outperform SNNs in terms of accuracy [9], but the bio-plausibility, power efficiency and small hardware footprint [10] of SNNs continue to attract researchers and manufacturers interested in bringing AI to edge devices, where power consumption and chip area come at a premium.

Hardware circuits differ significantly from software execution, thus several components need to be adapted or even redesigned when tackling the challenge of transitioning from a software proof-of-concept, to a digital hardware implementation. Hardware design emphasizes attention to detail, whether it is the implementation of basic math operators, or the integration of large scale multi-chip systems.

#### 2.2 Artificial Neuron

Artificial neurons are the basic building blocks of artificial neural networks, which are computational models loosely inspired by the human brain. These neurons, also known as nodes or units, are designed to simulate the way biological neurons process and transmit information. In an artificial neuron, multiple input signals are received, each associated with a weight that signifies its importance. The neuron computes a weighted sum of these inputs and then applies an activation function to produce an output. This output is then passed on to subsequent neurons in the network. The most common activation functions include the sigmoid function, hyperbolic tangent (tanh), and Rectified Linear Unit (ReLU). These functions introduce non-linea-rity into the model, enabling the network to learn complex patterns and make sophisticated predictions. Artificial neurons are the fundamental components of various neural network architectures, such as feedforward neural networks, convolutional neural networks (CNNs), and recurrent neural networks (RNNs), which are applied in fields like image recognition, natural language processing, and autonomous systems.

The design of artificial neurons was primarily pragmatic, iterations upon artificial neurons and ANNs sought only to improve inference performance with little regard to bio-plausibility. ANNs meet or even exceed human capability in specific classification tasks, but the field is facing constant hurdles in terms of power consumption and chip area. Many researchers branched out towards mimicking the internal processes of the brain, in hopes of better replicating its energy efficiency and well-rounded performance over innumerable tasks.

## 2.3 Spiking Neuron Models

Spiking neurons represent a more biologically realistic model of neural activity compared to traditional artificial neurons. Inspired by the behavior of biological neurons, spiking neurons communicate through discrete events known as spikes or action potentials. Instead of continuously varying outputs, a spiking neuron emits a spike when its membrane potential reaches a certain threshold. This event-based communication mirrors the way neurons in the brain operate, making spiking neural networks (SNNs) a powerful tool for modeling biological neural processes.

Many researchers in the field of neurophysiology sought, and continue to seek, to identify and quantify the exact processes of the human brain. Significant progress has been made in the area of modelling individual neurons, with many models being proposed based on bio-plausibility, performance, ease of implementation and other criteria.

#### 2.3.1 Hodgkin-Huxley Model

The Hodgkin-Huxley (HH) model is a foundational mathematical framework that describes how neurons generate and propagate action potentials (electrical signals). Developed by Alan Hodgkin and Andrew Huxley in 1952, the model is based on experimental data from the giant axon of the squid and has been highly influential in the field of neurophysiology. It represents the neuron as an electrical circuit with specific components that mimic the biological behavior of ion channels and membranes.

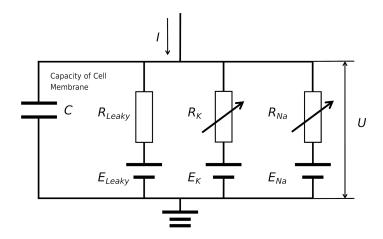

The Hodgkin-Huxley model comprises a set of nonlinear differential equations that describe the dynamics of the membrane potential  $V_m$  in response to ionic currents. These equations are derived from the equivalent electrical circuit of a neuron demonstrated in Figure 2.1.

Figure 2.1: Equivalent electrical circuit of the Hodgkin-Huxley neuron [11].

The neuron is modeled as a capacitor C that takes in the sum of the synaptic currents I, in parallel with a leak resistor  $R_{leaky}$  in order to model the exponential decay of membrane potential U over time. When the potential across the membrane capacitor reaches a threshold value, the neuron fires an output spike and enters the refractory period where its potential drops to the refractory level, often well below the typical resting potential. The model also considers the ionic currents resulting from potassium  $R_K$  and sodium  $R_{Na}$  ions permeating into and out of the membrane [12].

The total current *I* flowing across the membrane is the sum of the capacitive current and the ionic currents, hence it can be described by equation 2.1:

$$I = C_m \frac{dV_m}{dt} + I_{Na} + I_K + I_{Leaky}$$

(2.1)

Where:

- $C_m$  is the membrane capacitance per unit area.

- $dV_m$  is the rate of change of the membrane potential.

- $I_{Na}$ ,  $I_K$ , and  $I_{Leaky}$  are the ionic currents through sodium, potassium, and leak channels, respectively.

Despite its age, the HH model remains one of the most biologically plausible neuron models to date. However, its accuracy comes at the cost of its implementation complexity. Many spiking neural networks implement a subset of the HH model instead, while still achieving favorable results.

#### 2.3.2 Leaky Integrate-and-Fire (LIF)

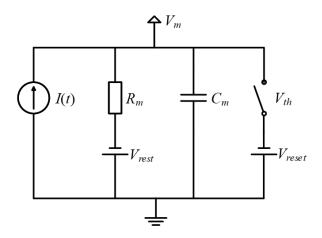

The Leaky Integrate-and-Fire or LIF neuron is a simplification of the Hodgkin-Huxley model, where the effects of the ionic currents are neglected due to their apparent insignificance.

The LIF model reduces the neuron down to just the membrane capacitor and parallel leak resistance, and features similar refractory period mechanics. The differential equation of the LIF neuron model is then given by:

$$\tau_{\text{mem}} \frac{\mathrm{d}U(t)}{\mathrm{d}t} = -\left(U(t) - U_{\text{rest}}\right) + RI(t) \tag{2.2}$$

Where  $\tau_{mem}$  is the membrane's RC time constant.

The circuit parameters were shown experimentally to differ significantly between neurons, even those taken from the same biological samples. The values of the circuit parameters affect the neuron's tendency to spike, and hence alters its output characteristics. Hence, the training process of a spiking neural network involves finding the best

Figure 2.2: Equivalent circuit of the LIF neuron [13].

circuit parameters, or "weights", for each neuron in the network in order to achieve accurate predictions or classifications.

In the context of discrete algorithmic design, both in software and in hardware, it is more convenient to consider the difference equation of the LIF neuron instead [14]:

$$I_i^{(l)}[t] = \sum_j W_{ij}^{(l)} S_j^{(l-1)}[t-1] + \sum_j V_{ij}^{(l)} S_j^{(l)}[t-1]$$

(2.3)

$$U_i^{(l)}[t] = (\beta U_i^{(l)}[t-1] + I_i^{(l)}[t]) \times (1 - S_i^{(l)}[t-1])$$

(2.4)

Since for a Feed-Forward Neural Network architecture (FFNN), the reccurency term is removed, hence further simplification are made to result in equations 2.5 and 2.6

$$I_i^{(l)}[t] = \sum_j W_{ij}^{(l)} S_j^{(l-1)}[t-1]$$

(2.5)

$$U_i^{(l)}[t] = (\beta U_i^{(l)}[t-1] + I_i^{(l)}[t]) \times (1 - S_i^{(l)}[t-1])$$

(2.6)

Where  $W_{ij}^l$  is the weight associated with the particular spike input j of a neuron i in a layer l of a neural network.  $\beta$  is the exponential decay factor of the membrane potential.

#### 2.3.3 Integrate-and-Fire (IF)

The Integrate-and-Fire or IF model further optimizes the spiking neuron down to its most fundamental operation: the accumulation of weights, and firing a spike if a threshold is reached. It is represented by the following difference equations:

$$I_i^{(l)}[t] = \sum_j W_{ij}^{(l)} S_j^{(l-1)}[t-1]$$

(2.7)

$$U_i^{(l)}[t] = (U_i^{(l)}[t-1] + I_i^{(l)}[t]) \times (1 - S_i^{(l)}[t-1])$$

(2.8)

## 2.4 Spike Train Encoding

To make use of SNNs, information needs to be encoded into, or decoded from spike trains. There exist multiple approaches to modulate information onto spike trains, the primary contenders being rate coding and temporal coding, specifically time-to-first-spike (TTFS) encoding. In rate coding, the number of spikes registered over a period of time is proportional to the intensity of the stimulus, while in TTFS more emphasis is placed on the exact time that a given spike was registered, where earlier spikes correspond to stronger stimuli. Rate coding tends to outperform temporal coding accuracy wise, especially in smaller datasets [15]. However, temporal coding continues to be an active topic of research, such as in the work of Mostafa [16] where temporal coding proves to be a potential avenue towards differentiable SNNs that can be trained using conventional gradient-descent techniques.

## 2.5 SNN Topology

The basic architecture of typical SNNs closely mimics that of conventional ANNs, with the only major difference being the structure of each neuron. In fact, a common method of SNN training is the ANN-to-SNN conversion method, where an equivalent ANN is constructed and trained, from which the resulting weights are quantized and deployed to the target SNN [9]. Most SNNs consist of an input layer, an output layer and one or more hidden layers, with certain implementations making use of additional convolutional and pooling layers as is the case in spiking convolutional neural networks or SCNNs [15, 17].

#### 2.5.1 Input Layer

The input layer neurons feed directly into the synapses of neurons in the first hidden layer, and thus the input layer serves more as an interface to distribute incoming spike events without performing any processing. Each neuron in the input layer represents a tangible feature in the input data, for example the intensity of a specific pixel in an image. The generation of input layer spikes occurs either in an event-based sensor, or using encoders that convert data from conventional sensors into spike trains. In

most digital hardware implementations, the input layer is a simply a buffer (queue), constructed using either logic elements or block RAM, that the input spike trains are latched onto before being analyzed further in the hidden layer.

The transmission of sample data to the neural network can severely affect its latency, i.e. the time it takes for the network to guess the correct output after being fed an input sample. Multiple interfaces exist for connecting FPGAs either to computers or even to sensors producing live data, ranging from simple chip-to-chip serial communication protocols such as UART, to high-speed network-based interfaces such as Etherent, to direct communication with a computer's resources using low-level busses such as PCI Express.

#### 2.5.2 Hidden Layer

The hidden layer neurons perform feature extraction, which is the identification of relevant abstract attributes in the incoming data in order to make a prediction or classification. Feature extraction is achieved through a linear combination of input data and weights obtained during the training process.

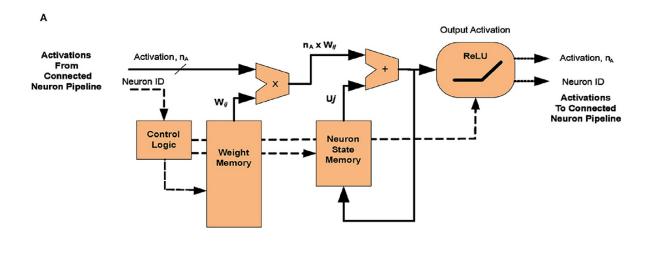

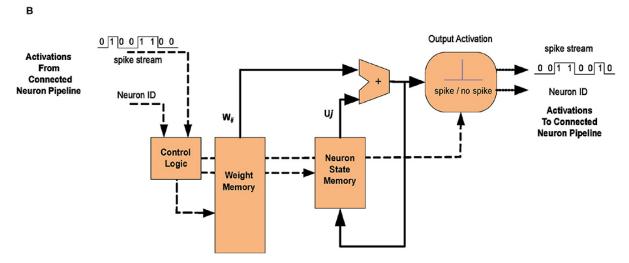

In conventional ANNs, the combination of input data with the weights of all the neurons in the layer can be mathematically interpreted as a matrix multiplication, the latter itself is a series of vector dot products performed over the various rows and columns of inputs and weights respectively. Finally, at the heart of the dot product is the multiply-and-accumulate operation (MAC) which multiplies corresponding elements in each vector and adds up each result in a running summation. While hardware circuits generally benefit from increased concurrency by performing multiple tasks in parallel, multiplication is considered a relatively expensive operation. Care must be taken when designing hardware multipliers by balancing multiple constraints such as latency, chip area, power consumption and portability of designs. The complexity of the design is exasperated when attempting to implement more parallel multipliers.

In contrast, the binary nature of spike inputs in an SNN allows us to completely bypass this problem, reducing the MAC operation down to a conditional accumulation of weights, based on the existence or lack of a spike at a given weight index [18]. The design of such accumulation process is trivial, especially when coupled with equally simple numerical representations. In an SNN, the accumulated weights are added to the membrane potential of the neuron, each neuron then makes a decision on whether to spike or not in the current time-step based on whether the new membrane potential crosses a preset threshold. The membrane potential of spiking neurons is reset to zero, it can also be reset to a level below zero in order to emulate the refractory period present in biological neurons.

When IF neurons are used, the new membrane potential is stored directly to some

Figure 2.3: (A) Typical Artificial neuron pipeline (B) An equivalent Spiking neuron system [18].

form of state memory, often implemented in block RAM, so that it can be used for spike calculation in the next time-step. LIF neurons operate in mostly the same principle, with an extra added step of multiplying by a decay factor  $\beta$  before memory write-back. The decay factor depends on the time-step, hence in variable time-step systems a look-up table is often used to fetch values from an exponential function. Some optimizations were proposed, such as approximating the exponential decay with an arithmetic right shift, which was implemented in the modified LIF neuron by Reddy at al. [19].

Hidden layer neurons typically feature a large number of input connections, a numerical weight value is assigned to each input as part of the training process. The storage of the weight matrix is an important design decision with impacts on both performance and power consumption. The naive approach would be to encode the weights directly using distributed RAM (i.e. within the logic fabric), this allows multiple access of the stored weights and can improve parallelism in theory, bringing the architecture closer to memory-in-compute levels of latency. But this approach is not

scalable for non-trivial neural network. Instead, either on-chip block RAM or off-chip DRAM are used to store the weights, granting much higher flexibility when it comes to neuron counts.

Multiple SNN implementations have experimented with different neuron counts and even multiple successive hidden layers, such as in the work of Sankaran et al. [20] which reveals that increasing neuron counts in the hidden layers of an SNN can help improve accuracy, but with diminishing returns relative to significant increases in resource utilization. For image classification tasks, some SNNs incorporate additional convolutional layers like in the work of Zhang et al. [17], where input spikes are grouped into 2D spike maps and then convolved by a fixed kernel, the results of this operation are further aggregated into pooling layers, which down-sample the dimensions of input data while retaining important information.

#### 2.5.3 Output Layer

The final layer in a neural network is the output layer, with neuron counts corresponding to the number of possible classification outcomes, the output of each neuron represents a likelihood that the associated classification decision is the correct one. For example, in digit recognition tasks, ten neurons are used, each neuron corresponding to a specific digit ('0' through '9'). Contrary to ANNs, which typically employ some form of a "softmax" function to extract outcome probabilities, SNNs were combined with a variety of output decoding techniques, often corresponding to the encoding scheme used to generate the input spike trains in the first place. For rate coded SNNs, the most likely output is that which corresponds to the highest frequency spike trains, while in TTFS SNNs, the first output neuron to spike is considered the winning output.

The design of output layer neurons tends to be identical to that of hidden layer neurons, but one alternative approach involves the use of non-spiking neurons on the output layer. These neurons accumulate their weights onto the membrane potential as is the case with the aforementioned hidden layer neurons. However, their membrane potential is allowed to grow beyond the spiking threshold without any reset. This approach is not present in biological neurons, but allows for easier training as membrane potential growth features less discontinuities than spike activations. The winning neuron in this approach is simply that with the highest peak recorded membrane potential.

### 2.6 Address Event Representation

The spike-train communication between neurons within an SNN can be modelled by digital systems with relative ease. Rather than receiving multi-valued (bit vector) inputs from pre-synaptic neurons, spiking neurons operate with single-bit inputs, each

input can only be either 0 (no spike) or 1 (spike). The vast reduction in the required data lines not only reduces gate count and routing cost, but also opens the door to alternative techniques of spike transmissions.

Many event-based sensors have adopted the Address Event Representation (AER) protocol, where instead of assigning a unique bit input coming from each neuron, the AER protocol transmits the address or index of the pre-synaptic neuron that spiked at any given moment, ignoring any neurons that did not spike [21]. In effect, this allows the neuromorphic system to simply skip weight calculations for non-spiking neurons, vastly improving efficiency and bio-plausibility. The on-demand nature of neuromorphic systems corresponds to reduced switching in an equivalent digital system, a key strategy in reducing power consumption. Finally, the AER protocol can be scaled up to arbitrary neuron counts with a mere logarithmic increase in the required bit width for transmission, making larger neuron layers more feasible.

Figure 2.4: Address Event Representation for chip-to-chip communication. [22]

### 2.7 Spatio-Temporal Data

The inner workings of the brain are directly influenced by the spiking-nature of our various senses, including our sense of sight as it is more event-oriented in nature rather than behaving like a conventional digital camera. Even when passively observing a static scene, the subtle timing differences in spike events registered in the eyes are of utmost significance to the human vision system. Replicating the brain's processing prowess necessitates the interpretation of the world's data the way a brain would experience it.

#### 2.7.1 Conventional MNIST

The MNIST (Modified National Institute of Standards and Technology) dataset is a collection of 28x28 pixel grayscale images depicting hand-written digits, it was first proposed and used by LeCun et al. [23] as a filtered variant of the US NIST dataset. The dataset is widely used for testing various digit recognition techniques, including both DSP algorithms and machine-learning-based approaches.

The MNIST dataset only offers a spatial component and lacks any temporal information, but through its popularity among the research community, it serves as a benchmark for evaluating ML vision models under development, and comparing their accuracy against existing models. This implored researchers in the area of neuromorphic computing to adapt the dataset into spatio-temporal (event-based) formats, with different approaches being explored across the literature.

#### 2.7.2 Event-based MNIST

The early development of neuromorphic computing systems was stunted by a shortage of neuromorphic datasets to train and test on. A common approach to bypass this problem is to generate that data synthetically by converting conventional datasets into event-based datasets, such as the case of Sequential MNIST [24]. However, the performance disparity between ANNs and SNNs is often attributed to the disadvantage that SNNs face by processing data that is not natively suitable for them [25]. Hence, development efforts were directed towards the native generation of neuromorphic datasets, these datasets were often open-sourced in hopes of reinvigorating SNN research.

Event-based (spiking) datasets remain relatively sparse, but the technology behind them continues to develop. A recent development by See et al.[26] involved the use of tactile (touch) events rather than vision, culminating in the spiking-tactile-MNIST dataset. Pixels from MNIST samples were replicated by touch events recorded on a "taxel" (tactile pixel) array constructed using a piezo-resistive thin film, a relatively common material used in pressure and strain gauge sensors. This approach aims to improve the training of high-precision robots, but the time domain sparsity of touch events could increase latency for computer vision systems beyond acceptable levels.

Advancements in event-based camera sensors led to the creation of natively event-based image datasets such as MNIST-DVS [27], where traditional MNIST samples are moved on a computer monitor, and recorded by a fixed dynamic vision sensor into spike trains. This approach was further developed for NMNIST [28].

#### 2.7.3 Neuromorphic-MNIST

The Neuromorphic MNIST, or N-MNIST, is a neuromorphic vision dataset containing MNIST samples recorded using a dynamic vision sensor. The dataset can be considered to be an evolution of MNIST-DVS, but its experimental setup was significantly altered.

MNIST samples were displayed on a computer monitor, but they were left static. Instead, the DVS itself is moved against the screen in a periodic manner using a custombuilt pan-tilt mechanism [28]. This configuration more accurately imitates micro-saccades in the human eye, which are involuntary micro-movements believed to counteract visual decay when fixating on static objects [29]. This approach also eliminates certain artifacts in the data due to the monitor's refresh behavior.

Figure 2.5: Digit 0 sample from the N-MNIST dataset.

Each sample in NMNIST is composed of three saccades, each saccade lasts about 100 milliseconds and consists of spike recordings of DVS pixel activation and deactivation events, with a spiking pixel resolution of 34 by 34. Figure 2.5, shows a sample of digit 0, after the accumulation of events for each of the three saccades. Each event is encoded as an (x, y, t, p) tuple, where x and y are the image coordinates of the event, t is the timestamp at which the event occurred (where time starts at the beginning of the current sample recording), and p is the polarity of the event: "On" events are denoted by 1, while "off" events are denoted by a 0. Pixels that did not experience a change in the current timestamp are not recorded, significantly reducing the required bandwidth for visual data transmissions.

# 2.8 Numerical Representation

Digital hardware ultimately deals only in zeroes and ones, and the basic laws of boolean algebra. To do conventional math, it needs to be framed in the context of binary values. The framing or representation of real numbers is of particular nuance, as many representational systems exist, each with their own advantages and hurdles.

#### 2.8.1 Floating-point numbers

Floating point numbers are a way to represent real numbers in computing, allowing for the representation of a wide range of values with varying degrees of precision. The IEEE 754 standard is the most widely adopted method for encoding these numbers, ensuring consistency and accuracy across different computer systems and applications. This standard specifies the format for floating-point arithmetic, detailing how numbers are stored in binary using three components: the sign, the exponent, and the mantissa (or significand). By allocating specific bits to each of these components, IEEE 754 allows for the representation of both very large and very small numbers, maintaining precision within a defined range. Additionally, the standard outlines rules for rounding, handling exceptions such as overflow and underflow, and defining special values like NaN (Not a Number) and infinity.

IEEE754 provides a great deal of flexibility and features used across different domains. But a full implementation of the exact standard that accommodates such features is a monumental task typically assigned solely to venerable hardware IP design companies. Such complex standard will also tend to consume more hardware resources and have higher latencies compared to regular integer arithmetic.

#### 2.8.2 Fixed-point numbers

Fixed-point representation is an alternative numerical format for performing arithmetic using fractional numbers without the need for dedicated floating-point hardware.

The principle of fixed-point representation is to interpret a regular two's complement binary number, which would typically represent an integer, with a virtual decimal point. This decimal point creates an inherent shift of the powers of two represented by the individual bits, meaning that a portion of the integral range is traded for that of a fractional range represented by negative powers of two. In this report, we default to the Q notation for denoting fixed-point representations, first defined by Texas Instruments [30]. The Q notation uses the format "Q(n-S).S" where n is the number of bits in the entire binary string, and S is the number of bits allocated for the fractional part.

An n-bit binary string in the integer two's complement format can represent any whole number in the range of  $\{-2^{n-1} ... 2^{n-1} - 1\}$ , with a step size between any two consecutive numbers (i.e. the resolution) of the smallest available power of two in the representation, that being  $2^0 = 1$ . When fixed-point format is employed, the aforementioned range is right shifted by the chosen number of bits allocated for the fractional part. The right shift is equivalent to a division by  $2^S$ , resulting in a new representational range of  $\{-2^{n-S-1} ... 2^{n-S-1} - 2^{-S}\}$ , with a minimum resolution of  $2^{-S}$ . For a concrete demonstration, an example of unsigned 8-bit integer binary and unsigned Q4.4 fixed-

Figure 2.6: Example of fixed-point number representation [31].

point representations is shown in Figure 2.6.

The primary advantage of using fixed-point format is the fact that the decimal point is entirely virtual. There is no additional encoding overhead, and well-established integer arithmetic circuits (both unsigned and two's complement signed) can be reused without any modification, save for the re-scaling of any constants being used, resulting in faster performance, lower power consumption and smaller chip area compared to a floating-point system for a given clock frequency. The main disadvantage of fixed-point format is the limited range of representation compared to floating-point formats, in which as their name suggests the decimal point is free to move to better accommodate the numerical data being processed, with decent resolution and encoding efficiency across a wide spectrum of magnitudes.

#### 2.9 Summary

In this Chapter, we described the different techniques and methodologies used in the topology of Spiking Neural Networks for inference. We also introduced a widely used spatio-temporal benchmark dataset; Neuromorphic-MNIST. In the next chapter, we will derive and explain our proposed design for the implementation of this neural network type on a hand written digit classification task.

# **Chapter 3**

# Design and Implementation of a Hardware SNN

## 3.1 Introduction

The implementation of SNNs on hardware is still a relatively immature field, the literature showed that there is often still points that can be improved upon [32]. We hope to address some trouble points with our own SNN design, which aims to be compact, power efficient and highly portable and adaptable. This chapter goes into detail about the design of the spiking neuron itself, and all the needed infrastructure and supporting logic that is used to ensure fault-free context-switching and high-accuracy inference capabilities.

#### 3.2 Design of SNN Architecture

The key design choice of our SNN is the use of one physical neuron for each layer (hidden and output layers). Through the use of time-division multiplexing and context-switching, a single neuron circuit can be used to perform the needed calculations for all the neurons in the neural layer. This neuron shall be contained within a "wrapper", which keeps track of the network neuron that is currently executing, and managing its state data accordingly, the wrapper in effect represents one layer in the neural network. We also designed an output encoder that converts the output layer's weight accumulation activity into tangible inference predictions. We will also define an abstraction that represents the entire neural network, whose role is to assign time slots to the network layers to ensure that the processing occurs in the correct order and with no shared resource contention.

#### 3.2.1 Neuron Model

The neuron model is the fundamental processing block of our SNN. Two neuron designs were conceived, an IF neuron and a LIF neuron, where the latter is functionally an extension of the former. Given the simplicity of the accumulation process, more emphasis was placed on the spike-train/weight-procurement pipeline.

#### • IF Neuron

The primary function of the designed Integrate-and-Fire Neuron is to accumulate weights and generate an output spike. Initially, the neuron subsystem loads the membrane potential from the previous time frame  $U_i^{(l)}[t-1]$ . It then accumulates the weights  $W_{ij}^{(l)}$  of the received spike indices for the current time frame, in addition to the previously loaded potential. For hidden layer neurons, an output spike is generated when the accumulated potential exceeds the set threshold potential, before resetting to zero. Simultaneously, a valid signal is asserted to

indicate the completion of neuron processing, enabling the transition to the next neuron and update of the state table. For non-firing readout layer neurons, the action potential is used as an output instead. The architecture of the IF neuron is shown in Figure 3.1, it should be noted that for the case of the IF neuron,  $\beta$  is taken as one and no multiplication is required.

Figure 3.1: IF/LIF neuron model architecture.

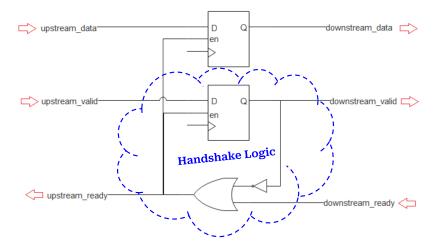

The ready-valid handshake is used throughout the design, the key principle of the handshake is that data transfer can only occur when the sender has valid data, and the receiver is ready to receive said data at the same time. This allows for composable interface design with minimum assumptions. The efficiency of handshakes is improved by including a one element buffer to help smooth out spike index and weight transfers, and avoid data stalls. The architecture of the handshake logic cloud introduced in this neuron model design shown in Figure 3.1, is demonstrated in Figure 3.2. The same handshake circuit is used for the rest of different modules design.

Figure 3.2: Handshake logic architecture.

#### LIF Neuron

With the establishment of the IF neuron design, we turned our focus to the LIF neuron. The LIF neuron features a near identical architecture to that of the IF neuron, except for an added multiplier that multiplies the resulting membrane voltage output by a decay factor  $\beta$ .

The  $\beta$  factor was designed as a constant. To accommodate this, the input spike indices are grouped into frames such that they have an equal temporal spacing between successive frames, eliminating the need for implementing an exponential function block in hardware as we only require one specific value for our test dataset. We also refrained from utilizing bit-shift techniques that approximate exponentiation in order to have more control over the exact value of  $\beta$ .

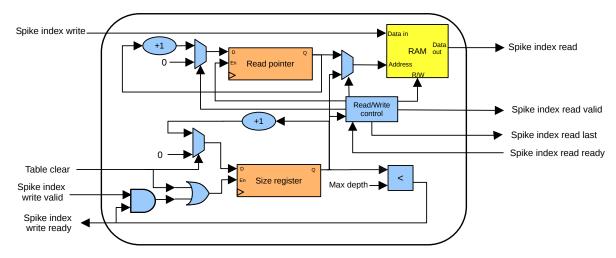

#### 3.2.2 Spike Index Table Design

The spike index table is the backbone of our spike-stream oriented architecture. It serves as a buffer that stores spike events occurring in a given layer in the address-event representation (AER) format, meaning that it instead of referencing all the neurons in the layer, it is meant to store only the indices (addresses) of the neurons that spiked in the previous time frame.

The table will provide a ready-valid interface for reading and writing spike indices. The indices are read in the same order they were written, which would suggest a First-In-First-Out (FIFO) principle of operation. But our table differs from a typical FIFO memory in that the elements that are read are not discarded; once all the indices in the current frame have been read, the table will roll over and begin re-transmitting the same set of indices from the beginning. This table was designed to complement the neuron model, which itself is designed to stop reading spikes events if it detects the "last input spike" flag. Evidently, the table will need provide said flag, indicating the end of a frame. The table will also need a control signal to entirely clear the table in preparation for a new frame.

Our proposed design takes the FIFO inspiration and tweaks it to fit our requirements. It consists of storage RAM, a memory read pointer, a size register and additional glue logic. The size register is incremented on every index write and is used to check that the table's contents do not exceed the set capacity, and it also doubles as a memory write pointer as it always points to the next available RAM address. The read pointer is similarly incremented on every index read, but when the read pointer coincides with the write pointer, the read pointer resets back to zero in order to restart the reading order. A summary of the architecture is shown in Figure 3.3.

Figure 3.3: Spike index table architecture.

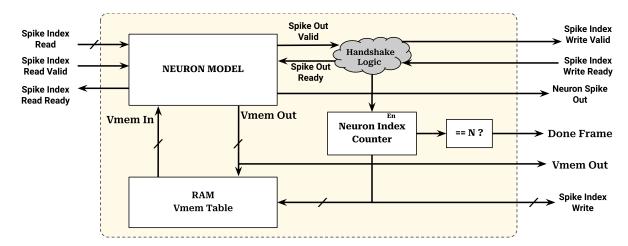

#### 3.2.3 Neuron Wrapper Design

The neuron wrapper module encloses the bare neuron model, and implements additional control logic for loading and storing neuron state. The wrapper loosely represents a neuron layer in our architecture, as it contains a state table for storing the membrane potential voltages of all neurons in the layer. A "neuron index" is used to identify and keep track of the "virtual" neuron that is currently performing operations. This allows the re-use of one instance of the neuron model to perform activation calculations for every virtual neuron in the layer.

The wrapper takes in a stream of spikes provided by a spike index table, the aforementioned spikes are a result from the output activations of the preceding layer. The weight RAM interface passes through the neuron wrapper to the neuron model, and the output spike ports in turn pass from the model to the rest of the system through the wrapper. All interfaces on the neuron wrapper's ports follow the handshake principle in accordance with the rest of the design. The output spike handshake is of particular interest as it can be used to stall the wrapper's execution flow if necessary.

The input spike stream goes through the neuron model, which accumulates the appropriate weights. The neuron only specifies the weight index corresponding to a particular spike input, while the wrapper selects the exact memory region in which the current neuron's weights are mapped, this is accomplished by using the neuron index as the "high-order" component on the weight RAM address bus, the wrapper also sets the upper address bits to match the designated layer. At the end of output calculation, the neuron asserts "spike out" valid. The wrapper then stores the resulting membrane potential in the appropriate state table location. Simultaneously, the wrapper also checks whether the downstream spike consumers are ready to sample the spiking event, before incrementing the neuron index register and resetting the neuron model. It is crucial that the output spike handshake is detected before attempting to increment

Figure 3.4: Neuron wrapper block diagram.

the neuron index, as the spiking event is transmitted not by the spiking bit, but by the index of the neuron that spiked, in accordance of the address-event representation protocol. Through the cyclical action of the index table, the same spike stream is processed by the following virtual neurons. This continues until all neurons in the layer are finished with their output activation calculations, upon which the neuron wrapper asserts the "done frame" signal, indicating that it is ready to move on and process the next stream of input spikes.

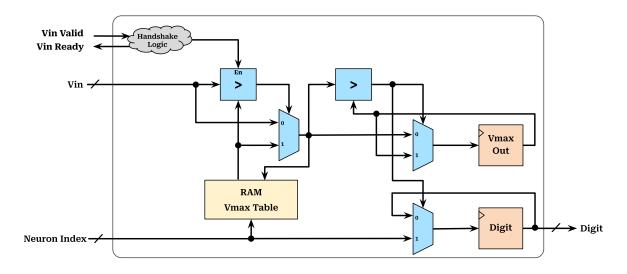

## 3.2.4 Output Encoding Module Design

The designed maximum membrane potential-based output encoding module compares the output action potentials of all readout layer neurons and selects the maximum value. The inferred output digit is simply the index of the neuron corresponding to this maximum value.

Figure 3.5: Output Encoding Module Diagram

#### 3.2.5 Neural Network Design

The aforementioned building blocks of our design could only perform their tasks if they are connected correctly, with careful consideration to the control of processing flow starting from the input frame all the way to the predicted output. The required interconnections and glue logic are primarily implemented within the network module which as the name implies, represents the overall neural network and thus encapsulates the neuron layers, the index tables in between them and the output decoder.

The input layer consists of a spike index table, which then connects to the hidden layer represented by a neuron wrapper. The resulting spikes from hidden layer neurons are stored by their neuron indices to a spike index table, where the neuron index is written only if a spike is registered at the current time frame. This leads to the output layer wrapper which performs additional processing and has a neuron count equal to the number of output classes. Instead of a spike index table, an output encoder is instead connected to the output layer in order to determine which output class was predicted by the neural network. The block diagram of the neural network is shown in 3.6.

Figure 3.6: Network diagram.

The network entity governs the execution flow of the inner modules using a finite state machine or FSM, which ensures the correct sequence of processing steps between the different layers.

## 3.3 Implementation

After establishing the basic design of the hardware SNN and its components, we will go through the details of implementing each component, and present the reasoning behind our design choices along the way.

#### 3.3.1 Targeted Application

To validate our SNN design, we settled on a handwritten digit classification task, specifically adopting the Neuromorphic-MNIST benchmark dataset. This initial assessment aimed to ensure the functionality and reliability of our SNN implementation.

The samples of N-MNIST consist of pixel activation and deactivation events recorded on a 34x34 grid, leading to a total dimension of 2312 elements, which maps directly to a neural network with an input layer of 2312 neurons. Said network will naturally require 10 output neurons, each neuron corresponding to an output digit class.

As a continuation of previous SNN work done on the same dataset by Bouanane et al [14], we opted to use one hidden layer of 200 neurons, which allowed us to reuse the weights the authors obtained from training, and helped us focus on the hardware inference. The aforementioned research also came to the conclusion that using a value of  $\beta=0.967$  for the decay factor of LIF neurons produces the most ideal results in the N-MNIST dataset.

## 3.3.2 Tools and Equipment

#### FPGA Board

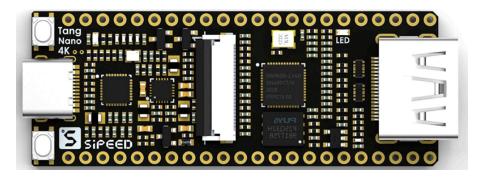

The Sipeed Tang Nano 4K is a development board based on the Gowin Little-Bee GW1NSR-4C FPGA. It includes an on-board JTAG programmer and debugger, camera interface, HDMI port, a 27MHz crystal oscillator and a whole host of components needed for the proper functioning of the FPGA chip.

Figure 3.7: Picture of the Sipeed Tang Nano 4K FPGA development board.

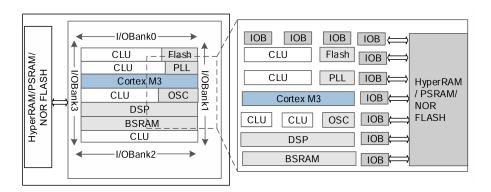

#### Gowin LittleBee GW1NSR-4C

The Gowin LittleBee series is a family of low-cost FPGA chips based on LUT4 logic elements, with LUT counts ranging from about a thousand to over 20 thousand look-up tables. Gowin FPGAs typically feature a variety of additional components packaged within the same chip. The GW1NSR-4C in particular features 4608 LUTs, 256Kbits of integrated flash memory for non-volatile bitstream storage, 180Kbits of block SRAM, two phase-locked loops (PLLs) for clock frequency multiplication, an ARM Cortex M3 processor core for System-on-Programmable-Chip (SoPC) applications, dedicated hardware multipliers (referred to as "DSP resources"), as well as an 8MiB array of HyperRAM memory.

Figure 3.8: Architecture overview of the GW1NSR-4C [33].

## • HDL Simulation & Synthesis

To perform HDL synthesis for our FPGA, we used the vendor provided tool named Gowin EDA. It provides basic code editing and synthesis for a variety of VHDL and Verilog standards. However, it unfortunately does not provide a simulator.

The absence of a simulator was rectified with the combination of open-source software: GHDL for VHDL-2008 simulation, and GTKWave for displaying simulation waveforms. Both tools are invoked through the terminal using documented commands and parameters, these commands were grouped into scripts for more efficient development.

The bulk of code editing was done using Visual Studio Code thanks to the TerosHDL extension, which provides VHDL syntax highlighting and linting, as well as helpful documentation features like the generation of port diagrams for entities.

#### • Software Libraries

Given the popularity of Python in machine learning circles, various libraries and frameworks have been developed for that purpose. We used the PyTorch library to process the pre-trained weights and test the inference of our network. We

also used the Tonic [34] library to obtain and process the Neuromorphic-MNIST dataset.

#### 3.3.3 Planning and Preliminary Testing

Before advancing to hardware experiments, it was crucial to first evaluate the model through software emulation. This step was essential to ascertain the accuracy and effectiveness of our network design. The emulation process provided a controlled environment to conduct preliminary tests and identify potential issues without the complexities introduced by hardware constraints.

A significant part of this preliminary analysis involved converting the neural network's weights. These weights, obtained through training, were initially in a 32-bit floating-point format. For implementation on an FPGA, these weights needed to be converted to a fixed-point format, a format which the neuron model in particular is designed based on. Determining the best fixed-point format for our application was the core objective of building the software model.

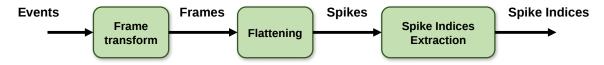

#### Dataset Wrangling

The N-MNIST dataset is based on individual spike events, each sample consists of a series of (x,y,t,p) tuples with no apparent image-like structure. Thus, we performed some pre-processing as shown in Figure 3.9. The discrete spike events of each sample are sorted into "bins" using Tonic's frame transform. This results in two 34x34 frames, one representing a history of pixel-on events in a given time-window, and the other represents a history of off-events in the same window. The frames are combined and then flattened to match the input structure of the neural network. Finally, the spike indices are extracted from the flattened frames and stored as ASCII binary strings into a text file, we pre-pended the spike indices of each frame with the number of spike indices in that frame.

Figure 3.9: N-MNIST pre-processing pipeline.

Depending on the time window, the Tonic frame transform can result in multivalued (non-binary) spikes due to event overlap, we remedied this by repeating the spike index in proportion to its magnitude.

#### SNN Software Model

To test the basic architecture and weights, we constructed a software model for our SNN in Python. The pseudocode for our model impelementation in python is represented in Algorithm 1, where it consists of two parts, first the input data is passed through hidden layer computation before proceeding to the output layer neurons processing.

#### • Weights conversion

The process of converting model weights into fixed-point equivalents starts with a floating-point tensor input. Each entry in the tensor input is multiplied by  $2^S$  (where S is the number of bits assigned to the fractional part) and then rounded to the nearest integer. The total desired number of bits are masked out using bit manipulation techniques, obtaining a 16-bit value for example would require bitwise-AND'ing the integer with the hexadecimal value  $0 \times FFFF$ . The shifted integer is then formatted as a binary string and written to a memory initialization file that can be used with VHDL testbenches; the process is repeated for all the weights in a given layer. For testing purposes, we also converted the resulting fixed-point weights back to floating-point in PyTorch tensor format in order to examine the effects of the conversion on accuracy, this was accomplished by casting the whole part of the fixed-point format into floating-point, and then dividing the fractional part by  $2^S$  before adding it back into the casted floating-point number.

Table 3.1: Accuracy summary for weight conversion

| Weight format | IF     | LIF    |

|---------------|--------|--------|

| FP32          | 97.50% | 97.65% |

| Q2.6          | 19.90% | 21.35% |

| Q2.14         | 97.24% | 97.31% |