People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

University M'Hamed BOUGARA – Boumerdès

# Institute of Electrical and Electronic Engineering Department of Electronics

Final Year Project Report Presented in Partial Fulfilment of

the Requirements of the Degree of

# 'MASTER'

# In Electrical and Electronic Engineering

# **Option:** Computer Engineering

Title:

# Hardware-In-The Loop simulation of Inverter's Control Unit based on OPAL-RT and FPGA

Presented By:

- BOUYAHIAOUI Hadjer

Supervisor:

Co-Supervisor:

Dr. AZZOUGUI Y.

**Dr. BENMERABET M.S.**

Registration Number:...../2023

# • Abstract:

Due to the increasing cost of power electronics switches and the cost of repairing failures of power electronics systems, semi-physical simulation technology such as hardware-in-the-loop (HIL) simulation is increasingly being used as an important design, development, and testing step in the manufacturing process of many power electronics systems. In this project, HIL simulation for an FPGA-based controller of a three-level power inverter was performed and tested using the OPAL-RT HIL simulation tool. First, an FPGA-based controller for a single-phase three-level inverter was designed and tested. Three different PWM digital control circuits (Bipolar SPWM, Unipolar SPWM, and SHEPWM) were designed from scratch using VHDL. Then Hardware-in-The-loop testing of the controller was implemented using the RT-LAB HIL testing platform. To emulate the three-level inverter, a simulation model based on MATLAB<sup>®</sup>/Simulink software and Simscap blocks was designed to perform real-time simulation testing of the FPGA-based controller. The obtained test results were compared to pre-simulated results using MATLAB<sup>®</sup>, the results have shown that the total harmonic distortion (THD) of the difference controlling circuits decreases gradually and thus helps improve the power quality of the inverter, the final HIL results were acceptable and close to the expected and real results especially with the SHEPWM where we obtained errors less than 7% between expected and HIL results.

**Keywords:** Pulse Width Modulation (PWM), Total Harmonic Distortion (THD), Hardware In the Loop (HIL), Unipolar & Bipolar Sinusoidal Pulse Width Modulation, SHEPWM, VHDL, FPGA, Inverter.

# • Acknowledgement:

In the name of Allah, the Most Gracious and the Most Merciful Alhamdulillah, all praises

to Allah for the strengths and His blessing in completing this project.

I would like to express my deepest and sincere gratitude to my project Supervisor

Dr. AZZOUGUI Yasmina, and Co-Supervisor Dr. BENMERABET Mohamed Salim, it was a great privilege and honor to work and study under your supervision. Thank you very much.

I would give special thanks to Mrs CHIKH Wafa and Mr BOUKERDOUN Haithem.

Finally, I am infinitely grateful to my family members, particularly my parents and my aunt Hafida DEBBAGHI for their patience, unwavering support, continuous encouragement, and belief in me throughout my whole life. I would have never made it this far without them beside me every step of the way.

# • Dedication:

I have a great pleasure to dedicate this modest work То Dear Father, my Beloved Mother, my To my Dear Sisters, Brother, Aunts, Uncles, and Cousins То all Friends my And to all with whom I spent wonderful moments And I do appreciate you taking the time to read this work, dedication my SO is you. to

## Hadjer BOUYAHIAOUI

| • Table of Content:                                                   |     |

|-----------------------------------------------------------------------|-----|

| Abstract:                                                             | i   |

| Acknowledgement:                                                      | ii  |

| Dedication:                                                           | iii |

| Table of Content:                                                     |     |

| List of figures:                                                      |     |

| <ul> <li>List of Tables:</li> </ul>                                   |     |

| <ul> <li>Abbreviation:</li> </ul>                                     |     |

|                                                                       |     |

| General Introduction:                                                 |     |

| Chapter I. Theoretical Background and Literature Review               | Z   |

| I.1. Introduction:                                                    | 3   |

| I.2. Overview of power electronics and inverter technology:           |     |

| I.2.1. History of Power Semiconductor Switches and Power Electronics: |     |

| I.2.2. Inverters:                                                     |     |

| I.2.3. Basic Voltage-Source Inverter's structures:                    |     |

| I.2.3.1. Half-Bridge inverter:                                        |     |

| I.2.3.2. Full-Bridge Inverter:                                        |     |

| I.2.3.3. Multi-Phase Inverter Structure:                              |     |

| I.2.4. Multi-Level Inverter Configuration:                            |     |

| I.2.4.1. Neutral-Point-Clamped Configuration:                         |     |

| I.2.4.2. Flying Capacitor Configuration:                              |     |

| I.2.4.3. Cascaded H-Bridge Configuration:                             |     |

| I.3. Modulation Topologies for 3-level Voltage Source Inverters:      |     |

| I.3.1. Pulse Width Modulation signals:                                |     |

| I.3.2. Sinusoidal Pulse Width Modulation:                             |     |

| I.3.3. Selective Harmonic Elimination Pulse Width Modulation:         |     |

| I.4. Overview of Real Time Simulation:                                |     |

| I.4.1. Model-In-The-Loop simulation:                                  |     |

| I.4.2. FPGA-In-The-Loop simulation:                                   |     |

| I.4.3. Rapid Control Prototyping:                                     |     |

| I.4.4. Hardware-In-The-Loop simulation:                               |     |

| I.4.5. Software-In-The-Loop simulation:                               |     |

| I.4.6. Power-Hardware-In-The-Loop simulation:                         |     |

| I.5. Conclusion:                                                      |     |

| Chapter II. Hardware In the Loop and MATLAB® Simulation Setup:        | 25  |

| II.1. Overview:                                                       |     |

| II.2. FPGA:                                                           |     |

| II.3. Altera Cyclone II DE2 Field Programable Gate Array Board:       |     |

| II.4. OP4510 RCP/HIL Real Time Simulator:                             |     |

|                                                                       |     |

| II.4.1. Overview:                                               |     |

|-----------------------------------------------------------------|-----|

| II.4.2. Op4510 Simulation Platform:                             |     |

| II.5. MATLAB <sup>®</sup> and Simulink <sup>®</sup> Software:   |     |

| II.6. Description of the simulation setup:                      |     |

| II.7. The Single-Phase Full Bridge Inverter Model:              |     |

| II.8. MATLAB® Simulation and Results:                           |     |

| II.8.1. Bipolar SPWM structure:                                 |     |

| II.8.2. Unipolar SPWM structure:                                |     |

| II.8.3. Selective Harmonic Elimination PWM structure:           |     |

| II.9. Hardware Setup of The Experiment:                         |     |

| II.10. Conclusion:                                              |     |

| Chapter III. Hardware In the Loop implementation and Results:   |     |

| III.1. Overview:                                                |     |

| III.2. Quartus II:                                              |     |

| III.3. RT-LAB Software:                                         |     |

| III.4. Description of The Software Setup:                       |     |

| III.5. Building HIL Model on RT-LAB                             |     |

| III.5.1. Overview                                               |     |

| III.5.2. Designing The H-bridge model for HIL simulation:       |     |

| III.5.3. The implementation of HIL simulation in RT-LAB:        |     |

| III.6. The Software designing Setup:                            |     |

| III.6.1. Bipolar Sinusoidal Pulse Width Modulation:             |     |

| III.6.2. Unipolar Sinusoidal Pulse Width Modulation:            | 52  |

| III.6.3. Selective Harmonic Elimination Pulse Width Modulation: | 56  |

| III.7. Results' Discussion:                                     | 59  |

| III.8. Conclusion:                                              | 61  |

| General Conclusion:                                             | lxi |

| Limitations & Future works:                                     | lxi |

| References                                                      |     |

|                                                                 |     |

# • List of figures:

| Figure I-1.1 Interdisciplinary nature and applications obtained from power electronics. [1]                                                                                        | 3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure I-2: Mercury arc rectifier under operation [34]                                                                                                                             | 4 |

| Figure I-3: Timeline of historical events in the power electronics devices evolution. [1]                                                                                          | 5 |

| Figure I-4: (a) Typical voltage-source inverter block diagram and (b) current–source inverter block diagram (c) [30]Z-source inverter [1] indicating input energy storage elements |   |

| Figure I-5: Block diagram of a DC-AC within a system in an abstract point of view                                                                                                  | 6 |

| Figure I-6: Inverter's basic structures diagram                                                                                                                                    | 8 |

| Figure I-7:Half-bridge inverter                                                                                                                                                    | 8 |

| Figure I-8: Switching pattern of half bridge switches along with Voltage waveform across<br>Resistive LOAD                                                                         | 9 |

| Figure I-9:Dead time representation                                                                                                                                                | 9 |

| Figure I-10: H-bridge inverter structure [2]1                                                                                                                                      | 0 |

| Figure I-11: Switching pattern of H- bridge switches and the outputted three level pattern1                                                                                        | 0 |

| Figure I-12: Basic Three Phase Inverter [2]1                                                                                                                                       | 1 |

| Figure I-13: Line-to-line three phase inverter waveform1                                                                                                                           | 1 |

| Figure I-14: (a) A three-level, (b) five-level and (c) seven-level output waveform at fundamental switching frequency. [26]                                                        | 2 |

| Figure I-15: Block Diagram for MLI Configurations1                                                                                                                                 | 2 |

| Figure I-16: Neutral point clamped inverter leg [2]1                                                                                                                               | 3 |

| Figure I-17: Flying capacitor inverter1                                                                                                                                            | 3 |

| Figure I-18:Cascaded H-bridge configuration1                                                                                                                                       | 3 |

| Figure I-19: Block diagram represent PWM Topologies1                                                                                                                               | 4 |

| Figure I-20: Figure show PWM characteristics1                                                                                                                                      | 4 |

| Figure I-21:Bipolar and Unipolar SPWM waveform of Three-level inverter1                                                                                                            | 6 |

| Figure I-22: Generalized three-level SHE PWM waveform. [12]1                                                                                                                       | 7 |

| Figure I-23: Diagram represent the communication in FPGA-In-The-Loop block [40]2                                                                                                   | 0 |

| Figure I-24: Schematic representation of RCP [28]2                                                                                                                                 | 1 |

| Figure I-25: Schematic representation of HIL. [22]                                                                                                                                                                        | 22 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure I-26: Schematic representation of SIL. [22]                                                                                                                                                                        | 22 |

| Figure I-27: Schematic representation of PHIL [22]                                                                                                                                                                        | 23 |

| Figure II-1: Simplified example illustration of a basic logic cell in FPGA [19]                                                                                                                                           | 26 |

| Figure II-2: DE2 Board Top View [35]                                                                                                                                                                                      | 27 |

| Figure II-3: OP4510 Top view [25]                                                                                                                                                                                         | 28 |

| Figure II-4: OP4510 Rear Interface.                                                                                                                                                                                       | 28 |

| Figure II-5: OP4510 V2 Front Interface. [25]                                                                                                                                                                              | 29 |

| Figure II-6: Target Simulator to host computer connection.                                                                                                                                                                | 30 |

| Figure II-7: MathWorks <sup>®</sup> Logo. [40]                                                                                                                                                                            | 30 |

| Figure II-8: Full Bridge Inverter Simulink Model.                                                                                                                                                                         | 31 |

| Figure II-9: Bipolar SPWM control circuit blocks                                                                                                                                                                          | 32 |

| Figure II-10: The Control signals for bipolar SPWM inverter                                                                                                                                                               | 32 |

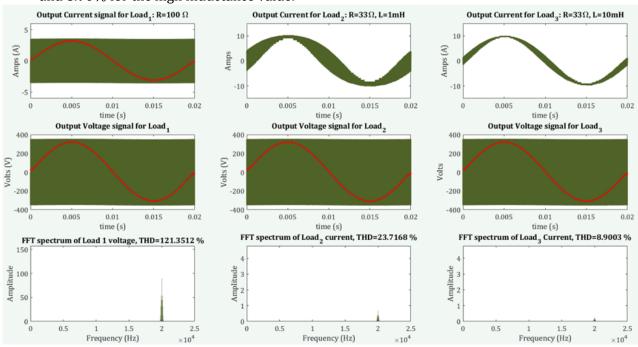

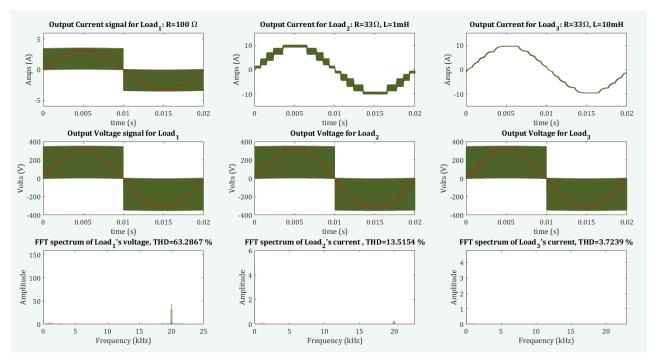

| Figure II-11: Results of MIL simulation with Bipolar SPWM controller using Simulink                                                                                                                                       | 33 |

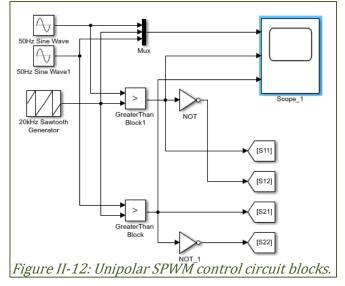

| Figure II-12: Unipolar SPWM control circuit blocks                                                                                                                                                                        | 33 |

| Figure II-13: The Control signals for Unipolar SPWM inverter.                                                                                                                                                             | 34 |

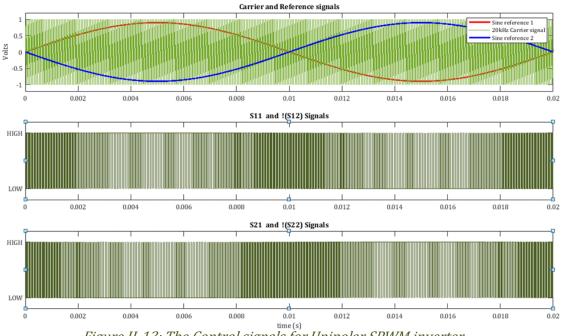

| Figure II-14: Results of MIL simulation with Unipolar SPWM controller                                                                                                                                                     | 34 |

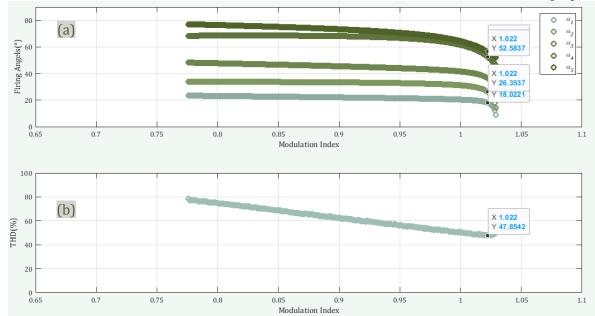

| Figure II-15: Graph represents the data obtained after solving the firing-angles equations<br>Graph represent calculated Firing Angels versus Modulation Index. b) Graph represents<br>Modulation Index versus THD values | -  |

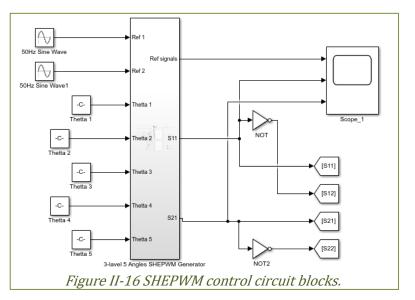

| Figure II-16 SHEPWM control circuit blocks                                                                                                                                                                                | 35 |

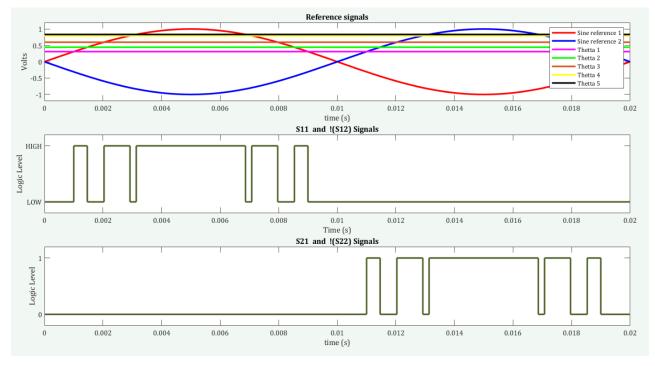

| Figure II-17: The Control signals for SHEPWM inverter.                                                                                                                                                                    |    |

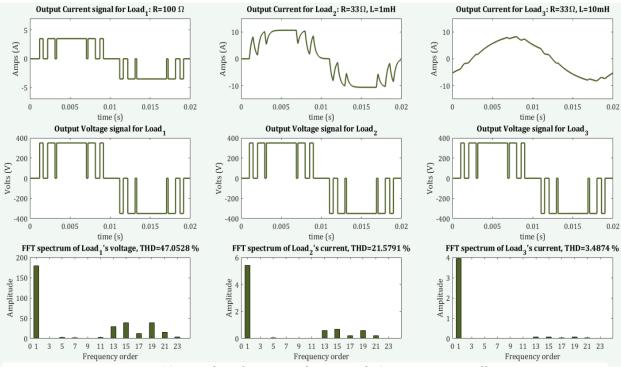

| Figure II-18: Results of MIL simulation with SHEPWM controller                                                                                                                                                            | 36 |

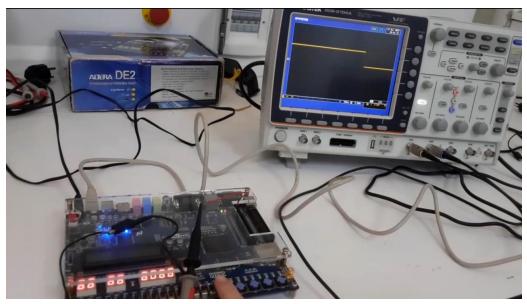

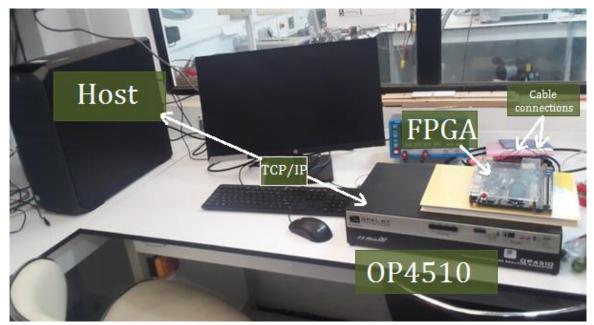

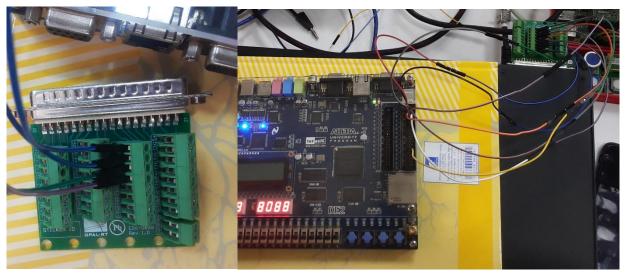

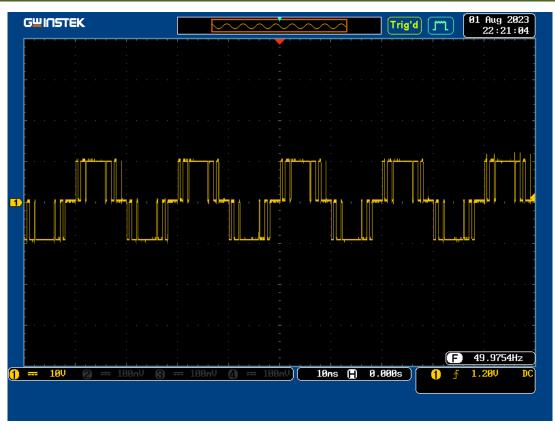

| Figure II-19: Testing FPGA output using oscilloscope                                                                                                                                                                      | 37 |

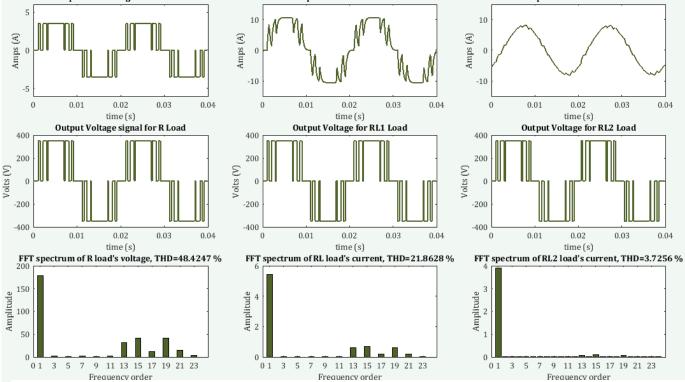

| Figure II-20: The Final Hardware Setup of the experiment.                                                                                                                                                                 | 38 |

| Figure III-1: Quartus II Logo [37]                                                                                                                                                                                        |    |

| Figure III-2: RT-LAB Logo [38]                                                                                                                                                                                            |    |

| Figure III-3: Opal RT simulator's model subsystems.                                                                                                                                                                       |    |

|                                                                                                                                                                                                                           |    |

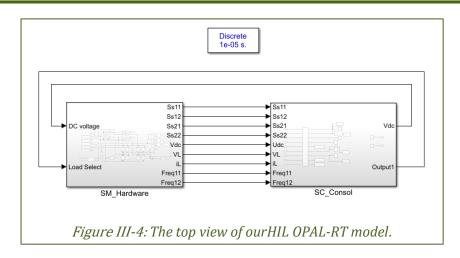

| Figure III-4: The top view of ourHIL OPAL-RT model.                                  | 43 |

|--------------------------------------------------------------------------------------|----|

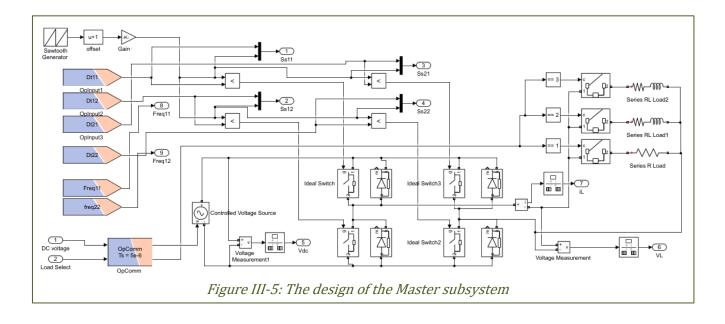

| Figure III-5: The design of the Master subsystem                                     | 44 |

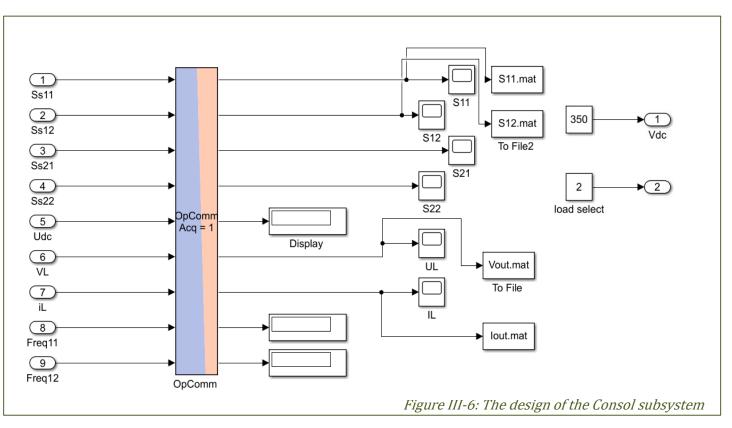

| Figure III-6: The design of the Consol subsystem                                     | 45 |

| Figure III-7: RT-LAB main interface                                                  | 45 |

| Figure III-8: Bipolar SPWM circuit schematic                                         | 46 |

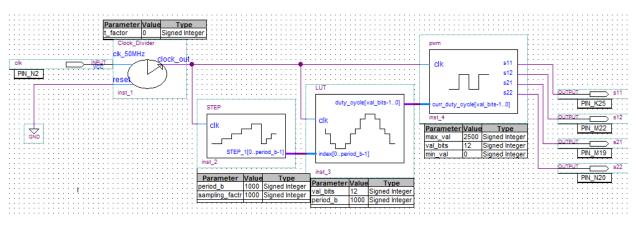

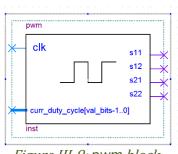

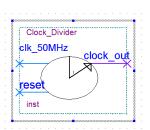

| Figure III-9: pwm block diagram                                                      | 47 |

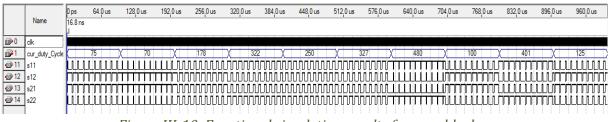

| Figure III-10: Functional simulation results for pwm block                           | 47 |

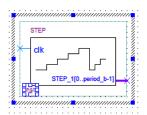

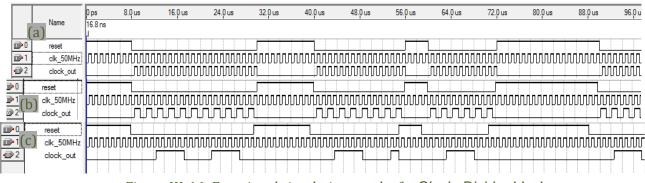

| Figure III-11: Block diagram of STEP Block                                           | 47 |

| Figure III-12: Functional simulation results of STEP Block                           | 47 |

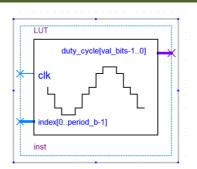

| Figure III-13: LUT block diagram                                                     | 48 |

| Figure III-14: Functional simulation results of LUT block                            | 48 |

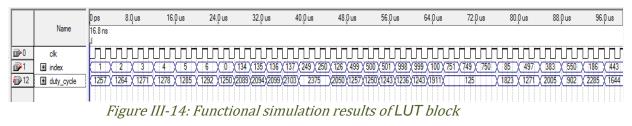

| Figure III-15: Clock_Divider Block diagram                                           | 48 |

| Figure III-16: Functional simulation results for Clock_Divider block                 | 48 |

| Figure III-17: Quartus II Pins Assignment settings table                             | 49 |

| Figure III-18: Gating signals generated from the FPGA-Based controller               | 50 |

| Figure III-19: waveform of the Output voltage across Load_1                          | 50 |

| Figure III-20: Results of HIL simulation with Bipolar SPWM controller                | 51 |

| Figure III-21: Unipolar SPWM circuit schematic                                       | 52 |

| Figure III-22: Functional simulation results of pwm Block                            | 52 |

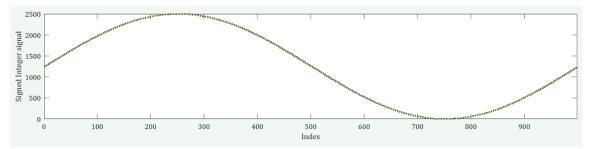

| Figure III-23: Graph represent the samples stored in ULUT table versus their indices | 53 |

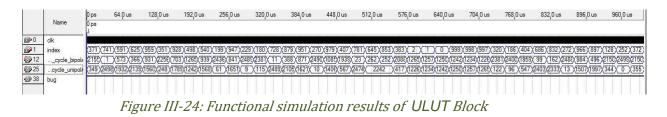

| Figure III-24: Functional simulation results of ULUT Block                           | 53 |

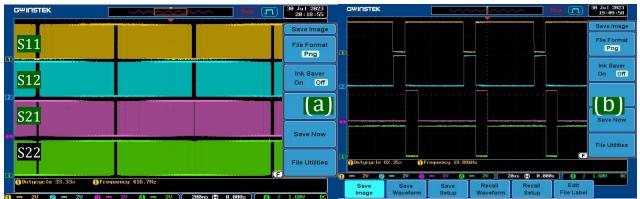

| Figure III-25: Unipolar SPWM gating signals generated from the FPGA-Based controller | 54 |

| Figure III-26: Execution interface in RT-LAB platform                                | 55 |

| Figure III-27: Results of HIL simulation with Unipolar SPWM controller               | 55 |

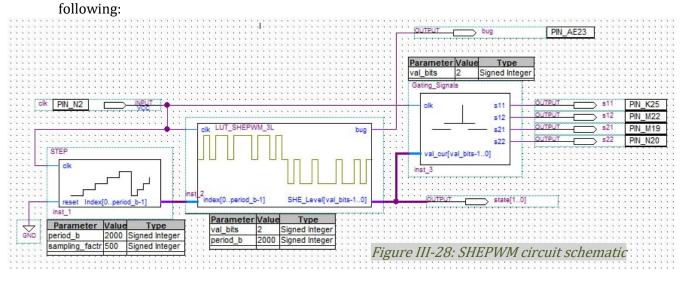

| Figure III-28: SHEPWM circuit schematic                                              | 56 |

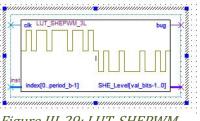

| Figure III-29: LUT_SHEPWM Block diagram.                                             | 56 |

| Figure III-30: Gating_Signal Block diagram                                           | 56 |

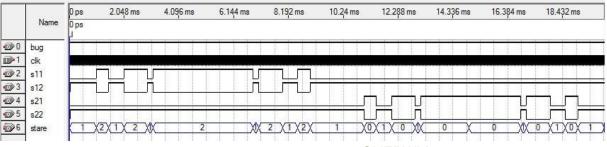

| Figure III-31: Functional simulation results of SHEPWM circuit design       | .57 |

|-----------------------------------------------------------------------------|-----|

| Figure III-32: Pin assignments of the SHEPWM final design                   | .57 |

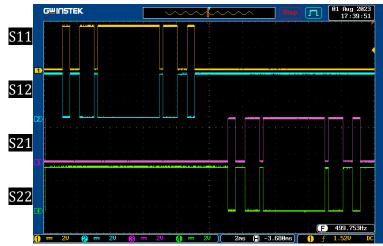

| Figure III-33: SHEPWM gating signals generated by the FPGA-Based controller | .58 |

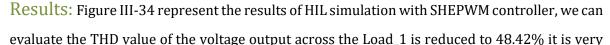

| Figure III-34: Results of HIL simulation with SHEPWM controller             | .58 |

| Figure III-35: Installation of the FPGA-Based controller in Real inverter   | .60 |

| Figure III-36: The voltage output waveform of the real H-bridge inverter    | .61 |

# • List of Tables:

| Table I-1:Inverter main component                                                      | 7  |

|----------------------------------------------------------------------------------------|----|

| Table I-2: Half-Bridge state table                                                     | 9  |

| Table I-3: H-bridge state table                                                        | 10 |

| Table I-4: Three Phase Inverter State table                                            | 11 |

| Table I-5: H-Bridge state table                                                        | 16 |

| Table II-1: Simulator Platforms Comparison [23]                                        | 28 |

| Table II-2: OP4510 Components (back view)                                              | 29 |

| Table II-3: OP4510 Components (front view)                                             | 29 |

| Table III-1: The Pseudo code of the system:                                            | 49 |

| Table III-2: Psuedo code of the Unipolar SPWM system:                                  | 54 |

| Table III-3: Psuedo code of the system:                                                | 57 |

| Table III-4: Table present the error percent of between Experiment and reference's THD | 59 |

## • Abbreviation:

А T ASIC: Application Specific IC. IC: Integrated Circuit. С L CHB:Cascaded H-Bridge. LE: Logic Elements. CPU: Centra Processing Unit. Μ CSI: Current-Source Inverters. MFO: Moth Flame Optimization. D MIL: Model in the Loop. DLL: Dynamic Link Library. MLI: Multilevel Inverter Topology. DUT: Device Under Test. Ν Е NPC: Neutral Point Clamped. EDA: Electronic Design Automation. NR: Newton-Raphson. F Ρ FC: Flying Capacitor. PHIL: Power Hardware-in-the-Loop. FIL: FPGA-In-the-Loop. PIL: Processor in the Loop. FPGA: Field Programmable Gate Array. PWM: Pulse-Width Modulation. G R GA: Genetic Algorithm. RCP: Rapid control prototyping. GUI: Graphical User Interface. RE: Renewable Energy. Н **RTS:** Real-Time Simulation. HDL: Hardware Description Language. S SHEPWM: Selective Harmonic Elimination Pulse HIL: Hardware In the Loop. Width Modulation. HMI: Human Machine Interface. SIL: Software In the Loop.

SoC: System on Chip.

SPF: Small Form-factor Pluggable.

SPWM: Sinusoidal Pulse Width Modulation.

Т

THD: Total Harmonic Distortion.

U

UPS: Uninterruptible Power Supply.

V

VHSIC: Very High-Speed Integrated Circuit.

VHDL: VHSIC Hardware Description Language.

VSD: Variable Speed Drive.

VSI: Voltage-Source Inverters.

Ζ

ZSI: Impedance-Source Inverters.

# • General Introduction:

Renewable energy is becoming increasingly important as we move towards a more sustainable future. Power electronics play a vital role in the generation, transmission, and distribution of renewable energy. Inverters are a type of power electronics device that converts DC power to AC power. They are used in a variety of applications like Uninterruptible Power Supply (UPS), Variable Speed Drive (VSD) and in renewable energy (RE) such as solar photovoltaic systems, wind turbines, and electric vehicles.

The control of inverters is a complex task. The controller must ensure that the inverter output voltage and frequency are accurately controlled, even under varying load conditions. Hardware-in-the-loop (HIL) simulation is a powerful tool that can be used to test and validate inverter controllers. HIL simulation allows the controller to be tested in real time with a simulated inverter model. This can help to identify and correct controller design flaws early in the development process, which can save time and money.

The objective of this report is to investigate the use of HIL simulation for testing and validating inverter controllers. The specific focus of the report is on the development and testing of an FPGA-based controller for a three-level power inverter. The controller was designed using VHDL and tested using the OPAL-RT HIL simulation tool. The results of the HIL simulation were compared to pre-simulated MATLAB® results and expected results. The results showed that the controller was able to control the inverter output voltage and frequency under varying load conditions.

In the first chapter, we provided a brief overview of the theoretical background of power electronics and inverter technology. We also discussed the different modulation topologies for 2-level and 3-level voltage source inverters and the different real-time simulation methods. In the second chapter, we described the hardware used in the HIL simulation, we also discussed the simulation setup and the results of the MATLAB® simulation. In the third chapter, we described the process used to implement the FPGA-based controller and present the results of the HIL simulation and discussed them and compared them with the presimulated results and finally we present a general conclusion based on the results.

Chapter I. Theoretical Background and Literature Review

#### I.1. Introduction:

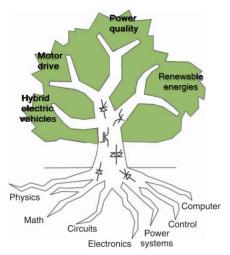

Power Electronics is a field in electronical engineering that deals with conversion and control of electrical power with the help of switching devices, it involves several theoretical aspects and disciplines including semiconductor physics, control theory, power systems and circuit principles. [1]. There are four basic possible conversions: AC/DC also known as rectifier, AC/AC, DC to AC or inverter and DC to DC conversion. The range of applications for power electronics converters is vast, including motor drive systems, renewable energies, robotics, electrical and hybrid vehicles as well as circuits promoting power quality. -Figure I-1.1 illustrates this by analogy-. Testing and validation of power converters are necessary during the design and improvement phases of these electrical systems and before final implementation

*Figure I-1.1 Interdisciplinary nature and applications obtained from power electronics. [1]*

on actual real processes. The Inverter is one of the power converters that are widely used in modern electrical systems. (Standalone-Inverters, Motor drives) In order to achieve the required performances of the power converter system and its control: real-time simulation technology is a prominent tool extensively used, aimed at testing functionality and performance of the electrical systems.

In this chapter, we will initiate an examination of power electronics and inverter technology. Our attempt will involve mapping briefly the domain of inverters, covering their classification and operational principles. We will explore a diverse range of inverter structures, configurations, modulation techniques and control strategies as well as real time simulation techniques widely used for testing systems functionality.

## I.2. Overview of power electronics and inverter technology: I.2.1. History of Power Semiconductor Switches and Power Electronics:

The history of power electronics can be traced back to the early 1902, with the

development of the mercury-arc rectifier by Peter Cooper Hewitt, despite being large and bulky as shown in Figure I-2, they were used in many applications, including power supplies, electric motors, and lighting. it was the only way to convert high AC power to DC power, two years later until the invention of semiconductor switches, in the 1950s, the first semiconductor power switches were developed, they were much smaller and more efficient than the mercury-arc rectifier, and paved the way for the development of modern power electronics [1].

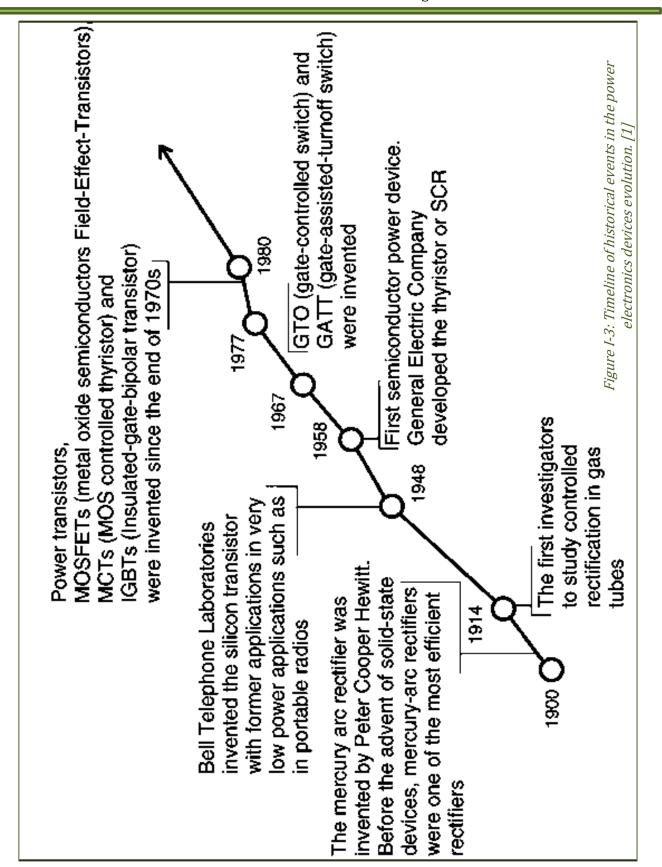

The development of semiconductor switching devices is essentially a search for the ideal switch. The efforts have been made through years to reduce device power losses, increase switching frequencies and simplify gate drive circuits [2]. some of the key events in the history of power electronics are described in the following timeline in Figure I-3:

*Figure I-2: Mercury arc rectifier under operation [34]*

#### I.2.2. Inverters:

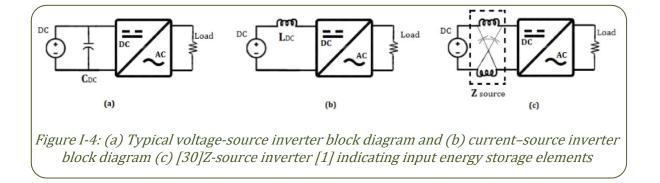

The inverter also known as DC -AC converter, is a one type of the power electronics that converts DC power to AC power at desired output amplitude and frequency, inverters can be voltage-source inverters (VSIs), current-source inverters (CSIs) and impedance-source inverters (ZSIs) [1]. Figure I-4 represents a typical block diagram representation of VSI, CSI and ZSI, they are mostly used in AC power supplies (power inverters), motor drives (VFD) and systems where the objective is to produce a sinusoidal AC output whose magnitude and frequency both can be controlled. Practically, inverters are used in both single-phase and Multi-phase AC systems.

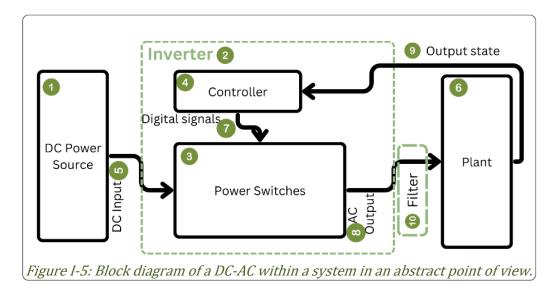

Inverters are available on the market in various configurations and power ratings. Figure I-5 illustrate an abstract representation of inverters in a system where: element<sup>1</sup> represent the DC power source that feeds the inverter, it could be a battery, a rectifier or a DC power supply.

Element<sup>2</sup> is the inverter, in within element<sup>3</sup> represents a set of power semiconductor switches that are connected together in specific structure to direct the flow of DC current,

there exist numerous different structures and topologies, some will be discussed later in this chapter, these power semiconductor switches are controlled via element<sup>4</sup> the controller of the inverter, this last generates digital signals based on different control and modulation techniques aimed to turn ON or OFF the power semiconductor switches, these digital signals are called control signals, gating signals and control commands interchangeably in this scope. The controller can be available as a separate off-the-shelf module as 'converter's control unit' for specific application, as it could be a circuit integrated internally within the system, these controllers can be single Integrated Circuit (IC) chips that generate the control commands (either ASIC or FPGA-based controller) like the TL494 PWM IC, as they can be a SoC (System on Chip) with a microcontroller that generates the command signals, integrated with safety circuits and Human Machine Interface (HMI) to manipulate the output signals..etc. The rest of the element are summarized in Table I-1 bellow:

| Element | Name                       | Description                                                                                                                                                                                                                                                                                   | Example                             |  |  |

|---------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| 5       | DC input                   | The Dc input is the DC power that feeds the<br>inverter and will be converted to AC power220Volts,<br>350Volts                                                                                                                                                                                |                                     |  |  |

| 6       | The output load<br>(plant) | IThe characteristics of the load can greatly affect<br>the performance of the inverter. For instance,<br>resistive loads (like incandescent lights or<br>heaters) are the easiest for an inverter to<br>                                                                                      |                                     |  |  |

| 7       | Digital signals            | These digital signals control the switches, they<br>are crucial for the operation of the inverter,<br>they turn high or low depending on the type of<br>the modulation controlling method used.                                                                                               |                                     |  |  |

| 8       | AC output                  | This output is the desired AC signal which have been converted from a DC signal.                                                                                                                                                                                                              | Square wave,<br>PWM signal          |  |  |

| 9       | Output state               | Feedback signal, generally used to control<br>actions needed to keep a specific variable of the<br>inverter under control, for instance, in a motor<br>drive system where the speed must be<br>controlled electronically through the inverter.<br>This signal requires sensors to be measured | Phase of the<br>AC signal<br>state, |  |  |

| 10      | Output filter              | The output filter removes the high-frequency components of the PWM wave, to produce a nearly sinusoidal output.                                                                                                                                                                               | Low pass LC<br>filter               |  |  |

#### Table I-1:Inverter main component

#### I.2.3. Basic Voltage-Source Inverter's structures:

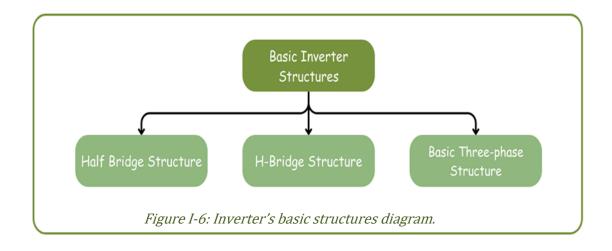

VSIs basic structures are the simplest inverter topologies that can output an AC signal from single DC source and can be classified as: 1) Single phase half bridge, 2) H-bridge structure and 3) Multi-phase inverter structure as shown in Figure I-6.

#### I.2.3.1. Half-Bridge inverter:

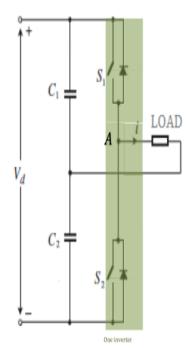

The half-bridge structure is the simplest inverter structure that generates AC voltage from

a DC source, it is composed of a single DC source Vdc and two capacitors (C1 & C2) that split the source in half in order to obtain 0V midpoint, it is possible to use a center-tapped voltage source supply instead. As can be observed on Figure I-7 it contains two power semiconductor switches (S<sub>1</sub> and S<sub>2</sub>) connected in series each with a freewheeling diode in parallel, it is called an inverter leg or an inverter arm, the diodes are used to provide current path when the power transistors are turned off. The DC link capacitors are used to store energy and provide a smooth DC voltage to the inverter. the switches are controlled to provide two-level output  $\left(-\frac{V_{dc}}{2} \text{ and } \frac{V_{dc}}{2}\right)$  thus it is also named: two-level inverter. Table I.2 and Figure I.8 show the switching states and the output levels respectively.

Figure I-7:Half-bridge inverter.

| Switch<br>state |            | output<br>Voltage   |

|-----------------|------------|---------------------|

| <b>S</b> 1      | <b>S</b> 2 | vonage              |

| 0               | 1          | $-\frac{V_{dc}}{2}$ |

| 1               | 0          | $\frac{V_{dc}}{2}$  |

Table I-2: Half-Bridge state table

*Figure I-8: Switching pattern of half bridge switches along with Voltage waveform across Resistive LOAD.*

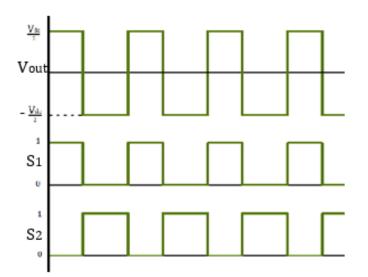

<u>DEDUCE THE STATE TABLE</u>: The switching states of the inverter can be deduced using circuit analysis. When both switches in one inverter leg are turned on, it results in a short-circuit state. When both switches are turned off, it results in a floating state. These two states are avoided and forbidden. The remaining two states, when one switch is turned on and the other is turned off, cause a voltage drop of either  $-\frac{V_{dc}}{2}$  **volts** or  $\frac{V_{dc}}{2}$  **volts** across the load. Applying certain periodic on and off control commands to the switches will lead to producing an alternating voltage and current signal in the output as illustrated in Figure I-8.

Table I-2 shows the possible switching states of the inverter and the corresponding output voltages.

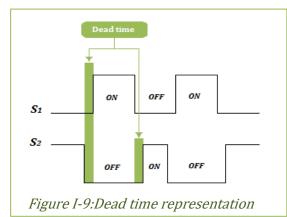

It is important to note that when using non-ideal semiconductor switches in an inverter leg

and transitioning between the two conducting states described in Table I-2, a delay circuit must be added to the output of the control signals that govern these switches. This addition is intended to avoid the occurrence of the short-circuit state [3], as shown in Figure I-9. This requirement applies to every inverter leg in real-world applications, particularly those involving medium and high voltages (MV and HV).

9

Chapter I.

## I.2.3.2. Full-Bridge Inverter:

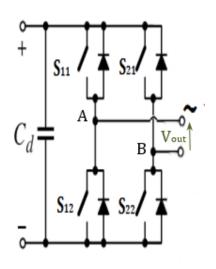

Full-bridge inverter also known as H-bridge cell is illustrated in Figure I-10 is another basic inverter structure where the switching circuit consists of two half-bridge legs connected in parallel with a DC link capacitor Cd, The switches can be controlled to provide Three-Level voltages (-Vdc , 0 and +Vdc), Table I-3 shows the possible switching states of the inverter and the corresponding output voltages. Figure I-11 presents the output waveform across points A and B: VAB=VA0-VB0, along with corresponding gating signals.

*Figure I-10: H-bridge inverter structure [2].*

|             | Outrust     |             |             |        |

|-------------|-------------|-------------|-------------|--------|

| <b>S</b> 11 | <b>S</b> 12 | <b>S</b> 21 | <b>S</b> 22 | Output |

| 0           | 1           | 1           | 0           | -Vdc   |

| 0           | 1           | 0           | 1           | 0      |

| 1           | 0           | 1           | 0           | 0      |

| 1           | 0           | 0           | 1           | Vdc    |

*Figure I-11: Switching pattern of H- bridge switches and the outputted three level pattern*

Table I-3: H-bridge state table

The output voltage of H-bridge can be written as:  $V_{out} = (S_{11} - S_{21})V_{dc}$  [1]

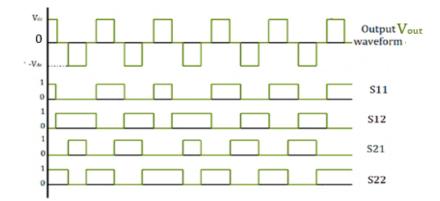

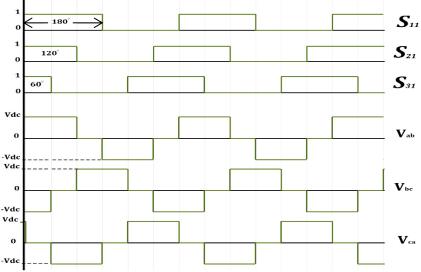

## I.2.3.3. Multi-Phase Inverter Structure:

There exist numerous Multi-phase inverter structures, the basic one is represented in Figure I-12, it is composed of three inverter legs all connected in parallel with two DC link capacitors and a three-phase load (either Y or  $\Delta$  connection). The output line-to-line voltages can result up to three-level pole voltages (-Vdc,0 and Vdc) as shown in Figure I-13.

Table I-4 represent the conducting switching stats along with output pole voltages:

*Figure I-12: Basic Three Phase Inverter* [2].

*Figure I-13: Line-to-line three phase inverter waveform.*

| Switching states |             | Pole voltages |      |      |      |

|------------------|-------------|---------------|------|------|------|

| <b>S</b> 11      | <b>S</b> 21 | <b>S</b> 31   | Vab  | Vbc  | Vca  |

| 0                | 0           | 0             | -Vdc | +Vdc | 0    |

| 0                | 0           | 1             | -Vdc | 0    | +Vdc |

| 0                | 1           | 1             | 0    | -Vdc | +Vdc |

| 1                | 0           | 0             | +Vdc | -Vdc | 0    |

| 1                | 1           | 0             | +Vdc | 0    | -Vdc |

| 1                | 1           | 1             | 0    | +Vdc | -Vdc |

Table I-4: Three Phase Inverter State table.

## I.2.4. Multi-Level Inverter Configuration:

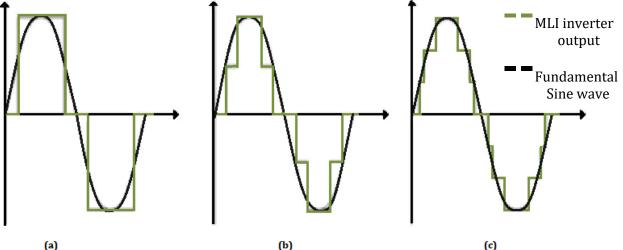

The concept of multilevel inverter topology (MLI) was introduced in the early 1975 with the three-level converters [4] [5]. Figure I-14 illustrates several multilevel waveforms. In multi-level converters, the desired output voltage waveform is composed of a specific number of voltage levels. These levels are typically achieved by combining one or more independent DC sources (depending on the type of the multi-level converter). The most used independent sources include photovoltaic panels, fuel cells, batteries, and ultra-capacitors. As the number of voltage levels increases, the complexity of circuit design grows, thus, more complex switching controller circuits. The multilevel inverters is constructed with a minimum of three levels. As the number of levels approaches infinity, the output waveform approximates a sinusoidal waveform. [6]

*Figure I-14: (a) A three-level, (b) five-level and (c) seven-level output waveform at fundamental switching frequency. [26].*

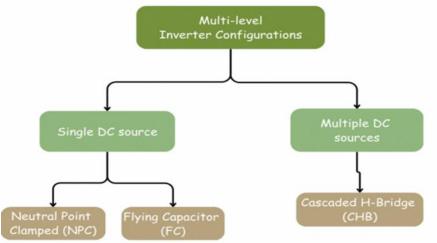

Multi-level inverters are generally categorized into three main commercial configurations: [4] [5]:Neutral Point Clamped (NPC), Flying Capacitor (FC) and Cascaded H-Bridge (CHB) as shown in Figure I-15.

Figure I-15: Block Diagram for MLI Configurations.

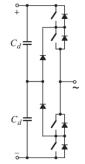

## I.2.4.1. Neutral-Point-Clamped Configuration:

The neutral-point-clamped (NPC) configuration as shown in Figure I-16, is a type of MLI configuration. In this configuration, the neutral point of the DC source is clamped to a fixed voltage. This means that the output voltage of the inverter is aimed to be balanced, even if the load is unbalanced [1] [5]. The NPC configuration is one of the most common topologies for medium and high voltage applications such as in variable-speed *Fi* drives.

*Figure I-16: Neutral point clamped inverter leg* [2].

## I.2.4.2. Flying Capacitor Configuration:

The flying capacitor (FC) configuration is another type of MLI configuration, it is similar to NPC. In this configuration, the neutral point of the inverter is not clamped to a fixed voltage. Instead, it is connected to a flying capacitor as shown in Figure I-17. This means that the output voltage of the inverter can be unbalanced [1]. The FC configuration is often used in applications where a high-power density is required, such as in electric vehicles.

# $E \stackrel{+}{=} C$ $E \stackrel{+}{=} C$ $E \stackrel{+}{=} C$ $S_{1} \stackrel{+}{\downarrow}$ $S_{2} \stackrel{+}{\downarrow}$ $S_{3} \stackrel{+}{\downarrow}$ $V_{1}$ $S_{4} \stackrel{+}{\downarrow}$

*Figure I-17: Flying capacitor inverter*

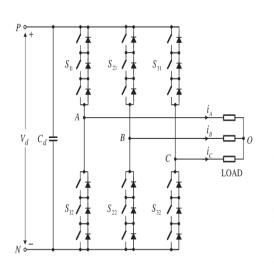

## I.2.4.3. Cascaded H-Bridge Configuration:

Cascaded H-bridge is a type of multilevel inverter that is made up of multiple H-bridge cells connected in series. Each H-bridge cell can produce three different output voltages: (-Vdc , 0 and +Vdc). The output voltage of the cascaded H-bridge is the sum of the output voltages of all the H-bridge cells. The number of output voltage levels in cascaded inverter is defined by: m = 2s + 1 where s is the number of sources or cells, Figure I-18 represent a basic cascaded H-bridge configuration with number of cells  $F_{H-L}$  s=3.

*Figure I-18:Cascaded H-bridge configuration.*

## I.3. Modulation Topologies for 3-level Voltage Source Inverters:

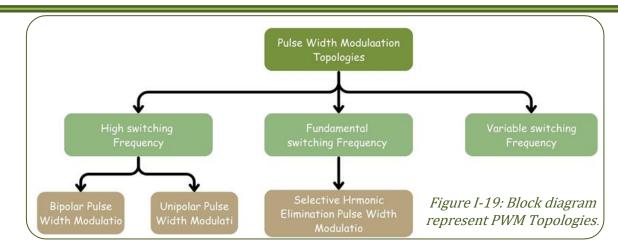

Since the invention of semiconductor power switches, multiple modulation topologies have been developed to control the power converters. Among these is pulse-width modulation (PWM), which was first developed in the 1960s. PWM are classified under three different categories (as shown in Figure I-19) based on the switching frequency used, as 1) High switching frequency, 2) Fundamental switching frequency PWM and 3) variable frequency modulation techniques [6] [7].

#### Chapter I.

Theoretical Background and Literature Review

## I.3.1. Pulse Width Modulation signals:

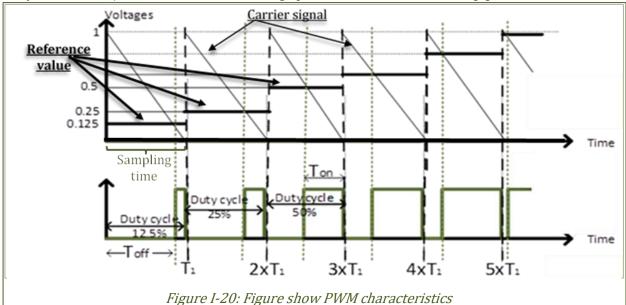

Figure I-20 represents the main characteristic of PWM, PWM is a technique for generating a variable-width pulse train from a fixed-frequency clock signal. The width of the pulse train is modulated according to a reference signal. The duty cycle is the ratio of the pulse in ON state (Ton) to the period of the clock signal T. A duty cycle of 50% means that the pulse is High for half of the period [8], in this case a rectangular waveform is generated. The duty cycle can be adjusted to control the average power delivered to the load [7].

To generate PWM gating signals, a reference signal, a carrier signal, and a comparator are needed. The maximum amplitude or peak value of the reference and carrier signals are denoted by  $V_{r,peak}$  and  $V_{c,peak}$ , respectively. Their frequencies are denoted by  $f_c$  and  $f_r$ , respectively. The ratio of  $V_{r,peak}$  to  $V_{c,peak}$  is known as the modulation index or amplitude modulation index,  $m_a$ :  $m_a = \frac{V_{r,peak}}{V_{c,peak}}$ .

The ratio of  $f_c$  to  $f_r$  is known as the frequency modulation index,  $m_f = \frac{f_c}{f_r}$

The PWM gating signals are generated by comparing the reference signal to a triangular carrier signal. When the reference signal is greater than the carrier signal, the comparator outputs a high pulse. When the reference signal is less than or equal to the carrier signal, the comparator outputs a low pulse. The width of the pulses is determined by the modulation index [8].

#### I.3.2. Sinusoidal Pulse Width Modulation:

Sinusoidal pulse width modulation or SPWM is the most common used method in motor control and inverter application [3] [9]. It is a modulation technique that uses a sinusoidal as a reference signal to generate a pulse width modulated (PWM) signal. The PWM signal is then used to control the switching of power semiconductor devices in the inverter.

In the case of a half-bridge inverter, two switching signals are required to control the two power semiconductor devices S1 and S2. from Table I-2 it is possible to notice that  $S_1 = \overline{S_2}$  in both conducting states [1], The upper switch S1 is controlled by the SPWM signal from the comparator, while the lower switch is controlled by the logical inverse of the SPWM signal. This ensures that the two switches are never turned on at the same time (because that would create a short circuit.) therefore the output is a two level SPWM signal (-Vdc/2 and +Vdc/2).

In the case of an H-bridge inverter, four switching signals are required to control the four semiconductor devices. The two switches on each leg are controlled in the same way as the switch in a half-bridge inverter. However, the two upper switches must be carefully synchronized to ensure that the desired output voltage is well generated.

Chapter I.

The two types of SPWM signals that can be generated by an H-bridge inverter are bipolar

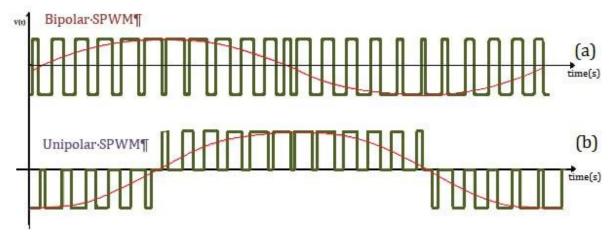

SPWM and unipolar SPWM [1] [3] [10] as shown in Figure I-21.

- Bipolar SPWM is generated when  $S_{11}$  is the logic-inverse of  $S_{21}$  (i.e  $S_{11} = \overline{S_{21}}$ ) this will generate a two level SPWM signal (-Vdc and +Vdc) [1] as shown in Figure I-21 and illustrated in Table I-5.

- Unipolar SPWM is generated when  $S_{11}$  is leading  $S_{21}$  by 180° as described in Table I-5, this will generate a three level SPWM signal (-Vdc, 0 and +Vdc) as shown in Figure I-21, this is named Unipolar SPWM because in positive half cycle only levels (+Vdc, 0) occur while in negative half cycle only signal (-Vdc, 0) occur [8].

Figure I-21:Bipolar and Unipolar SPWM waveform of Three-level inverter.

<u>Harmonics and THD</u>: In multi-level inverters the output of the DC/AC inverter actually looks more like staircase signal and not ideal sinusoidal because it contains harmonics [11], which are frequencies that are not present in the original sinusoidal waveform and that are integer multiples of the fundamental frequency. Harmonics can cause problems such as noise and vibration. However, the staircase signal has several advantages over the square-wave inverter, such as lower voltage stress and reduced switching losses [2].

THD is a ratio that can be calculated to deduce whether a signal is close to a pure sine wave or not, it is calculated as the ratio of the RMS value of the harmonics to the RMS value of the fundamental frequency:

$$THD = \frac{\sqrt{RMS \text{ of harmonic components}^2 - RMS \text{ of fundamental component}^2}}{RMS \text{ of fundamental component}}$$

(a)

A lower THD value indicates a signal that is closer to a pure sine wave. A signal with a low THD value is more likely to be a pure sine wave than a signal with a high THD value.

|   |             | Switchin    | g state     |             | Output |      |

|---|-------------|-------------|-------------|-------------|--------|------|

| Ċ | <b>S</b> 11 | <b>S</b> 12 | <b>S</b> 21 | <b>S</b> 22 |        |      |

|   | 0           | 1           | 1           | 0           | -Vdc   | 0°   |

| ( | 1           | 0           | 1           | 0           | 0      | 90°  |

|   | 1           | 0           | 0           | 1           | Vdc    | 180° |

|   | 1           | 0           | 1           | 0           | 0      | 270° |

#### I.3.3. Selective Harmonic Elimination Pulse Width Modulation:

SHEPWM is a modulation technique mainly used to eliminate any number of harmonics, including the lower-order harmonics that are most harmful to power quality. It can also be used to reduce the switching frequency, which can improve the efficiency of the inverter. Historically, SHEPWM was proposed in the early 1960s, when it was found that low order harmonics could be suppressed by adding several switching angles in a square wave voltage. Years later the idea was extended by Patel and Hoft [12]using Fourier series to mathematically express the harmonic contents of a PWM waveform as follows:

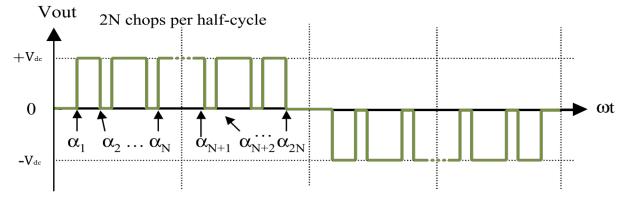

Figure I-22: Generalized three-level SHE PWM waveform. [12]

Figure I-22 represents the generalized three-level SHEPWM waveform where N is the number of switching angles per quarter-cycle. The output waveform is assumed to be odd quarter-wave symmetry, therefor the dc component and the even harmonics are equal to zero and the Fourier series of the three-level SHEPWM can be written as:

$$V_{out}(\omega t) = \sum_{n=1}^{\infty} a_n \sin(n\omega t)$$

(b)

Where:

$$a_n = \frac{4 V_{dc}}{n \pi} \sum_{k=1}^{N} (-1)^{k+1} \cos(n\alpha_k) \text{, for } n \text{ odd}$$

(c)

N is the number of switching angles per quarter.

$\alpha_k$  is the switching angles, which must satisfy the following condition:  $0 < \alpha_1 < \alpha_2 < ... \alpha_N < \frac{\pi}{2}$

E is the amplitude of the dc source.

and n is the harmonic order.

The above equation results a group of nonlinear and transcendental equations of the harmonic components:

$$\cos(\alpha_{1}) - \cos(\alpha_{2}) + \cos(\alpha_{3}) - \dots \mp \cos(\alpha_{N}) = \frac{\pi}{4}m \qquad (I-1)$$

$$\cos(3\alpha_{1}) - \cos(3\alpha_{2}) + \cos(3\alpha_{3}) - \dots \mp \cos(3\alpha_{N}) = \frac{3\pi}{4V_{dc}}h_{3} \qquad (I-2)$$

$$\cos(5\alpha_{1}) - \cos(5\alpha_{2}) + \cos(5\alpha_{3}) - \dots \mp \cos(5\alpha_{N}) = \frac{5\pi}{4V_{dc}}h_{5} \qquad (I-3)$$

$$\vdots$$

$$\cos(N\alpha_1) - \cos(N\alpha_2) + \cos(N\alpha_3) - \dots \mp \cos(N\alpha_N) = \frac{N\pi}{4V_{dc}}h_N \quad (I-N)$$

To control the amplitude of the fundamental component, the modulation index in the above set of equations, m is given. According to the above nonlinear system, N-1 harmonic can be eliminated from the output waveform by setting equations (I-2) to (I-N) to zero. , therefore, N nonlinear equations will be set up as follows:

$$\cos(\alpha_1) - \cos(\alpha_2) + \cos(\alpha_3) - \dots \mp \cos(\alpha_N) = \frac{\pi}{4}m$$

$$\cos(3\alpha_1) - \cos(3\alpha_2) + \cos(3\alpha_3) - \dots \mp \cos(3\alpha_N) = 0$$

$$\cos(5\alpha_1) - \cos(5\alpha_2) + \cos(5\alpha_3) - \dots \mp \cos(5\alpha_N) = 0$$

$$\vdots$$

$\cos(N\alpha_1) - \cos(N\alpha_2) + \cos(N\alpha_3) - \dots \mp \cos(N\alpha_N) = 0$

The switching angles are calculated by solving the above equations. The challenge of SHEPWM is solving nonlinear equations using the best technique. In overall, with the help of Fourier series THD of the output signal can be eliminated by calculating the value of 2N firing angels that make the first 2N-1 harmonics of the signal equal to zero [12].

There are several optimization algorithms such as Newton-Raphson, PSO algorithm Genetic Algorithm (GA), Moth Flame Optimization (MFO) [11] etc. can be used for efficiently solving the nonlinear system of equations , however solving such equations is not in the objective of this project, therefore a set of solution have been taken from references [13] [12] [14] and , compared and tested in MATLAB<sup>®</sup> then use the best solution (less THD) in the implementation of the FPGA-Based SHEPWM controller.

#### I.4. Overview of Real Time Simulation:

Real-time simulation (RTS) refers to a computer simulation of a physical system that can run at the same rate as real time. In other words, the computer model operates at the same rate as the real physical system [15], For example, if a tank takes 20 minutes to fill in the real world, in the simulation would also take 20 minutes. RTS is used whenever there is an interaction between a system operating at real-world speed and a model.

Real-time simulation is common in computer games, but it is also important in the industrial market for operator training and offline controller tuning. Computer languages such as LabVIEW, SolidThinking Embed, and Simulink enable the rapid creation of real-time simulations.

. Some commercially available HIL simulators [16]:

- Nvidia: Nvidia HIL simulators are primarily used for the development of driver assistance systems and autonomous driving functions. Using a GPU, a 3D model of the road and environment is calculated, like a racing game on a game console.

- dSPACE: The larger real-time simulators are typically based on a combination of Intel Xeon and FPGA processors. The Model development is performed in MATLAB/Simulink with proprietary libraries for interface definition, while manufacturer-specific software provides the user interface for control and visualization. dSpace systems are widely used in the automotive sector.

- OPAL-RT: Intel Xeon processors are often used in combination with FPGA boards, and similarly, like the simulators from dSPACE, application-specific systems can be created. The development environment is also MATLAB/Simulink, which also serves as the user interface. Manufacturer-specific software is also used for visualization. OPAL-RT real-time simulators are mainly used in the energy industry and in power electronics.

- Typhoon HiL: FPGA in cooperation with coprocessors, for software-side there are proprietary models with interfaces and integration possibilities for C/Python/MATLAB programs.

- PLECS: RT-Box, Xilinx Zynq System-on-Chip with FPGA and multiple CPU cores, software-side solved by MATLAB<sup>®</sup> connection with additional proprietary add-on libraries or with completely independent software.

- Micronova: Various systems for simulating vehicle components, solutions for electrified drives are available.

- Siemens: Siemens are often used in industry. The company's newer products include the virtual commissioning of fully industrial automated production lines including extensive software libraries.

Real time simulation can be classified into:

#### I.4.1. Model-In-The-Loop simulation:

Model in the Loop (MIL) is the simulation of an embedded system in an early development phase of modeling in the field of model-based software development. Embedded systems communicate with their environment and often expect sensor signals as input and then stimulate the physical system. In order to function properly, the environment of the embedded system must be simulated. If the embedded system (model) is now simulated in a loop together with the environmental model, this is called Model in the Loop Simulation. [17]

MIL is a cost-effective way to test algorithms for embedded systems. Development and simulation environments for model-based development are, for example, MATLAB/Simulink, PLECS, Dymola, ASCET or the free software Scilab/Xcos.

MIL is typically used in the early stages of embedded system development. It can be used to investigate specified model behaviors. Data collected during MIL simulation helps to validate that the model behaves as expected and can even be used for reference during the next design and testing phase i.e. in later stages, the system may be tested using Software in the Loop (SIL), Processor in the Loop (PIL), or Hardware in the Loop (HIL) simulations. These simulations are more complex than MIL, but they provide a more realistic test of the system's performance.

## I.4.2. FPGA-In-The-Loop simulation:

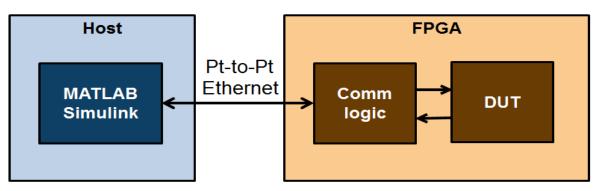

FPGA-in-the-loop (FIL) simulation provides the capability to use soft simulation platforms such as MATLAB® or Simulink® software for testing designs in real hardware for any existing Hardware Description Language (HDL) code.

Figure I-23: Diagram represent the communication in FPGA-In-The-Loop block [40]

In MATLAB® for example, the FILSimulation System object<sup>™</sup> can be used to connect an FPGA execution to a MATLAB® test bench. It does so by applying input signals to and reading output signals from an HDL model running on an FPGA. This object can be used to model a source or sink device by configuring the object with input or output ports only. The HDL code can be either manually written or software generated from a model subsystem, All Device Under Test (DUT) I/Os are routed to Simulink through the FIL communication logic as it can be observed in Figure I-23.

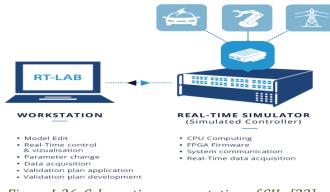

### I.4.3. Rapid Control Prototyping:

Rapid control prototyping (RCP) is a test and development methodology used to accelerate the design process by using model-based design from an RCP platform to test a control strategy on physical hardware i.e. implement a simulated controller early in the design process to test the physical hardware as illustrated in Figure I-24. RCP typically involves the following steps:

- Design a control strategy for the system.

- Implement the control strategy on a rapid prototyping platform.

- Connect the RCP platform to the physical system and send the control signals to the physical system.

- Iterate the design process as needed.

RCP can help to improve the quality of a control system and allows for greater flexibility in the design process, as it is possible to quickly experiment with different control strategies by ensuring that it is well-tested and executed.

Figure I-24: Schematic representation of RCP [28]

#### I.4.4. Hardware-In-The-Loop simulation:

Hardware in the Loop (HIL) is a procedure in which an embedded system (e.g., real electronic control unit) is connected to a real time simulator via its inputs and outputs and test the controller on simulated environment, as illustrated in Figure I-25, the HIL simulator serves as a replica of the system's real environment. From the perspective of testing, HIL is a method for securing embedded systems, supporting development, and commissioning machines and plants early on. If the target controller is not used and only a simulation of the software is performed, this is referred to as Software in the Loop (SiL) [15]

*Figure I-25: Schematic representation of HIL. [22]*

## I.4.5. Software-In-The-Loop simulation:

In contrast to Hardware in the Loop (HIL), no physical hardware is used in the Software in the Loop (SIL) method [18] as graphically explained in Figure I-26. The original controller code is written into a file using an automated coding process, typically a Dynamic Link Library (DLL). This DLL can be embedded in an environment model in a simulation tool (e.g., MATLAB® and Simulink®). The DLL is then tested in the purely virtual model world. Unlike the HIL method, no real controller is required. SIL makes it possible to test software prior to the initialization of the hardware prototyping phase, significantly accelerating the development cycle.

Figure I-26: Schematic representation of SIL. [22]

SIL simulators do not run in real time, and the simulation can be paused at any time for debugging. Hardware-related runtime problems or variable overflows that occur on the real controller can hardly be detected with SIL simulations.

Other advantages of SIL include the fact that the target hardware does not have to be set yet, and that the costs are much lower due to the lack of a real simulation environment. The simulation model used here can also be used in subsequent HIL simulations, which allows the individual test runs to be compared with each other.

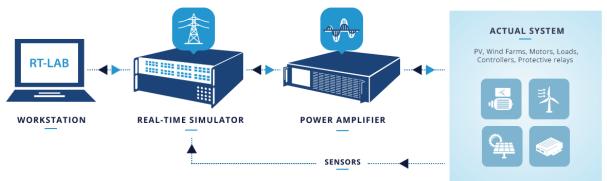

#### I.4.6. Power-Hardware-In-The-Loop simulation:

Power Hardware-in-the-Loop (PHIL) simulation represents a natural extension of HIL, in which the real-time simulation environment can exchange not just low-voltage, low-current signals, but the power required by the Devices under Test (DUT). To bridge this gap, power amplifiers are inserted between DUTs rated for higher power and the low-level simulator I/Os, all while providing the necessary feedback to properly close the loop as it can be observerd in Figure I-27. Power amplifiers are selected for user applications based on their closed-loop performance and ability to generate and absorb power. PHIL also allows the simulation of higher power flows between DUTs, as well as with the simulated electric circuit running on the simulator. This capability enables engineers to test multiple systems, including power converters, generators, motors, and PV loads, while also benefiting from high-fidelity simulation that provides greater flexibility and safety than typical analog benches and dynamometers.

Figure I-27: Schematic representation of PHIL [22]

## I.5. Conclusion:

This chapter dealt with the main theoretical background that has been used in the implementation of this project. Starting with the main inverter topologies and inverter modulation techniques, then passed to the most real-time simulation technologies used in research laboratories and industry. Power electronics systems on large ships act as multimegawatt microgrids, powering propulsion and all other onboard electrical equipment. These systems often require multimillion-dollar investments and a year or more to build. As a result, engineering teams that develop the control software often lack access to feature-complete hardware until late in development. For that reason, semi physical simulation has become popular these last years.

In this project, an H-bridge topology has been constructed as the simulated environment using HIL Simulink and Opal-RT simulation tools to test the implemented FPGA-based inverter controller. Chapter II. Hardware In the Loop and MATLAB® Simulation Setup:

#### II.1. Overview:

In this chapter we will describe the hardware used in the HIL simulation, we also discuss the simulation setup and the results of the MATLAB® simulation, Early in last year, a group of electrical engineering students designed an industrial H-bridge PWM inverter for research purposes, the power semiconductor switches (Industrial High frequency MV IGBT modules) used in their design where very expensive modules therefore Rapid Control Prototyping was used to control and test the functionality of the designed H-Bridge inverter, Despite being fully operational, the finished product was not ready, the designed inverter needs a real control unit. The objective of this project is to implement an FPGA-Based control unit for inverter's High frequency semiconductor switches, In addition designing a functional PWM control circuits (using Bipolar PWM, Unipolar and SHEPWM) using VHSIC Hardware Description Language (VHDL) Then upload and run the circuit in DE2 Field Programable Gate Array Board then test its functionality using OPAL-RT HIL simulation tools and compare the results with simulated results before test the controller in real hardware. The results of the HIL simulation as well as the VHDL design are discussed in the next chapter.

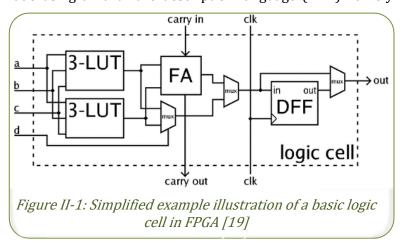

#### II.2. FPGA:

FPGA, which stands for **Field Programmable Gate Array** is a type of integrated circuit that can be programmed or reprogrammed after manufacturing its architecture that consists of an array of programmable logic block that can be configured to perform various digital functions, these logic blocks can be configured to perform complex combinational functions, or act as simple logic gates like AND and XOR, they can be seen as Lego basic block that we can use to build several digital circuits . In most FPGAs, logic blocks as shown in Figure II-1 also include memory elements, like simple flip-flops or more complete blocks of memory [19]. FPGA configuration is made using a hardware description language (HDL) namely

Verilog or VHDL (Very High-Speed Integrated Circuit Hardware Description Language), Many FPGAs can be reprogrammed to implement different logic functions, allowing flexible reconfigurable computing as performed in computer software.

In this project, we used the Altera DE2 standard board containing the Cyclone II FPGA chip.

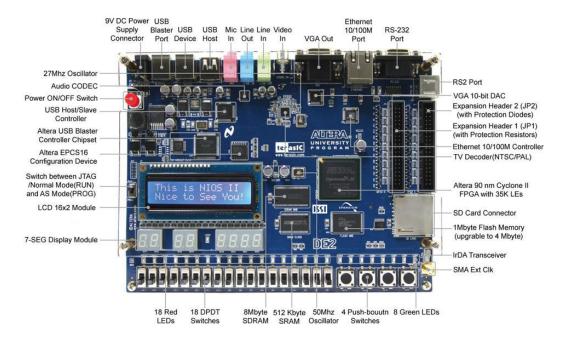

#### II.3. Altera Cyclone II DE2 Field Programable Gate Array Board:

DE2 is a Development and Educational board conceived for the practical implementation of digital and mixed-signal circuits, even quite complex ones. It includes several I/O devices and interfaces, from simple ones (switches, pushbuttons, LEDs, seven segment displays) to complex devices (LCD matrix display, Ethernet network interface, USB 2.0, SD memory cards, analog audio I/O, analog video input, VGA video output ...etc.) [20]. The core of DE2 is an FPGA, composed of more than 30.000 Logic Elements (LE). DE2 may host simple introductory projects, and sophisticated ones that may include one or more microcomputers [20]. Figure II-2 represents DE2 Board top view.

Figure II-2: DE2 Board Top View [35].

# II.4. OP4510 RCP/HIL Real Time Simulator: II.4.1. Overview:

OPAL-RT TECHNOLOGIES is the leading developer of open Real-Time Digital Simulators and Hardware-In-the-Loop testing equipment for electrical, electro-mechanical and power electronic systems. OPAL-RT Simulators are used by engineers and researchers at leading manufacturers, utilities, universities and research centers around the world.

OPAL-RT offers a wide range of simulator platforms as shown in Table II.1 to meet all current industry needs and forthcoming challenges. All simulators are based on a modular and flexible design and are fully customizable and expandable for specific I/O requirements. [21] [22].

| Simulator              | OP4200        | OP4510      | OP5600       | OP5707       | OP5031       |

|------------------------|---------------|-------------|--------------|--------------|--------------|

| platform<br>Compatible | RT-LAB,       | RT-LAB,     | RT-LAB,      | RT-LAB.      | RT-LAB,      |

| Simulation             | eFPGASIM      | HYPERSIM,   | HYPERSIM.    | HYPERSIM.    | HYPERSIM,    |

| Systems and            | or r dribin r | eMEGASIM,   | eMEGASIM,    | eMEGASIM,    | eMEGASIM,    |

| Software               |               | ePHASORSIM, | ePHASORSIM,  | ePHASORSIM,  | ePHASORSIM   |

|                        |               | eFPGASIM    | eFPGASIM     | eFPGASIM     |              |

| CPU                    | ARM           | INTEL XEON  | INTEL XEON   | INTEL XEON   | INTEL XEON   |

|                        |               | E3          | E5           | E5           | E5           |

| Number of              | 2             | 4           | 4,8,16 or 32 | 4,8,16 or 32 | 4,8,16 or 32 |

| cores                  |               |             |              |              |              |

| XILINX FPGA            | ZYNQ          | Kintex 7    | Spartan 3    | Virtex 7     | n/a          |

| (standard              | (7030)        | (325T)      |              | (485T)       |              |

| configuration)         |               |             |              |              |              |

| I/O modules            | 4             | 4           | 8            | 8            | n/a          |

| with 16 analog         |               |             |              |              |              |

| or 32 digital          |               |             |              |              |              |

| signals                |               |             |              |              |              |

| Maximum                | 128           | 128         | 256          | 256          | n/a          |

| number of I/O          |               |             |              |              |              |

| channels               |               |             |              |              |              |

Table II-1: Simulator Platforms Comparison [23].

## II.4.2. Op4510 Simulation Platform:

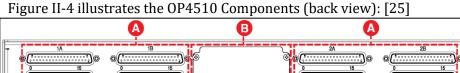

The OP4510 as illustrated in Figure II-3 and Table II-1 is an entry-level simulator that contains an FPGA carrier, which can accept four standard OPAL-RT mezzanine boards [24], contains two digital and two analog boards in addition to the RS422 signals, these mezzanine boards interface using a DB37 connector at

Figure II-3: OP4510 Top view [25].

the back of the chassis as shown in Figure II-4. (A), OP4510 has a rear and a front interface as presented in the next Figures and their elements are described in Table II-2 and Table II-3:

|         | Table II-2: OP4510 Components (back view)                                                                         |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Element | Description                                                                                                       |  |  |  |  |  |  |

| Α       | DB37 connectors for digital or analog inputs and outputs.                                                         |  |  |  |  |  |  |

| В       | This section contains a blank plate; however, several options are available.                                      |  |  |  |  |  |  |

| С       | Standard computer connectors (left to right): Serial (COM) port, IPMI, USB ports*, network ports**, monitor (VGA) |  |  |  |  |  |  |

| D       | Connector availability depends on the expansion option                                                            |  |  |  |  |  |  |

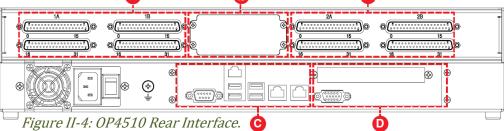

Figure II-5 illustrates the OP4510 Components (front view) [25]

#### Table II-3: OP4510 Components (front view)

| Element | Description                                                                                                                                                                                                                                                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | Small form-factor pluggable (SFP) module connectors provide four high-speed<br>communication links between other FPGA simulators or third-party devices.<br>Each socket controls one communication link. SFP transceivers and fiber optic<br>cables must be selected (and purchased separately) according to the type and<br>speed of the communication protocol. |

| В       | JTAG connector (for OPAL-RT technicians' use only) [24].                                                                                                                                                                                                                                                                                                          |

| С       | Synchronization connectors status, and user-configurable LEDs                                                                                                                                                                                                                                                                                                     |

| D       | Target computer monitoring interface. Two pushbuttons and six LED indicators                                                                                                                                                                                                                                                                                      |

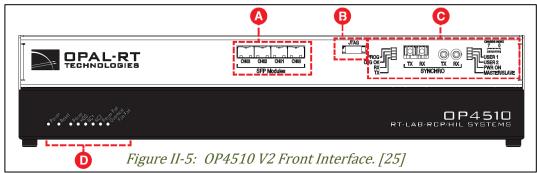

The OP4510 contains four Intel Xeon E3 processing cores, and comes with a customdesigned Linux operating system, providing the best real-time performance on the market. The OP4510 also provides the option of user-programmable I/O management, handled by a fast Xilinx® Kintex®-7 FPGA. In general, the simulator (target simulator) is connected to a computer (host computer) as illustrated in Figure II-6 via ethernet cable with TCP/IP communication protocol. The host computer is supposed to send and control the model, display the graphical results, and receive or read the stored simulation results files in the simulator and some other functions. While the target simulator is supposed to load, build and run the model, during simulation the simulator can store the data without affecting the simulation operation's results and at the end it sends the file to the host computer.

## II.5. MATLAB® and Simulink® Software:

MATLAB<sup>®</sup> is a popular software tool for modeling and simulating dynamic systems from MathWorks<sup>®</sup> (as shown in Figure II-7) while Simulink is a MATLAB-based graphical programming environment developed for

modelling, simulating and analyzing dynamical systems. Its primary interface is a graphical block diagramming tool and a customizable set of block libraries. It offers tight integration with the rest of the MATLAB<sup>®</sup> environment. Simulink is widely used in automatic control and digital signal processing for multidomain simulation and model-based design. In this project Simulink is used for building and simulating the model circuits.

## II.6. Description of the simulation setup:

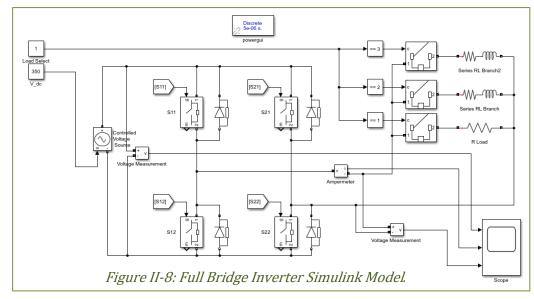

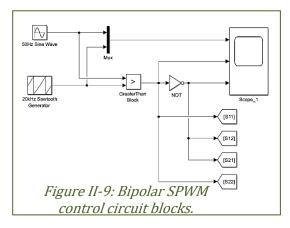

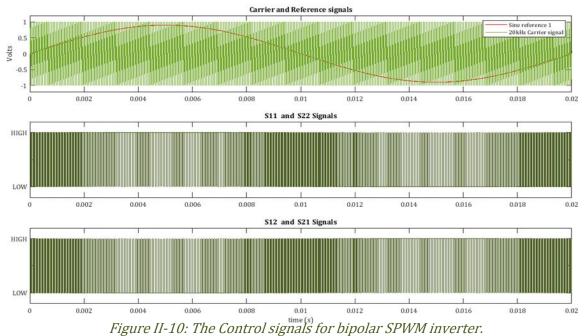

As mentioned in the theoretical chapter, before moving to HIL, we first implemented an MIL simulation. In this project, the DUT is the three-level inverter's control unit. The testing environment of this DUT contains a single-phase H-bridge inverter, a load, and wire

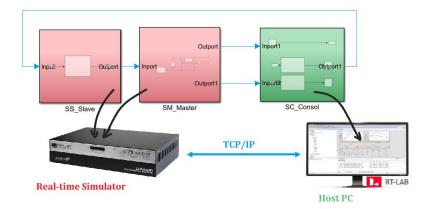

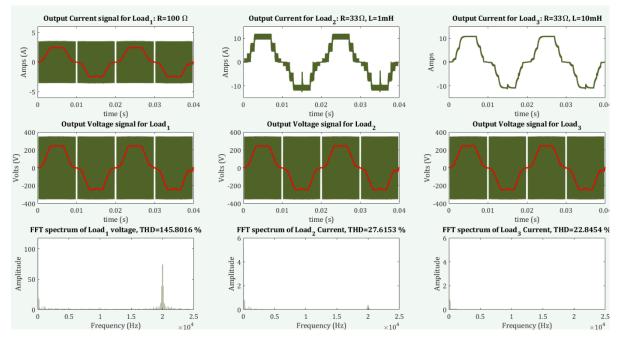

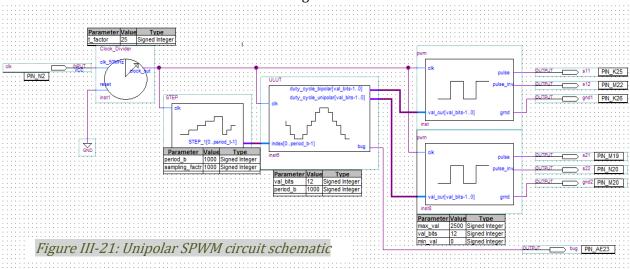

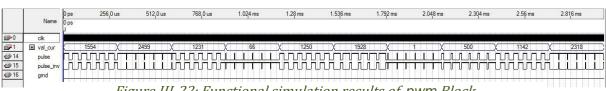

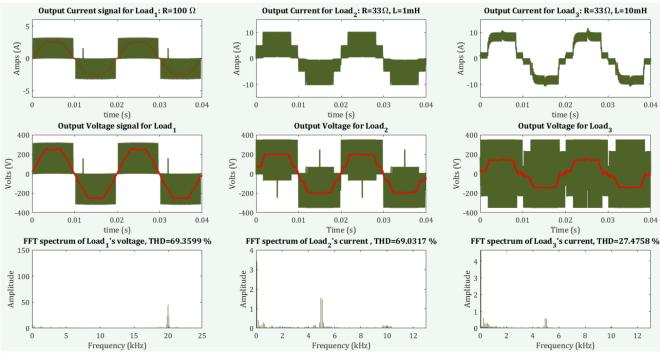

connections. Therefore, we first implemented a model for the environment (load and Hbridge inverter) and then a model for the DUT, as mentioned previously; a three different PWM controller circuits were designed and tested: Bipolar Sinusoidal PWM, Unipolar Sinusoidal PWM and Selective Harmonic Elimination PWM, the first circuit that have been implemented was the Bipolar SPWM since it is the simplest SPWM modulation circuit, after getting the results we improved the project by designing other complex SPWM controlling circuit which are Unipolar SPWM then SHEPWM.