# National Institute of Electricity and Electronics INELEC - BOUMERDES DEPARTMENT OF RESEARCH

# **THESIS**

Presented in partial fulfilment of the requirements of the

## DEGREE OF MAGISTER

in Applied Electronics

by

Arezki BENFDII.A

# Effect of Frequency on The Substrate Current in MOS Devices

Defended on November 14, 1992 before the jury:

President: Dr M. BENZOHRA, Professeur, USTO.

Members: Dr V. MITRA, Professeur, INELEC.

Dr A. CHIKOUCHE, Maitre de Recherche, UDTS.

Dr H. BOURDOUCEN, INELEC.

Dr A. AMROUCHE, Charge de Recherche, CDTA.

registration Number: 02/92.

## **DEDICATIONS**

To my mother and father,

to my sister and brothers,

to all my parents;

To people who struggle for democracy and Algerianity,

to people who struggle for the official recognition

of the Amazigh language and culture;

To my students,

I dedicate the result of my reaserches enclosed in the present thesis.

On Friday November 27, 1992.

BENFDILA AREZKI.

### ACKNOWLEDGEMENTS

I extend my most sincere gratitude to my research advisor Dr Ved Mitra for his continued and untiring interest and guidance throughout this project without which this work could not be achieved in the present form. The overall training and experience that I have gained under him is a valuable addition to my academic knowhow.

I am very grateful to Mr A. Moufek, the present Director General of the Institute, who along with his predecessor (Mr A. Benazzouz) could succeed in establishing postgraduate program and provided us opportunity of completing our magister degree in this institute. My special thanks are due to the above two Directors for providing all necessary research facilities and encouragements throughout the project.

Many thanks are also due to Dr K. Harriche for the moral support, encouragement and research facilities to make our project a success.

I must express my gratitudes to Mr. A. Amrouche for the efforts he made to provide us necessary devices without

which this work could not have been done. I am indebted to all staff of the CDTA who helped in lending us the microscope prober and in the device procurement.

I would like to thank Dr. H. Bourdoucen for encouragements and useful suggestions from time to time and for providing some useful documents. Thanks also go to Mr. Y. Kribes for useful discussions and providing us commercial devices.

I must acknowledge my colleague R. Bouderbala for his collaboration and cooperation during the present study and research. I am equally thankful to my friend H. Bentarzi, another member of our research group.

I would like to thank also all my friends and INELEC staff who provided necessary help and support needed for the achievement of this work.

On July 21, 1992.

BENFDILA AREZKI.

# TABLE OF CONTENTS

| CHAPTER | ONE: IN  | TRODUCTION1                            |

|---------|----------|----------------------------------------|

| CHAPTER | TWO: TH  | E MOS STRUCTURE8                       |

|         | 2.1. Int | roduction9                             |

|         | 2.2. The | Ideal MOS Structure10                  |

|         | 2.2.1.   | The Accumulation Mode10                |

|         | 2.2.2.   | The Depletion Mode                     |

|         | 2.2.3.   | The Inversion Mode16                   |

|         | 2.3. The | Non Ideal MOS Structure22              |

|         | 2.3.1.   | Influence Of The Metal-Semiconductor   |

|         |          | Work Function Difference23             |

|         | 2.3.2.   | Influence Of The Oxide Charges24       |

|         | 2.3.3.   | Influence Of The Interface             |

|         |          | Trapped Charges                        |

|         | 2.3.4.   | Influence Of Dielectric Polarization26 |

|         | 2.3.5.   | The Concept Of Flathand Voltage 27     |

| CHAPTER | THREE: | CONDUCTION IN THIN INSULATING FILMS29    |

|---------|--------|------------------------------------------|

|         | 3.1.   | Introduction30                           |

|         | 3.2.   | The Schottky (Thermionic) Current31      |

|         | 3.3.   | The Tunnelling Current32                 |

|         | 3.4.   | The Poole-Frenkel Current33              |

|         | 3.5.   | The Hopping Current35                    |

|         | 3.6.   | The Space-Charge Limited Current36       |

|         | 3.7.   | Other Types Of Conduction                |

|         |        |                                          |

|         |        |                                          |

| CHAPTER | FOUR:  | THE SUBSTRATE CURRENT STUDIED BY THE     |

|         |        | CHARGE PUMPING TECHNIQUE42               |

|         | 4.1.   | Introduction43                           |

|         | 4.2.   | The Charge Pumping Technique44           |

|         | 4.     | 2.1. Basic Principles Of The Charge      |

|         |        | Pumping Technique44                      |

|         | 4.     | 2.2. Theory Of The Charge Pumping        |

|         |        | Technique45                              |

|         | 4      | .2.3. Techniques Used To Sweep The       |

|         |        | Surface Potential48                      |

|         | 4.3    | . The Idea Of Emission Of Carriers       |

|         |        | From The Surface States50                |

|         | 4.4    | . Effect Of The Frequency On The         |

|         |        | Charge Pumping Current57                 |

|         | 4      | .4.1. Determination Of The Capture Cross |

|                    | Section Of Carriers59                 |

|--------------------|---------------------------------------|

| 4.4.2              | Determination Of The Average Density  |

|                    | Of The Surface States60               |

|                    |                                       |

| CHAPTER FIVE: EXPE | RIMENTAL SET-UP AND DEVICES63         |

| 5.1. The           | Experimental Devices64                |

| 5.1.1.             | The Commercial Devices64              |

| 5.1.2.             | The Wafers64                          |

| 5.2. The           | Basic Equipments                      |

| 5.2.1.             | The Picoammeter65                     |

| 5.2.2.             | The Digital Multimeter69              |

| 5.2.3.             | The Frequency Meter70                 |

| 5.2.4.             | The Function Generator70              |

| 5.2.5.             | The Oscilloscope71                    |

| 5.2.6.             | The Microscope Prober71               |

| 5.2.7.             | The Test-Fixture Box71                |

| 5.2.8.             | The HP Computer72                     |

| 5.3. Des           | cription Of The experimental Set-up72 |

| 5.4. Ope           | rating Principle Of The               |

| Exp                | erimental Set-up77                    |

| 5.5. Des           | cription Of The Experiments78         |

|                    |                                       |

| CHAPTER SIX: EXPER | IMENTAL RESULTS81                     |

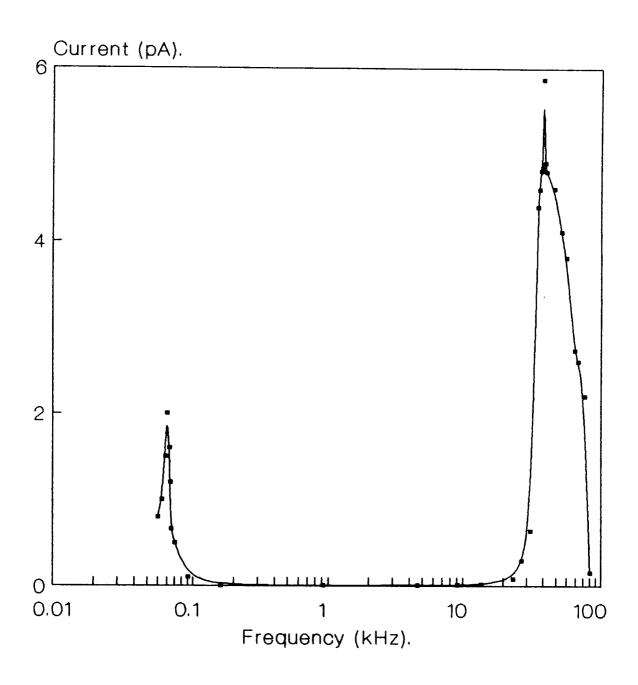

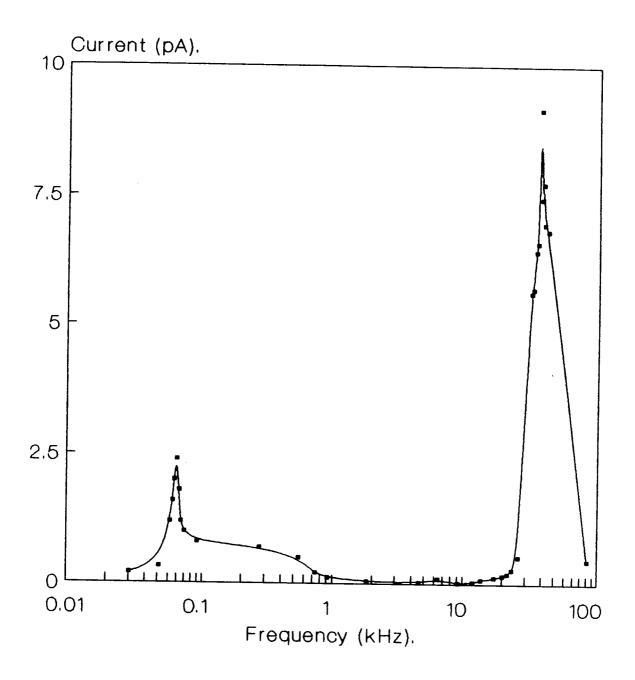

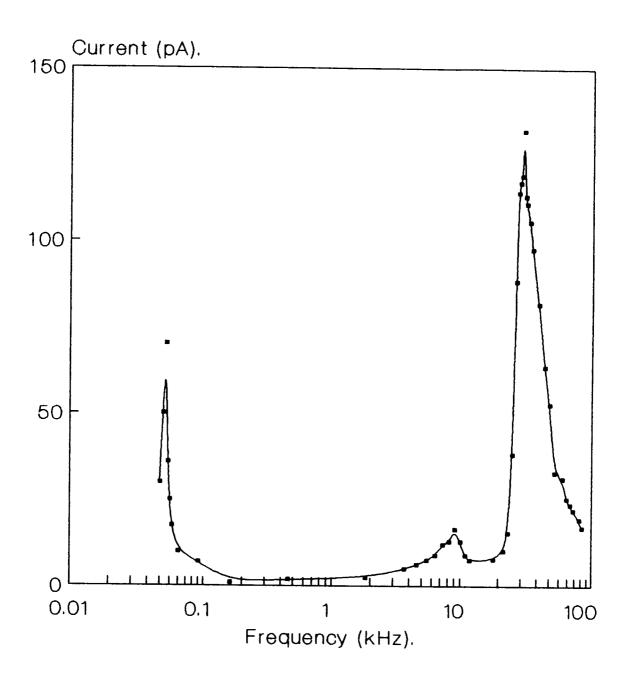

| 6.1. A S           | urvey Of The Experimental Results82   |

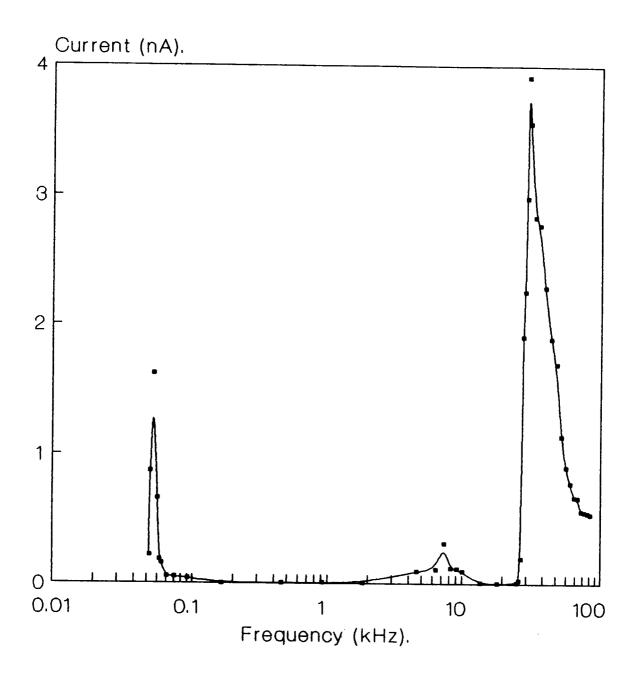

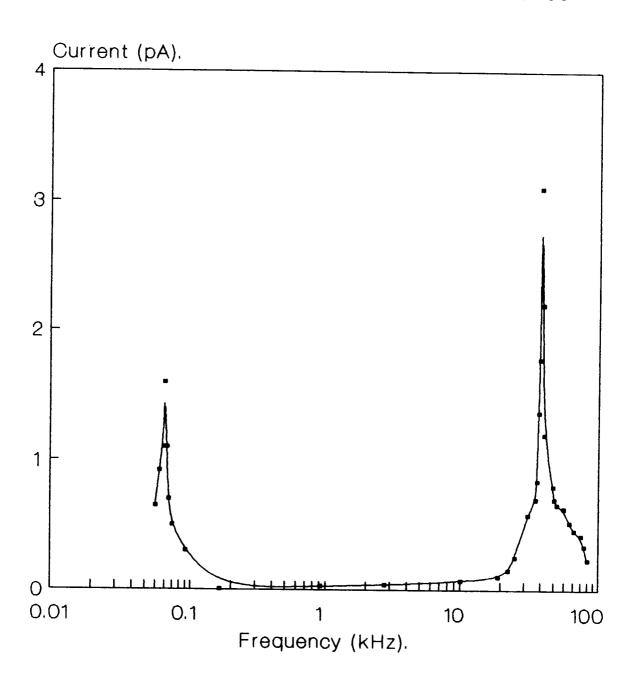

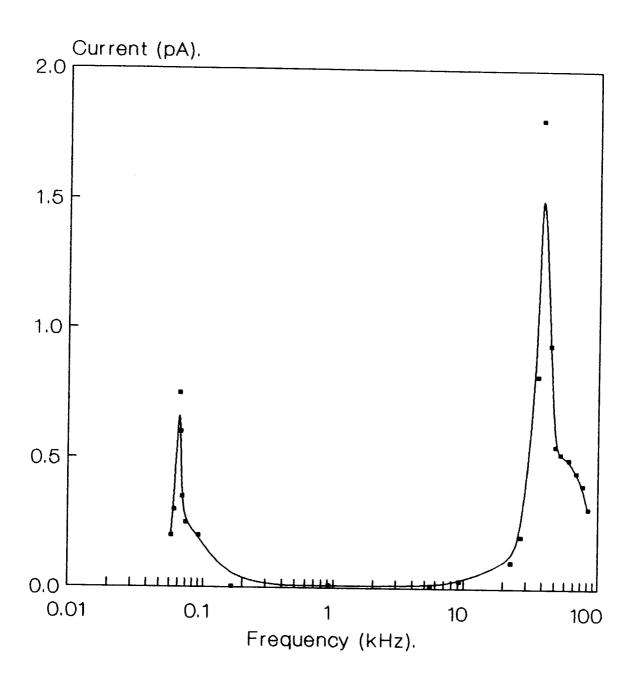

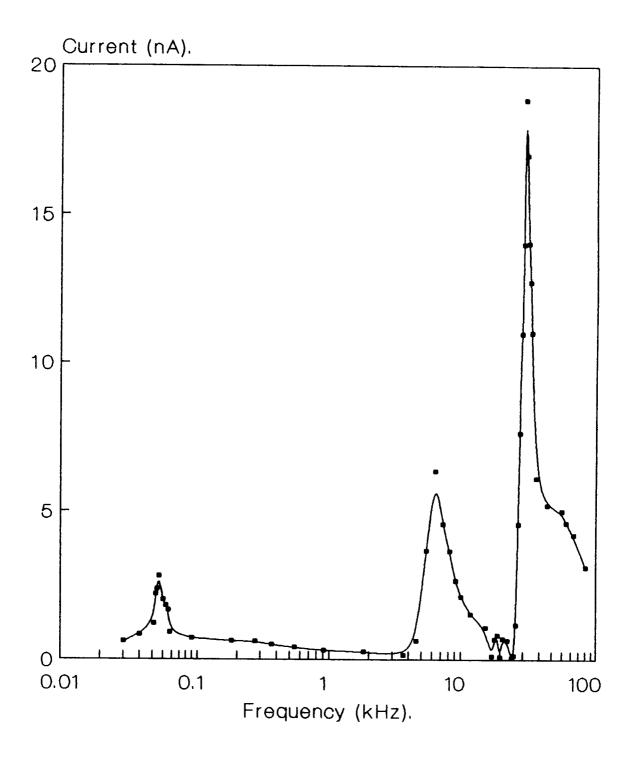

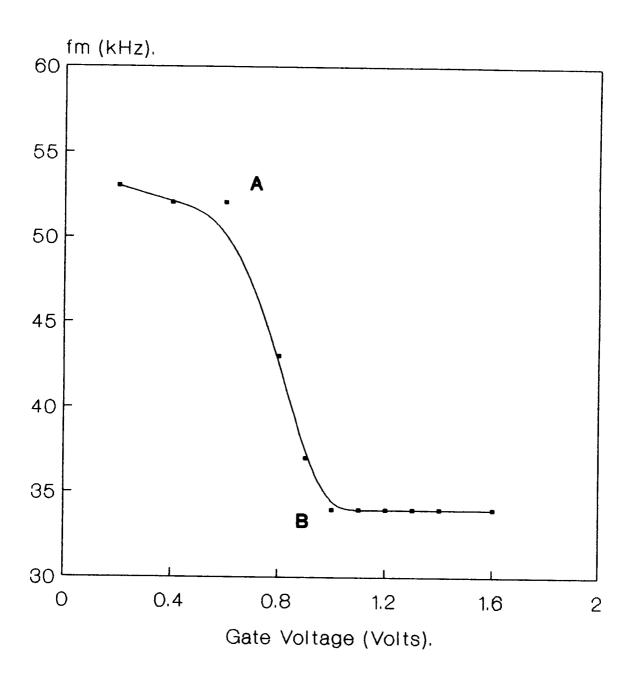

| 6 1 1              | Experimental Results Of Version 183   |

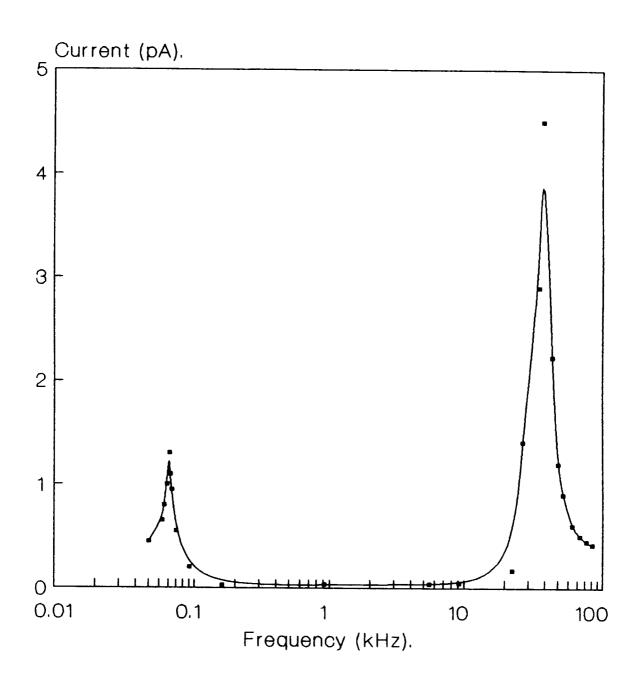

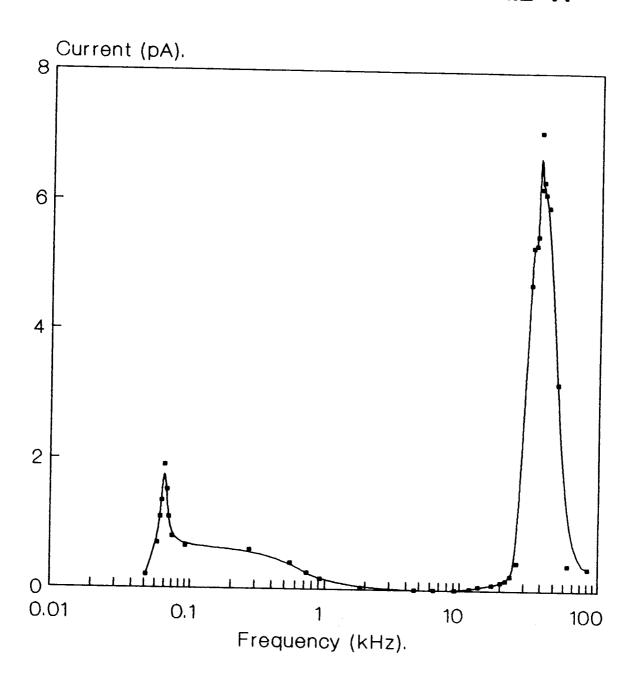

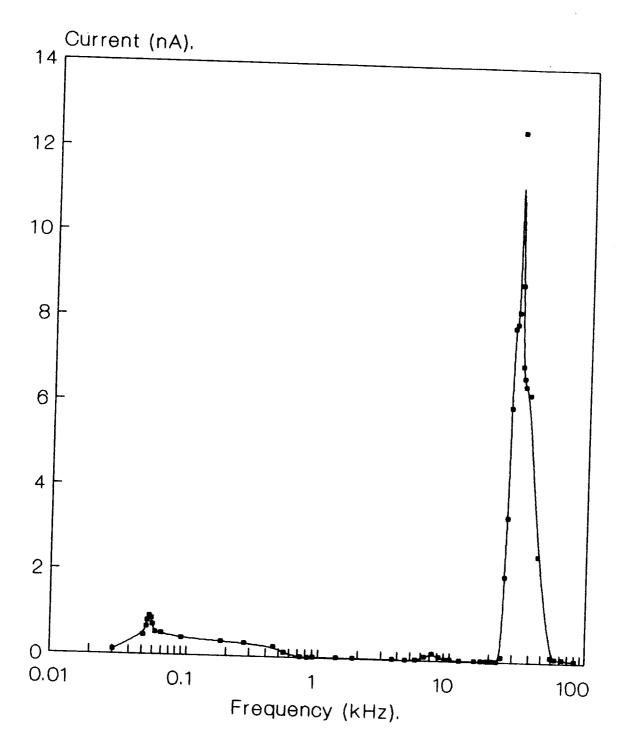

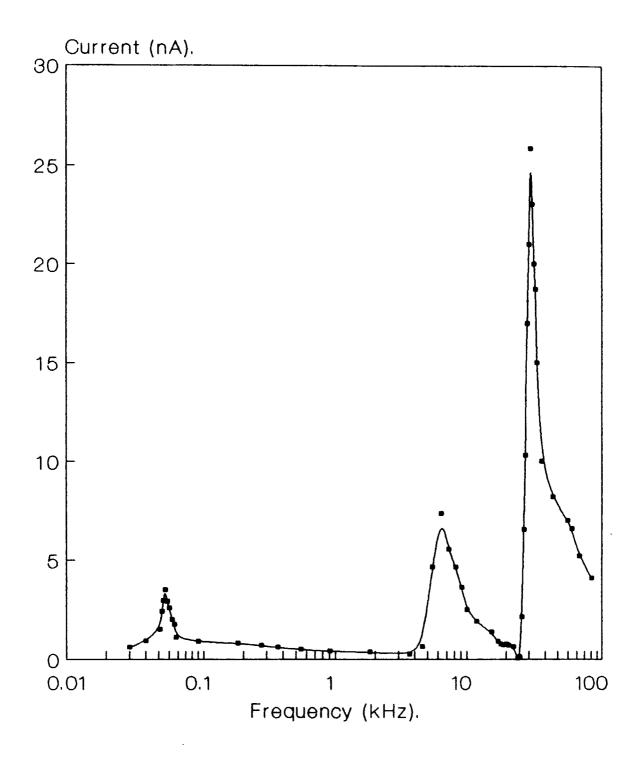

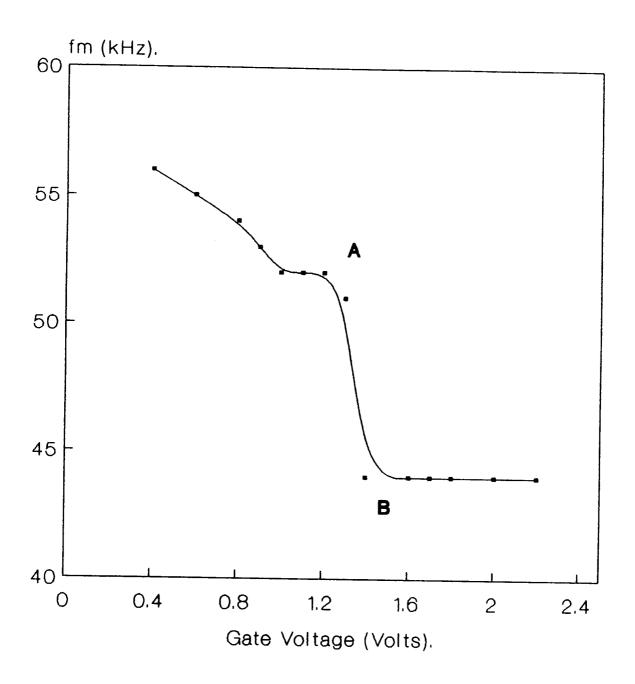

| 6.1.2. Experimental Results Of Version 284             |

|--------------------------------------------------------|

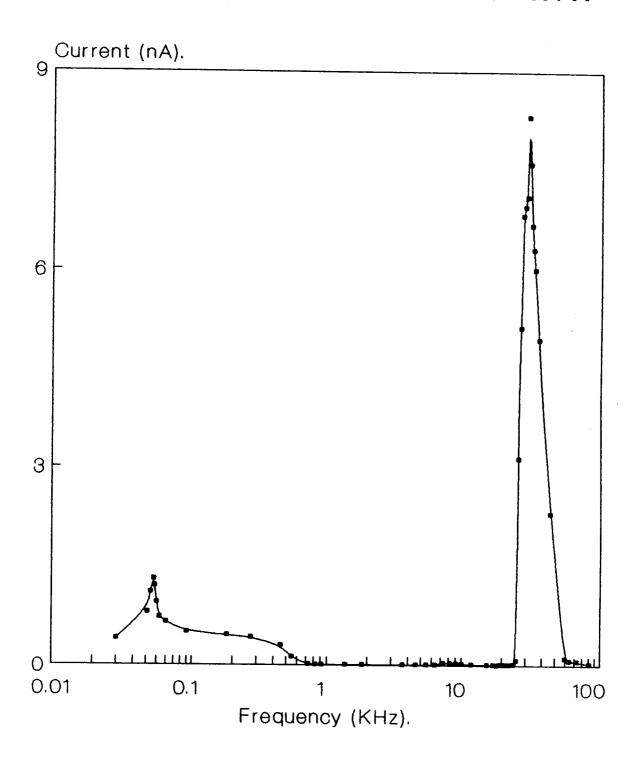

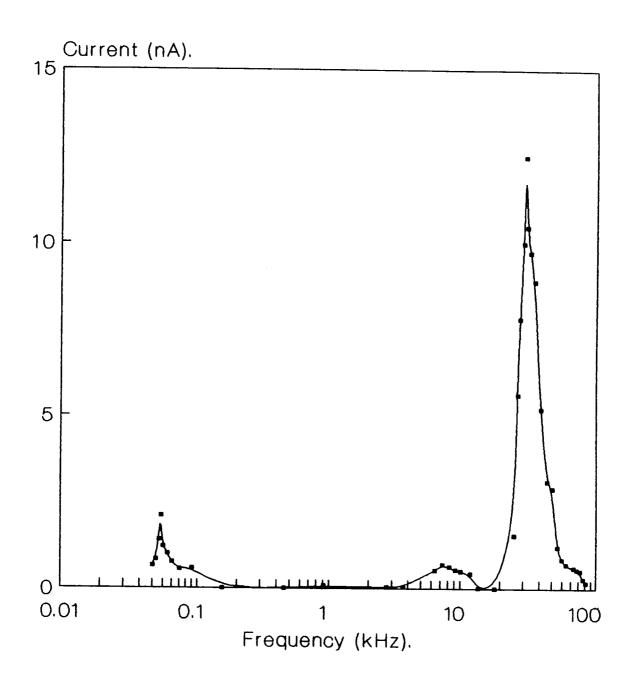

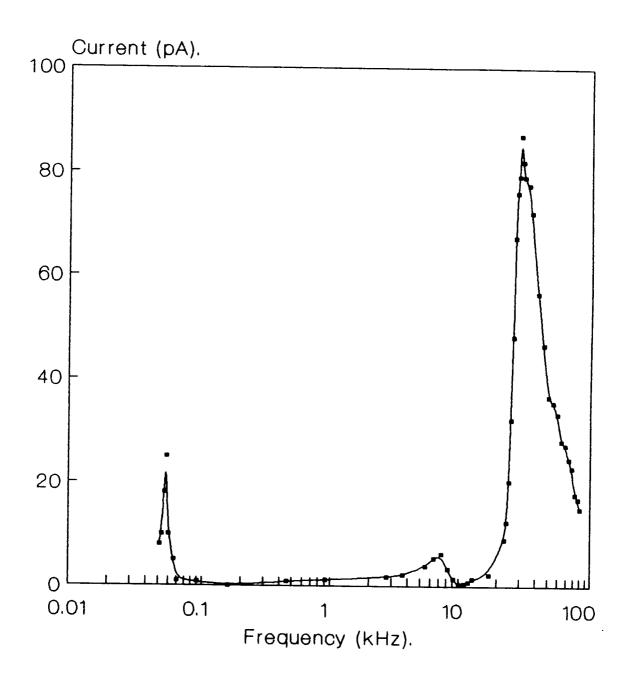

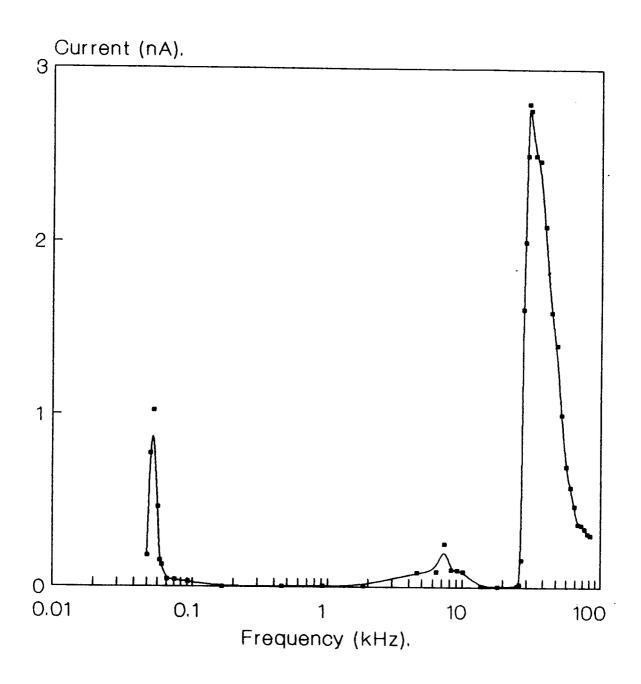

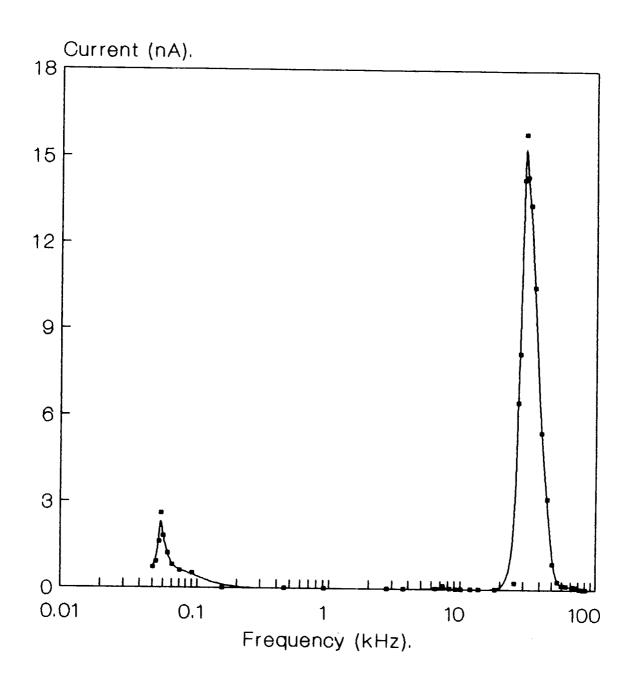

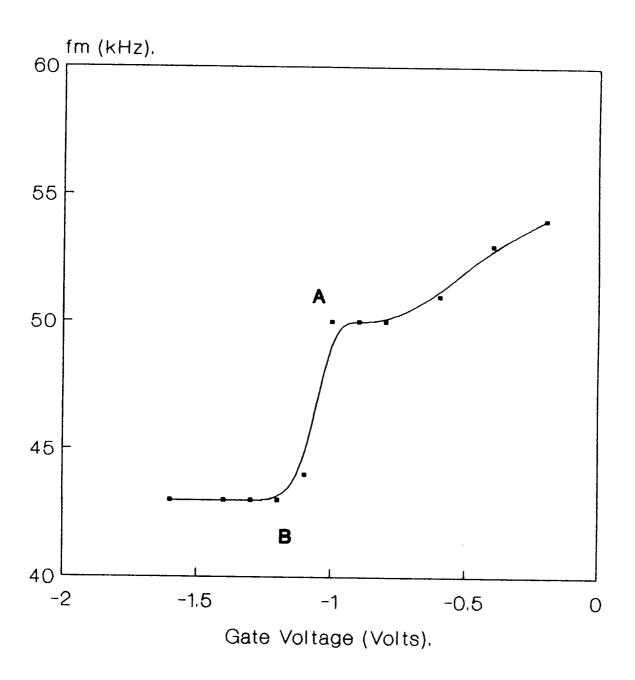

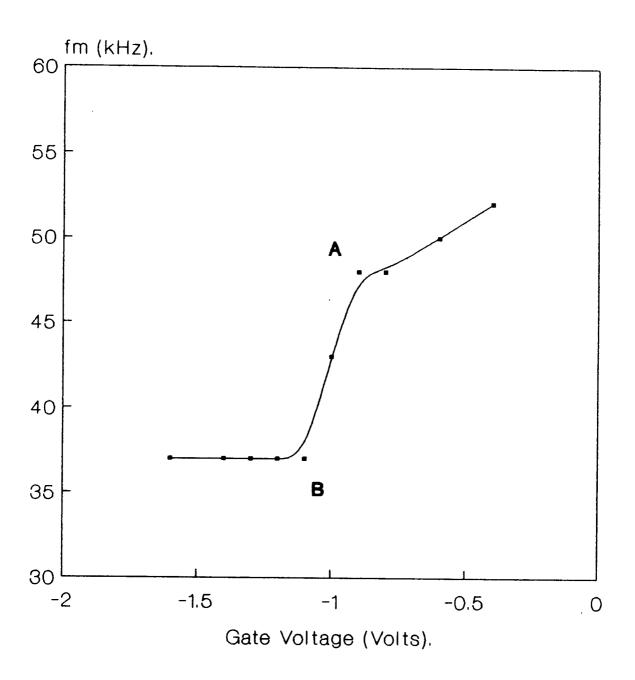

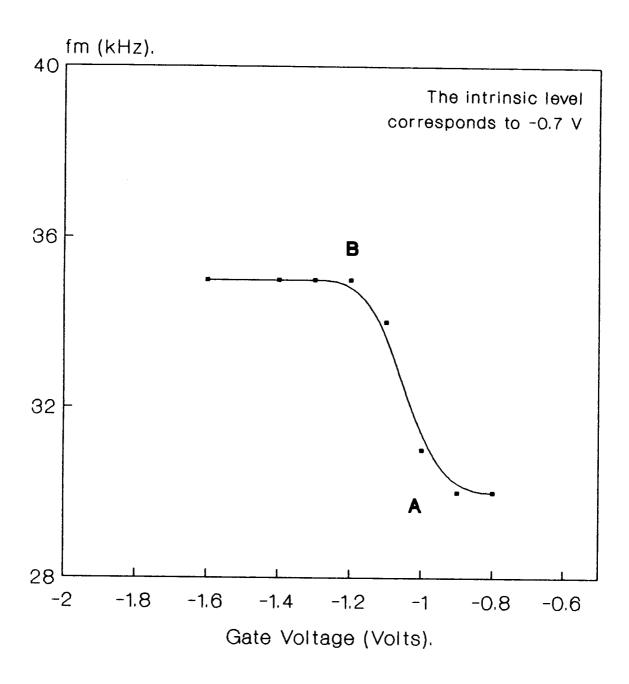

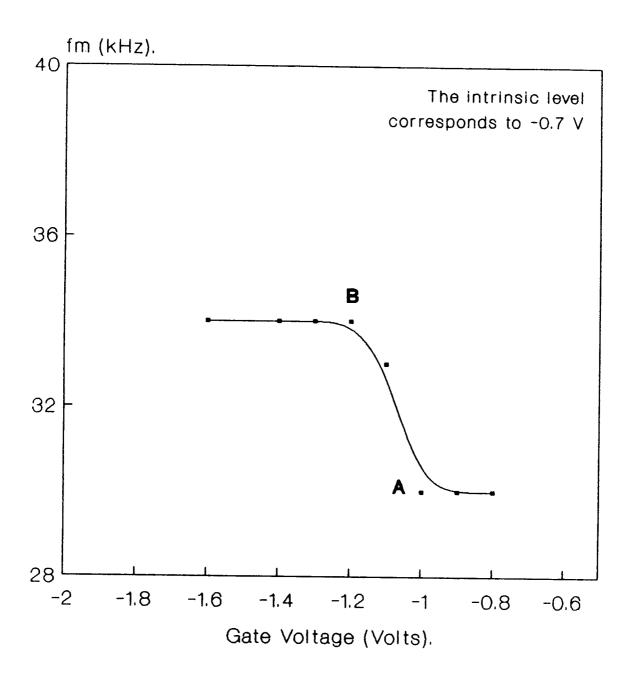

| 6.1.3. Experimental Results Of Version 385             |

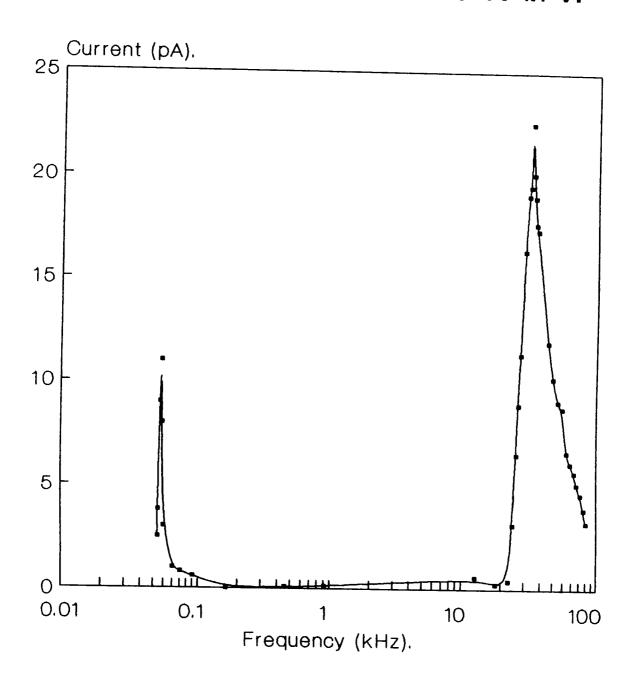

| 6.2. Summary Of Observational Facts88                  |

|                                                        |

| CHAPTER SEVEN: DETERMINATION OF FLATBAND AND THRESHOLD |

| VOLTAGES IN MOS DEVICES                                |

| 7.1. Introduction112                                   |

| 7.2. Determination Of Flatband Voltage113              |

| 7.3. Determination Of Threshold Voltage119             |

|                                                        |

| CHAPTER EIGHT: CONCLUSION AND FURTHER SCOPE141         |

|                                                        |

| REFERENCES :151                                        |

|                                                        |

| APPENDIX: SOFTWARE PROGRAMS MANAGING THE OVERALL       |

| EXPERIMENTAL SET-UP                                    |

| 1. Program To Produce Elliot Version Of                |

| The Charge Pumping Method                              |

| 2. Programs To Produce Signal Frequency                |

| Variations Used In The Present Study 162               |

## INTRODUCTION

Control of the electrical properties of the MOS (Metal Oxide Semiconductor) systems has been one of the major factors that has led to stable and high performance integrated circuits. The MOS capacitor (or MOS Diode) is used in both monitoring integrated circuit fabrication and studying the electrical properties of the MOS system. The MOS capacitor has the advantage of simplicity of fabrication and of analysis. Historically, the motivation behind the use of the MOS capacitor has been the fabrication of stable and high performance devices and integrated circuits.

Liandrat [1] proposed that the conductivity of a thin semiconductor layer could be modulated by an external field. This effect called *field effect* became one of the powerful tools in surface studies. The existence of quantum states on free semiconductor surface was demonstrated by Shockley and Pearson [2] in 1948 by a field effect experiment. Frosh and Derrik [3] found in 1957 that silicon dioxide acts as an effective barrier against commonly used impurities, thus preventing them from reaching the underlying silicon. Therefore, free semiconductor-surfaces are no more used, they have been replaced, in 1960, by the solid-solid interface between the semiconductor and the grown oxide film of known composition and structure. This process is termed as oxide passivation.

Lilienfeld [4] and Heil [5] made a proposal on the amplifying devices based on the field effect in 1920s and 1930s. However, there was not much understanding of the physical phenomena involved. In 1948 Shockley and Pearson [2] made a demonstration on the field effect which led to the development of the field effect transistor (FET). Weimer [6] described the first FET in 1961. The FETs are based on the principle of modulation of the inversion layer conductance. In fact, the idea of inversion layer arose as a problem in studying the bipolar transistor where, for npn transistor, an inversion layer was postulated to exist between the two pn junctions. Brown [7] and Ross [8] found

that the inversion layer could be induced electrically by an electrode deliberately placed in the vicinity of the base region of a bipolar transistor. At about the same time, the idea of putting an insulator between the semiconductor and the control gate came out. This marks the first introduction to the idea of metal-insulator-semiconductor (MIS) structure in the design of FETs. In 1958, Walmark [9] proposed a structure incorporating the native oxide of the semiconductor itself as an insulator in germanium realizing in this way MIS as MOS structure in practice. The first oxide used to fabricate MOSFET (Metal Oxide Semiconductor Field Effect Transistor) is realized by Kahng and Attala [10] and Attala [11] in 1960. Attala [11] suggested that a thermally grown Si-SiO2 can also be used as a gate insulator. These oxides were grown by Ligenza [12]. Practical MOSFETs were fabricated only after the interface properties of the oxidised silicon surface and the nature of the drift and ionic contamination have been understood and controlled. The MOSFET is largely used in VLSI (very large scale integration) because of its low fabrication cost, small size, and low power consumption.

The fabrication of MOS capacitor (Metal Oxide Silicon) uses the same processing as used in the fabrication of integrated circuits. Therefore, the MOS capacitor provides direct measurements and monitoring of the MOS system

as it is actually fabricated and used in the integrated circuits. Three regions of MOS system are important: the bulk oxide, the silicon-silicon dioxide interface, and the silicon itself. Charges in all three regions play an important role in integrated circuits. In the oxide and in the interface, these charges are undesirable because they adversely affect the device performance and stability. In the silicon, charges such as dopant are intentionally introduced for device operation. The three regions of a MOS system are described below.

The bulk or substrate is the silicon added with impurities which form the desired charges. Depending on the type of these impurities, the silicon can be of p-type if it is added with donor type impurities and of n-type if it is added with acceptor type impurities. The amount of impurity atoms added to silicon is called doping concentration. Traps can be present in the bulk semiconductor but they are of less importance compared to that of interface or that of oxide.

The oxide bulk (SiO<sub>2</sub>) is made up of silicon dioxide grown on the silicon. The transport properties of the oxide thus depend on the structure of the oxide which are directly related to the fabrication process. Two major properties of the oxide are of paramount importance: the level of oxide charges and the dielectric breakdown strength. The oxide charges are three types, the oxide fixed charges which

result after interface annealing, the interface trapped charges which are usually located at the silicon-oxide interface, and the mobile ions which are caused by the presence of ionized alkali metal such as potassium and sodium.

The oxide-silicon (Si-SiO2) interface (also resulting from fabrication process) is characterized essentially by the surface (or Interface) states that it contains. The most important parameters of the surface states are 1) the surface state density, 2) the density distribution, 3) the capture cross section, and 4) the type of the surface states. The surface states characteristics have been studied by various methods. The most commonly known and used methods are: C-V (Capacitance Voltage) [13-17], DLTS (Deep Level Transient Spectroscopy) [18-20], PCTS (Photocapacitance Transient Spectroscopy) [21] and Conductance [22]. Recently, some techniques based on the study of substrate current have been developed. The most common method is the charge pumping technique [13-27]. However, the charge pumping technique is thought to suffer with certain limitations [24],[27],[29-34].

In an attempt if the existing limitations of the charge pumping technique can be removed or an alternate approach can be developed which is free from such limitations, we carried out a study on the gate and substrate currents in different MOS devices under varied conditions.

During this study an unusual phenomenon marked by the presence of a new current has been observed. This current is found to exhibit quite distinct properties so as to distinguish it not only from the charge pumping current but also from any hitherto known substrate current. The present work is devoted to carry out at first an extensive experimentation to serve the purpose of as much more fact-finding and data collection as possible. The data and information so collected is then put to some practical applications. However, before taking up the proposed work, a few earlier chapters are devoted to the background study of MOS structure and other related phenomena which are needed for the further understanding and development of the subject.

In chapter 2, a study of the MOS structure operated under different modes is presented. As the present study involves de conduction through the oxide, various de conduction phenomena in the oxide are described in chapter 3. One of the characterization technique recently developed, using the substrate current as a means to extract information, is the charge-pumping technique. As the present study is also based on the measurement of the substrate current, which is supposed to arise due to some process of charging and discharging of the surface traps in charge pumping technique, the present technique based on the observed new phenomenon may be supposed as an alternate approach to the charge pumping technique. Based on these considerations the charge

pumping technique needs special treatment which is presented in chapter 4.

After preparing the required background, chapter 5 is used to describe the experimental set-up and devices used in the present experimentation. All experimental details how the whole experimental arrangement is made to operate and give output results automatically are also given in the same chapter. The different results obtained in this work along with the various conclusions drawn on the basis of these results are presented in Chapter 6.

In chapter 7, one of the most important use of the present study, which is the determination of the flatband and threshold voltages in MOS devices, is presented.

Finally, chapter 8 concludes with certain remarks on the future scope and usefulness of the present study. However they are rather qualitative because of the poor understanding of the physical phenomena involved.

# THE MOS STRUCTURE

A simple method of controlling the surface conductivity of a semiconductor is to apply an electric field normal to that surface. The electric field is due to the potential difference between the semiconductor bulk and a metallic plate parallel to the semiconductor surface. The applied field causes a redistribution of the mobile charge within a certain layer near the surface, and therefore, a modulation of the conductivity of this layer. This field effect is experimentally observed when the metallic electrode is very close to the semiconductor surface. A practical way to obtain this is to construct a metal-insulator-semiconductor (MIS) structure.

#### 2.1. INTRODUCTION.

Metal-insulator-semiconductor structures have been instrumental in gaining knowledge about the insulator-semiconductor interface. Most of the reliable results have been obtained in thermally oxidized silicon, but the physical picture emerging from these results is generally applicable to any semiconductor-insulator interface. When the insulator used in the MIS structure is silicon dioxide grown on silicon substrate, the structure is given the name of MOS (metal oxide semiconductor). The MOS structure is one of the simplest heterostructures; it is made up of a metal (gate), oxide (dielectric), and silicon (substrate). The presence of a dielectric material between the gate and the substrate gives rise to a capacitor, hence the MOS structure (also called MOS Diode) exhibits the properties of a capacitor. The study of the behaviour of MOS capacitor under a varying signal applied to the gate with respect to the substrate is a powerful way of investigating the characteristics of the oxide (SiO2) and oxide-substrate Si-SiO2 interface. The MOS capacitor can be used in principle for the determination of semiconductor properties (minority carrier life time, doping concentration), interface properties (interface state density, capture cross section), and the oxide properties (mobile or fixed charges in the oxide). The study of the MOS capacitor is based on the comparison of the ideal to the non ideal MOS structure characteristics.

#### 2.2 THE IDEAL MOS STRUCTURE.

A MOS structure is ideal, if it satisfies the following conditions:

- 1) no current flows through the structure whatever the applied bias may be. It follows that the Fermi-level in the metal and that in the semiconductor remains flat or the metal and semiconductor work functions are equal, that is,  $\Phi_{M} = \Phi_{SC}$ .

- 2) the electric field is nil everywhere when the applied bias is nil, that is, there is no charges in the oxide  $SiO_2$  ( $Q_{ox}=0$ ) and in the interface  $Si-SiO_2$  ( $Q_{1f}=Q_{1t}=0$ ).

Under an alternating voltage signal applied to the gate, the MOS structure experiences three different modes observed under different gate voltages. These modes are: 1) accumulation, 2) depletion, and 3) inversion.

#### 2.2.1 The Accumulation Mode.

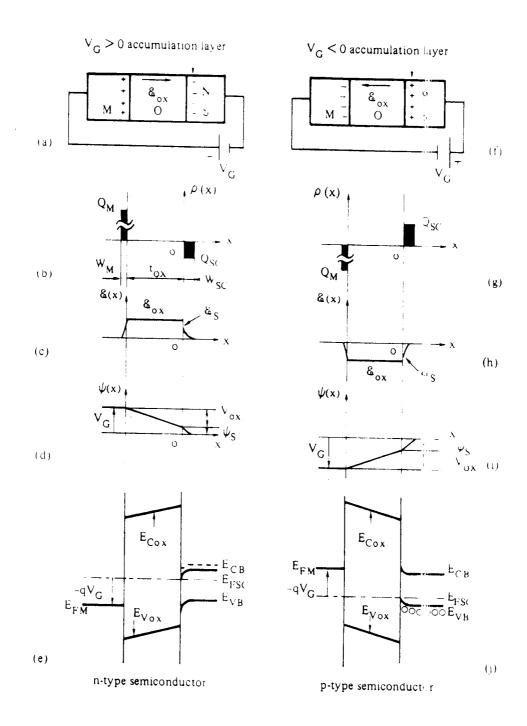

In the accumulation mode, the MOS structure is biased in such a way that the majority carriers are attracted towards the gate. In an n-type silicon (see Fig.2.1a) under a positive bias (or a negative bias for a

p-type silicon), a space charge layer (SCL) builds up near the metal oxide interface. It is due to an electron depletion or to a local reduction in the density of free carriers in the metal. Likewise, a layer of negative charges is generated in the silicon near the oxide-silicon interface. It is due to an electron accumulation or to a local increase in the density of free carriers in the silicon as shown by Fig. 2.1b. The condition of neutrality occurs when the amount of charges on the metal is equal but opposite in sign to that on the semiconductor that is.

$$Q_{M} + Q_{SC} = 0 \tag{2.1}$$

Figure 2.1c shows that in the bulk of the metal, the electric field E(x) is equal to zero. Hence, the presence of the charge  $Q_H$  is the reason for a positive discontinuity of the field E(x) at the Si-SiOz interface. The electric field E(x) remains constant throughout the oxide of thickness  $t_{ox}$ , this is due to the absence of charges in it.

At the oxide-silicon interface, we observe another discontinuity of the electric field  $(E_{ox} \longrightarrow E_{x})$  since the dielectric constant of the oxide  $\epsilon_{ox}$  is different from that of silicon  $\epsilon_{x}$ . The electrostatic potential  $\Psi(x)$  in the metal as shown in Fig.2.1d remains constant and equal to Vo upto the metal oxide interface.

- In the oxide,  $\Psi(x)$  decreases linearly until it reaches the value  $\Psi_{\bullet}$  at the oxide-silicon interface.

- In the silicon,  $\Psi(x)$  decreases rapidly from  $\Psi$ , to zero. Since the accumulation layer is very thin,  $\Psi$ , is very small (a few mV). It follows that the applied gate bias is given by:

$$V_G = V_{ox} + \Psi_s = V_{ox} = E_{ox} t_{ox}$$

(2.2)

where Vox is given by

$$V_{ox} = \frac{Q_M}{C_{ox}} \tag{2.3a}$$

and the capacitance of the oxide Cox by

$$C_{ox} = \frac{\epsilon_o \epsilon_{ox}}{t_{ox}} \tag{2.3b}$$

The energy band diagram of the MOS structure is shown in Fig.2.1e. The figure shows the variations of the potential  $E_P(x)$  in the three materials. Near the oxide-silicon interface, the energy bands bend so that the conduction band at the interface Ec moves towards the Fermi-level which is kept horizontal since the structure is in equilibrium. This is consistent with an increase of the probability of occupation

of the states by the majority carriers near the semiconductor interface.

Figure 2.1.e-f shows the same treatment for a p-type material.

#### 2.2.2 The Depletion Mode.

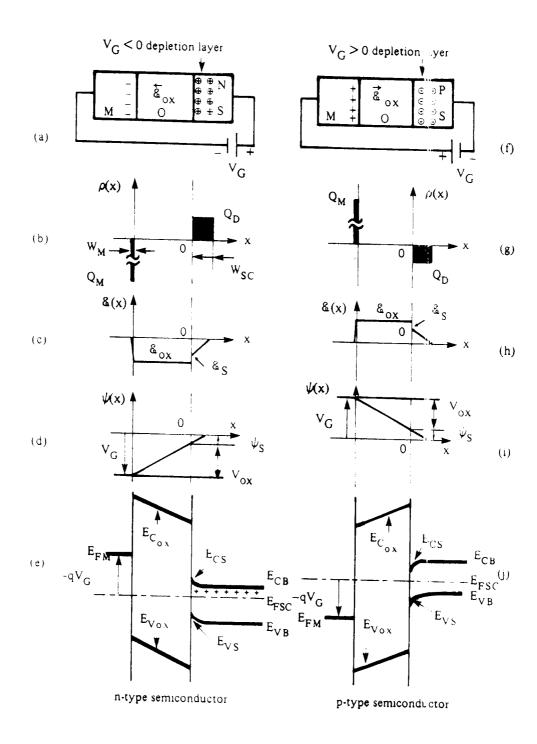

In the depletion mode, the MOS structure is biased in such a way the majority carriers of the substrate are repelled away from the Si-SiO2 interface towards the bulk. Thus, for an n-type silicon (Fig.2.2a)  $V_{G}<0$  and for a p-type  $V_{G}>0$ .

When the metal is negatively biased, a layer of negative charges builds up at the metal-oxide interface. It is due to an electron accumulation or to a local increase of the density of free carriers of the metal. A layer of positive charge is generated in the silicon near the Si-SiO2 interface because the electrons of the substrate which have been repelled by the field, leave behind the fixed positively ionized doping atoms (Fig.2.2b). The condition of electric equilibrium gives rise to a charge Qm on the metal such that:

$$Q_{\mathbf{M}} + Q_{sc} = 0 \tag{2.4}$$

where

$$Q_{sc} = q N_D W_{sc}, \qquad (2.5)$$

Fig. 2.1. a-e MOS structure under bias in accumulation mode, for an n-type silicon. a) Biasing conditions, b) Charge distribution, c) Field distribution, d) Potential distribution, and d) Knergy band diagram. f-j Same as above but for p-type semiconductor.

(After [35]).

No is the doping concentration and Wac is the width of the charge layer.

The field and the potential distribution can be obtained from the charge distribution illustrated in Fig.2.2b. Figure 2.2c shows that the electric field is zero in the bulk of the metal, hence the presence of  $Q_{M}$  is responsible for a negative discontinuity of E(x) at the metal-oxide interface. The electric field remains constant throughout the oxide layer since the oxide contains no charge.

At the Si-SiO2 interface, a discontinuity of the electric field has been observed, it is due to the same phenomenon as discussed in section 2.2.1. Within the space charge layer, the electric field varies linearly with distance x, where x is measured from the interface Si-SiO2. Poisson's equation, with the boundary conditions E(x)=0 at x=0 and E(x)=0 for x>Wsc shows that the potential  $\Psi(x)$  remains constant and equal to  $V_G$  as it is shown in Fig.2.2d. In the oxide,  $\Psi(x)$  increases linearly until it reaches the value  $\Psi_s$  at the Si-SiO2 interface. In silicon,  $\Psi(x)$  increase with respect to x from  $\Psi_s$  to zero in a quadratic manner. For x=0, the surface potential is given by:

$$\Psi_s = \frac{q N_D W_{SC}^2}{2\epsilon_o \epsilon_{sc}} \tag{2.6}$$

When Eqs. (2.3a) and (2.6) are used in Eq. (2.2), the expression of Va becomes:

$$V_{G} = \frac{Q_{M}}{C_{ox}} + \frac{q N_{D} W_{sc}^{2}}{2\epsilon_{o} \epsilon_{sc}}$$

(2.7)

Figure 2.2e illustrates the energy band diagram of the MOS structure. In the silicon, near the surface the bands are bent upward leading to a lower probability of occupation of the allowable states in the conduction band.

The same discussion can be carried out for a p-type silicon as described in Fig.2.2f to Fig.2.2j.

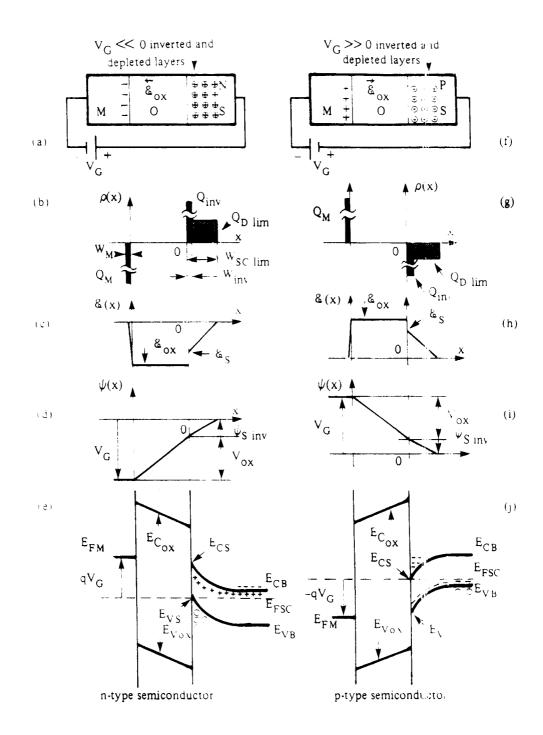

#### 2.2.3. The Inversion Mode.

The inversion mode starts when the bands experience a banding equal or greater than twice the bulk potential  $\phi_{\mathfrak{g}}$ . This happens if for a negatively biased n-type MOS structure, the amplitude of the gate signal is increased. This increase of gate signal brings negative charges on the metal electrode, which must be balanced by an equivalent increase on the semiconductor side. This is obtained by increasing Wac. Consequently, the band bending increases and the top of the valence band (Ev) at the surface gets closer to the Fermi-level. However, as band bending increases, the density

Fig. 2.2. a-e MOS structure under bias in depletion mode, for an n-type silicon. a) Biasing conditions, b) Charge distribution, c) Field distribution, d) Potential distribution, and d) Energy band diagram. f-j Same as above but for p-type semiconductor.

(After [35]).

of minority carriers (holes in the case of an n-type substrate) becomes important. When the hole concentration (p) at the silicon surface becomes larger than the concentration of the doping atoms (ND), an inversion layer [which is separated from the bulk of the silicon by depletion layer] builds up. The built up of the inversion layer is a threshold phenomenon. The threshold condition arises when the doping concentration equals the concentration of minority carriers at the surface. This condition can be written as:

$$p = N_v \exp\left(\frac{E_{is} - E_F}{kT}\right) = N_D = n_B = N_C \exp\left(\frac{E_F - E_C}{kT}\right) \qquad (2.8)$$

where Nv is the effective density of the states in the valence band, Ev the energy level of the valence band edge at the surface, E: the midgap level at the surface, Nc the effective density of the states in the conduction band, nB the concentration of the electrons in the bulk of the silicon and Ec the lower edge of the conduction band in the bulk.

To avoid comparison of minority carriers with the majority carriers, the former are expressed in terms of  $n_1$ , the intrinsic concentration, and  $E_1$ , the intrinsic energy level at midgap, so that Eq.(2.8) can be written as:

$$p = n_i \exp\left(\frac{E_{is} - E_F}{kT}\right) = n_B = n_i \exp\left(\frac{E_F - E_{iB}}{kT}\right) \quad (2.9)$$

where EiB is the midgap level at the bulk. From Eqs.(2.8) and (2.9), the surface potential  $\Psi_{s,low}$  required to reach the inversion can be expressed by:

$$q\Psi_{s,inv.} = E_{is} - E_{iB} = 2kT \ln\left(\frac{n_B}{n_i}\right) = 2kT \ln\left(\frac{N_D}{n_i}\right)$$

(2.10)

At the onset of inversion, the depletion layer reaches a limiting value given by:

$$W_m = q \left( \frac{2\epsilon_o \epsilon_{sc} |\Psi_{s,inv.}|}{q N_D} \right)^{1/2}$$

(2.11)

and the charge contained within the depletion layer reaches the value

$$Q_{DM} = q N_D W_m \tag{2.12}$$

The gate voltage necessary to reach the onset of the inversion, referred as threshold voltage and having a symbol  $V_{\mathbf{T}}$  is defined by:

$$V_T = -\frac{Q_{DM}}{C_{ox}} + \Psi_{s,inv}. \tag{2.13}$$

Once the inversion is reached, the distribution of charges, electric fields and potentials, and the energy band diagrams experience a change that is shown in Fig.2.3a to 2.3e. Figure 2.3b shows the negative charge Qm balanced by the sum of the charge contained in the inversion layer and that contained in the depletion zone, that is,

$$Q_{M} + Q_{inv} + Q_{DM} = 0 ag{2.14}$$

Since QD remains constant, any increase in QDM is cancelled by an increase in Qinv.. The field and potential distributions are similar to those of depletion except for the inversion region. Since the inversion layer has a negligible thickness, the potential  $\Psi_s$  and  $\Psi_{s,uv}$  are nearly equal, thus

$$V_G = -V_{ox} + \Psi_{s,inv}. \tag{2.15a}$$

$$V_{G} = -\frac{Q_{inv.} + Q_{DM}}{C_{ox}} + \Psi_{s,inv.}$$

(2.15b)

It is clear that when  $V_{G}$  increases,  $\Psi_{\text{s,inv.}}$  increases since  $V_{\text{ox}}$  is constant.

Fig. 2.3. a-e MOS structure under bias in inversion mode, for an n-type silicon. a) Biasing conditions, b) Charge distribution, c) Field distribution, d) Potential distribution, and d) Energy band diagram. f-j Same as above but for p-type semiconductor.

(After [35]).

#### 2.3. THE NON IDEAL MOS STRUCTURE.

A real or non-ideal MOS structure contains always charges located in the bulk oxide and/or at the oxide-semiconductor interface. These charges are tradititonally classified into four groups which are: 1) the mobile charges, 2) the fixed interface charges, 3) the interface trapped charges, and 4) the oxide trapped charges. These charges introduce a difference in the metal and semiconductor work functions that is,  $\Phi_M \neq \Phi_{sc}$ . This gives rise to an electric field in the insulator as well as in the semiconducture of the semiconductor even under no bias.

The mobile charges  $(Q_m)$  are in fact foreign ions mobile in the silicon network under the action of an electric field in a temperature range usually taken from zero to  $400 \circ C$ .

The fixed interface charges also called oxide fixed charges (Qf) are located close to the Si-SiO2 interface. They are impervious to the action of electric fields and are only affected by high temperature annealing.

The defects or impurities located at the Si-SiO<sub>2</sub> interface can act as carrier traps if their presence introduces energy levels in the silicon forbidden gap. They are then referred to as interface or surface states (or traps). These surface states can interchange carriers with both silicon bands and possibly with those of the oxide. The carriers temporarily

or permanently trapped in the interface form the so-called interface-trapped-charge  $(Q_{1t})$  and the amount of this charge depends on the applied bias.

The above mentioned charges influence the MOS diode characteristics in a different manner.

### 2.3.1 Influence of The Metal-Semiconductor

Work Function Difference.

In the case of ideal MOS structures, the surface potential of the metal is equal to that of the semiconductor; no fundamental change in the physical behaviour of the MOS structure occurs when the surface potentials are different. However, in this case there exists an electric field in the oxide (insulator) and in the top layer of the silicon. A bias must be applied to the MOS diode to flatten the silicon bands. This bias, henceforth called flat-band voltage, is given by:

$$V_{FB0} = \frac{\Phi_{M} - \Phi_{SC}}{q} = \frac{1}{q} \left[ \Phi_{M} - \chi + \frac{E_{G}}{2} \pm kT \ln \left( \frac{N}{n_{i}} \right) \right]$$

(2.16)

The sign (+) or (-) depends on the type of the semiconductor, (+) for a p-type and (-) for an n-type. In general, the MOS diode is studied by C-V methods [13-17], the effect of the work function difference is to shift the actual C-V curve with respect to the ideal one.

#### 2.3.2 Influence of The Oxide-Charges.

The oxide-charges can be mobile ions or oxide fixed charges which are distributed unevenly in the oxide bulk. The distribution of these charges is represented by a volume density  $\rho(x)$  which varies with distances and depends on time in case of electrically stressed MOS structures.

To study the influence of the charge distribution on MOS structures, the origin of the distance axis (x) is defined to be the metal-oxide interface and the various effects and phenomena occurring in the oxide and at the interface are integrated in the interval zero (the interface) to tox (the oxide thickness).

Using Gauss's law, the electric field experiences a discontinuity  $\delta E_{**}$  when crossing the charge layer and this discontinuity is given by:

$$\delta E_{ox} = \frac{\rho(x)dx}{\epsilon_o \epsilon_{ox}} \tag{2.17}$$

For flatband conditions in the silicon, the electric field should be equal to zero at the right hand side of the discontinuity, that is, the corresponding voltage giving flatband conditions is given by:

$$\delta V_{FB} = -\frac{\rho(x)xdx}{\epsilon_o \epsilon_{ox}}$$

(2.18)

The effects of all layers in the oxide is similar and hence can be added together, it comes out that the voltage necessary for flatband conditions is:

$$V_{FB1} = \int_{o}^{t_{ox}} \frac{\rho(x)x dx}{\epsilon_{o}\epsilon_{ox}}$$

(2.19)

The oxide fixed charges Qr are positive and have a different effect from that described before. These charges are produced due to the structural defects created during fabrication. The oxide fixed charges cause a band bending which can be corrected by a corresponding voltage given by:

$$V_{FB2} = \frac{Q_f t_{ox}}{\epsilon_o \epsilon_{ox}} \tag{2.20}$$

#### 2.3.3. Influence of The Interface Trapped Charges.

Interruption of the silicon lattice at the interface with the oxide introduces electronic states whose energy levels are distributed in the forbidden gap of the silicon. In a semiconductor, energy levels below Fermi-level Er are occupied and above it are not occupied and hence, there exists a trapped charge at the interface.

Any increase in the charge Qm on the metal electrode due to an increase of gate bias will be balanced on the silicon side by an increase of the space charge layer which results in an increase in the charge trapped in the interface states because the increase of the gate bias produces a filling of more surface states due to the displacement of the Fermilevel.

The interface traps do not react to high frequency signals, this is the reason why the overall capacitance in the high frequency C-V curves do not show any shift in conjunction to the surface states as it is the case in the low frequency C-V curves. When the flatband conditions are met, the charge trapped in the surface states (that can not follow the rapid change of the high frequency signal) are responsible for the shift of the high frequency C-V curve with respect to the low frequency C-V one. The value of the corresponding voltage necessary for the flatband conditions is given by:

$$V_{FB3} = \frac{Q_{ii}(FB)t_{ox}}{\epsilon_o \epsilon_{ox}}$$

(2.21)

At low frequencies, the interface traps modify both the overall capacitance as well as the C-V curves. This can be explained by the time available for the surface states to follow the gate signal variations.

### 2.3.4 Influence of The Dielectric Polarization.

In general, the polarization effect under normal

condition can be neglected in the case of  $SiO_2$  dielectrics. However, it can be very important in other dielectrics or  $SiO_2$  added with PSG layers. The application of an electric field  $\vec{E}$  generates dipoles which align themselves in the direction of the field. To quantify the polarization effect, the polarization vector P which is the sum of the dipolar moments per unit volume qR is introduced as

$$\vec{P} = \frac{\sum q \, \vec{R}}{volume} \tag{2.22}$$

The polarization is proportional to the electric field and is given by:

$$\vec{P} = \epsilon_o \chi_p \vec{E} \tag{2.23}$$

where  $\chi_{p}$  is the polarizability of the material.

The polarization does not modify the charge density in the bulk since, the overall charge of the dipole is equal to zero. However, the polarization gives birth to a superficial positive charge at the interface where the electric field is directed outwards and to a negative charge at the other interface. The charge densities of these superficial layers are equal to the polarization P.

#### 2.3.5 The Concept of Flat-band Voltage.

To calculate the capacitance of a MOS diode using

the flatband voltage on a C-V curve, one has to consider the resulting flatband voltage which is the sum of all the previously described flatband voltages and is given by:

$$V_{FB} = V_{FB0} + V_{FB1} + V_{FB2} + V_{FB3} + V_{FB4}$$

(2.24)

with  $V_{FB4}$  being the flatband voltage due to the polarization. This term is considerable in case of PSG added oxides and very small in pure Silicon-oxide.

The sum of the actions of the flatband voltages  $V_{\rm FB1}$ ,  $V_{\rm FB2}$  and  $V_{\rm FB3}$  can be represented by an image charge  $Q_{\rm im}$  given by:

$$Q_{im} = -C_{ox}(V_{Fb1} + V_{FB2} + V_{FB3})$$

(2.25)

which can be expressed as:

$$Q_{im} = \int_{0}^{t_{ox}} \frac{\rho(x)x \, dx}{t_{ox}} + Q_{f} + Q_{ifFB}$$

(2.26)

Except VFBO and VFB4, the other flatband voltages can not be calculated. They have to be measured. This makes the determination of the net flatband voltage VFB quite difficult and accurate methods of measurements do not exist, especially for short channel MOS transistors.

# CONDUCTION IN THIN INSULA TING FILMS

In integrated circuit technology, insulating layers are widely used. They can be used to passivate a surface or allow field effects in a semiconductor. If these insulators were perfect, they would block the flow of any current. In fact, under certain specific temperature and or field conditions, several physical processes allow electrical charges (electrons, holes, or ions) to move in insulators, thus leading to a sizable current densities, especially when the insulating films are thin (typically less than 1 µm).

# 3.1 INTRODUCTION.

An electric current in an insulator can result from the flow of electrons and/or ions. The present chapter deals only with electronic conduction. Electrons can either be intrinsic (belonging to the insulator) or extrinsic (injected from nearby layers -electrode-).

In the case of intrinsic electrons, the carrier density is low (there are few conduction electrons naturally available in an insulator) and conduction is of the ohmic type with very high resistivity.

Two cases are possible in case of extrinsic electrons. 1) The electrodes behave as unlimited sources. The current is then only limited by the bulk of the insulator (Poole-Frenkel effect, space charge limited current, hoping conduction). 2) The electrodes make limited carrier injection. The electrons once introduced travel in free flight inside the insulator (Schottky effect if the energy of the electrons is sufficient to propel them into the insulator conduction band; tunnel effect otherwise).

The different conduction cases that will be discussed next, suppose that the insulating layer is wholly homogeneous. This condition is satisfied for layers thicker than 50 nm but rarely satisfied for thinner layers. When the insulator is not homogeneous, it is difficult to introduce,

in the mathematical models, the parameters defined by geometrical considerations. In addition, the range of applied bias should not exceed the rigidity of the insulator that is, the electric field should not exceed  $5.10^6 \ V.Cm^{-1}$ .

# 3.2. THE SCHOTTKY (OR THERMIONIC) CURRENT.

The thermionic current or schottky current is due to the electrons which transit above the potential barrier, i.e, those of energy  $E > \Phi_m$  and is given by [35]:

$$J = \frac{4\pi m^* q k^2 T^2}{h^3} \left( 1 - \exp\left(-\frac{V}{kT}\right) \right) \exp\left(-\frac{\Phi_m - \xi}{kT}\right)$$

(3.1)

where:

m\* is the electron effective mass, q the coulombic charge, h the Planck's constant, k the Boltzman's constant, T the temperature in Kelvin, V the bias voltage, and  $\Phi_m - \xi$  is the effective metal-insulator barrier.

We notice that for V/kT>>1, the expression [1-exp(-V/kT)], which takes into account the flux of electrons in both directions, tends towards 1. At room temperature, this condition corresponds to V>>25 mV.

As expected, the current flow is a thermally activated process (the electrons must get over the barrier to cross the insulator). The activation energy is  $\Phi_o - \beta_s \xi^{1/2}$ , where  $\Phi_o$  is the difference between the insulator-metal

barrier height and  $\beta_i \xi^{1/2}$  is the barrier lowering due to image force. A plot of  $\ln(J/T^2)$  versus 1/T yields a straight line with a slope determined by the permittivity  $\epsilon_i$  of the insulator.

### 3.3. THE TUNNELLING CURRENT.

The tunnel emission is caused by field ionization of trapped electrons into the conduction band or by electrons tunnelling from the metal Fermi energy into the insulator conduction band.

The tunnelling current density J(V,T) is given by [36]:

$$J(V,T) = \frac{4\pi m^* q}{h^3} \cdot \frac{\exp(-b_1)}{c_1^2}.$$

$$\frac{\pi c_1 kT}{\sin \pi c_1 kT}.(1 - \exp(-c_1 V)) \tag{3.2}$$

with

$$b_1 = \alpha^* \int_{x_{11}}^{x_{21}} (\Phi(x) - \xi_1)^{1/2} dx$$

(3.3)

$$c_1 = \frac{\alpha^*}{2} \int_{x_{11}}^{x_{21}} (\Phi(x) - \xi_1)^{-1/2} dx$$

(3.4)

$$\alpha^* = \alpha \left(\frac{m^*}{m}\right)^{1/2} \tag{3.5}$$

where  $\alpha = 10.25$  (in  $eV^{-1/2}.nm^{-1}$ ) (the other symbols have their previous meanings).  $x_{11}$  and  $x_{21}$  are the abscissae of the turning points for electrons whose energy is equal to the Fermi level in the metal.

The tunnel emission is strongly dependent on the applied voltage but essentially independent of temperature. When the bias is high, the effective thickness is changed to  $X_{21} = t_i \cdot \Phi_o / V$ ,  $X_{11}$  being still nil. Replacing the value  $X_{11}$  and  $X_{21}$  in Eq.(3.3) and (3.4), the tunnelling current expressed by Eq.(3.2) becomes:

$$J = \frac{q^2}{8\pi h} \cdot \frac{V^2}{t_i \Phi_o} \cdot \exp\left(-\frac{2}{3} \cdot \alpha^* \cdot t_i \cdot \frac{\Phi_o^{3/2}}{V}\right)$$

(3.6)

with to being the thickness of the insulator. Equation (3.6) describes the Fowler-Nordheim type of current.

# 3.4. THE POOLE-FRENKEL CURRENT.

The Poole-Frenkel emission is due to field-enhanced thermal excitations of trapped electrons into the conduction band. For trap states, the expression of the current density is identical to that of the  $S_0^2$ hottky emission. The barrier height however, which is the depth of the trap potential well and the quantity  $\xi^{1/2}$  is larger than in the case of Shottky emission by a factor of two because the barrier

lowering is twice as large due to the immobility of the positive charges. The expression of the Poole-Frenkel current depends on the insulator thickness and on trap sites presence in the insulator. Three major cases can be distinguished [35]:

1) Thick insulator without traps.

The current in this case is given by :

$$J = q(N_c N_D)^{1/2} \cdot \mu \cdot \exp\left(-\frac{\Phi_D}{2kT}\right) \cdot \exp\left(\frac{\beta_{BF}}{2kT}\xi^{1/2}\right)\xi$$

(3.7)

where:

No is the equivalent density of states in the insulator conduction band, No the concentration of donor atoms,  $\Phi_D$  the potential of the donor states with respect to the conduction band of the insulator,  $\mu$ , the mobility of electrons, and  $\beta_{BF}$  is given by  $(q/(\pi\epsilon_a\epsilon_l))^{1/2}$ .

2) Thick insulator with traps.

The poole-Frenkel current for this case is found to be:

$$J = q \cdot N_c \cdot \left(\frac{N_D}{N_t}\right)^{1/2} \mu.$$

$$\exp\left(-\frac{\Phi_D + \Phi_t}{2kT}\right) \cdot \exp\left(\frac{\beta_{PF}}{2kT} \cdot \xi^{1/2}\right) \cdot \xi \tag{3.8}$$

where  $N_t$  is the spatial density of the carrier traps of the insulator and  $\Phi_t$  is the potential of the traps with respect to the conduction band of insulator.

3) Thin insulator with or without traps.

The current for the case of thin or thick insulator is identical and given by:

$$J = q.N_c.\mu.\exp\left(-\frac{\Phi_o}{kT}\right).\exp\left(\frac{\beta_{PF}}{kT}.\xi^{1/2}\right).\xi \qquad (3.9)$$

In all cases, the quantity  $ln(J/\xi)$  varies linearly with  $\xi^{1/2}$ .

# 3.5. THE HOPPING CURRENT.

In the case of hopping conduction, the energy of the electron is inferior to the maximum energy of the potential energy barrier between two sites. The electrons can still transit using the tunnelling effect. The hopping current can be derived, using the following equation:

$$J = \frac{q^2}{kT} . n^* . \Gamma_s . \alpha^2 . \xi \tag{3.10}$$

where  $n^*$  is the electron density on the sites,  $\alpha$  is the distance between two sites, and  $\Gamma_s$  is the hopping frequency and is given by:

$$\Gamma_s = \frac{1}{\tau_o} \cdot \exp\left(\frac{-4\pi m^*}{h} \cdot \Phi_m \cdot \alpha\right) \tag{3.11}$$

where  $\tau_o$  is a time constant and  $\Phi_m$  is the energy corresponding to maximum barrier (the other symbols have their usual meanings).

The corresponding current comes out to be:

$$J = \frac{q^2}{kT} \cdot \frac{\alpha^2}{\tau_o} \cdot n^* \cdot \xi \cdot \exp\left(\frac{-4\pi m^2}{h} \cdot \Phi_m \cdot \alpha\right)$$

(3.12)

When the insulator contains no traps, the hopping conduction does not depend on temperature. When the insulator contains traps, the conduction depends strongly on temperature. In any case, the current J is always proportional to bias.

# 3.6. THE SPACE CHARGE-LIMITED CURRENT.

In the case of Poole-Frenkel and hopping conductions, the electric field is assumed constant. When the electron injection is strong, this hypothesis is no more valid and the potential distribution should be calculated using Poisson's equation. The space charge current results from a carrier injection into the insulator where no compensating charge is present. This current has different expressions for different injections.

1) Very weak injection.

When the injection is very weak, the insulator charge density is nil and the electric field is therefore constant. This ohmic mode occurs as long as the insulator is electrically quasi-neutral, i.e, as long as all donor centers are not filled. The current is then given by:

$$J = q \cdot n(x) \cdot \mu \cdot \frac{V}{t_i}$$

(3.13)

where n(x) is the number of conduction electrons,  $t_1$  the insulator thickness, and V the applied bias.

2) Strong injection.

In case of strong injection, the insulator traps fill up and a space charge appears. The current is then given [35] by:

$$J = \frac{9}{8} \cdot \mu \frac{\epsilon_i \cdot \epsilon_o}{t_i^3} \cdot \theta \cdot V^2$$

(3.14)

where

$$\theta = \frac{N_c}{N_D} \cdot \exp\left(-\frac{\Phi_t}{kT}\right) \tag{3.15}$$

with  $N_t$  is the trap density,  $N_C$  the density of states in conduction band, and  $\Phi_t$  the energy difference between the conduction band and trapping site.

3) Very strong injection.

In this case, all traps being filled the space charge is due to conduction electrons and the current is given by:

$$J = \frac{9}{8} \cdot \mu \cdot \frac{\epsilon_i \cdot \epsilon_o}{t_i^3} \cdot V^2$$

(3.16)

At low voltage and high temperature, current is carried by thermally excited electrons hopping from one isolated state to another. This mechanism yields an ohmic characteristic exponentially dependent on temperature.

# 3.7. OTHER TYPES OF CONDUCTION.

The ionic conduction is similar to a diffusion process. Generally the dc ionic conductivity decreases during the time the electric field is applied, since ions can not be readily injected or extracted from the insulator. After an initial current flow, positive and negative space charges will build up near the metal-insulator and the semiconductor-insulator interfaces. This causes a distortion of the potential distribution. When the applied field is removed large internal fields remain, which cause some, but not all of the ions to flow back toward their equilibrium position, thus resulting in a hysteresis effects. The ionic current is proportional to  $E.T^{-1}.\exp(-\Delta E_{at}/kT)$  where  $\Delta E_{at}$  is

the ion activation energy, E is the electric field, and T is the temperature in K degree.

The ohmic conduction is basically identical to the ionic conduction except that the ohmic current resulting from the ohmic conduction increases with temperature. Whereas in ionic conduction, the ionic current decreases drastically with increase of temperature. The ohmic current in insulators is always referred to as leakage current. The ohmic current is found to be proportional to  $F.\exp(-\Delta F_{as}/kT)$  where  $\Delta F_{as}$  is the electron activation energy.

The hot carrier conduction phenomenon occurs under special condition and in particular devices. This type of conduction is encountered in MOSFETs; when the channel is under the action of a high field, the hot carriers originating from the drain moving towards the source or vice versa can tunnel through the oxide or go to the substrate where they recombine. This results in a gate to substrate current that flows through the oxide. The gate and substrate current are not usually equal [37-38]. There is no standard formula expressing hot carrier currents in terms of insulator parameters.

For a given insulator, each conduction process may dominate in a certain range of temperature and bias. The tunnel emission has the strongest dependence on the applied

voltage and the shottky emission has the strongest dependence on the temperature. The space charge limited process is dependent on temperature but shows quite an important dependence on the applied gate voltage. The Poole-Frenkel process is important at moderate temperature and field. ohmic and ionic conduction processes are of less importance among the above described phenomena however, the ionic process is severely affected by high temperature. The hopping process shows the same dependence on temperature and voltage as the ionic process. The hot carrier process occurs only at very high field and or temperature. The processes are not also exactly independent of one another and should be carefully examined. For example, for the large space-charge effect, the tunnelling characteristic is found to be similar to the Shottky-type emission [39].

Basic Conduction Processes in Insulators.

| Conduction<br>Mode        | Expression of current                                                                                                                      | Dependence on<br>temperature<br>and field             |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Schottky                  | $4\pi m^{\bullet} q \frac{k^2 T^2}{h^3} \left( 1 - \exp\left(-\frac{V}{kT}\right) \right) \cdot \exp\left(-\frac{\Phi_m - \xi}{kT}\right)$ | $T^2 \exp\left(\alpha \cdot \frac{V^{1/2}}{T}\right)$ |

| Tunnel-<br>ling           | $\frac{q^2}{8\pi h} \frac{V^2}{t_i \Phi_a} \exp\left(-\frac{2}{3} \alpha^* t_i \frac{\Phi_a^{3/2}}{V}\right)$                              | $V^2 \exp\left(-\frac{b}{V}\right)$                   |

| Poole-<br>Frenkel         | $qN_c\mu\exp\left(-\frac{\Phi_a}{kT}\right)\exp\left(\frac{\beta_{FF}}{kT}\xi^{1/2}\right)\xi$                                             | $V \exp\left(2a \frac{V^{1/2}}{T}\right)$             |

| Space char-<br>ge limited | $\frac{9}{8} \cdot \mu \frac{\epsilon_i \cdot \epsilon_o}{t_i^3} \cdot V^2$                                                                | c.V²                                                  |

| Ohmic                     | $A.E.\exp\left(-\frac{\Delta E_{ae}}{kT}\right)$                                                                                           | $V \exp\left(-\frac{d}{T}\right)$                     |

| Ionic                     | $B.\frac{E}{T}\exp\left(-\frac{\Delta E_{at}}{kT}\right)$                                                                                  | $\frac{V}{T} \exp\left(-\frac{f}{T}\right)$           |

| Hot-<br>carrier           | No standard known formula.                                                                                                                 | Increases<br>with field<br>and tempe-<br>rature       |

All symbols have their previous meanings. The constants a, b, c, d, and f are positive and independent of temperature and field. A and B are constants.

# THE SUBSTRATE CURRENT STUDIED BY THE CHARGE PUMPING TECHNIQUE

The charge-pumping phenomenon is one of the chief sources which can give rise to the substrate current in MOS transistors. As the present study is also based on the measurement of the substrate current which is supposed to arise due to the same process of charging and discharging of the surface states as used in the charge pumping, the present technique may be supposed to be an alternative approach to charge pumping technique. Therefore, a thorough study of the charge pumping current is necessary to understand the different physical phenomena related to the generation of substrate current.

# 4.1. INTRODUCTION.

Since the existence of the surface states at the silicon-silicon dioxide interface was demonstrated, several techniques have been proposed for the determination of the density of these states and of their energy distribution in the forbidden energy band gap of silicon. Most of these techniques are based on measurements on MOS capacitor [13-22] and have been studied in great details. Consequently they have became sufficiently reliable to be used in most laboratories. For the determination of the surface state density on MOS transistors only a few techniques are reliable. However, they are not commonly used, partly because of poor quantitative reliability and partly because they are not very practical to use. Therefore, none of these techniques can be qualified as generally accepted for MOS transistors.

Recently, a new method called charge-pumping technique is developed to characterize MOS transistors. The charge pumping technique was evidenced by Brugler and Jespers in 1969. They have shown [23] that repetitive gate pulses of magnitude sufficient to invert the conductivity type in the channel of a MOS transistor can stimulate a net flow of majority carriers from the source and drain to the substrate. This current is observed as a dc substrate current.

The charge pumping technique is based on the recombination process at the silicon-silicon dioxide (Si-SiO2) interface involving the surface states. This induces a substrate current which can be related to the surface states density. In spite of its capability for measurements on small area MOS transistors, it never became a standard technique because of some ill-understood phenomena which made the method qualitative rather than quantitative.

# 4.2. THE CHARGE PUMPING TECHNIQUE.

In a MOSFET, there exists a possibility of charging and discharging the surface states with carriers originating from the drain and source terminals of the device. This phenomenon can occur under the effect of a train of gate voltage pulses which charge and discharge the surface states provided that the amplitude of these pulses is such that their bottom (base) level is within the deep accumulation region and their top level is within the inversion region. This produces a dc current that is detected at the substrate. This current is found to have a direction opposite to that of the transistor's p-n junctions leakage currents.

# 4.2.1 Basic Principles of The Charge Pumping Technique.

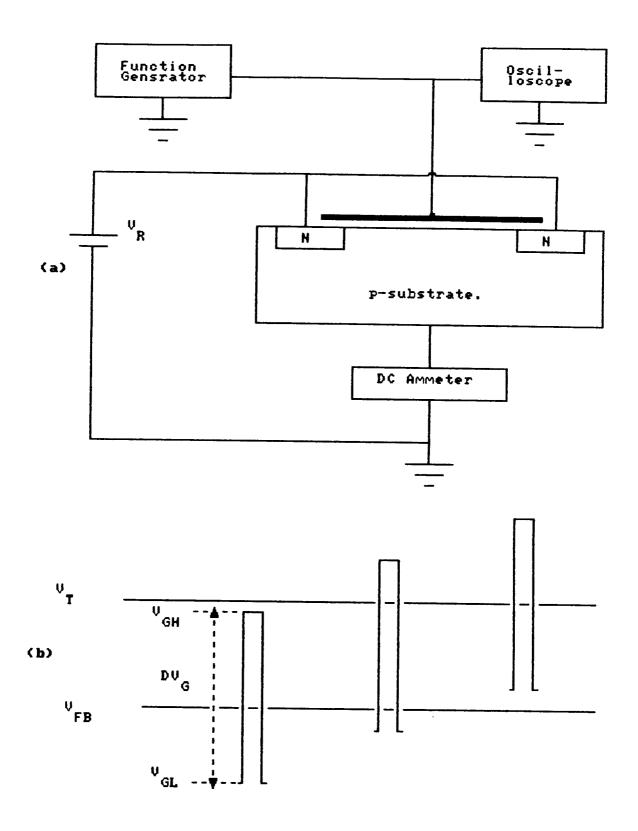

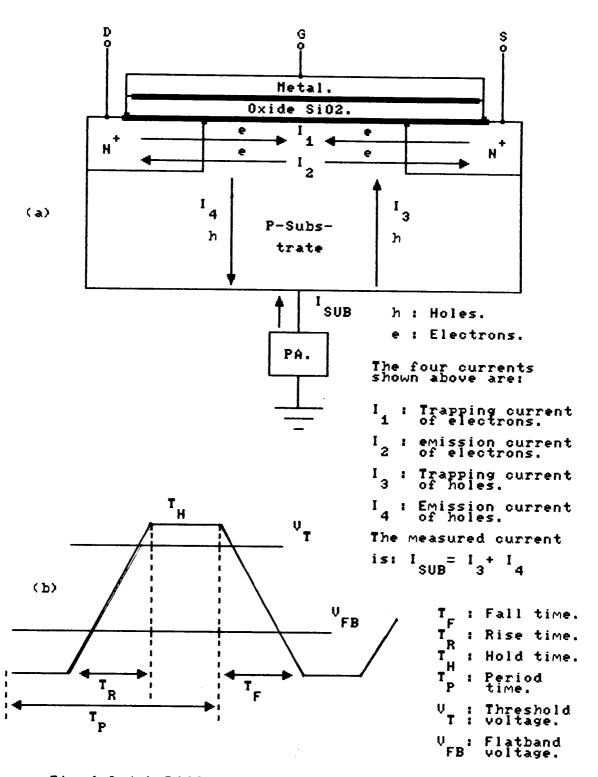

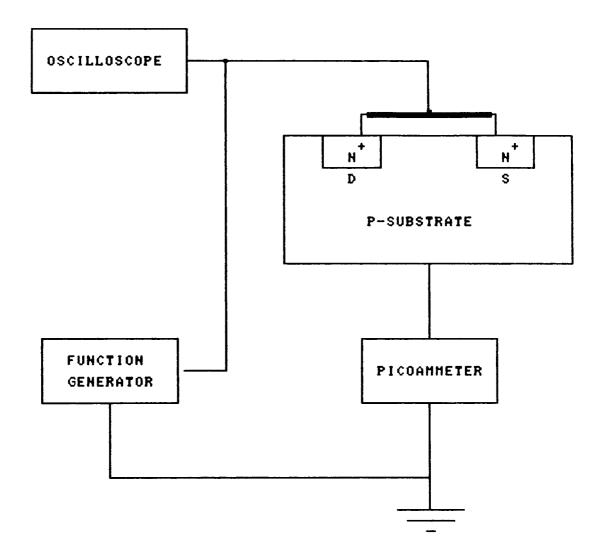

The experimental set up used in the charge pumping method was first described by Brugler and Jespers [23]. It

is illustrated in Fig.4.1a. To an n-channel MOS transistor, a gate voltage signal of amplitude such that it can sweep the energy interval from the deep accumulation to the deep inversion is applied. The drain and source are short-circuited together and connected to a dc reverse-biasing voltage source. The substrate is connected to the ground through a dc picoammeter which measures the resulting charge pumping current.

# 4.2.2 Theory of The Charge Pumping Technique.

When a transistor is pulsed into inversion, the surface region becomes deeply depleted and electrons will flow from the source and drain regions into the channel where some of them will be captured by the surface states. When the gate pulse is driving the surface back into accumulation, the mobile charges drift back to the source and drain under the influence of the reverse bias, but the charges trapped in the surface states will recombine with the majority carriers from the substrate and give rise to a net flow of negative charges into the substrate. The charge Qas that will recombine is given by:

$$Q_{ss} = A_g.q. \int D_u(E)dE. \qquad (4.1)$$

It can also be expressed as

Fig.4.1 (a) Basic experimental set-up for charge pumping measurements.

(b) Illustration of the base level method on an n-channel MOSFET.

$$Q_{ss} = A_g \cdot q^2 \cdot \overline{D_u} \Delta \Psi_s \tag{4.2}$$

where:

- -A<sub>s</sub> is the area of the channel of the MOSFET  $(Cm^2)$ .

- -q is the electron charge (C),

- $-\Delta\,\Psi_{\bullet}$  is the total sweep of the surface potential V,

- $-\overline{D_u}$  is mean surface state density averaged over the energy level swept by the Fermi-level  $Cm^{-2}$   $eV^{-1}$ ).

- $-D_{\pi}(E)$  is the surface density of state at energy E.

When applying repetitive pulses to the gate with frequency f, this charge  $Q_{\text{SS}}$  will give rise to a current in the substrate. This current can be written as:

$$I_{cp} = f \cdot Q_{ss} = f \cdot A_q \cdot q^2 \cdot D_u \cdot \Delta \Psi_s$$

(4.3)

By measuring this substrate current, an estimate of the mean capture cross-section and the interface-states density over the energy range swept by the gate pulse can be obtained. However, this substrate current is found to consist of two components, the surface states component and the geometric component. The geometric component is an undesirable effect. Brugler [23] concluded that to eliminate this undesirable component of the current, the experimental device should show a ratio of the length (L) and the width (W) larger than unity (W/L >> 1).

# 4.2.3 Techniques of Sweeping The Surface Potential.

The charge pumping measurements have been performed in different manner. All of these measurement methods are based upon the way of applying the gate voltage signal to the MOS transistor. The most commonly used methods are listed below:

- 1. keeping the pulse base level in accumulation and pulsing the surface into inversion with increasing amplitude [23].

- 2. varying the pulse base level from inversion to accumulation while keeping the amplitude of the pulse constant [25] as illustrated in Fig.4.1b.

- 3. keeping the pulse base level in accumulation and pulsing the surface into inversion with a sufficient amplitude. However, the pulse base level does not reach the accumulation level while coming back from the inversion region. It goes through an intermediate position which is referred to as a step voltage before reaching the accumulation region [29].

- 4. keeping the pulse base level between the flatband voltage and the threshold voltage and pulsing the surface into inversion and then into accumulation alternately [32].

In the first method, a saturation level of the charge pumping current is expected when the top of the gate pulse exceeds the threshold voltage of the MOS transistor. This saturation value is reached when the surface potential

sweep  $\Delta \Psi_s$  reaches its maximum value. However, this saturation value, beside the surface potential, depends on the value of the reverse biasing voltage  $V_R$ .

In the second method, the charge pumping current is found to be very small when the gate pulse is less than the flatband voltage  $V_{FB}$  or greater than the threshold voltage  $V_{T}$ . The maximum value of the current is obtained when the pulse amplitude  $\Delta V_{G}$  is greater than the value  $|V_{FB}-V_{T}|$  and the amplitude of the pulse is such that its base level is below the flatband voltage  $V_{FB}$  and its top level is beyond the threshold  $V_{T}$  while the reverse biasing voltage  $V_{R}$  is equal to zero. This method allows the complete sweep of the surface potential.

The third method provides the knowledge, which of the surface states act as traps and which as recombination centers. It is also used to measure the surface states at the Si-SiO2 interface.

The last method, called modified charge pumping technique or interface probing, enables uninterrupted scanning of bandgap and provides the mean value of capture cross section of the carriers. It also allows an experimental characterization of the distribution of capture cross section and elimination of a number of potentially distorting effects associated with the original charge pumping technique.

# 4.3. THE IDEA OF EMISSION OF CARRIERS FROM THE SURFACE STATES.

The idea of carrier emission was introduced by Groeseneken et al [27]. It is based on the emission theory described by Simmons and Wei [40-41].

When a transistor is switched from accumulation towards inversion and vice versa, the state of the channel goes through three different modes each of which can be characterized by a different time constant and essentially corresponds to one of the conventional operating regions of the MOS structure (i.e., accumulation, depletion, and inversion). For the sake of simplicity, let us consider an n-channel transistor. A gate signal of a given fall and rise times and known amplitude and frequency is applied to the gate of a MOSFET. When the surface region is in accumulation, all of the surface-states below the quasi-Fermi level of the minority carriers are filled with electrons, while those above it are empty. The states are thus in equilibrium with the energy bands. When the gate voltage increases (starting from deep accumulation to deep inversion), the surface potential is changing at a certain rate. Therefore, holes that have to be emitted from the surface states towards the valence band in order to maintain equilibrium, will flow back to the substrate. Initially, the rate of emission of trapped charge is able to meet the one

that is required to keep the trap occupation in dynamic equilibrium with the voltage sweep. The channel is in the steady state condition as long as [40] the rate of change of the trapped charge density required to maintain steady state condition is greater than the real rate of the change of trapped charge density as imposed by the emission of holes to the valence band. As soon as this rate of change of trapped charges imposed by the emission process becomes smaller than the one required by the voltage sweep at the gate, the channel enters the non-steady state regime and the emptying of the traps is completely controlled by the emission process described by Simmons and Wei [40] and Kaden and Reimer [42]. The transition from the non-steady state to the steady state occurs at a certain gate voltage corresponding to the flatband voltage VFB. The surface potential sweeps very fast from the flatband position to the strong inversion through the depletion region. In this depletion region, the concentration of carriers is very small. Therefore, the time constant is only controlled by that of the hole emission. Because of this high rate of change of surface potential, the steady state condition will cease very shortly after reaching the flatband conditions and hence, starting from the flatband voltage the channel is in the non-steady state regime. When the gate voltage is near the threshold voltage  $V_T$ , the trapping time constant is approximately given by [23]:

$$\tau_i = \frac{1}{V_{th} \sigma_n n_s} \tag{4.4}$$

where  $n_{\mathbf{z}}$  is the surface concentration of minority carriers, Vth is the thermal velocity of carriers, and  $\sigma_n$  is the capture cross section of electrons. This time constant becomes gradually smaller and consequently, electrons will be trapped by the surface states not yet emptied. This process will become important when the gate voltage exceeds the threshold voltage. At this time, the electrons coming from the drain and source junctions will fill the remaining traps. The same mechanisms operate when the gate is pulsed back to accumulation.

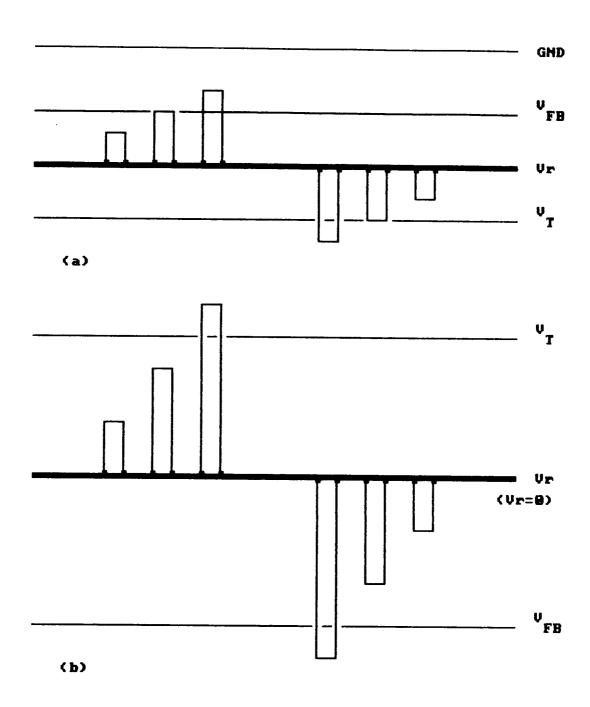

It has been found [27] that, during the voltage sweep from accumulation to inversion and vice versa, a steady state is followed by a non-steady state emission of carriers. During the total sweep from deep accumulation to deep inversion while assuming the average density  $\overline{D_n}$  of the surface states constant, four currents that are shown in Fig. 4.3a have been observed. These currents are:

$$I_1 = -A_q q^2 f \overline{D_u} \Delta \Psi_e \tag{4.5}$$

$$I_2 = A_g q^2 f \overline{D_u} \Delta \Psi_{ee} \tag{4.6}$$

$$I_3 = -A_g q^2 f \overline{D_u} \Delta \Psi_h \tag{4.7}$$

$$I_4 = A_g q^2 f \overline{D_{ii}} \Delta \Psi_{he} \tag{4.8}$$

The net charge pumping current measured at the substrate is:

$$I_{cp} = I_3 + I_4 = A_q q^2 f \overline{D_u} (\Delta \Psi_{he} - \Delta \Psi_h)$$

(4.9)

and the source/drain current is:

$$I_{S/D} = I_1 + I_2 = A_q q^2 f \overline{D_{tt}} (\Delta \Psi_{ee} - \Delta \Psi_e)$$

(4.10)

Simmons and Wei [41] found that the emission levels of surface states for electrons are :

$$E_{em,e} - E_i = -kT \ln \left( V_{th} \sigma_n n_i t_{em,e} + \exp \left( \frac{E_i - E_{F,inv}}{kT} \right) \right), \quad (4.11)$$

and for holes:

$$E_{em,h} - E_i = kT \ln \left( V_{th} \sigma_h n_i t_{em,h} + \exp \left( \frac{E_{F,acc.} - E_i}{kT} \right) \right)$$

(4.12)

where tem.e and tem.n are respectively the non-steady state emission times of electrons and holes and the exponential terms are introduced to account for the case when the emission levels are situated closer to the band edges than to the quasi-Fermi levels. Groeseneken et al showed [27] that the emission times of the electrons and holes can be expressed respectively as:

$$t_{em,e} = \frac{|V_{FB} - V_T|}{|\Delta V_G|} t_f,$$

(4.13)

$$t_{em,h} = \frac{|V_{FB} - V_{T}|}{|\Delta V_{G}|} t_{r}$$

(4.14)

for square pulses and:

$$t_{em,e} = \frac{|V_{FB} - V_T|}{|\Delta V_G|} \cdot \frac{1}{f} \cdot \alpha \tag{4.15}$$

$$t_{em,h} = \frac{|V_{FB} - V_T|}{|\Delta V_G|} \cdot \frac{1}{f} \cdot (1 - \alpha)$$

(4.16)

for triangular pulses.

Where  $V_{FB}$  is the flat band voltage,  $V_{T}$  the threshold voltage,  $\Delta V_{G}$  the amplitude of the pulse,  $t_{F}$  and  $t_{F}$  the fall and rise times of the pulses as shown in Fig.4.2b, f the frequency of the signal, and  $\alpha$  the fraction of the pulse when it is rising.

Fig. 4.2 (a) Different currents generated under charge pumping effect.

(b) Gate pulse shape applied to the MOSFET.

The charge pumping current obtained after manipulating Eq.(4.2) using the Eqs.(4.11), (4.12), (4.13), (4.14), (4.15), and (4.16) is found to be:

$$I_{cp} = 2q f \overline{D_{u}} A_{g} . kT . \left[ \ln \left( V_{th} . n_{t} . \sqrt{\sigma_{h} \sigma_{n}} \right) + \left( \frac{\left| V_{FB} - V_{T} \right|}{\left| \Delta V_{G} \right|} . \sqrt{t_{f} t_{r}} \right) \right]$$

$$(4.17)$$

for square pulses and by:

$$I_{cp} = 2q f \overline{D_{it}} A_g kT \left[ \ln(V_{th} \cdot n_i \cdot \sqrt{\sigma_h \sigma_n}) + \ln\left(\frac{|V_{fB} - V_T|}{|\Delta V_G|} \cdot \frac{1}{f} \sqrt{\alpha(1 - \alpha)}\right) \right]$$

(4.18)

for triangular pulses.

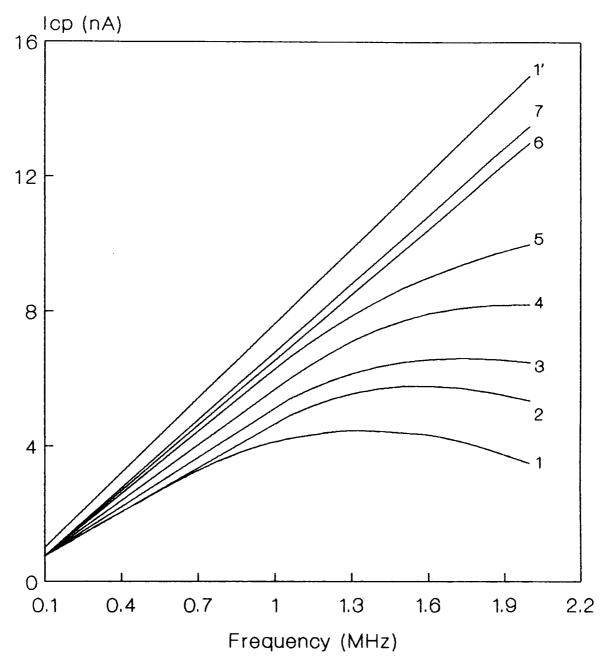

At higher frequencies, the charge pumping current is found to vary in a non linear manner with respect to frequency. Hence the previous formulae are not valid, even though they do not show any ambiguity or do not have any of their terms adversely affected by very high frequencies. Groeseneken et al explained this phenomena based on the surface states response time. The surface states need a certain time to capture the carriers present in the channel and hence, the linearity of the  $I_{CP}$  versus f curves is valid upto the stage

where the inversion time becomes smaller than the trapping time constant of the surface states. At this stage, the surface states will no longer be completely filled and the charge pumping current decreases as it is shown in Fig.4.3.

# 4.4. EFFECT OF THE FREQUENCY ON THE CHARGE PUMPING CURRENT.

The charge pumping current [given by Eq.(4.2)] is directly proportional to frequency. This is due to the fact that, the charge pumping current is the result of the charges produced under the effect of a gate signal. When a gate pulse is applied to the gate of a MOSFET, the charges are produced in each cycle and the electric current is constituted by the charges of all cycles in one second which explains the proportionality of the current to frequency. Figure 4.3 illustrates the dependence of the charge pumping current on the frequency. This current is not only affected by the frequency, but also by the shape of the gate signal.

Groeseneken et al found that the linear dependence of the current on frequency is due to the constant fall and rise times of the gate pulse. This gives a constant amount of emitted charge per cycle or a constant amount of the recombining charge per cycle. However, for triangular pulses the frequency dependent fall and rise times give rise to a frequency dependent emitted charge and therefore, to a frequency dependent charge recombining with the substrate

Fig.4.3 Charge pumping current versus frequency. Curve 1' is for square pulses; curves 1 to 7 are for triangular pulses with Vgh increasing from Vt (cur.1) to Vt+4 V (cur.7). Influence of trapping time constant. (After [27]).

majority carriers as expressed by Eq.(4.18). This charge-frequency dependence is used to determine some transistor (MOSFETs) parameters.

# 4.4.1. Determination of capture cross-section of carriers.

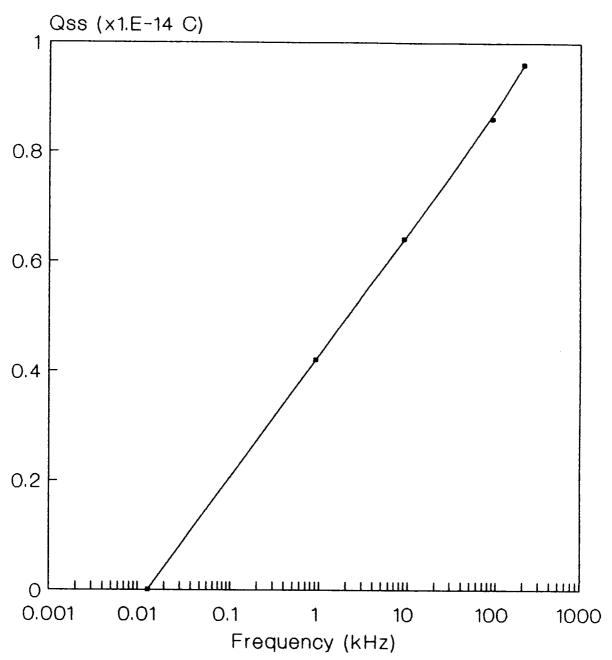

A train of triangular pulses of 15% rise and 85% fall times (or a sawtooth signal shape) is applied to the gate of a MOSFET with the source/drain connected to a reverse biasing voltage. The charge per cycle is measured and plotted with respect to frequency on a semilogarithmic plot. The variation of the amount of charge is found to be linear with respect to logarithmic variation of frequency and is given by:

$$Q_{ss} = \frac{I_{cp}}{f} \tag{4.19}$$

Replacing  $I_{\text{cp}}$  by its expression given by Eq.(4.18), the charge  $Q_{\text{ss}}$  becomes:

$$Q_{ss} = 2q A_g \overline{D_{tt}} kT \left[ \ln \left( V_{th} \cdot n_t \sqrt{\sigma_h \sigma_h} \right) + \left( \frac{|V_{fB} - V_T|}{|\Delta V_g|} \cdot \frac{1}{f} \cdot \sqrt{\alpha (1 - \alpha)} \right) \right]$$

(4.20)

The extrapolation of the curve  $Q_{22}$  versus log(f) to the zero value of the charge gives a certain frequency  $f_o$  which can

be used to obtain the value of the geometrical mean capture cross section. It is obtained by solving Eq.(4.20) for  $Q_{22}=0$  so that:

$$\sqrt{\sigma_h \sigma_n} = \frac{1}{V_{th} \cdot n_t} \cdot \frac{|\Delta V_G|}{|V_{FB} - V_T|} \cdot \frac{f_o}{\sqrt{\alpha(1-\alpha)}}$$

(4.21)

# 4.4.2. Determination of The Average Density Distribution of The Surface States.

The slope of the  $Q_{\tt SS}$  versus log(f) curve ,shown by Fig.4.4 and described by Eq.(4.20), is found to be:

$$\frac{dQ_{ss}}{d\log(f)} = \frac{2 \cdot q \cdot kT \cdot \overline{D_u}}{\log(e)} \cdot A_g \tag{4.22}$$

Equation (4.22) allows the determination of the average density of the surface states which is given by:

$$\overline{D_{ii}} = \frac{dQ_{ss}}{d\log(f)} \cdot \frac{\log(e)}{2 \cdot q \cdot kT \cdot A_g} \tag{4.23}$$

The value of the average density  $\overline{D_u}$  so obtained by Groeseneken et al comes out to be in the range of the known values of their experimental devices. However the values of

Fig.4.4 Qss verus frequency used to determine the capture cross section and the average density distribution of surface-states. (After [27]).

the capture cross sections as obtained previously by Nicollian [16],[22] are not in a good agreement compared to that obtained by the charge pumping method. This disagreement may be due to the fact that Groeseneken et al introduced the idea of the geometrical mean capture cross section of carriers, which necessitates the use of electrons as well as holes capture cross sections in the same material whereas commonly it is assumed that a p-type semiconductor is characterized by the hole capture cross section  $(\sigma_n)$  and an n-type by  $(\sigma_n)$ .

The charge pumping method, which has become a conventional technique for the study of interface properties in MOSFETs, has been extensively used and several modified versions have been developed by different workers [28-34].

# EXPERIMENT AL SET - UP AND DEVICES

The present study was commenced primarily with the same experimentation as used in the conventional charge pumping technique with the aim to verify the earlier results. During the above study, certain theoretical considerations and reasoning led to the development of a new technique and experimentation. However, the basic experimental set-up remains essentially the same as used in the charge pumping technique which is described in this chapter.

# 5.1. THE EXPERIMENTAL DEVICES.

The devices used in the experiments are two types: a) commercial devices and b) special devices in wafer-form fabricated for this project.

# 5.1.1. The Commercial Devices.

The commercial devices—used are the standard—MOS transistors having the reference—3N 170. They are manufactured by the National Semiconductor Company USA. The 3N 170 MOSFETs are four terminal devices having isolated drain, source, gate, and substrate. Among the device parameters, only the threshold voltage is known.

### 5.1.2. The Wafers.

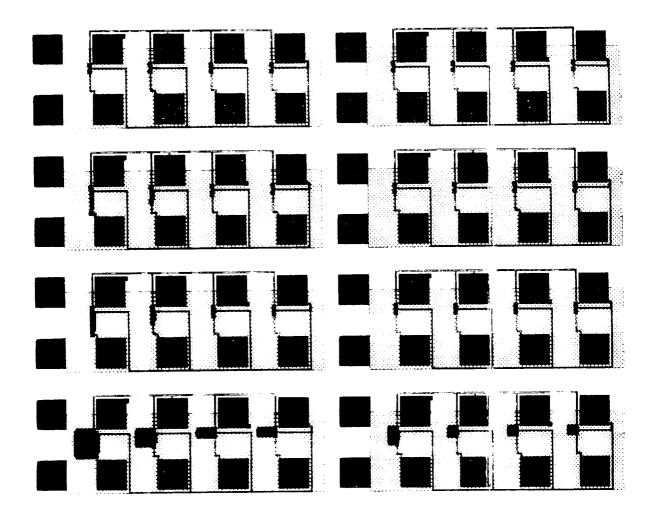

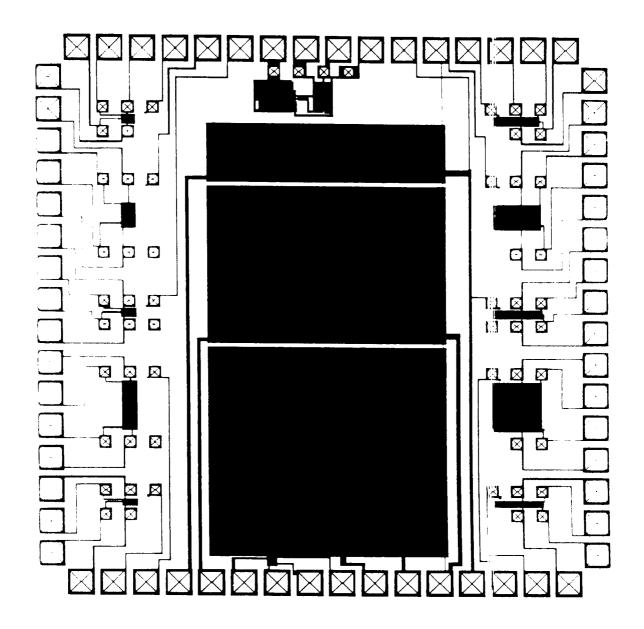

The devices in the form of wafers are manufactured by the ES2 (European Silicon Structures, France) laboratory via the CDTA (Centre de Developement des Technologies Avancees, Algerie) research center. Figures 5.1 and 5.2 show different sets of devices manufactured. The devices shown in Fig.5.1 are manufactured using the 1.2  $\mu m$  CMOS technology and those shown in Fig.5.2 are manufactured using the 2  $\mu m$  CMOS technology. The wafers consist of MOS transistors and MOS diodes of different dimensions. However, the value of the doping concentration and the oxide thickness is the same in all the

wafers. Figure 5.1 shows wafers consisting of sets of transistors having the source, the gate, and the substrate com-There are two series of transistors of the same dimensions, one series is an n-channel and the other is a p-channel transistors. Figure 5.2 shows wafers consisting of transistors that are five terminal devices, having isolated gate, substrate, drain, source, and well. Each terminal independently accessible. The transistors are n-channel. In addition, there are some capacitors that are build in the n-type substrate. Some of these wafers are encapsulated in a 64 PGA package to allow their use without the help of microscope-prober. The wafers of Fig. 5.1 are used in the first stage experiments meant for the observation of physical phenomena. Devices shown in Fig. 5.2 are used for experiments carried out to analyse the physical phenomena. These devices are fabricated according to the requirements of the present experiment. Table 5.1 gives the dimensions and data of these wafers.

#### 5.2. THE BASIC EQUIPMENTS.

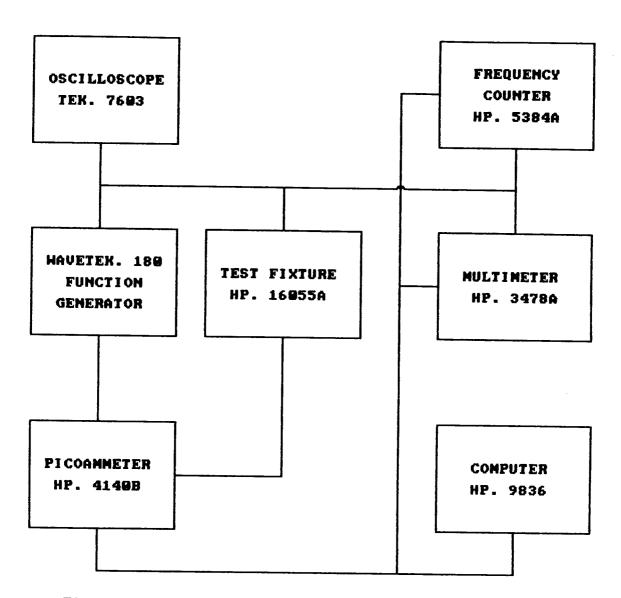

The capital equipment used in the present experiment includes the following:

#### 5.2.1. The Picoammeter.

The picoammeter that has been used is the HP 4140B,

Fig. 5.1a. General view of the 1.2 um process technology wafer.

(After ES2 Laboratory).

Fig. 5.1b. MOS transistors included in the 1.2 um process technology wafers.

(After ES2 Laboratory).

Fig. 5.2 Wafers manufactured using the 2um process technology.

(After ES2 Laboratory).

it has a sensitivity of 0.001 pA. It has been used in earlier experiments [43] where required information involve current value of the order of 0.025 pA.