# People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

**University M'Hamed BOUGARA – Boumerdes**

# Institute of Electrical and Electronic Engineering Department of Electronics

Thesis Presented in Partial Fulfilment of the Requirements of the Degree of

# Doctorate

In Electrical and Electronic Engineering

Entitled

# FPGA-Based Intelligent Dual-Axis Solar Tracking Control System

By

# **BENZEKRI** Azzouz

# Before the examining board composed of

| AKSAS Rabia         | Professor, ENP  | President  |

|---------------------|-----------------|------------|

| AZRAR Arab          | Professor, UMBB | Supervisor |

| LARBES Chérif       | Professor, ENP  | Examiner   |

| DAHIMENE Abdelhakim | MCA, UMBB       | Examiner   |

# Acknowledgments

I express my sincere gratitude to my supervisor **Professor** *Arab* **AZRAR** for allowing me to conduct this research under his auspices despite his busy agenda. I am especially grateful for his confidence, the freedom he gave me to do this work, his assistance, support and encouragements throughout the course of this work.

I am deeply grateful to **Professor** *Rabia*. **AKSAS** for agreeing to chair the jury. My warmest thanks go to **Professor** *Cherif*. **LARBES** and **Dr** *Abdelhakim* **DAHIMENE** for accepting to participate in the defense of this thesis.

I am grateful to Amira for her support and kindness.

## Abstract

This thesis describes the design process of an FPGA-based sensor-driven intelligent controller applied to a dual-axis sun tracking system. Fuzzy control based on fuzzy logic theory is used as a solution for the FPGA implementation of a digital controller for this industrial application. The real-time controller determines when and how much to tune the driving motors to minimize the misalignment of the solar panel surface with the sun's incident rays during the day in order to harvest maximum power from the solar panel mounted on a tracker.

To achieve such a digital controller, we developed an FPGA-based heterogeneous computing platform with the capability of partitioning the overall controller between two concurrent subsystems: (1) a hardware subsystem made up of a pair of fuzzy-like PD-type controllers implemented on the programmable fabric of the FPGA using the (Very-High Speed Integrated Circuit) Hardware Description Language (VHDL), and (2) a software subsystem, a soft processor Nios® II-based supervisory control system implemented using the system-on-a-programmable (SoPC) approach. This hardware/software codesign implemented in a single chip makes the connections between the two subsystems work with low power and low latency resulting in an optimal efficiency and performance. An experimental structure is constructed in the laboratory. The controller allows this structure to perform an approximate three-dimensional hemispheroidal rotation to track the sun's movement during the day to improve the overall efficiency of the solar panel.

Integrating the whole digital controller in a single chip accelerates development time while maintaining design flexibility. Moreover, it reduces the circuit board costs with a single-chip solution, and simplifies product testingcompared with traditional design approach using programmed logic (microprocessor- microcontroller- and DSP-based systems), the proposed solution uses a single low-cost FPGA device while enabling higher degrees of flexibility and concurrency.

The digital controller developed with Altera Quartus II 9.1 sp2 Web Edition software development suite tools is simulated and realized on a Cyclone-II EP2C35F672C6 FPGA platform to verify its feasibility and functionality.

Keywords: FPGA; SoPC; Fuzzy logic module; Nios® II; Sun tracker.

## ملخص المنشورة

تصف هذه المنشورة تصميم منهج على أساس استعمال المنطقة القابلة للبرمجة في الميدان (FPGA) لقيادة ذكية لكشاف في نظام ملاحقة ذو قطبين للشمس. إن المراقب الأني يحدد الوقت و بكم يضبط محرك القيادة لتقليص انحر اف اللوح الضوئي مع الأشعة الشمسية الواردة للاستخلاص الأعظم للطاقة. لإنجاز مثل هذا المراقب الرقمي، صممنا نظام غير متجانس مرتكز على المنطقة القابلة للبرمجة في الميدان (FPGA) مبني على نظامين غير متجانس مرتكز على المنطقة القابلة للبرمجة في الميدان (FPGA) مبني على نظامين غير متجانس مرتكز على المنطقة القابلة للبرمجة في الميدان (FPGA) مبني على نظامين فر عيين: (1) مشتق متناسب متحكم ضبابي أنجز على عناصر المنطقة القابلة للبرمجة في الميدان (PGA) مبني على نظامين فر عيين: (1) مشتق متناسب متحكم ضبابي أنجز على عناصر المنطقة القابلة للبرمجة في الميدان (Nios® II على المنطقة القابلة البرمجة في الميدان (Quartus II) باستعمال لغة استعمل نظام التطوير (II ouartus) من إنتاج شركة الميدان (Altera) الميدان (Altera) من إنتاج شركة الميدان (Altera) التعليق طريقة و مدة المراقبة، إن إدماج هذا المراقب يحاكي و ينجز على مالية المنطقة القابلة البرمجة في الميدان (Altera) باستعمال معالج « II هركة الميدان (Rego) من إنتاج شركة الميدان (Rego) من إنتاج المركان (2) جمع البيانات باستعمال معالج « II مركة الميدان (Rego) باستعمال لغة المراقب و (2) جمع البيانات باستعمال معالج « الا مركة الميدان (Rego) باستعمال لغة المركة الميدان (Rego) من إنتاج شركة بتطبيق طريقة (SoPC) باستعمال معالج أنجاز من و حد الوحدات، التكلية و مدة المراقبة، إن إدماج هذا المراقب يحاكي و ينجز على بطاقة المنطقة التنابة البرمجة في الميدان (Rego) من نوع ((Rego) من وع و زورد والد يعلى طركة و ماليانة المنطقة المنطقة المنطقة و مدة المراقبة، إن إدماج هذا المراقب يحاكي و ينجز على مالياته مركة و التكانية تشعلية المنطقة المنطقة المنطقة و مدة المرويز، مع تحسين الموثوقية. المراقب يحاكي و ينجز على بطاقة المنطقة القابلة للبرمجة في الميدان (Rego) من نوع ((Rego) لتعرفي و المنابة المراجبة و المراقبة، إن إدماج و المراقب يحاكي و ينجز على مامينا و المنطقة المابة البرمجة في الميدان (Rego) من وع ((Rego) لتعليم مروز من مركوم و المابة و المابع مي وع الموم الموم و و مدة المابية المابي مي مو و الموم و الموم و المابع

كلمات مفتاح: SoPC ، FPGA، متحكم ضبابي، II «Nios، ملاحق الشمس

iv

## Résumé

Cette thèse décrit le processus de conception d'un contrôleur intelligent à base de FPGA appliqué à un système de poursuite du soleil à double axe. Le contrôleur a base de logique floue détermine en temps réel quand et de combien faudrait-il ajuster les moteurs d'entraînement pour minimiser le désalignement de la surface du panneau solaire avec les rayons du soleil pendant la journée afin de récolter le maximum de puissance du panneau solaire monté sur un suiveur.

Pour atteindre un tel objectif de commande numérique, nous avons développé une plate-forme informatique hétérogène à base de FPGA avec la possibilité de cloisonner le contrôleur global entre deux sous-systèmes simultanés: (1) un sous-système de matériel informatique constitué d'une paire de logique floue comme régulateurs de type PD mis en œuvre sur FPGA en utilisant le langage VHDL, et (2) un système de contrôle de surveillance à base II processeur Nios® mis en œuvre en utilisant l'approche SoPC. Cette conception matériel / logiciel mise en œuvre dans une seule puce rend les connexions entre les deux sous-systèmes fonctionnent avec une faible puissance et de faible latence résultant en une efficacité et des performances optimales.

L'intégration du contrôleur numérique en une seule puce accélère le temps de développement tout en maintenant la flexibilité de conception. En outre, il réduit les coûts avec une solution mono-puce, et simplifie les tests de produits. Par rapport à l'approche traditionnelle de conception utilisant la logique programmée (microprocesseur et microcontrôleur et de DSP), la solution proposée utilise un dispositif de FPGA à faible coût unique tout en permettant des degrés de flexibilité et de concurrence plus élevés.

Le contrôleur numérique développé avec le logiciel de développement d'Altera le Quartus II Edition 9.1 sp2 est simulé et réalisé sur une plate-forme Cyclone II FPGA EP2C35F672C6 pour vérifier sa faisabilité et sa fonctionnalité.

Mots Clés: FPGA; SoPC; Logique Floue; Nios® II; Suiveur.

# **Graphical Abstract**

- A brand new methodology to implement intelligent embedded systems using SoPC approach

- Both simulation and physical implementation of the digital controller

- Implementation in the FPGA functions commonly realized by analog discrete components.

- Partitioning the digital controller between SoPC and non-SoPC simplifies design complexity while increasing design flexibility and reusability.

- The FLC module designed and implemented in VHDL is seamlessly integrated in the overall system using SoPC approach

- The target device on the DE2 board is the Altera EP2C35F672C6 FPGA of Cyclone II family

# **Table of Contents**

| Acknowledgement        | i  |

|------------------------|----|

| Abstract               | ii |

| Graphical Abstract     | v  |

| Table of Contents      | vi |

| List of Figures        | xi |

| List of Tablesx        | iv |

| List of Abbreviationsx | iv |

## Chapter 1 Introduction

| 1 | Introduction1      |                                               |    |

|---|--------------------|-----------------------------------------------|----|

| 2 | Renewable Energies |                                               | .2 |

|   | 2.1                | Hydro source of Energy                        | .2 |

|   | 2.2                | Wind Source of Energy                         | 3  |

|   | 2.3                | Biomass Source of Energy                      | 3  |

|   | 2.4                | Geothermal Source of Energy                   | 3  |

|   | 2.5                | Solar Energy                                  | 3  |

| 3 | Sun                | Tracker Types                                 | 5  |

| 4 | Sun                | Tracker Driving Modes                         | 5  |

| 5 | Com                | puting Platforms                              | 7  |

|   | 5.1                | ASIC Solution                                 | 7  |

|   | 5.2                | Software-Programmed Logic                     | 8  |

|   | 5.3                | Reconfigurable Logic or Programmable Hardware | 8  |

|                  | 5.4   | Implementation of Fuzzy Controllers9   |

|------------------|-------|----------------------------------------|

| 6                | Struc | cture of the Sun Tracking System10     |

| 7                | Obje  | ctives of the Thesis11                 |

| 8                | Orga  | nization of the Thesis13               |

| Chapter 2        |       | Literature Review                      |

| 1                | Intro | duction14                              |

| 2                | Oper  | a Loop Tracking Strategies15           |

| 3                | Close | ed Loop Tracking Strategies18          |

| 4                | FPG   | A Based Tracking Strategies            |

| 5                | Fuzz  | y Control Tracking Strategies24        |

| <u>Chapter 3</u> |       | Fuzzy Logic                            |

| 1                | Intro | duction26                              |

| 2                | Fuzz  | y Sets                                 |

|                  | 2.1   | Operations with Fuzzy Sets             |

|                  | 2.2   | Properties of Fuzzy Sets               |

| 3                | Mem   | bership Functions                      |

|                  | 3.1   | Piecewise Linear Membership Function   |

|                  |       | 3.1.1 Triangular Membership Function33 |

|                  |       | 3.1.2 Trapezoidal Membership Function  |

|                  | 3.2   | Features of the Membership Function    |

|                  |       | 3.2.1 Core                             |

|                  |       | 3.2.2 Support                          |

|                  |       | 3.2.3 Boundary                         |

|                  |       | 3.2.4 Height                           |

|                  | 3.3   | Structure of Membership Functions      |

|   | 3.4   | Number and Degree of Overlapping of Membership Functions36 |

|---|-------|------------------------------------------------------------|

|   | 3.5   | Linguistic Variables and Values                            |

| 4 | Fuzzy | IF-THEN Rules                                              |

| 5 | Prope | rties of Fuzzy Rules                                       |

|   | 5.1   | Completeness                                               |

|   | 5.2   | Consistency                                                |

|   | 5.3   | Continuity40                                               |

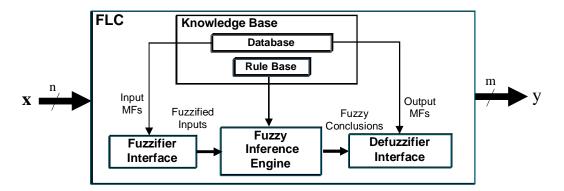

| 6 | Fuzzy | Logic Controller                                           |

|   | 6.1   | Fuzzification Interface                                    |

|   | 6.2   | Fuzzy Knowledge Base41                                     |

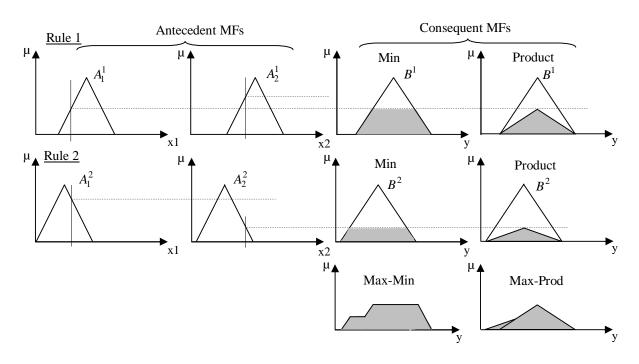

|   | 6.3   | Fuzzy Inference Mechanism42                                |

|   |       | 6.3.1 Fuzzy Implication42                                  |

|   |       | 6.3.2 Aggregation of Fuzzy Conclusions43                   |

|   | 6.4   | Defuzzification Interface45                                |

|   |       | 6.4.1 Maxima Methods46                                     |

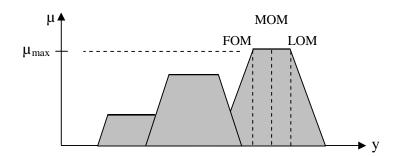

|   |       | 6.4.1.1 First of Maxima (FOM)46                            |

|   |       | 6.4.1.2 Last of Maxima (LOM)47                             |

|   |       | 6.4.1.3 Middle of Maxima (MOM)47                           |

|   |       | 6.4.2 Distribution Methods47                               |

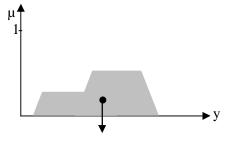

|   |       | 6.4.2.1 Max-Membership Method48                            |

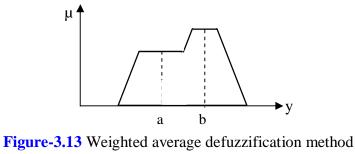

|   |       | 6.4.2.2 Weighted Average Method48                          |

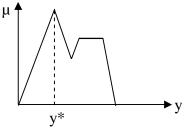

|   |       | 6.4.2.3 Center of Gravity (COG)49                          |

|   |       | 6.4.2.4 Center of Gravity for Singleton (COGS)49           |

## Chapter 4 FPGA Technology\_\_\_\_\_

| 1 | Intr                  | oduction                                        | 51 |

|---|-----------------------|-------------------------------------------------|----|

| 2 | Hist                  | ory and Evolution of Programmable Logic devices | 52 |

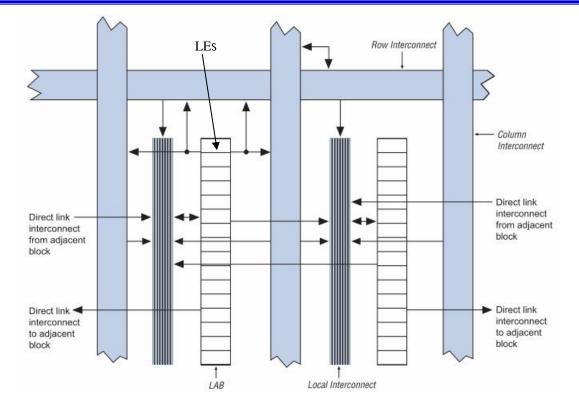

| 3 | Architecture of FPGAs |                                                 | 54 |

|   | 3.1                   | Logic Element                                   | 55 |

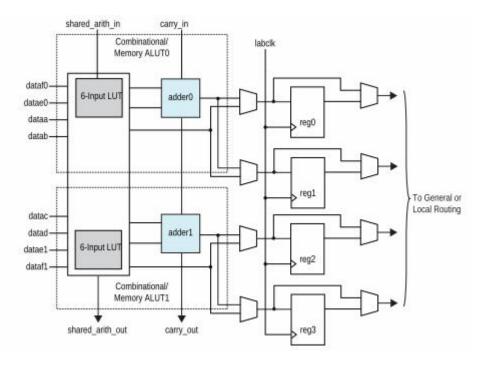

|   | 3.2                   | Logic Array Block                               | 55 |

|           | 3.3     | Adaptive Logic Module56                   |

|-----------|---------|-------------------------------------------|

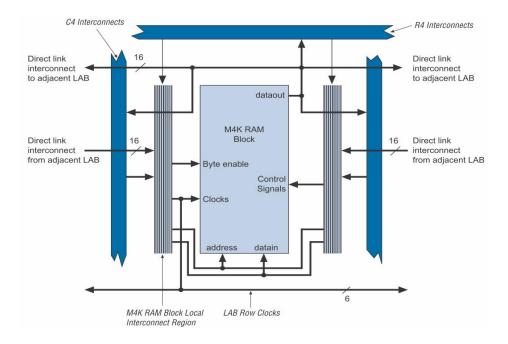

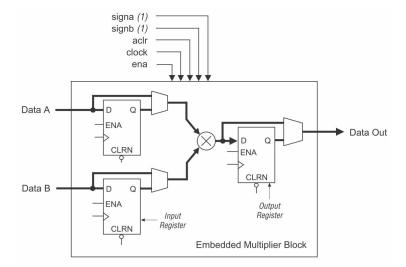

|           | 3.4     | Integrated Functional Blocks              |

|           |         | 3.4.1 Embedded RAM Blocks                 |

|           |         | 3.4.2 Embedded Multiplier Blocks          |

|           |         | 3.4.3 Gigabit Transceivers                |

|           |         | 3.4.4 Embedded Processor Cores            |

| 4 FPG     | A Pro   | gramming Technologies61                   |

|           | 4.1     | SRAM-Based FPGA61                         |

|           | 4.2     | Antifuse-Based FPGA                       |

|           | 4.3     | Flash-Based FPGA                          |

| 5 App     | licatio | ns of FPGAs62                             |

| 6 The     | Nios®   | II and SoPC Builder                       |

|           | 6.1     | The Nios® II Processor62                  |

|           | 6.2     | The SoPC Builder65                        |

|           |         |                                           |

| Chapter 5 |         | Design of the Fuzzy Logic Module          |

| 1         | Intro   | duction                                   |

| 2         | Struc   | ture of the Fuzzy Logic Module69          |

| 3         | Fuzzy   | y Logic Controller Design Flow69          |

| 4         | The A   | Azimuth Fuzzy Logic Controller71          |

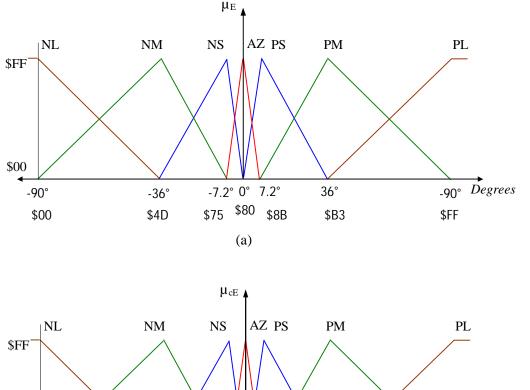

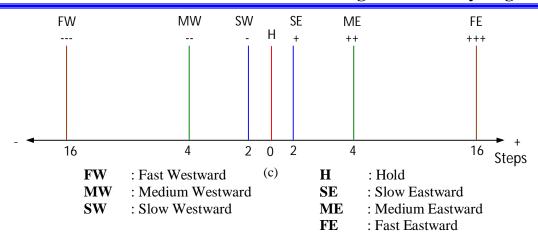

|           | 4.1     | Input/Output Membership Functions72       |

|           | 4.2     | Construction of Rule Base74               |

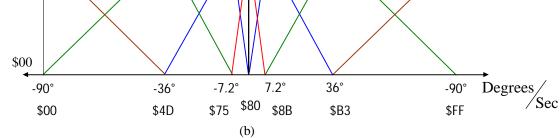

| 5         | The I   | Elevation Fuzzy Logic Controller77        |

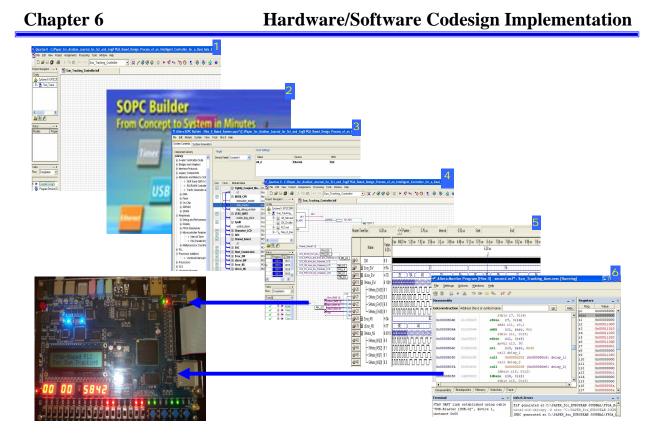

| Chapter 6 |         | Hardware/Software Codesign Implementation |

| 1         | T       | duction                                   |

| T |                                                             |

|---|-------------------------------------------------------------|

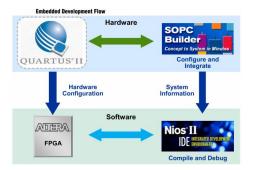

| 2 | FPGA Hardware Design Flow (SoPC Approach)80                 |

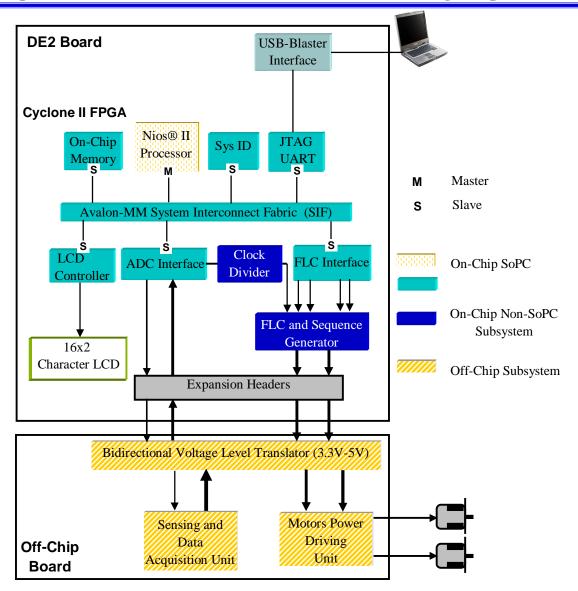

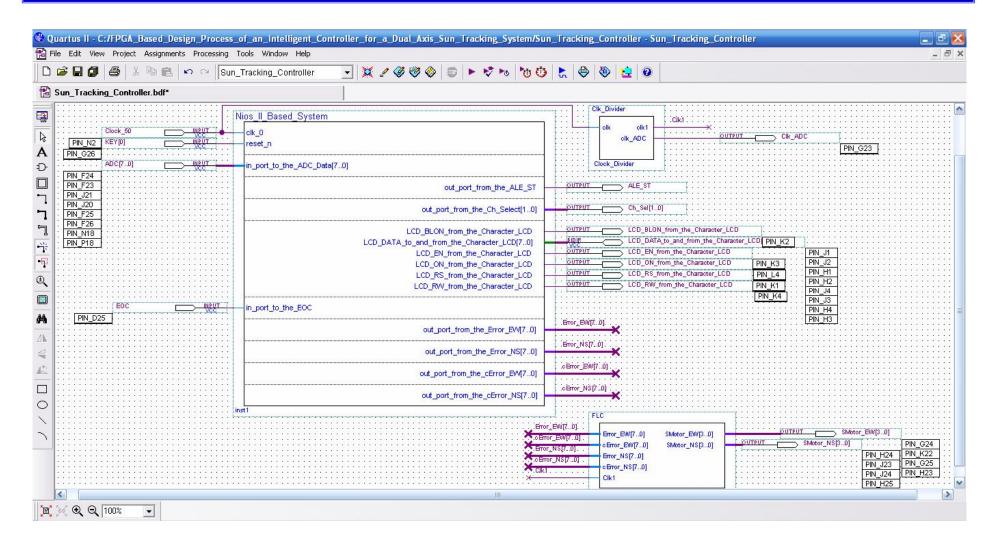

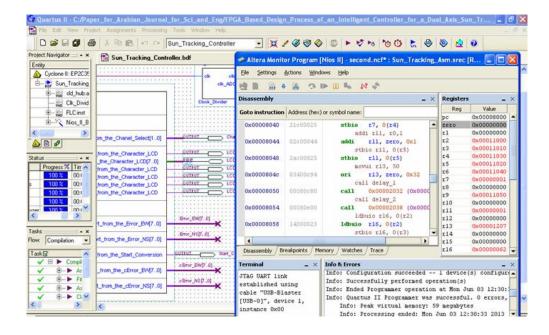

| 3 | Implementation of the Intelligent Sun Tracking Controller82 |

|                  | 3.1   | Off-Chip Hardware Module                               | 83  |

|------------------|-------|--------------------------------------------------------|-----|

|                  |       | 3.1.1 Sun Finder Unit                                  | 83  |

|                  |       | 3.1.2 Data Acquisition Unit                            | 85  |

|                  |       | 3.1.3 Bidirectional Voltage Level Translation Unit     |     |

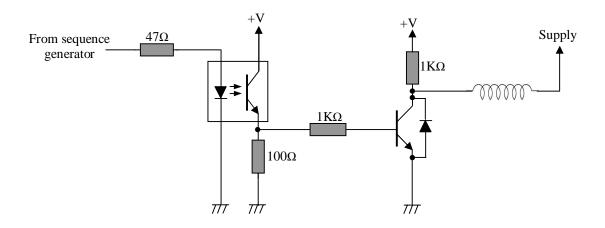

|                  |       | 3.1.4 Motors Driving Unit                              | 88  |

|                  | 3.2   | On-Chip Hardware Module                                | 91  |

|                  |       | 3.2.1 On-Chip non-SoPC Builder Subsystem               | 91  |

|                  |       | 3.2.1.1 The clock divider module                       | 91  |

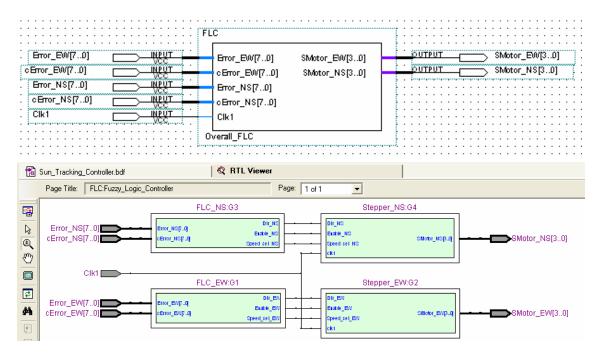

|                  |       | 3.2.1.2 Implementation of the Fuzzy Logic Module       | 92  |

|                  |       | 3.2.1.3 Stepper Motor Sequence Generator               | 93  |

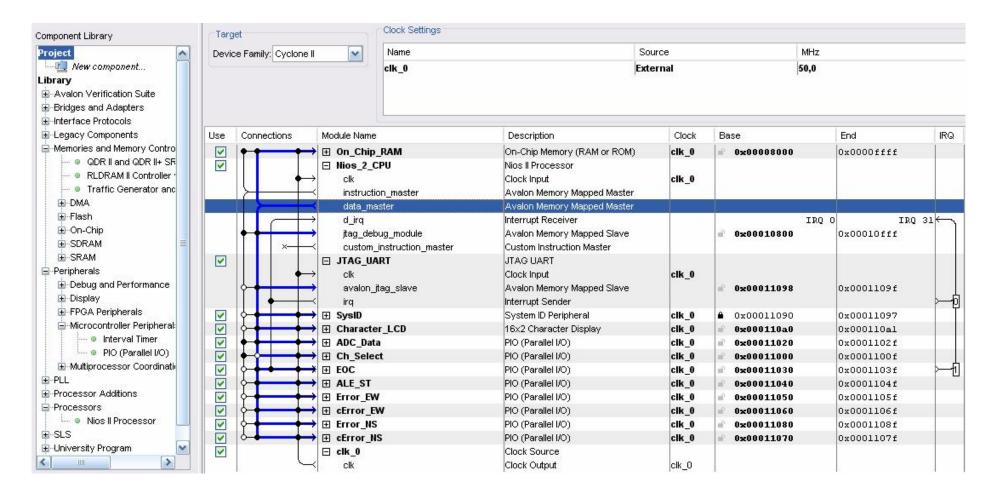

|                  |       | 3.2.2 On-chip SoPC Builder Subsystem                   | 95  |

|                  |       | 3.2.3 Building the Embedded System in the SoPC Builder | 96  |

|                  |       | 3.2.4 Integrating the SoPC and non-SoPC Builder        |     |

|                  |       | Subsystems in Quartus II Project                       | 99  |

|                  |       | 3.2.5 Firmware Development                             | 101 |

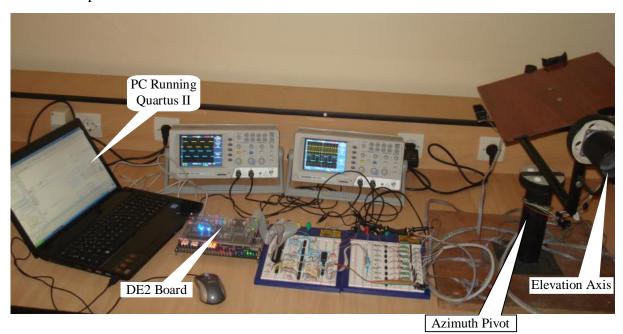

| 4                | Real- | Time Experiment                                        | 102 |

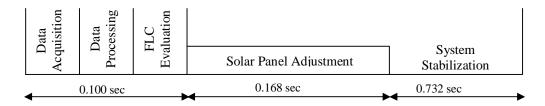

|                  | 4.1   | Operational Cycle Time                                 | 103 |

|                  | 4.2   | Simulation                                             | 104 |

| <u>Chapter 7</u> |       | Conclusions                                            | 106 |

| References       |       |                                                        | 109 |

# **List of Figures**

| Figure-1.1 | (left) A dam to energize a hydroelectric power station. (right) Airflows       |

|------------|--------------------------------------------------------------------------------|

|            | used to run wind turbines2                                                     |

| Figure-1.2 | Wood chip bio fuel a renewable alternative source of energy                    |

| Figure-1.3 | (a) Multi-crystalline-based solar panel. (b) Single crystal-based solar panel. |

|            | (c) Amorphous-based solar panel4                                               |

| Figure 1.4 | Structure of a dual-axis sun tracker                                           |

| Figure-1.5 | High-level representation of the FPGA-based intelligent dual-axis sun          |

|            | tracking system10                                                              |

| Figure-1.6 | Pictorial representation of the FPGA-based intelligent dual-axis sun           |

|            | Tracking system                                                                |

| Figure-3.1 | Membership function for crisp and fuzzy sets                                   |

| Figure-3.2 | Graphical representation of complement, union and intersection                 |

|            | of fuzzy operations                                                            |

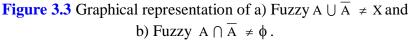

| Figure-3.3 | Graphical representation of fuzzy union and intersection                       |

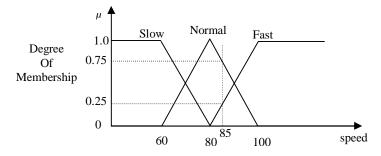

| Figure-3.4 | Fuzzy membership function for speed32                                          |

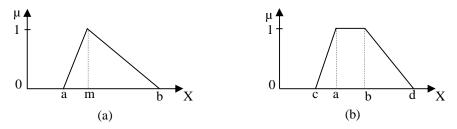

| Figure-3.5 | Asymmetric triangular and trapezoidal membership functions                     |

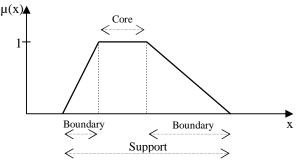

| Figure-3.6 | Features of a membership function                                              |

| Figure-3.7 | Graphical representation of a fuzzy variable with 5 fuzzy sets                 |

| Figure-3.8 | Structure of a generic Mamdani type Fuzzy Logic Controller41                   |

| Figure-3.9 | Graphical representation of Max-Min and Max-Prod inference                     |

|             | methods with crisp inputs with two inputs and two rules                 |

|-------------|-------------------------------------------------------------------------|

| Figure-3.10 | Example of defuzzification for two-rule fuzzy inference45               |

| Figure-3.11 | First, Last and Middle of maxima defuzzification methods47              |

| Figure-3.12 | Max-membership defuzzification method48                                 |

| Figure-3.13 | Weighted average defuzzification method48                               |

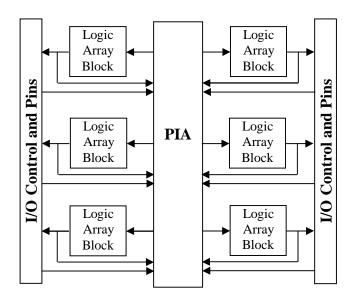

| Figure-4.1  | Generic structure of a CPLD                                             |

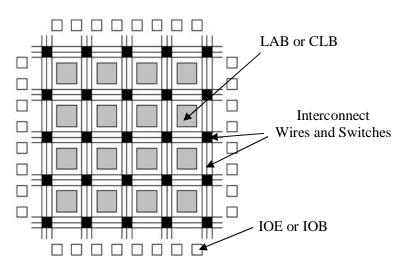

| Figure-4.2  | Generic structure of an early FPGA54                                    |

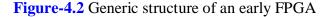

| Figure-4.3  | Block diagram of the Altera logic element55                             |

| Figure-4.4  | Block diagram of a Cyclone II LAB [78]56                                |

| Figure-4.5  | High-level block diagram of the Altera Stratix-V ALM [79]57             |

| Figure-4.6  | An M4K RAM embedded memory block in a Cyclone FPGA [78]58               |

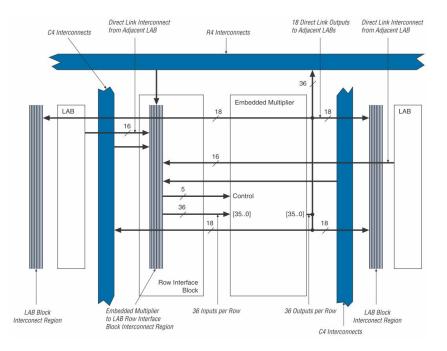

| Figure-4.7  | Architecture of an embedded multiplier block in a Cyclone FPGA [78]59   |

| Figure-4.8  | Architecture of an embedded multiplier block in a Cyclone FPGA [78]59   |

| Figure-4.9  | The 3 flavors of the Nios® II soft core processor [79]63                |

| Figure-4.10 | Screenshot of a SoPC Builder system                                     |

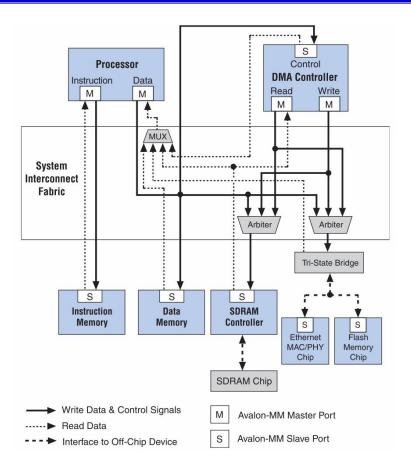

| Figure-4.11 | System interconnect fabric with multiple mastering components [85]67    |

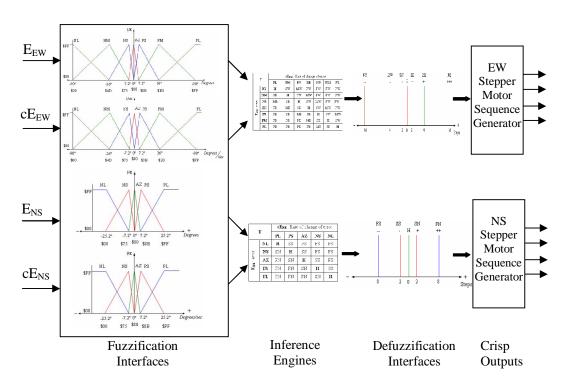

| Figure 5.1  | Operational block diagram of the intelligent dual-axis sun tracking     |

|             | fuzzy logic module69                                                    |

| Figure-5.2  | Sun tracking fuzzy logic module with errors and rate of change of error |

|             | Generator70                                                             |

| Figure-5.3  | Incident angle of sunrays with solar panel surface71                    |

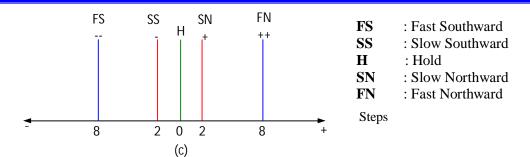

| Figure-5.4  | (a) MFs of the angular error $E_{EW}$ in degrees. (b) MFs of $cE_{EW}$  |

|             | in degrees/sec (c) Singleton membership functions of the output         |

|             | variable 'U' in number of steps73                                       |

| Figure-5.5  | (a) MFs of the angular error $E_{NS}$ in degrees. (b) MFs of $cE_{NS}$  |

|             | in degrees/sec (c) Singleton membership functions of the output         |

|             | variable 'U' in number of steps78                                     |

|-------------|-----------------------------------------------------------------------|

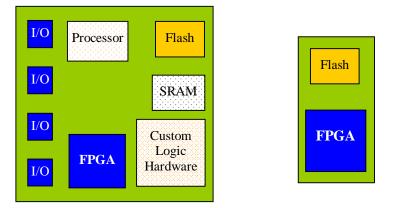

| Figure-6.1  | A Typical microprocessor-based system, (left) traditional method      |

|             | (right) SoPC approach                                                 |

| Figure-6.2  | FPGA-Based Hardware/Software Design Flow using SoPC Approach81        |

| Figure-6.3  | The overall fuzzy control based dual-axis sun tracking system         |

|             | block diagram implemented in the Cyclone II FPGA83                    |

| Figure-6.4  | The Off-Chip hardware functional block diagram                        |

| Figure-6.5  | Circuit diagram of the sensing and data acquisition unit              |

| Figure-6.6  | Flow chart for the data acquisition subroutine                        |

| Figure-6.7  | The motor driver power stage unit to energize the two actuators       |

| Figure-6.7b | One branch (out of 8) of the driver power stage unit90                |

| Figure-6.8  | The On-Chip hardware module91                                         |

| Figure-6.9  | VHDL code of the clock divider custom hardware module92               |

| Figure-6.10 | Detailed view of the FL module in Quartus II and the RTL Viewer       |

| Figure-6.11 | Unipolar stepper motor windings and full-step sequence                |

| Figure-6.12 | VHDL code for a stepper motor full-step sequence generator94          |

| Figure-6.13 | SoPC-based intelligent sun tracking controller optimized in an FPGA97 |

| Figure-6.14 | Top-Level schematic for the FPGA-Based FLC design process for a       |

|             | dual-axis sun tracking system100                                      |

| Figure-6.15 | PC running Quartus II and Altera Monitor Program software101          |

| Figure-6.16 | Hardware setup of the FPGA Based intelligent dual-axis                |

|             | sun tracking systems102                                               |

| Figure-6.17 | The operational cycle time104                                         |

| Figure-6.18 | Behavioral simulation window in the Quartus II simulator105           |

# **List of Tables**

| Table 3.1 | The NxM set of fuzzy if-then rules in matrix form             | ;9 |

|-----------|---------------------------------------------------------------|----|

| Table-5.1 | The 7x7 fuzzy rule-base matrix used in the fuzzy-like PD-type |    |

|           | FLC for the vertical pivot shaft (east-West)7                 | '4 |

| Table-5.2 | The 5x5 fuzzy rule-base matrix used in the fuzzy-like PD-type |    |

|           | FLC for the horizontal pivot shaft (North-South)              | '8 |

# **List of Abbreviations**

| ADC    | Analog to Digital Converter                              |

|--------|----------------------------------------------------------|

| ALE    | Address Latch Enable                                     |

| ALM    | Adaptive Logic Module                                    |

| AMP    | Altera Monitor Program                                   |

| ARM    | Advanced RISC (Reduced Instruction Set Computer) Machine |

| ASIC   | Application Specific Integrated Circuit                  |

| ASSP   | Application Specific Standard Product                    |

| CLB    | Configurable Logic Block                                 |

| CMOS   | Complementary Metal Oxide Semiconductor                  |

| COG    | Center of Gravity                                        |

| COGS   | Center of Gravity for Singleton                          |

| CPLD   | Complex Programmable Logic Device                        |

| DCT    | Discrete Cosine Transform                                |

| DMIPS  | Dhrystone Million Instructions Per Second                |

| DOM    | Degree of Membership                                     |

| DSC    | Digital Signal Controller                                |

| DSP    | Digital Signal Processor                                 |

| EOC    | End of Conversion                                        |

| EEPROM | Electrically Erasable Programmable Read Only Memory      |

| EPROM  | Erasable Programmable Read Only Memory                   |

| FFT    | Fast Fourier Transform                                   |

| FIFO   | First IN First OUT                                       |

| FIR    | Finite Impulse Response                                  |

| FLC    | Fuzzy Logic Controller                                   |

| FOM    | First Of Maximum                                         |

| FPD    | Field Programmable Device                                |

| FPGA   | Field Programmable Gate Array                            |

| GPIO   | General Purpose Input/Output                             |

| GUI    | Graphical User Interface                                 |

| HDL    | Hardware Description Language                            |

| HPS    | Hard Processor System                                    |

| IBM    | International Business Machine                           |

| IC     | Integrated Circuit                                       |

| IOB    | Input Output Block                                       |

| IOE    | Input Output Element                                     |

| IP     | Intellectual Property                                    |

| JTAG   | Joint Test Action Group                                  |

| LAB    | Logic Array Block                                        |

| LCD    | Liquid Crystal Display                                   |

|        |                                                          |

| LDR      | Light Dependent Resistor                                           |

|----------|--------------------------------------------------------------------|

| LE       | Logic Element                                                      |

| LOM      | Last of Maxima                                                     |

| LUT      | Look Up Table                                                      |

| MCU      | Micro Controlling Unit                                             |

| MF       | Membership Function                                                |

| MIPS-ISA | Microprocessor without Interlocking Pipe Stages – Instruction Set  |

|          | Architecture                                                       |

| MMI      | Monolithic Memories Inc                                            |

| MMU      | Memory Management Unit                                             |

| MOM      | Middle of Maxima                                                   |

| MSI      | Medium Scale Integration                                           |

| NIOS     | Netware Input-Output Subsystem                                     |

| OTP      | One-Time Programmable                                              |

| PAL      | Programmable Array Logic                                           |

| PC       | Personal Computer                                                  |

| PCB      | Printed Circuit Board                                              |

| PD       | Proportional Derivative                                            |

| PI       | Proportional Integral                                              |

| PIA      | Programmable Interconnect Array                                    |

| PID      | Proportional Integral Derivative                                   |

| PLA      | Programmable Logic Array                                           |

| PLD      | Programmable Logic Device                                          |

| PROM     | Programmable Read Only Memory                                      |

| RAM      | Random Access Memory                                               |

| RISC     | Reduced Instruction Set Computer                                   |

| ROM      | Read Only Memory                                                   |

| RTL      | Register Transfer Logic                                            |

| SDRAM    | Synchronous Dynamic Random Access Memory                           |

| SoC      | System on Chip                                                     |

| SoPC     | System on Programmable Chip                                        |

| SPI      | Serial Peripheral Interface                                        |

| SPLD     | Simple Programmable Logic Device                                   |

| SRAM     | Static Random Access Memory                                        |

| SSI      | Small Scale Integration                                            |

| TTL      | Transistor Transistor Logic                                        |

| UART     | Universal Asynchronous Receiver Transmitter                        |

| USB      | Universal Serial Bus                                               |

| VHDL     | (Very High Speed Integrated Circuit) Hardware Description Language |

Chapter 1

# Introduction

#### 1 Introduction

Since the beginning of the Industrial Revolution, coal, crude oil and natural gas are the three forms of fossil fuels mostly used worldwide. These non-renewable sources of energy are so called because they have been formed from the organic remains of prehistoric plants (plants which grew on earth millions of years ago) and animals and have rotted away over million of years and became solids, liquids and gasses. They will run out one day. Fossil fuels must be located, excavated and transported before they can be used. These carbon-based fuels are employed to feed power plants to produce electrical energy [1]. They must be burned to produce electricity. Burning them creates unwanted by-products such carbon dioxide. These unwanted by-products pollute the environment (air and water pollutions) and contributes to the global warming due to the release of huge amount of greenhouse gasses into the atmosphere. To minimize this major problem, there is a need to replace (at least partially) these fossil fuels with an environment friendly alternative. For a long time, it has been thought that the nuclear-based power plants would be the ideal solution for the increased demand for electrical energy, ever increasing oil price and environmental concern. It is true that nuclear energy has several benefits: absence of airborne pollutants, no greenhouse effect and reduction in dependence on oil. However, the accidents of Three Mile Island (1979), Tchernobyl (1986) and the recent tragedy of Fuckushima (2011) increased anti-nuclear sentiment. This public awareness pushed several countries to rethink the use of this energy. Germany decided to close all of its reactors by 2022, while Italy and others countries halted expanding their nuclear power plants.

### 2 Renewable Energies

In the 1970s with the energy crisis, the interest in green power was primarily driven by the goal of replacing fossil fuels to reduce the dependence on oil and gas. Nowadays, with climate change, ozone layer depletion, global warming etc, the principle goal is the preservation of the environment by minimizing carbon-dioxide emissions in the atmosphere. There is a wide variety of renewable energies. These energies use resources that are naturally replenished on a human timescale and will exist infinitely. The list of these resources, ordered by the amount of contribution to the production of electricity, currently includes: hydro, wind, biomass, geothermal heat and sunlight. Electricity derived from these energies is considered "green" because of the negligible negative impacts on the environment.

#### 2.1 Hydro source of Energy

The contribution from renewable energy sources for electricity production is small with the exception of hydro. Over the last 100 years, hydro has been the most mature renewable source of electricity around the world. **Figure-1.1** (left) depicts a huge energy stored in a dam which can be used to generate hydroelectric power. Today, hydro power contributes to about 21% of electricity capacity worldwide [2].

Figure-1.1. (left) A dam to energize a hydroelectric power station. (right) Airflows used to run wind turbines.

### Chapter One

#### 2.2 Wind Source of Energy

Wind is the next most popular source of green electricity and the fastest growing renewable energy world-wide. Figure-1.1(right) illustrates airflows used to run wind turbines. An average of wind speed of 14 miles/hour ( $\approx 20$  Km/hour) is needed to efficiently convert wind energy into electricity. Today, large new wind farms at excellent wind sites generate electricity at a cost in the range that is competitive with that of electricity from conventional power plants, while offshore areas experience average wind speeds larger than that of land.

#### 2.3 Biomass Source of Energy

Wood remains the largest biomass energy source today. Grasses, agricultural crops, or other biological materials can be converted to heat, then steam, and then electricity. Biomass power is the third largest source of renewable electricity. **Figure-1.2** shows biological material derived from living, or recently living organisms used to feed a power plant to produce electricity.

Figure-1.2 Wood chip bio fuel a renewable alternative source of energy

#### 2.4 Geothermal Source of Energy

Heat contained in the core of the earth can be exploited to produce electricity through steam. The geothermal source while this is an abundant source with today's technology only a small fraction can be converted commercially to electricity. Geothermal power plants are highly capital intensive because enough steam-supply wells have to be drilled up-front to provide the full plant capacity at startup.

#### 2.5 Solar Energy

Among all renewable energy sources available, solar energy is believed to be the most promising source. It is free, secure, pollution-free, available all over the world, and will last forever [3, 4].

The sun creates its energy through a thermonuclear process that converts about 650,000,000 tons of hydrogen to helium every second [5]. The process creates heat and electromagnetic radiation. The heat remains in the sun and is instrumental in maintaining the thermonuclear reaction. The electromagnetic radiation (including visible light, infra-red light, and ultra-violet radiation) streams out into space in all directions. Only a very small fraction of the total radiation produced reaches the Earth [6]. One of many ways of generating electricity from solar energy is the use of solar panels which covert sunlight into direct electricity (DC) using the photovoltaic effect. Solar panels are formed out of interconnected photovoltaic cells that are arranged in series/parallel fashion.

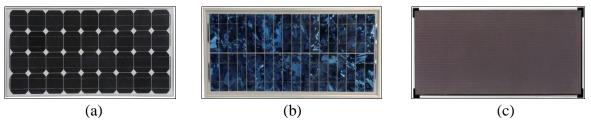

A Photovoltaic Cell (PV) or solar cell is a semi-conductor device used to convert lights directly into electricity by the photovoltaic effect. The efficiency and the cost of the photovoltaic cells depend greatly on the material chosen. Present PV cells come into three major categories: Multi-crystalline, Single crystal, and Amorphous, Figure-1.3.

Figure-1.3 (a) Multi-crystalline-based solar panel. (b) Single crystal-based solar panel. (c) Amorphous-based solar panel

There are several factors that affect the efficiency (percentage of sun's energy striking the PV cell that is converted into electricity) of the solar panel. The two major ones are: (1) the PV cell efficiency and, (2) the intensity of sun rays received on the surface of the solar panel.

Although there is a continuous improvement in the PV materials to enhance PV cell efficiency, current technology delivers PV cells with an efficiency level ranging from 10 to

20% (some laboratories reached efficiencies of more than 30% but not yet available commercially). Therefore, to lower the per KWh cost, we need to rely on the dimensions of the panels and/or the irradiation intensity. Increasing the surface area of the solar panels is not a viable solution. It increases investments cost and requires more ground surface. A more feasible and economical solution however, is to maximize power extraction from the panel by operating the cell arrays at their full potential. This can be achieved by continuously exposing the surface of the panel perpendicular to the sun's rays. This strategy can be accomplished by a sun tracker, a device onto which a solar panel is fitted to track the movement of the sun across the sky (mimicking sunflower).

### **3** Sun Tracker Types

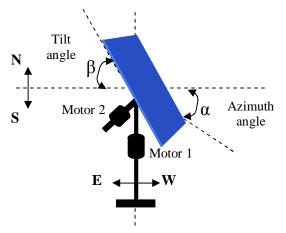

The efficiency of a photovoltaic panel depends on the incident angle of the sun rays with respect to the surface of the panel. For the solar panel to harvest maximum energy from the sun, a high-precision sun tracking system is necessary to track the sun in the sky from early morning until late in the afternoon. A sun tracking system is a mechatronic system. It consists of the mechanics, electric drives and information technology [7]. The mechanics consists mainly of a tracker onto which a solar panel is fitted to track the movement of the sun by maintaining the panel surface perpendicular to the sun incident radiations (mimicking sunflower). The mechanics provide the necessary torque to change the azimuth and elevation positions of the solar panel with respect to the sun, while the controller determines when and how much to tune the driving motors to minimize the misalignment of the solar panel surface with the sun's incident rays.

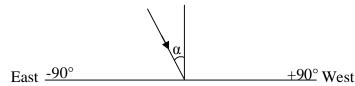

Sun trackers are classified according to the number and orientation of their axes. They are grouped into single- and dual-axis tracking devices. Single-axis trackers have one degree of freedom. They are used to vary the azimuth angle in order to follow the movement of the sun East-West during the day with fixed tilt angle. These types of trackers are more suitable in tropical regions. Dual-axis trackers accommodate two degrees of freedom, azimuth and tilt. Their axles are typically normal to one another. They have the capability to tune the solar panel east-west and north-south and follow the sun's apparent motion anywhere in the sky. **Figure 1.4** illustrates the structure of a dual-axis sun tracker. Angle  $\alpha$  is an azimuth angle of the solar panel and  $\beta$  is a tilt angle.

Motor 1 changes the azimuth angle along the east-west direction, whereas motor 2 changes the elevation angle along the north-south direction.

Figure 1.4 Structure of a dual-axis sun tracker

#### 4 Sun Tracker Driving Modes

There are three methods of tracking: passive, chronological and active. Passive trackers use a low boiling point compressed fluid (often Freon) as a means of tilting the solar panel. When heated by the solar heat, it creates a gas pressure in the system, the fluid pressure increases causing the liquid to move inside the tracker from one side to another allowing gravity to rotate the tracker to follow the sun. These trackers do not use motors or control and hence do not consume any energy. They are also less precise and therefore, operate with low efficiency compared to active trackers. Passive trackers are however, unpractical in cold locations. Chronological trackers employ electronic logic to control the actuators to follow the sun based on mathematical formulae based on astronomical references with the data of a whole one-year sun trajectory to calculate the sun movement in the sky. This data is usually the current time, day, month and year of a specific geographical location. These trackers are also known as open-loop trackers as they do not require any feedback for the controlled system. Active trackers also known as closed-loop dynamic trackers on the other hand employ motors and gear trains to direct the PV panel as commanded by the controller. They commonly use light detecting sensors to provide raw data as inputs to the controller to track in real-time the real position of the sun in the sky. They are more reliable than open loop trackers. The use of the feedback makes their system response less sensitive to external disturbances [8], [9].

### **5** Computing Platforms

At the heart of most embedded control systems is usually a real-time digital controlling unit. Nowadays, designers are blessed by the variety of computing platforms they have at their disposal to address these controlling units. These latter can be implemented using one or a combination of design methodologies [10-11]. There are three major methodologies, namely:

- Dedicated (fixed) digital logic or application-specific integrated circuits or ASICs,

- (ii) Software-programmed logic platforms, and

- (iii) Hardware reconfigurable logic platforms.

#### 5.1 The ASIC Solution

There is no doubt, of all solutions; dedicated controllers or ASICs provide highest performance as they are optimally tailored for particular use. They are great at speed and power consumption. Moreover, they have reduced size and cost at high volume. They exhibit high reliability of system operation. ASICs present some disadvantages. They are fixed function integrated circuits, that is, the design is frozen in silicon with no possibility to make any change.

#### 5.2 Software-Programmed Logic

For years, digital designers largely relied on general-purpose microprocessors microcontrollers, personal computers (PCs), digital signal processors (DSPs) and digital signal controllers (DSCs) for the design of digital embedded systems. Despite the large number of commercially available off-the-shelf products, designers of embedded systems are often challenged to find the exact processor and the appropriate peripherals that will fit their needs [12]. Often, designers must make compromises between performance, chip count, flexibility, cost and power consumption in their choices.

Although flexible and able to implement complex algorithms, processor-based solution presents some disadvantages. Off-the-shelf processors and peripheral devices have fixed hardware, leaving software as the unique alternative to the designer to develop/enhance his/her desired application. Moreover, the sequential nature of program execution with these processors leads to several orders of magnitude inferior to ASICs in terms of performance, silicon area usage and power consumption [10], [13].

#### 5.3 Reconfigurable Logic or Programmable Hardware

In the above modalities, the hardware architecture is settled in the early stage of the design cycle making even minor changes affect dramatically the ASIC design, processor selection and printed-circuit board (PCB) design. An elegant and cost effective solution is obtained when using the reconfigurability of the FPGA. In such computing platform, the system hardware needs no longer to be frozen. The processor and peripheral devices as well as the target FPGA can all be changed during development time, or migrated to new more performant FPGA.

With today's high density FPGAs, the emerging and revolutionary SoPC design methodology provides a new paradigm in the design of embedded systems. This methodology

allows the integration of embedded processor(s) (hard-core and/or soft-core) with or without user defined hardware accelerator blocks tailored to fit the desired application. The heterogeneity of this approach allows the co-existence of the embedded microprocessor with the FPGA logic in the same chip, taking the benefit of both the microprocessor and the ASIC. Partitioning the controller into two main blocks makes the design process easier while achieving better performance by avoiding the processor to get bogged down. The embedded microprocessor will be used to implement non-timing critical functions, while timing critical are best implemented as hardware accelerators in the FPGA fabric. To cope and design efficient complex systems with this new paradigm, Altera for example provides sophisticated and powerful electronic design automation (EDA) tools; Quartus II and the SoPC builder.

#### 5.4 Implementation of Fuzzy Controllers

Fuzzy systems implementation has been exploited since the mid-1980s and different architectures were devised. Naturally, the realization of these controllers will always be digital because its algorithm is primarily based on rule inference using the "IF-THEN" statements [14]. An efficient and effective implementation should satisfy two main requirements: flexibility and performance. There exist two main branches of fuzzy systems implementations: software and hardware implementations. A third branch can be a combination of the first two.

Early fuzzy systems were mostly implemented in software by means of generalpurpose microprocessors, and microcontrollers. These implementations are flexible, require the least hardware resources and can be developed rapidly. However, the sequential nature of execution of these processors may not permit real-time processing.

Fuzzy systems hardware implementations can be realized as a dedicated hardware, as an ASICs or on a reconfigurable FPGAs. Hardware implementations use a certain level of parallelism and pipelining leading to a very high increase in processing speed. Nowadays, with ceaseless increasing density of FPGAs and the SoPC approach, it is possible to takes advantage of both the flexibility of software and the performance of hardware [15].

Several survey and review papers were published to highlight fuzzy systems implementations. In [16], the authors reviewed many interesting fuzzy hardware/software architectures from a categorical and historical point of view. Recently, in [17], Bosque et al surveyed fuzzy systems and neural networks with a particular focus on hardware taxonomy and highlighted the characteristics of the different applications covering the paradigms done over the last two decades.

### 6 Structure of the Sun Tracking System

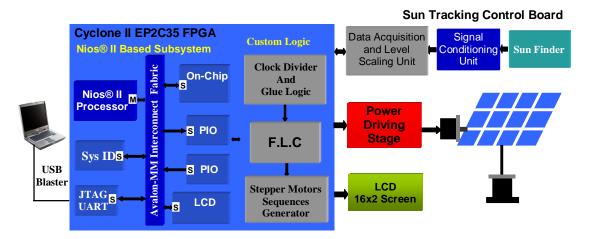

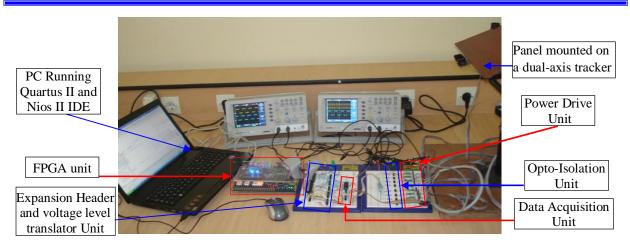

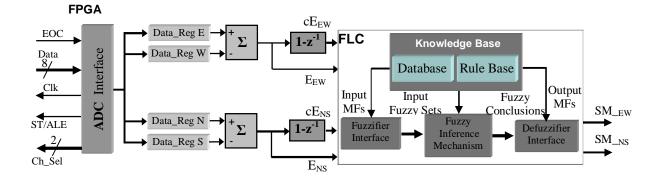

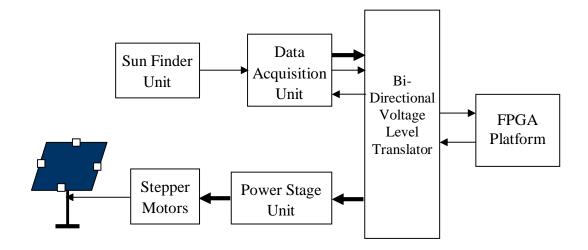

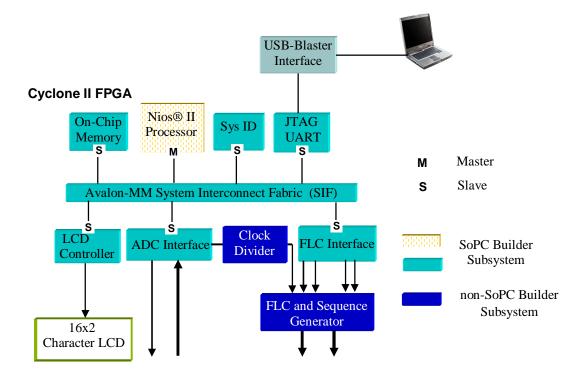

**Figure-1.5** depicts the hardware structure of the FPGA-based intelligent sun tracking system. The proposed architecture consists of several units linked together to form an integrated autonomous programmable system. These units are partitioned into two major modules:

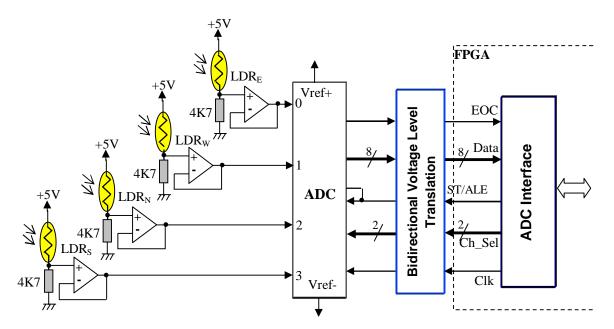

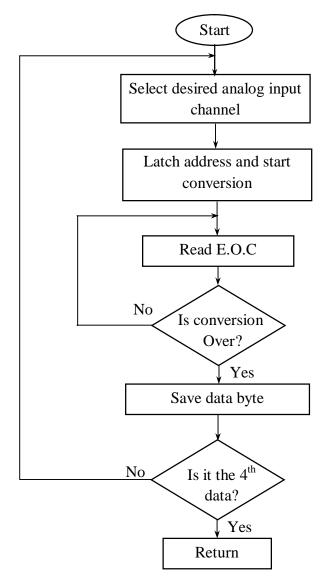

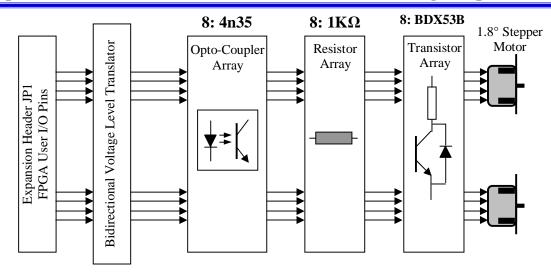

(i) The off-chip or on board module, realized on breadboards, is implemented with offthe-shelf discrete components. It is composed of a panel equipped with a sun finder, used to determine the position of the sun in the sky, mounted on an azimuth-elevation dual-axis tracker, a signal conditioning circuit, a data acquisition unit built around an analog-to-digital converter (ADC), a bidirectional voltage level translator (3.3V-5V) and two unipolar 4-phases

Figure-1.5 High-level representation of the FPGA-based intelligent dual-axis sun tracking system

1.8° per step bidirectional stepper motors with their power driving circuits.

(ii) The on-chip module which is the digital controller is implemented onto the FPGA chip of the low-cost DE2 board. The digital controller consists of two subsystems: a System-on-a-Programmable-Chip or SoPC based subsystem built around the Altera Nios® II embedded soft core processor and a custom non-SoPC subsystem. The SoPC Builder subsystem includes several functional blocks such as the ADC interface, the liquid crystal display or LCD controller, and an interface with the custom logic. It controls and gathers data from the data acquisition unit by scheduling and generating the necessary signals to the analog-to-digital converter, it performs the necessary data processing, monitoring and control of the external actuators. The non-SoPC Builder subsystem consists of several custom hardware components developed in VHDL that operates in conjunction with the processor-based system. The core system of which is the fuzzy-like PD-type FLC and the stepper motors sequence generator.

### 7 Objectives of the Thesis

This thesis addresses the design process of a FPGA-based fuzzy logic controller (FLC) applied to a sensors-driven dual-axis sun tracking system. The digital controller is implemented using the SoPC approach. This methodology combines a soft processor core the Nios® II, on-chip memory, intellectual property (IP) peripheral components and a user defined hardware accelerator components integrated into a single FPGA device, **Figure-1.6**.

The approach combines the features of software programming and reconfigurable hardware implementations into two inter-related modules: (i) a Nios® II embedded processorbased subsystem which constitutes the upper layer of the digital controller and (ii) a PD-like fuzzy logic module to steer the tracker actuators.

The first subsystem provides an ideal platform for microcontroller applications. Its mission is to keep track of the data gathered from the sun finder unit by scheduling and initiating the signals required by the data acquisition unit. It computes the angular errors and

## **Chapter One**

## Introduction

Figure-1.6. Pictorial representation of the FPGA-based intelligent Dual-axis sun tracking system

the rates of change of these errors and applies them as crisp inputs to the PD-like fuzzy logic module. In addition, the Nios® II subsystem controls the liquid crystal display (LCD) to display in real-time the system's status messages on a two-line LCD, and manipulates the general-purpose input-output peripherals. The control program that runs on the Nios® II processor is written in assembly language for highest performance and minimal code density.

The second module, the PD-like fuzzy logic module, which demands more computational power, is designed and implemented in the FPGA's massively parallel logic elements using a handcrafted VHDL code as a custom reconfigurable application-specific accelerator component to maximize parallel processing. The fuzzy logic module calculates the necessary energy by which the system modifies the process in such a way the control objective can be obtained.

The approach allows a processor to co-exist with custom logic in the FPGA fabric, provides the flexibility to combine reconfigurable hardware and software based controls to achieve a simple and better control of the sun tracker. This hardware/software solution runs on an Altera low-cost Cyclone II FPGA, the EP2C35, to control the motion of two stepper motors used as the mechanical drive system to keep the solar panel surface continuously facing the sun during the day.

### 8 Organization of the Thesis

This thesis is compiled into 7 chapters including this introduction and followed by references used in this work. Chapter 1 introduced the problematic. It also reviewed existing computing platforms used to implement digital controllers: processor-based and FPGA-based with or without the SoPC technology.

In chapter 2, a literature review that surveys relevant research works on sun tracking systems conducted in the last few decades is presented. Chapter 3 introduces fuzzy set theory and fuzzy logic control. Chapter 4 presents background material to highlight the possibilities and advantages using the FPGA. It also describes the most versatile and industry-standard soft-core processor, the Nios® II as well as the emerging and revolutionary SoPC technology.

Chapters 5 and 6 constitute the bulk of the thesis. The former describes in details the design and implementation of the fuzzy logic module. The latter begin by reviewing the merits of the SoPC approach over the off-the-shelf processor and peripheral devices as platforms for industrial applications. It lays out in detail the hardware and software design. This chapter also presents the simulation and implementation of the FPGA-based intelligent dual-axis sun tracking system. It reports the setup of the simulations and a prototyping real-time implementation of the system which can be seen as a proof-of-concept. Chapter 7 concludes the thesis with some discussions and remarks for future research.

Finally, the thesis terminates with an extensive list of references for additional information on the subject.

Part of the work reported in chapters 1, 5 and 6 has been published in [90].

Chapter 2

## **Literature Review**

## 1 Introduction

Before diving into the practical of this thesis, a review of literature in the core area will be presented with the aim to provide the reader with a survey on active sun tracking systems using different types of computing platforms and control strategies, as well as developments in FPGA-based designs with or without model-based fuzzy logic control systems. Also, we report by whom, when and how.

Over the past four decades or so, a large number of contributions have been reported in seminars and literature showing the increasing interest in the design and implementation of sun tracking systems to increase their performances and efficiencies to harvest maximum power from the solar panels mounted on trackers. Several control strategies as well as different computing and control platforms have been used and tested to tackle this problem [7], [8], [18-66]. These strategies can be categorized into three main classes: open-loop, closed-loop and hybrid sun tracking control systems.

(i) Open-loop control strategies rely on a fixed control algorithm [7], [8], [18-29]. These controllers use mathematical formulae with the data of a whole one-year sun trajectory to calculate the sun's movement in the sky and need not sense the sunlight to position the solar panel. This data is usually the current time, day, month and year of a specific geographical location. The algorithms do not use any feedback from the controlled system to determine if it has achieved or not the desired goal.

- (ii) Closed-loop types of sun tracking systems are based on feedback principles. They usually use light sensors such as light dependent resistors (LDRs) to determine the position of the sun in the sky with respect to the surface of the solar panel [8], [30-37]. They are more reliable than open loop type controllers. The use of the feedback makes their system response less sensitive to external disturbances.

- (iii) Hybrid implementations, a strategy that combines both open- and closed-loop control are also reported in literature [31], [38].

There is a large variety of techniques used to implement closed-loop type controllers. These range from the On-Off control laws to more advanced techniques based on fuzzy logic control including the classical controllers: the Bang-Bang controller, proportional-integral (PI), proportional-derivative (PD) and proportional-integral-derivative (PID).

A myriad of physical implementations of sun tracking strategies are also reported in literature. Similar to other industrial applications, these implementations have gone through several stages of evolutions. They evolved from the early mechanical designs to the use of discrete analog and digital standard integrated circuits. The general-purpose microprocessor-, microcontroller- and DSP-based were the dominant platforms for the implementation and realization of control algorithms based on conventional PID and alike, Bang-Bang and fuzzy controllers. The use of the FPGA with or without the system-on-programmable-chip approach emerged during the last decade.

### 2 Open-Loop Tracking Strategies

An open-loop type controller computes its input into a system using only the current state and the algorithm of the system to determine if its input has achieved the desired goal. These types of controllers based on mathematical algorithms/programs provide predefined trajectories for the tracking system. These trajectories can be accurately determined because the relative position of the sun can be precisely calculated at any time for any location on the earth [7], [18] [19].

It is in 1975, that McFee [20] presented the first automatic solar tracking system. The algorithm used to control the tracker computes the flux density distribution and the total received power in a solar power system. Since that time, numerous works using open-loop control have been carried out in the design and implementation of algorithms based on astronomical formulae. They were used to drive electromechanical actuators to steer single-and dual-axis sun tracking systems.

Semma et al [21] were among the first to use a microprocessor as a replacement of the hard-wired logic used in earlier sun trackers to control the motion of a two-axis sun tracking system. The controller was based on an active sun tracking approach and allows an array to track the sun within five arc-minutes. This resulted in significant improvements in reliability via parts screening and packaging and increased the functional capabilities of former basic tracking systems.

In [22], the authors derived a general formula arguing that it embraces all the possible one-axis tracking methods. To derive the formula, they used coordinate transformation technique. This consists in transforming the sun's position vector from earth-center frame to earth-surface frame and then to collector-center frame. In doing so, they could resolve it into solar azimuth and altitude angles relative to the solar collector making it simpler to the controller to determine by how much it should tune the solar collector to minimize the misalignment.

In 2004, Abdallah [23] designed and implemented four electromechanical open-loop solar tracking systems: two-axis, one-axis vertical, one-axis east-west, and one-axis north-south in

order to investigate the effects of the current, voltage and power characteristics of a flat-plate photovoltaic system compared to a fixed one with an inclination of 32° to the south. The movement of the tracker was controlled by an algorithm in which the pre-calculated position was programmed into a programmable logic controller (PLC). The author claimed that the tracking systems increased the electrical powers of the collector by 43.87, 37.53, 34.43 and 15.69% respectively for the two-axis, one vertical axis, one-axis east-west and one-axis north-south compared to that of the fixed one.

In paper [24], Grena describes an algorithm for obtaining highly precise values of the solar position. Taking the fractional Universal Time (UT), the date, and the difference between UT and Terrestrial Time (TT) (longitude, latitude, pressure and temperature) as inputs, the algorithm computed the angular position of the earth with respect to the sun in the ecliptic plane and then used this angle and the inclination angle of the earth's rotational axis to calculate the position of the sun.

In reference [25], the authors argued that the open-loop tracking strategies used to compute the direction of the solar vector should be both accurate and computationally straightforward to minimize the price of the tracking system. They developed an algorithm for predicting the solar vector given knowledge of the time and the location.

In 2004, Reda et al [26] presented a simple step-by-step procedure for implementing a solar position algorithm. In this algorithm, the solar zenith, azimuth and incident angles were derived using ecliptic longitude and latitude for mean Equinox of data along with other information. They reported that the solar zenith and azimuth angles could be calculated with uncertainties of  $\pm 0.0003^{\circ}$ .

In [27] an open-loop control algorithm was developed to control a dual-axis sun tracking system. The algorithm implemented into the LOGO-24 RC programmable logic controller (PLC) is based on the mathematical definition of surface position. This latter is defined by

two angles: the slope of the surface and the surface azimuth angle. The authors used two tracking motors, one for the joint rotating about the horizontal north-south axis to adjust the slope of the surface and the other motor to rotate the collector about the vertical axis to control the surface azimuth angle. A computer software has been developed to calculate the optimal positions of the tracking surface during the daylight hours which were divided into four identical time intervals. For each interval, the solar and motors speed are defined and programmed into the PLC. The authors concluded the gain is considerable with an increase in the daily collection of about  $41.34^{\circ}$  as compared to that of a fixed surface.

In 2010, Duarte et al [28] presented in an international conference on renewable energies the design of a microcontroller-base two-axis solar tracker using solar maps. They employed solar maps with the sun coordinates which depend on the time and geographical location.

Mousazadeh et al [29] and Lee et al [8] reviewed different types of sun-tracking systems. They focused on the potential energy gain obtained by the application of both open- and closed-loop algorithms. They surveyed some of the most significant proposals of both types and discussed their pros and cons. They compared the outcomes of tracking systems with fixed-position counterparts. They concluded that solar systems which track the changes in the sun's trajectory over the course of a day collect far greater amount of solar energy. They also reported that the most efficient and popular sun-tracking devices was found to be in the form of polar-axis and azimuth/elevation types.

### **3** Closed-Loop Tracking Strategies

Closed-loop types of sun tracking systems are based on feedback control principles [8]. They use the concept of the open-loop for their forward path and feedback loop(s) between the system's output and input. In a closed-loop sun tracking system, light and image sensors are in general used to discriminate the sun's position and the induced signals

proportional to the sun light intensity employed as inputs to the controller. These data are processed by the controller to automatically achieve and maintain the desired output condition.

Roth et al [30] described the design and construction of an electromechanical automatic sun-following system. They used a pyrheliometer to measure direct solar radiation. A fourquadrant photo detector to sense the position of the sun and two small DC motors to move the instrument platform are controlled by a Z80 microprocessor to keep the sun's image at the center of the four-quadrant photo detectors. The presented tracker can be adapted to work with solar cell panels or concentrators. The interesting feature of this system is under cloudy conditions, when the sun is not visible; a computing program calculates the position of the sun and takes control of the movement, until the detector can sense the sun again. The same authors described in [31] an improved version of their sun tracker. Although they kept the same mechanical base they brought some novelties. The DC motors were replaced by stepper motors, the four-quadrant sensor replaced by two sensors and the Z80 computing platform was replaced by a microcontroller connected to a PC. The two sensors were used, one for sun position information and the other to measure the sun light intensity. The tracker can operate in two modes. In the clocked mode of operation, the position of the sun is calculated based on the date and time information of its clock. Light position errors are measured during the day and stored for later analysis. These data will be used the next day to compute more accurate positions of the sun. In the active or sun mode of operation, the tracker uses the data of the sun monitor to control the pointing.

In [32] Kalogirou described the design and construction of a one-axis sun tracking system where the position and status of the sun are detected by three LDRs. One LDR is used to detect the focus state of the collector; another one is responsible of detecting any cloud cover, while the third is employed to discriminate daylight. The controller is constructed with

standard analog and digital integrated circuits. The actuator used in the tracker to point the collector toward the sun is a low-power DC motor with speed-reduction gearbox. The author reported that the deviation from the ideal posture is  $0.2^{\circ}$  and  $0.05^{\circ}$  with solar radiation of 100 and 600 Wm<sup>-2</sup> respectively.

Recently, an image-based sun-tracking system was developed by Cheng. D. Lee et al [33]. The system consists of a self-design reflecting Cassegrain telescope, a webcam and an embedded image processing algorithm to point to the sun. the central coordinates of the sun images are calculated then sent to the solar tracker to follow the sun. Authors claimed that their tracking system achieved a tracking accuracy of  $0.04^{\circ}$ .

In [34] Sefa et al designed and implemented a PC-based one-axis sun tracking system for production of clean energy. The data from the two light sensors is collected by the microcontroller-based data acquisition unit and transmitted serially to the PC for processing and storage. Software developed in C language processes the collected data and instructs a DC motor to follow the sun during day time. In addition, current, voltage and solar position panel are displayed on the PC's screen.

In reference [35], A. Konar et al employed a microprocessor to automatically position an optimally tilted photovoltaic flat type solar panel for the collection of maximum solar irradiation. The azimuth angle of the optimally tilted panel is controlled using one infrared light detector. The technique used is similar to "perturb and observe" to determine maximum irradiation. The use of step-tracking scheme instead of continuous tracking keeps the motor idle for most of the time which results in power saving. The adjustment of the tilt angle is done on a monthly basis. They suggested the use of a two-dimensional tracker for an automatic tracking. We believe that the use of a second light detector would have not only simplified the design but saved energy and motor aging due to continuous rotation in both direction of the motor searching for optimal position of the solar collector.

Another microprocessor controlled automatic sun tracker is reported in [36]. Two light sensors arranged in east-west direction are used to discriminate the position of the sun with respect to the solar panel. A DC motor is gear coupled to rotate the panel along the east-west direction to keep the panel perpendicular to the sun vector. Attached to the collector are two switches used to limit the movement of the panel beyond its maximum angular positions in the east and west directions.

In [37] Saxena et al designed and fabricated a microprocessor-based controller for a dualaxis sun tracker to follow the sun in azimuth and altitude directions using two stepper motors. The system operates in both open- and closed-loop modes. In closed loop mode the sensor card provides signals to the controller. In open-loop mode, the tracker is brought to a precalculated position depending on the month and time of the day.

In general, open-loop control systems are cheaper because they do not require any means to gather feedback information such as light sensors. However, they present a major problem as they have no error correction capabilities. In addition, a given algorithm is valid for a specific location only. Closed-loop systems use sun finding position sensors. They are more reliable than open-loop systems. However, they may not have capabilities to track the sun on cloudy days. Hybrid control systems which consist of a combination of open- and closed-loop strategies are also reported in literature [**31**], [**38**]. In such systems, the closed loop tracking strategies are used to check and calibrate the astronomical control system.

## 4 FPGA-Based Tracking Strategies

A FPGA-based digital controller has many advantages compared to processor-based and other platform types based controllers. It supports high-speed and concurrent control algorithms, provides a higher degree of flexibility and a rapid low-cost manufacturing solution. In the last decade, with high density FPGA chips, SoPC-based systems using Nios® II soft core processor are being extensively used to implement control algorithms. This reconfigurable computing approach is bringing a major revolution in the design of these digital controllers. It allows the co-existence of the microprocessor with the user defined hardware accelerators developed in HDL in a single chip instead of the mixed structure microprocessor/FPGA [7], [39-48]. This approach is being adopted for its flexibility in hardware and software, higher performance, reduced chip count and low cost.

In [39], Xinhong et al studied the applications of a FPGA development board to intelligent solar tracking. Utilizing the Nios II Embedded processor, the authors developed a solar tracking system. The two motors are controlled by a fuzzy logic module. The fuzzy controller uses five fuzzy rules which reduce significantly the computation complexity in the real-time control. The tracking systems can be operated into three modes: balance positioning, manual mode and automatic mode. For the balance positioning, they used four mercury switches. In the automatic mode, the fuzzy controller processes signals induced by four Cadmium sulphide Photoresistors which discriminate the position of the sun in the sky. These signals are digitized using four single-channel ADCs. The manual mode is used if the system has a fault or needs to be maintained. The results of the experiment yielded more energy than the array as a stationary unit. They reported that their system can achieve the maximum illumination and energy concentration and cut the cost of electricity by requiring fewer solar panels, therefore, it has significance for research and development.

In [40], the authors aimed to test whether FPGAs are able to achieve better position tracking performance than software-based real-time platforms. The comparison was conducted be embedding the same fuzzy logic controller (FLC) into a Virtex-II (XC2v1000) FPGA from Xilinx and into software-based real-time platform NI CompactRIO-9002 architectures with the same sampling time. They concluded that the FPGA based FLC

22

exhibits much better performances (up to 16 times in the steady-state error, up to 27 times in the overshoot and up to 19.5 times in the settling time) over the software-based FLC.

In publication [7], the authors dealt with an open-loop two-axis sun tracking for a PV system. The tilt- and azimuth-angle trajectories of the tracking system are determined using an optimization procedure based on a stochastic search algorithm called Differential evolution. In this procedure, the objective function is evaluated by giving the models of available solar radiation, tracking system consumption, and the efficiency of solar cells.

In [41], the authors describe the design of a stand-alone solar tracking system using a FPGA. The design is based on astronomical equations to determine the position.

The basic software of the stand-alone tracking system is made up of (i) an Off-line calculations of the sun path equations (developed in C), and (ii) a FPGA with suitable data to the driving mechanical system.

Sun path equation determines the value of altitude and azimuth angles at any time of the day. These values are stored as 8-bit words in a ROM. Two look-up tables were used, one for the altitude angle and the other for the azimuth. The FPGA is designed to control the address allocation for the look up tables stored in the ROMs for the sun tracking application. The FPGA code is written in VHDL in Xilinx FPGA.

In [42], Monmasson et al reviewed the state of the art of FPGA design methodologies with a focus on industrial control system applications. They review is followed with a short survey on FPGA-based intelligent controllers for modern industrial systems. To illustrate the benefits of an FPGA implementation using the proposed design methodology, two case studies were presented. They consist of the direct torque control for induction motor drives and the control of a diesel-driven synchronous generator using fuzzy logic.

In recent years, high density FPGA chips can efficiently integrate a reduced instruction set computer (RISC) embedded soft-core processor, ready made intellectual property (IP)

peripherals and user defined hardware accelerator modules. A technology termed SoPC. This hardware/software co-design combines the software-program executed by the embedded processor to implement non-timing crucial repetitive control laws, while timing critical intensive-computational functions are best implemented as hardware accelerator modules in the FPGA logic. A large number of contributions using SoPC technology in different fields of electrical engineering and control are reported in literature [49-54].

## 5 Fuzzy Control Tracking Strategies

Fuzzy control is the application of fuzzy logic to real-world control problems [55]. The first fuzzy control application belongs to Mamdani & Assilian where the control of a small steam engine is considered [56]. Since that time and due to its ease of use and robustness, fuzzy control technology witnessed a wide range of applications in almost all areas. Applications of fuzzy control include mechatronic systems (as manufacturing, robotics, automotive, etc), nuclear industry, telecommunications, medical services etc. There are a lot of contributions and reviews that illustrate the use of fuzzy control in industrial applications [55-66].

A fuzzy logic computer-controlled sun tracking system is described in [57]. This closedloop dual-axis tracking system is driven by two permanent magnet DC motors to provide necessary torque to the PV panel. A PC-based basic fuzzy-like P-type controller with 14 fuzzy rules was implemented. A data acquisition and a serial communication were implemented. Back to 1999, in our opinion, it would have been simpler and more performant to use either the parallel port or the Industry Standard Architecture (ISA) bus to interface the sun tracking hardware circuitry with the PC.

In implementing a fuzzy system on a field programmable gate array, McKenna et al [58], implemented a fuzzy control system in a FPGA to have a control surface as smooth as possible. They used a weighted average approach to minimize the dimension of the look-up table (LUT). The approach uses 3 or 4 most significant bits of each input to determine the

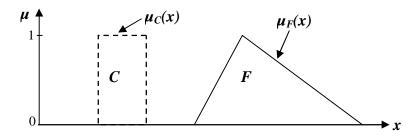

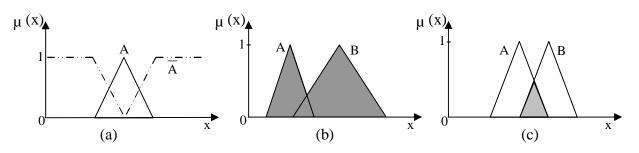

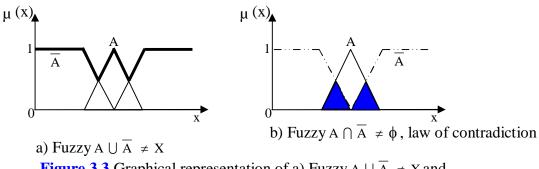

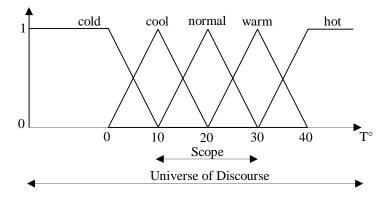

address for the LUT and to eliminate the rawness, the remaining bits are used to perform the weighted average. Simulations were carried on using Matlab to verify the functionality of the approach. The authors concluded that even with a large number of inputs, this approach helps solve the exponential growth problem and complexity of LUT. The overall controller was written in Verilog HDL and implemented in Xilinx 4000 series FPGA chip.