# Deep analysis of the Geometric Component in Charge Pumping of Polysilicon Thin-Film Transistors

Hakim TAHI, Boualem Djezzar, Cherifa TAHANOUT, Karim BENMESSAI

Abstract- In this article, we model the geometric component in charge pumping technique (CP) of polysilicon thin film transistors (poly-Si TFT). This model is based on both remaining carrier types when the device transit from accumulation to inversion and vice versa. Therefore, it depends on gate length (L) and width (W) as well as on gate signal rise  $(t_f)$  and fall  $(t_f)$  time. The proposed model shows a good agreement with the experimental data. We have shown that the geometric component due to the remaining carriers, when poly-Si TFT transits from inversion to accumulation, is very small compared to that due to the transition from accumulation to inversion. Consequently, a new analytic CP model, depending on gate width, is developed for n-channel poly-Si TFT.

*Index Terms*—Charge pumping (CP), geometric current ( $I_{Geo}$ ), polycrystalline Silicon thin-film transistors (poly-Si TFTs).

### I. INTRODUCTION

The geometric component ( $I_{Geo}$ ) in charge pumping (CP) technique is well known as the parasitic and undesirable effect causing the overestimation of interface trap density [1-3]. In conventional metal- oxide -silicon field effect transistors (MOSFETs), this component arises from recombination of remaining inversion-layer carriers, which not have enough time to flow back to the source and drain regions, with the substrate majority carriers, when the device is witched from inversion to accumulation. Therefore, in conventional MOSFETs  $I_{Geo}$  is inversion-layer carriers- transport limited and depends on the gate length and the gate signal time ( $t_f$ ) in N-MOSFET (gate signal rise time,  $t_r$ , in P-MOSFET). These issues have been modeled in our previous work [4].

The poly-silicon thin film transistors (poly-Si TFT) have recently attracted research interest, due to their application in integrated active matrix display [5-6]. Some authors investigated IGeo in CP technique of poly-Si TFT [7-8]. They reported that IGeo is somewhat different from that of the conventional MOSFET. For an n-channel poly-Si TFT, during  $t_r$  of the CP gate signal, the device is switched from the accumulation regime to the inversion regime, the accumulated holes and the trap emitted holes return from the channel to the side contact laterally through the active area along the channel width (W) direction. If  $t_r$  is sufficiently short, some holes have not enough time to flow back to the substrate side contact, they will subsequently recombine with electrons coming from the Source/Drain when the channel is switched to the inversion, resulting in the geometric component. Hence, contrary to the conventional MOSFET,  $I_{Geo}$  in n-channel poly-Si TFTs depends on W and  $t_r$ , and is hole-transport (substrate carrier) limited [8]. However, in those above-sited works the

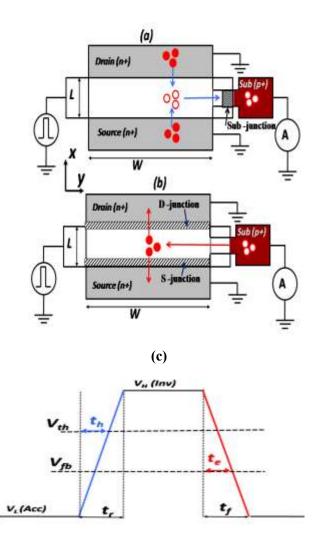

Fig.1 Illustrative schematic of the contribution mechanisms to the geometric component at different time of gate signal in n channel poly-Si TFT. (a) Recombination of remaining accumulation holes with the electrons inversion layer during the rise time of the gate signal  $(t_r)$ , (b) remaining electrons of the inversion layer which recombine with the incoming substrate holes during the gate signal fall time (this geometric component is similar to that occuring in conventional MOSFETs), (c) definition of CP gate signal parameters.

effect of the gate length *L* on  $I_{Geo}$  is not investigated and is unclear. In addition, recently, Wang et *al* [8] proposed an interesting method to extract and separate  $I_{Geo}$  in CP measurement of n-channel poly-Si TFTs. However, this method is based on the empirical equation with undefined fit parameters (without physical meaning). In this work, using the semiconductors theory the  $I_{Geo}$  in CP of poly-Si TFTs is modeled in two dimensions (by taking into account both inversion-layer and substrate carriers transport). Consequently, a new analytic physical-based CP model is established for poly-Si TFTs.

#### II. GEOMETRIC COMPONENT IN POLY- SI TFT

The geometric component model, developed in this paper is based on both amount of remaining inversion-layer carriers (electrons in the case of n-channel poly- Si TFT) transferred to the poly-Si TFT substrate after the switching off and remaining accumulated carriers (holes) after the switching on. Since, it holds that the remaining inversion-layer (accumulated) carrier density  $n_s$  ( $p_s$ ) is lower than the majority substrate (inversion-layer) carriers, it is reasonable to assume that all remaining carriers recombine with incoming substrate majority (inversion-layer) carriers (see fig.1). Hence,  $I_{Geo}$  can be expressed by the contribution of two components  $I_{Geo_n}$  and  $I_{Geo_p}$  due to remaining electrons and holes, respectively:

$$I_{Geo} = I_{Geo -n} + I_{Geo -p}$$

=  $q f [n_s(L)W + p_s(W)L]$  (1)

where q is the electron charge, f is the gate signal frequency, L and W are the gate length and width, respectively.  $n_s(p_s)$  is the total number of remaining electrons (holes) under the gate given by:

$$n_{s}(L) = 2\int_{0}^{\frac{L}{2}} g(x)dx$$

(2)

$$p_s(W) = \int_0^W g(y) dy$$

(3)

g(x) and g(y) (cm<sup>-2</sup>) are the remaining carriers concentration after transition from inversion to accumulation and from accumulation to inversion, respectively. g(x) [g(y)] depends on gate length (width) and gate fall (rise) times as well as on the following mechanisms (see fig.1):

During the rise time, the accumulated holes are first evacuated at the side substrate contact by the self induced field [9]. Then, as soon as the hole are evacuated the self induced field decreases and the holes evacuation is caused by the combination of the fringing field (due to substrate-contact side depletion zone, Sub Junction) and the thermal diffusion, see fig.1 (a). However, during the fall time  $(t_j)$ , the electrons of the inversion layer are evacuated in the same manner as in the conventional MOSFET, see fig.1 (b), the detail can be found in ref [4,9].

#### III. MODEL DERIVATION

During the gate rise time, the holes drift back to p+ contact laterally thought the active area along the channel width. However, during the gate fall time, the electrons move only from the middle of the channel to the source/drain due to CP configuration (the source-substrate and drain-substrate are biased to the same potential). In our previous work [4], we have modeled the remaining carriers in n-channel transistor by using the continuity equation, the current carrier density equation, and the evacuation processes by both the electric field and the thermal diffusion, which are generally the most case encounters in experimental CP. We have demonstrated that the total number of remaining carriers in conventional NMOSFET is given by [4]:

$$n_{s}(L,t) = 2\left(\frac{C_{ox}(V_{H} - V_{th})}{q}\right) \left[ \left(\frac{\mu_{n}\beta}{v_{n}} EXP(\frac{v_{n}}{\mu_{n}\beta}\frac{L}{2}) - \frac{\mu_{n}\beta}{v_{n}} - \frac{L}{2} \right) \right] EXP\left(-\frac{t_{e}}{\tau_{L}}\right)$$

(4)

Using the same method as in [4] for the evacuation of hole during the gate rise time and keeping in mind that in poly-Si TFT the holes move laterally thought the active area along the channel width, it will be easy to find the fallowing expression:

$$p_{s}(W,t) = \left(\frac{C_{ox}(V_{L} - V_{fb})}{q}\right) \left[ \left(\frac{\mu_{p}\beta}{\nu_{p}} EXP(\frac{\nu_{p}}{\mu_{p}\beta}W) - \frac{\mu_{p}\beta}{\nu_{p}} - W \right) \right] EXP\left(-\frac{t_{h}}{\tau_{W}}\right]$$

(5)

where  $C_{ox}$  is the gate capacitance par unit area,  $\mu_{n(p)}$  is the electron (hole) mobility,  $v_{n(p)}$  is the drift electron (hole) velocity  $\beta$  is the thermal voltage,  $V_L(V_H)$  is the low (high)-level of the gate signal,  $V_{th}(V_{fb})$  is the threshold (flat band) voltage,  $\tau_L(\tau_W)$  is the exponential decay constant associated with the influence of the electric field and the thermal diffusion in x (y) direction, see fig.1.  $t_e$  and  $t_h$  are the time of electron and hole drift, respectively, given by :

$$t_e = \frac{\left| V_H - V_{fb} \right|}{\Delta V_G} t_f \tag{6}$$

and

$$t_h = \frac{\left|V_L - V_{th}\right|}{\Delta V_G} t_r \tag{7}$$

where  $\Delta V_G$  is the gate signal magnitude.

Therefore, using (1), (4) and (5) the geometric component can be expressed by:

$$I_{Geo}(L, W, t) = I_{Geo-n}(L, W, t) + I_{Geo_p}(L, W, t)$$

$$= qW f\left[\left(\frac{2\mu_n\beta}{\nu_n} EXP(\frac{\nu_n}{\mu_n\beta}\frac{L}{2})\right) - L - \frac{2\mu_n\beta}{\nu_n}\right]X$$

$$\left(\frac{(C_{ox}(V_H - V_{th}))EXP\left(-\frac{t_e}{\tau_L}\right)}{q}\right) + qLf\left[\left(\frac{\mu_p\beta}{\nu_p} EXP(\frac{\nu_p}{\mu_p\beta}W)\right) - W - \frac{\mu_p\beta}{\nu_p}\right]X$$

$$\left(\frac{(C_{ox}(V_L - V_{fb}))EXP\left(-\frac{t_h}{\tau_W}\right)}{q}\right)$$

(8)

By adding the expression of the geometric component given by (8) to the pure CP current  $I_{CP-Pure}$  given by [2]:

$$I_{CP\_Pure} = 2kTqfD_{it}LWLn\left[v_{th}n_i\left(\sqrt{\sigma_n\sigma_p t_f t_r}\right)\frac{|V_{th} - V_{fb}|}{\Delta V}\right]$$

(9)

where  $\sigma_n/\sigma_P$ ,  $v_{th}$ ,  $n_i$ ,  $D_{it}$ , k and T are, respectively, the electron/hole capture cross section, the carrier thermal velocity, intrinsic carrier density, the density of state within the band gap, the Boltzmann constant and temperature.

Therefore, the modeled CP current  $(I_{CP\_Mod})$  can be expressed as :

$$I_{CP\_Mod}(L, W, t) = I_{CP\_Pure} + I_{Geo}$$

$$= 2kTqfD_{it}LWLn\left[v_{th}n_{i}\left(\sqrt{\sigma_{n}\sigma_{p}t_{f}t_{r}}\right)\frac{\left|V_{th}-V_{fb}\right|}{\Delta V}\right] + qWf\left[\left(\frac{2\mu_{n}\beta}{v_{n}}EXP(\frac{v_{n}}{\mu_{n}\beta}\frac{L}{2})\right) - L - \frac{2\mu_{n}\beta}{v_{n}}\right]X$$

$$\left(\frac{\left(C_{ox}(V_{H}-V_{th})\right)EXP\left(-\frac{t_{e}}{\tau_{L}}\right)}{q}\right) + qLf\left[\left(\frac{\mu_{p}\beta}{v_{E}}EXP(\frac{v_{p}}{\mu_{p}\beta}W)\right) - W - \frac{\mu_{p}\beta}{v_{p}}\right]X$$

$$\left(\frac{\left(C_{ox}(V_{L}-V_{fb})\right)EXP\left(-\frac{t_{h}}{\tau_{W}}\right)}{q}\right)$$

$$(10)$$

The terms  $\frac{2\mu_n\beta}{v_n}$  and  $\frac{\mu_p\beta}{v_p}$  present the gate length and

width below which the  $I_{CP Mod}$  is linearly depending on L and W, respectively. In other words, they present the gate length and width below which the geometric component can be negligible.

For  $L < \frac{2\mu_n \beta}{\nu_n}$  and  $W < \frac{\mu_p \beta}{\nu_n}$ , the geometric component is

reduced in x and y direction, thus (10) can be rewrites as:

$$I_{CP\_Mod}(L,W,t) = qfWL$$

$$X\left(N_{it} - \frac{(C_{ox}(V_H - V_{th}))EXP\left(-\frac{t_e}{\tau_L}\right)}{q} - \frac{(C_{ox}(V_L - V_{fb}))EXP\left(-\frac{t_h}{\tau_W}\right)}{q}\right)$$

(11)where  $N_{it}$  is the density of state par unity area  $(N_{it}=Dit^*\Delta E,$ where  $\Delta E$  is the scan energy band gap interval by the CP,

given by

$$\Delta E = 2kTLn \left[ v_{th} n_i \left( \sqrt{\sigma_n \sigma_p t_f t_r} \right) \frac{\left| V_{th} - V_{fb} \right|}{\Delta V} \right].$$

Therefore:

lefelore.

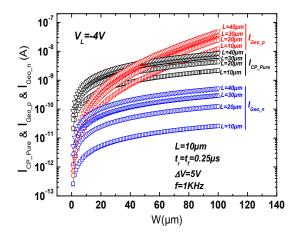

Fig.2 Calculated pure charge pumping current ( $I_{CP Pure}$ ), the geometric component in x direction  $(I_{Geo_n})$ , and y direction  $(I_{Geo_p})$  as a function of the gate width (W) for different gate lengths (L). The used parameters are:  $V_L=-4$ ,  $\Delta V_G=5V$ ,  $t_f=t_r=0.25 \ \mu s$ ,  $C_{ox}=9.667 \ 10^{-8} \ F/cm^2$ ,  $V_{th}=0$  and  $V_{fb}=-2V$ ,  $ni=1.510^{10} \ cm^2$ ,  $\sigma_p=\sigma_n=2.027 \ 10^{-16} \ cm^2$ ,  $D_{it}=2.01410^{12} \ cm^{-2} \ eV^{-1}$ ,  $v_{th}=10^7 \ cm/s$ ,  $\mu_p=40 \ cm/Vs[8]$ ,  $\mu_n=80 \ cm/Vs$ ,  $v_p=v_n=400 \ cm/s$ .

$$\frac{d^2 I_{CP\_Mod}(L,W,t)}{dLdW} = 0$$

$$N_{it} = \frac{(C_{ox}(V_H - V_{th}))EXP\left(-\frac{t_e}{\tau_L}\right)}{q} + \frac{(C_{ox}(V_L - V_{fb}))EXP\left(-\frac{t_h}{\tau_W}\right)}{q}$$

(12)

The last equation relies the exponential decay constants evacuation ( $\tau_e$  and  $\tau_h$ ) with the transistors and gate signal parameters. It will be used later, in section-IV to experimentally extraction of  $\tau_e$  and  $\tau_h$ .

#### IV. MODEL VALIDATION

In the fallowing, to validate our proposed model we used the literature CP experimental data of n-channel poly-Si TFT as well as their parameters reported by Lu et al [7] and Wang et al[8].

First, we used equation (12) and the following parameters:  $t_f = t_r = 0.25 \ \mu s$ ,  $\Delta V = 5V$ ,  $C_{ox} = 9.667 \ 10^{-8} \ F/cm^2$ ,  $V_{th} = 0$ ,  $V_{fb} = -2V$ , and  $N_{it} = 1.3 \ 10^{12} \ \text{cm}^{-2}$  to extract the exponential decay constants  $\tau_W$  and  $\tau_L$  along the gate width (y direction) and length (x direction), respectively, using two low voltage CP gate signal a round the CP maximum current (  $V_{\underline{L}} \text{=-} 4 V$  and  $V_L$ =-3.5V).  $\tau_W$  and  $\tau_L$  are found around of 6.58 10<sup>-7</sup> s and 5.4  $10^{-7}$  s, respectively. Then, we have computed  $I_{CP Pure}$ ,  $I_{Geo n}$ and  $I_{Geo p}$  as function of gate width for different gate lengths  $(L=10-40\mu m)$ , using the first, the second and the third term of equation (10). The results of the calculation are given in fig.2. These results show that  $I_{Geo_n}$  is lower compared to  $I_{Geo_p}$  and for all used gate length. I<sub>CP Pure</sub>

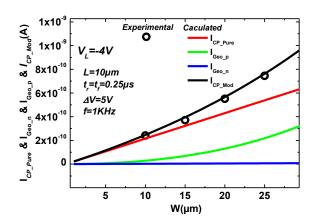

Fig.3 Comparison between the calculated  $I_{CPMod}$  using the proposed model and the CP experimental data for gate length fixed at 10µm and varied gate width ,reported in[8]. The same parameters as in fig .1 are used for the calculation.

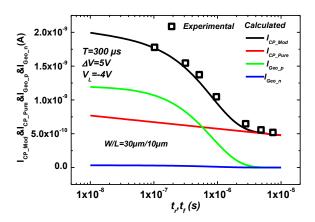

Fig.4 Comparison between the experimental CP data reported by Lu et al and the calculated  $I_{CP-Mod}$  using the proposed model as a function of transition gate signal time  $(t_f=t_r)$ .

This behavior is not surprising, since it is clear that for conventional n-channel poly-Si TFT the electron evacuation during fall time could be much faster than that of (evacuation) hole during the rise time, because the electrons can be quickly drift along the low resistance of inversion channel, while the hole must drift through the substrate (of high resistance due to grain boundaries) to side contact. In addition due to CP configuration the electrons move back only from the middle of the channel to the source/drain. Contrary, to the hole which drift along the gate width to the side contact. Finally, the mobility of holes is smaller than that of electrons. According to the above analysis, one can plausibly think that the geometric component in n-channel poly-Si TFT (under certain condition  $t_f$  and  $t_f$ ) is dominated by the remaining hole when the transistor transits from accumulation to inversion and depend on  $t_r$  and W. Indeed, the same behavior is experimentally reported in [7] and [8] for the same parameters as used in our calculation. In those works, it has been demonstrated that,  $I_{Geo}$  is hole transport limited and for typical  $t_f > 0.1 \mu s$  the sheet density of remaining hole in the channel is

independent of the channel length but depends on channel width. Furthermore, fig.3 shows a good agreement between the CP experimental data and calculated I<sub>CP Mod</sub> (black curve), which is the sum of  $I_{CP Pure}$  (red curve),  $I_{Geo p}$  (green curve) and  $I_{Geo n}$  (blue curve), as a function of the gate width using the same experimental conditions and devices parameters as those used in [8]. We should note that the evacuation velocity carriers  $(v_n = v_n)$ , is the only adjustable parameter to fit the experimental data. The comparison un between the experimental CP data reported by Lu et al [7] and the computed  $I_{CP Mod}$ , using equation (10) as a function of  $t_{f,r}$  $(t_f = t_r)$  is presented in fig.4 for n-channel poly-Si TFT with W/L=30/10. In this figure, we also presented the calculated  $I_{CP\_Pure}$ ,  $I_{Geo\_p}$  and  $I_{Geo\_n}$ . It is clear, from fig.4, that the CP experimental data is well fitted by computed  $I_{CP Mod}$  using the proposed model (equation (10)).  $I_{CP Mod}$  increases with decreasing  $t_{f,r}$  and fallow the pure CP current ( $I_{CP Pure}$ ) as described in [2]. However, an additional increase can be observed when  $t_{f,r} < 1 \mu s$  and  $I_{CP Mod}$  diverges rapidly from  $I_{CP Pure}$  . This is due to the geometric component increase caused by t<sub>fr</sub> decrease, which is principally dominated by  $I_{Geo_p}$  (green curve), whereas  $I_{Geo_n}$  is negligible. According to this comparison, our proposed model not anly fit well the experimental CP data but captures all experimental observations reported in [7] and [8] such as the disappearance of the geometric component for the transition time  $t_{fr} > 1 \mu s$  and the dependence of the geometric component on gate width and not on gate length. Thus, our developed model could be powerful tool to predict the geometric component and charge pumping in poly-Si TFT devices.

In addition, as we have reported above, the  $I_{Geo\_n}$  is negligible. Therefore, we can use equation (10) to establish CP empirical relationship reported by Wang et al [8] and identify their empirical parameters as follow:

$I_{Geo -n}(L, W, t) \approx 0$ , if we put:

$$\lambda = \frac{\beta \mu_p}{\nu_p} \tag{13}$$

and

$$\alpha = qfW\lambda f\left(\frac{\left(C_{ox}\left(V_{L} - V_{fb}\right)\right)EXP\left(-\frac{t_{h}}{\tau_{W}}\right)}{q}\right)$$

(14)

we can express (8) as

$$I_{Geo} = \frac{\alpha}{\lambda} \left( \lambda EXP \left( \frac{W}{\lambda} \right) - W - \lambda \right)$$

(15)

Equation (15) corresponds to the empirical model of the geometric component developed in [8]. Where fitting parameters  $\alpha$  and  $\lambda$  are well defined as function of device and experimental conditions, and they have now a physical meaning in CP as a function of W. Note that the equation (15) is also used by Tahi et al [10] to extract the geometric

component in CP current of MOSFET, excepting using L instead of W, because in MOSFET the geometric component is L-controlled effect.

In addition, in the absence of  $I_{Geo_n}$ , equation (12) can be expressed as:

$$N_{it} = \frac{\left(C_{ox}\left(V_L - V_{fb}\right)\right) EXP\left(-\frac{t_h}{\tau_W}\right)}{q}$$

(16)

Therefore using (14), (15) and (16), the CP current given by (10) can be expressed as:

$$I_{CP\_Mod} = -\alpha + \alpha EXP\left(\frac{W}{\lambda}\right) \tag{15}$$

This equation is used by Wang et al [8] to fit their experimental CP data, where the empirical parameter  $\lambda$  and  $\alpha$  are not physically explained, but in this work they are well established and given by (13) and (14), respectively.

# V. CONCLUSION

Based in our understanding of the physical mechanisms behind the geometric component in charge pumping of polycrystalline thin film transistors, we have proposed an analytic model for this component. The developed model seems to be in good agreement with the experimental data and can capture all the experimental behaviours reported in the literature for polycrystalline thin film transistor, In addition, based on this geometric component model developed in this work, we have fixed the parameters of CP empirical equation previously reported elsewhere. Thus a new expression of CP current with geometric current is established.

## ACKNOWLEDGMENTS

The authors would like to thank Prof Mingxiang Wang and Jiajia Wang for providing the experimental CP of poly-Si TFT data used in this work.

#### VI. REFERENCE

- J. S. Brugler and P. G. A. Jespers, "Charge pumping in MOS devices," IEEE Trans. Electron Devices, vol. ED-16, no. 3, pp. 297–302, Mar. 1969;

- [2] G. Groeseneken, H. E. Maes, N. Beltran, and R. F. DeKeersmaecker, "Areliable approach to charge-pumping measurements in MOS transistors," IEEE Trans. Electron Devices, vol. ED-31, no. 1, pp. 42– 53, Jan. 1984.

- [3] G. Van den Bosch, G. Groeseneken, H.E. Maes, "On the geometric component of charge-pumping current in MOSFETs," IEEE Electron Device Letters, vol. 14 no.3, pp-107-109, Mar.1993

- [4] H.Tahi, B.Djezzar, A.Benabdelmoumene, A.Chenouf, M.Goudjil, "Inves tigation of interface, shallow and deep oxide traps under NBTI stress using charge pumping technique," Microelectron.Reliab. vol 54, no.5, pp.882–888, May. 2014.

- [5] E.Persidis, H. Baur, F. Pieralisi, P. Schalberger, N. Fruehauf, "Area laser crystallizedLTPS TFTs with implanted contacts for active matrix OLED displays," Solid-State Electronics, Vol.52, no.3, pp.455-461, March 2008.

- [6] W. Benzarti, F. Plais, A. De Luca, D. Pribat, "Compact analytical physical-based model of LTPS TFTfor active matrix displays addressing circuits simulation and design," IEEE Trans. Electron Devices, vol. 51, no. 3, pp.345-350, Mar.2004

- [7] L. Lu, M. Wang et M. Wong "Geometric Effect Elimination and Reliable Trap State Density Extraction in Charge Pumping of Polysilicon Thin-Film Transistors," *IEEE Trans. Electron Devices*, vol. 30, no. 5, pp.517-519, May. 2009.

- [8] Jiajia Wang, Mingxiang Wang, "Separation of the Geometric Current in Charge Pumping Measurement of Polycrystalline Si Thin-Film Transistors," *IEEE Trans. Electron Devices*, vol. 61, no. 12, pp. 4113-4119, Dec.2014

- [9] H. Tahi, B. Djezzar, A. Benabdelmoumen, B. Nadji, and Y. Kribes, "Geometric Component in Constant-Amplitude Charge-Pumping Characteristics of LOCOS- and LDD-MOSFET Devices," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 1, pp. 131–140, Murch. 2011.

- [10] H. Tahi, B. Djezzar, A. Benabdelmoumene "A new procedure for eliminating the geometric component from charge pumping: Application for NBTI and radiation issues," vol.53, no. 4, , pp.513–519, April. 2013