### République Algérienne Démocratique et Populaire Ministère de L'enseignement Supérieur et de la Recherche Scientifique

### Université M'Hamed Bougara Boumerdes Faculté de Technologie

Département Ingénierie des Systèmes Electriques

### Polycopié de Cours

# Electronique des Impulsions

Aux étudiants Licence 3<sup>ème</sup> Année Electronique

Réalisé par :

### Dr. HARRAR Khaled

Maitre de conférences A à l'université de Boumerdes

# Table des matières

| Liste des figures et tableaux                                                    | V  |

|----------------------------------------------------------------------------------|----|

| Introduction générale                                                            | 1  |

| Chapitre 1 : Définitions et caractéristiques de l'impulsion                      |    |

| 1.1 Introduction                                                                 | 3  |

|                                                                                  |    |

| 1.2 Types de signaux en électronique                                             | 3  |

| 1.3 Définitions                                                                  | 5  |

| 1.4 Signal carré ou rectangulaire                                                | 6  |

| 1.4.1 Signal positif                                                             | 6  |

| 1.4.2 Signal positif et négatif                                                  | 7  |

| 1.4.3 Signal positif oscillant entre deux valeurs E1 et E2                       | 7  |

| 1.4.4 Signal négatif                                                             | 7  |

| 1.5 Caractéristiques de l'impulsion                                              | 8  |

| Chapitre 2 : Circuit RC en commutation                                           |    |

| 2.1 Charge d'un condensateur                                                     | 11 |

| 2.2 Décharge d'un condensateur                                                   | 14 |

| 2.3 Graphe universel                                                             | 16 |

| 2.4 Expression générale de l'équation de charge ou de décharge d'un condensateur | 19 |

| 2.5 Tensions particulières                                                       | 19 |

| 2.6 Formes des tensions d'un circuit RC                                          | 21 |

| <u>Chapitre 3 :</u> Composants actifs en commutation                             |    |

| 3.1 Diode en commutation                                                         | 23 |

| 3.1.1 Polarisation directe                                                       | 24 |

| 3.1.2 Polarisation inverse                                                       | 25 |

| 3.1.3 Schémas équivalents de la diode                                            | 25 |

| 3.1.3.1 Caractéristique parfaite : approximation 1                               | 25 |

| 3.1.3.2 Caractéristique idéalisée : approximation 2     | 26 |

|---------------------------------------------------------|----|

| 3.1.3.3 Caractéristique linéarisée : approximation 3    | 26 |

| 3.2 Transistor en commutation                           | 27 |

| 3.2.1 Mode bloqué                                       | 29 |

| 3.2.2 Mode saturé                                       | 30 |

|                                                         |    |

| <u>Chapitre 4 :</u> Circuits de mise en forme           |    |

| 4.1 Introduction                                        | 33 |

| 4.2 Ecrêteur à diode simple                             | 33 |

| 4.2.1 Ecrêteur à diode en série                         | 33 |

| 4.2.2 Ecrêteur à diode en parallèle                     | 35 |

| 4.2.3 Ecrêteur à diode polarisée                        | 35 |

| 4.2.3.1 Ecrêteur à diode polarisée en série             | 35 |

| 4.2.3.2 Ecrêteur à diode polarisée en parallèle         | 36 |

| 4.2.4 Ecrêteur à deux diodes polarisées                 | 37 |

| 4.3 Ecrêteur à diode zener                              | 38 |

| 4.3.1 Caractéristique de la diode zener                 | 38 |

| 4.3.2 Ecrêteur à une diode zener                        | 39 |

| 4.3.3 Ecrêteur à deux diodes zener tête-bêche           | 40 |

| 4.4 Détecteur de crête                                  | 42 |

| 4.4.1 Détecteur de crête simple                         | 42 |

| 4.4.2 Détecteur de crête-à-crête                        | 43 |

| 4.5 Amplificateurs opérationnels en régime non linéaire | 44 |

| 4.5.1 Comparateur à un seuil                            | 44 |

| 4.5.1.1 Comparateur à un seuil non-inverseur            | 45 |

| 4.5.1.2 Comparateur à un seuil inverseur                | 46 |

| 4.5.2 Comparateur à hystérésis                          | 46 |

| 4.5.3 Trigger de Schmitt à amplificateur opérationnel   | 47 |

| 4.5.3.1 Trigger de Schmitt inverseur                    | 47 |

| 4.5.3.2 Trigger de Schmitt non-inverseur                | 49 |

| 4.5.3.3 Trigger de Schmitt à portes logiques            | 51 |

| 4.5.3.4 Trigger de Schmitt à base du Timer NE555        | 52 |

| <b>Chapit</b> | e 5:           | Les       | convertisseurs                 | analogiques       | numériques    | (CAN) | et |

|---------------|----------------|-----------|--------------------------------|-------------------|---------------|-------|----|

|               | n              | umério    | ques analogiques               | s (CNA)           |               |       |    |

| 5.1 Intr      | oductio        | on à la r | numérisation des s             | signaux           |               |       |    |

| 5.2 La c      | onvers         | ion ana   | alogique-numériq               | ue CAN            |               |       |    |

|               | .2.1 Pr        | rincipe   | du CAN                         |                   |               |       |    |

|               | 5.2.2 Ca       | aractér   | istiques d'un CAN              |                   |               |       |    |

|               | 5.2.3 Et       | ude de    | s exemples de CAN              | <b>1</b>          |               |       |    |

|               |                | 5.2.3.1   | Convertisseur à ir             | itégration simpl  | e rampe       |       |    |

|               | !              | 5.2.3.2   | Convertisseur à in             | itégration doubl  | e rampe       |       |    |

|               | ļ              | 5.2.3.3   | Convertisseur à a <sub>l</sub> | pproximations s   | uccessives    |       |    |

|               | ļ              | 5.2.3.4   | Convertisseur flas             | sh (en parallèle) |               |       |    |

|               | 5.2.4 Sp       | oécifica  | tions                          |                   |               |       |    |

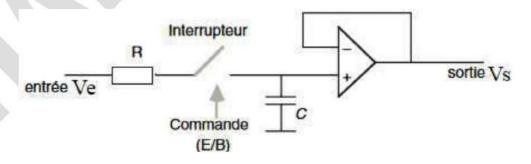

| 5.3 Circ      | uit éch        | antillo   | nneur-bloqueur                 |                   |               |       |    |

|               | 5.3.1 Pr       | incipe    | de fonctionnemer               | ıt                |               |       |    |

|               | 5.3.2 Cr       | itères (  | de sélection des ci            | rcuits échantillo | nneur-bloqueu | r     |    |

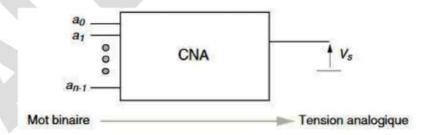

| 5.4 Con       | version        | numé      | rique analogique               | CNA               |               |       |    |

|               | 5.4.1 Pr       | incipe    | de CNA                         |                   |               |       |    |

| 1             | 5.4.2 Et       | ude de    | s exemples de CN               | A                 |               |       |    |

|               | Į              | 5.4.2.1   | Convertisseurs à r             | ésistances pond   | érées         |       |    |

|               |                | 5.4.2.2   | Convertisseurs à 1             | réseau R/2R       |               |       |    |

| 3             | 5.4.3 Sp       | oécifica  | tions                          |                   |               |       |    |

|               |                |           |                                |                   |               |       |    |

| <b>Chapit</b> | <u>e 6 :</u> C | ircuits   | à deux états : Le              | s multivibrate    | ırs           |       |    |

| 6.1 Intr      | oductio        | on        |                                |                   |               |       |    |

| 6.2 Circ      | uit bist       | table     |                                |                   |               |       |    |

|               | 5.2.1 Bi       | stable :  | à transistor                   |                   |               |       |    |

|               | 5.2.2 Bi       | stable    | à amplificateur op             | oérationnel       |               |       |    |

| 6.3 Mul       | ivibra         | teur as   | table                          |                   |               |       |    |

| 9)            | 5.3.1 As       | stable à  | transistors                    |                   |               |       |    |

|               | 5.3.2 As       | stable à  | amplificateur op               | érationnel        |               |       |    |

| 6.4 Mul       | ivibra         | teur mo   | onostable                      |                   |               |       |    |

| 9             | .4.1 M         | onosta    | ble à transistors              |                   |               |       |    |

| 6.4.2 Monostable à AOP                                           | 88  |

|------------------------------------------------------------------|-----|

| 6.4.3 Monostable à circuit intégré                               | 93  |

| 6.4.4 Monostable non redéclenchable                              | 95  |

| 6.4.5 Monostable redéclenchable                                  | 96  |

|                                                                  |     |

| <u>Chapitre 7 :</u> Les générateurs de fonctions                 |     |

| 7.1 Introduction                                                 | 98  |

| 7.2 Les générateurs de rampes                                    | 98  |

| 7.2.1 Générateur de courant constant                             | 98  |

| 7.2.2 Intégrateur de Miller                                      | 100 |

| 7.3 Principe de génération d'un signal en dents de scie          | 101 |

| 7.4 Principe de génération d'un signal triangulaire              | 102 |

| 7.5 Principe de la conversion Triangle-Sinus                     | 104 |

| 7.6 Générateurs de signaux avec des circuits intégrés            | 106 |

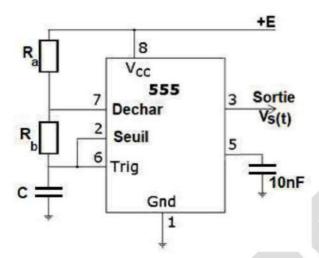

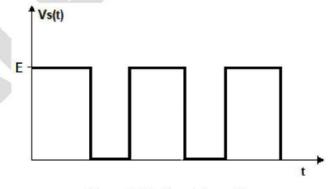

| 7.6.1 Génération de signaux carrés avec le Timer NE555           | 106 |

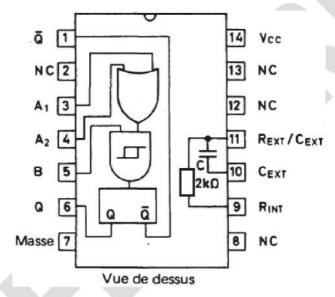

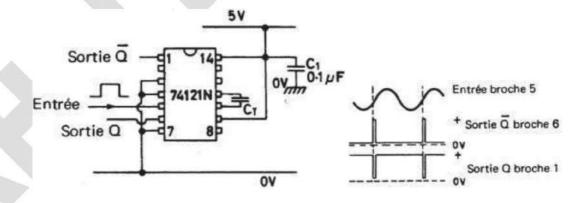

| 7.6.2 Génération d'impulsions avec le circuit intégré 71121N     | 108 |

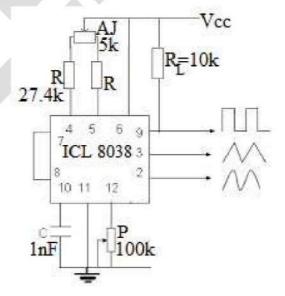

| 7.6.3 Générateurs multifonctions avec le circuit intégré ICL8038 | 110 |

| Références hibliographiques                                      | 111 |

## Liste des figures

| <u>Chapitre 1 :</u> Figure 1.1 : Types de signaux. (a) sinusoïdal, (b) carré ou rectangulaire, (c) triangulaire, |    |

|------------------------------------------------------------------------------------------------------------------|----|

| (d) dents de scie, et (e) impulsions                                                                             | 4  |

| Figure 1.2 : Valeurs caractéristiques d'un signal electrique                                                     | 6  |

| Figure 1.3 : Génération d'un signal strictement positif [0, E]                                                   | 6  |

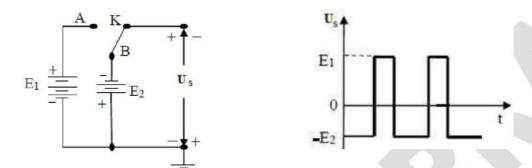

| Figure 1.4 : Génération d'un signal avec deux piles inversées                                                    | 7  |

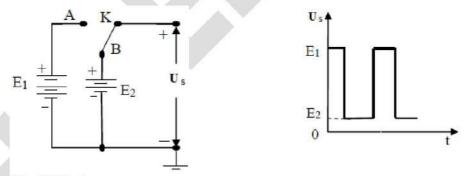

| Figure 1.5 : Génération d'un signal positif avec deux piles branchées dans le même sens                          | 7  |

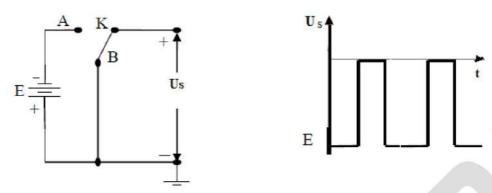

| Figure 1.6 : Génération d'un signal négatif avec une pile inversée                                               | 8  |

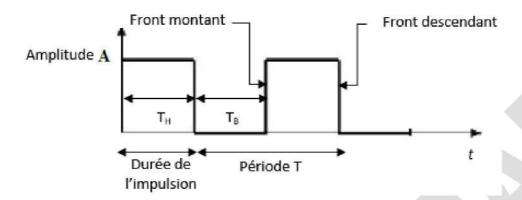

| Figure 1.7 : Paramètres décrivant une impulsion                                                                  | 9  |

| Figure 1.8 : Signal carré réel avec surexcitations et rebondissements                                            | 9  |

| Figure 1.9 : Caractéristiques temporelles d'une impulsion                                                        | 10 |

|                                                                                                                  |    |

| Chapitre 2:                                                                                                      |    |

| Figure 2.1 : Montage de charge d'un condensateur                                                                 | 11 |

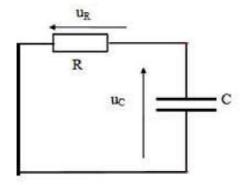

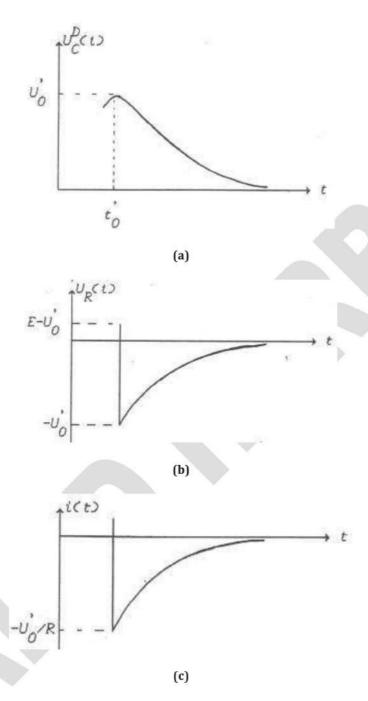

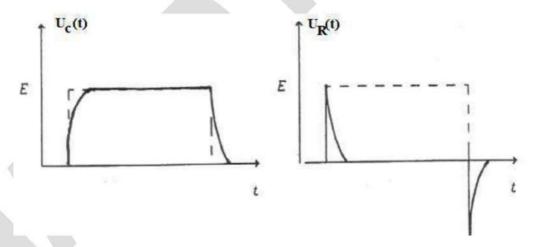

| Figure 2.2 : Courbes de variations de $Uc(t)$ , $U_R(t)$ , et $i(t)$ pendant la charge de C. (a)                 |    |

| courbe de charge de C, (b) courbe de tension aux bornes de R, et (c) courbe                                      |    |

| du courant lors de la charge                                                                                     | 14 |

| Figure 2.3 : Montage de décharge d'un condensateur                                                               | 14 |

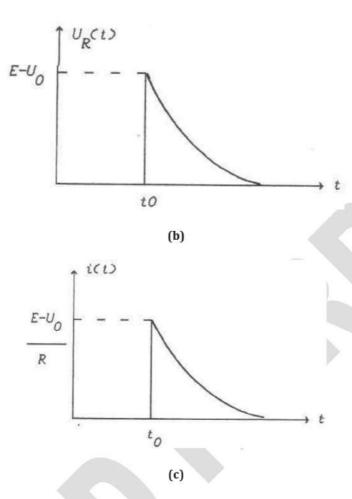

| Figure 2.4 : Courbes de variations de $Uc(t)$ , $U_R(t)$ , et $i(t)$ pendant la décharge de C, (a)               |    |

| courbe de décharge du condensateur, (b) courbe de tension aux bornes de                                          |    |

| R lors de la décharge, et (c) courbe du courant lors de la décharge                                              | 16 |

| Figure 2.5 : Graphes universels de $Uc(t)$ , $U_R(t)$ , pendant la charge de C, (a) graphe                       |    |

| universel de la charge, (b) graphe universel de la tension aux bornes de R                                       |    |

| lors de la charge                                                                                                | 18 |

| Figure 2.6 : Graphes universels de $Uc(t)$ , $U_R(t)$ , pendant la décharge de C, (a) graphe                     |    |

| universel de la décharge, (b) graphe universel de la tension aux bornes de                                       |    |

| R lors de la décharge                                                                                            | 19 |

| Figure 2.7 : Circuit RC avec tension d'entrée rectangulaire                                                      | 20 |

| Figure 2.8 : Constante de temps très faible $\tau << T$ . La forme et l'amplitude Uc(t) est                      |    |

| presque identique à celle de e(t)                                                                                | 21 |

| Figure 2.9 : Constante de temps et période identiques $\tau$ = $T$ . La charge de $C$ n'atteint                  |    |

| jamais la tension maximale d'entrée (E), et sa décharge n'atteint jamais la                                      |    |

| valeur inférieure de e(t)                                                                                        | 22 |

| Figure 2.10: Constante de temps très élevée $\tau >> T$ . La forme de Uc(t) devient                  |    |

|------------------------------------------------------------------------------------------------------|----|

| triangulaire et d'amplitude faible                                                                   | 22 |

| Figure 2.11 : Constante de temps infinie $\tau \to \infty$ . Le signal Uc(t) est une constante égale |    |

| à la moyenne de e(t)                                                                                 | 22 |

| Chapitre 3:                                                                                          |    |

| Figure 3.1 : Schéma d'une diode                                                                      | 23 |

| Figure 3.2 : Caractéristique de la diode                                                             | 24 |

| Figure 3.3 : Polarisation directe de la diode                                                        | 24 |

| Figure 3.4 : Polarisation inverse de la diode                                                        | 25 |

| Figure 3.5 : Caractéristique parfaite de la diode                                                    | 26 |

| Figure 3.6 : Schéma équivalent et caractéristique d'une diode idéalisée                              | 26 |

| Figure 3.7 : Caractéristique d'une diode linéarisée                                                  | 27 |

| Figure 3.8 : Schéma équivalent d'une diode linéarisée en polarisation directe                        | 27 |

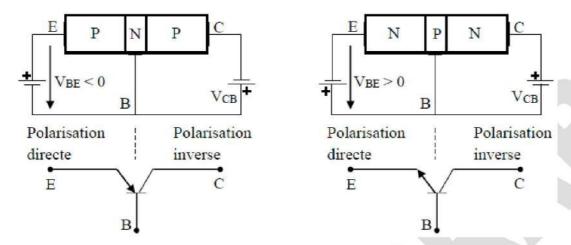

| Figure 3.9 : Transistor PNP et NPN                                                                   | 28 |

| Figure 3.10 : Schéma équivalent d'un transistor en commutation                                       | 28 |

| Figure 3.11 : Caractéristiques de sortie d'un transistor                                             | 29 |

| Figure 3.12 : Montage d'un transistor en régime bloqué                                               | 30 |

| Figure 3.13 : Schéma équivalent d'un transistor en régime de blocage                                 | 30 |

| Figure 3.14 : Montage d'un transistor en régime saturé                                               | 31 |

| Figure 3.15 : Droite de charge d'un transistor en commutation. Point A (régime saturé),              |    |

| et point B (régime bloqué)                                                                           | 31 |

| Figure 3.16 : Schéma équivalent d'un transistor en régime de saturation                              | 32 |

| Chapitre 4 :                                                                                         |    |

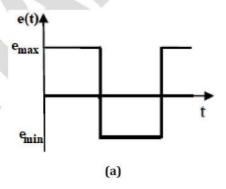

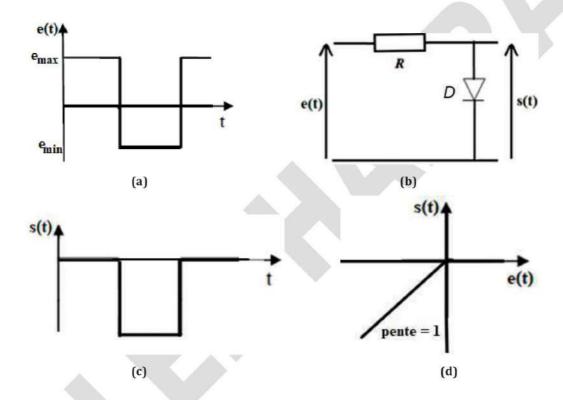

| Figure 4.1 : Ecrêteur à diode en série inférieur à zéro. (a) signal d'entrée, (b) circuit            |    |

| écrêteur, (c) signal de sortie, (d) caractéristique de transfert                                     | 34 |

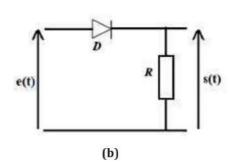

| Figure 4.2 : Ecrêteur à diode en série supérieur à zéro. (a) signal d'entrée, (b) circuit            |    |

| écrêteur, (c) signal de sortie, (d) caractéristique de transfert                                     | 34 |

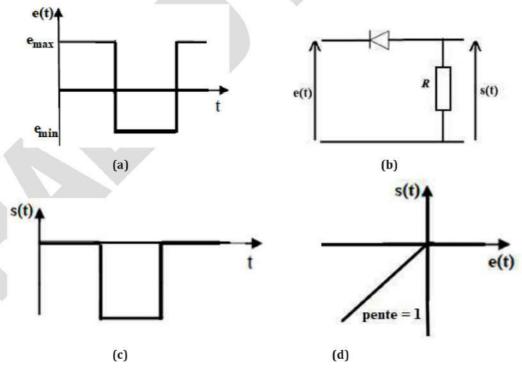

| Figure 4.3 : Ecrêteur à diode parallèle. (a) signal d'entrée, (b) circuit écrêteur, (c) signal       |    |

| de sortie, (d) caractéristique de transfert                                                          | 35 |

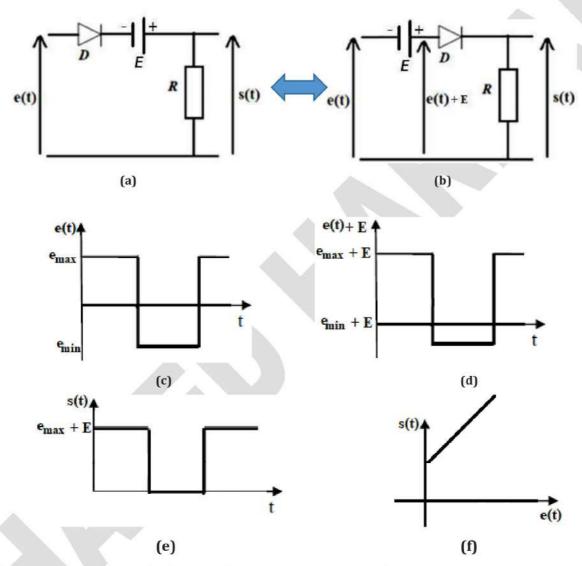

| Figure 4.4 : Ecrêteur à diode polarisée en série. (a) circuit type, (b) équivalent du circuit,       |    |

| (c) signal d'entrée, (d) signal d'entrée de la diode, (e) la sortie, (f)                             |    |

| caractéristique de transfert                                                                         | 36 |

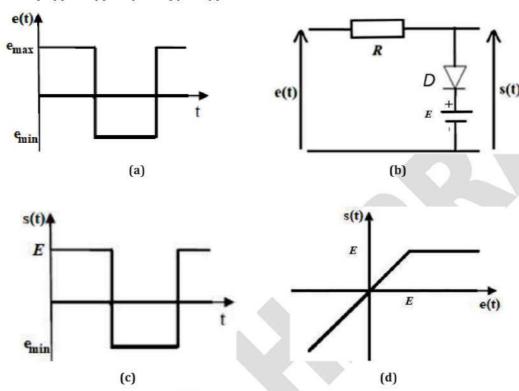

| Figure 4.5 : Ecrêteur à diode polarisée parallèle. (a) signal d'entrée, (b) circuit écrêteur, |    |

|-----------------------------------------------------------------------------------------------|----|

| (c) signal de sortie, (d) caractéristique de transfert                                        | 37 |

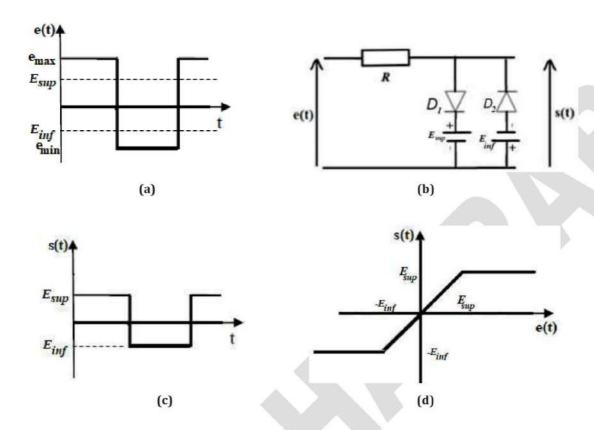

| Figure 4.6 : Ecrêteur à 2 diodes polarisées. (a) signal d'entrée, (b) circuit écrêteur, (c)   |    |

| signal de sortie, (d) caractéristique de transfert                                            | 38 |

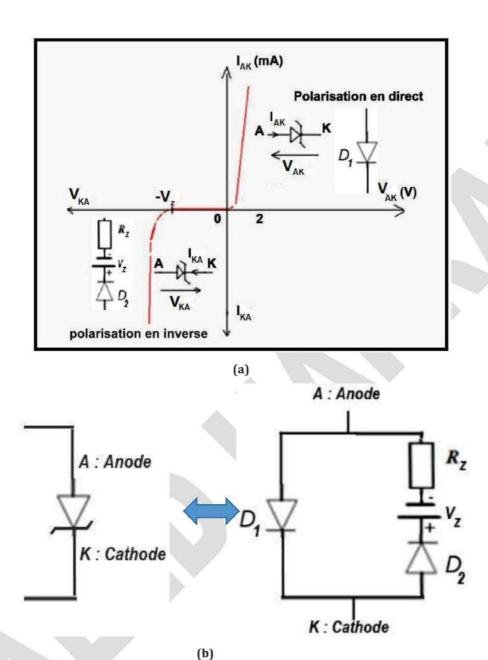

| Figure 4.7 : Diode zener. (a) Caractéristique, (b) schéma équivalent                          | 39 |

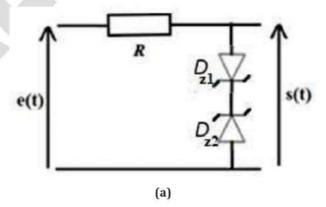

| Figure 4.8 : Ecrêteur à une diode zener. (a) circuit, (b) circuit équivalent, (c) signal de   |    |

| sortie                                                                                        | 40 |

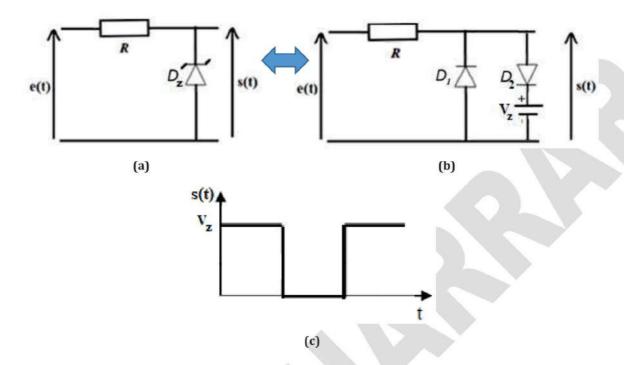

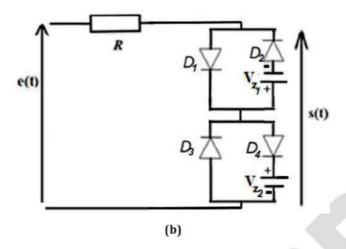

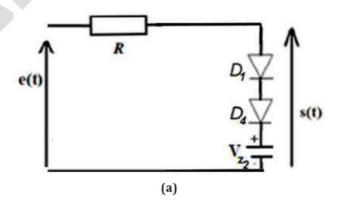

| Figure 4.9 : Ecrêteur à 2 diodes zener. (a) circuit, (b) circuit équivalent                   | 41 |

| Figure 4.10 : Schémas équivalents du circuit selon les alternances du signal d'entrée. (a)    |    |

| pour $e(t) > 0$ , (b) pour $e(t) < 0$ , (c) sortie $s(t)$                                     | 42 |

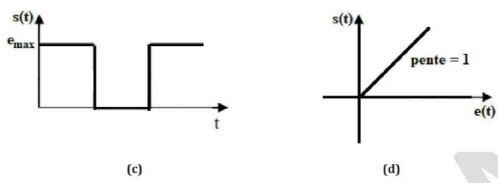

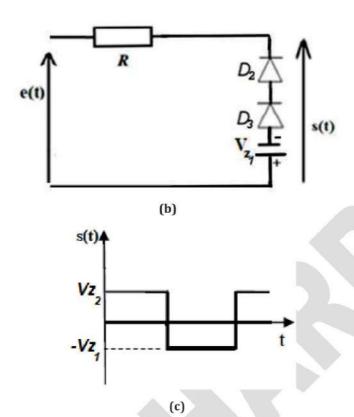

| Figure 4.11 : Détecteur de crête. (a) signal d'entrée e(t), (b) circuit détecteur, (c) sortie |    |

| s(t)                                                                                          | 43 |

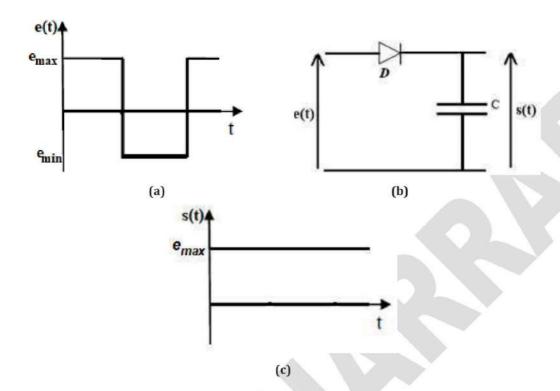

| Figure 4.12 : Détecteur de crête-à-crête (doubleur de tension)                                | 44 |

| Figure 4.13 : Schéma d'un amplificateur opérationnel                                          | 44 |

| Figure 4.14 : Schéma d'un comparateur non-inverseur. (a) circuit, (b) caractéristique de      |    |

| transfert, (c) chronogrammes d'entrée et de sortie                                            | 45 |

| Figure 4.15 : Schéma d'un comparateur inverseur. (a) circuit, (b) caractéristique de          |    |

| transfert, (c) chronogrammes d'entrée et de sortie                                            | 46 |

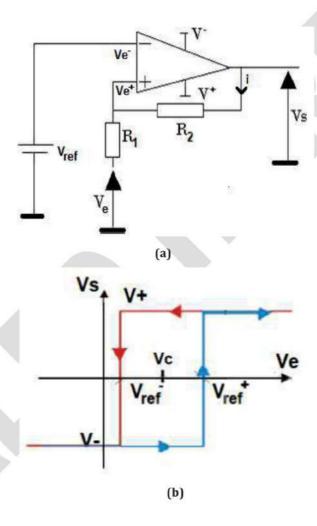

| Figure 4.16 : Trigger de Schmitt inverseur. (a) circuit à AOP, (b) Caractéristique de         |    |

| transfert                                                                                     | 47 |

| Figure 4.17 : Trigger de Schmitt non-inverseur. (a) circuit à AOP, (b) Caractéristique de     |    |

| transfert                                                                                     | 49 |

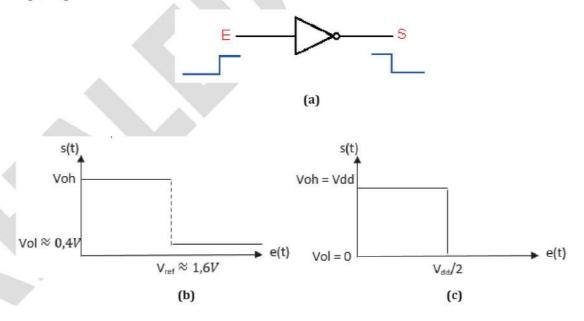

| Figure 4.18: Caractéristiques des portes logiques. (a) porte inverseuse, (b)                  |    |

| caractéristique de transfert pour porte TTL, et (c) pour CMOS                                 | 51 |

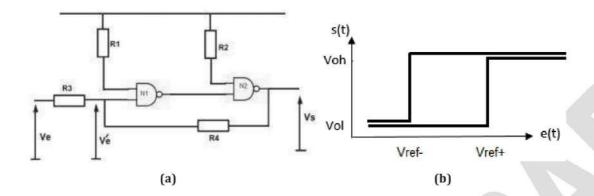

| Figure 4.19 : Trigger de Schmitt à portes logiques. (a) circuit, (b) caractéristique de       |    |

| transfert                                                                                     | 52 |

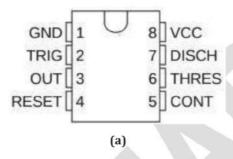

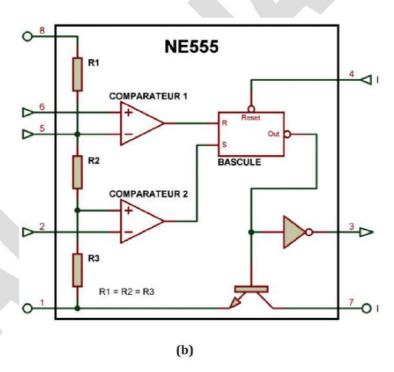

| Figure 4.20 : Timer NE555. (a) Brochage, (b) schéma synoptique fonctionnel                    | 53 |

| Figure 4.21: Montage trigger de Schmitt à base du NE555. (a) le circuit, (b)                  |    |

| caractéristique de transfert                                                                  | 54 |

| Chapitre 5 :                                                                                  |    |

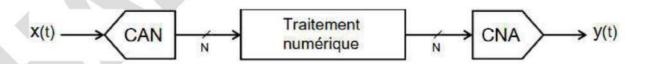

| Figure 5.1 : Conversion de CAN et CNA                                                         | 56 |

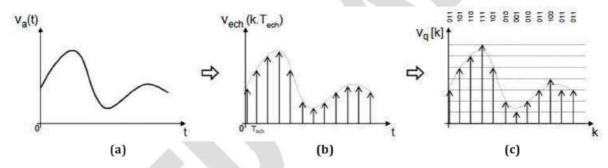

| Figure 5.2 : Etapes de CAN                                                                    | 57 |

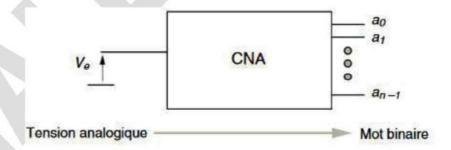

| Figure 5.3 : Schéma d'un CAN                                                                  | 57 |

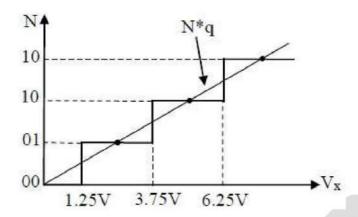

| Figure 5.4 : Caracteristique de transfert d'un CAN                                       | 58 |

|------------------------------------------------------------------------------------------|----|

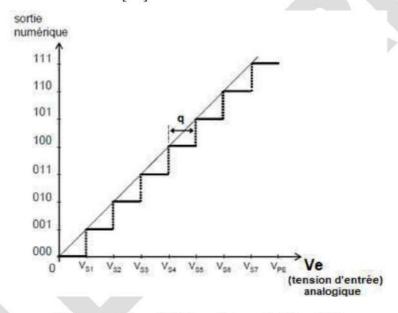

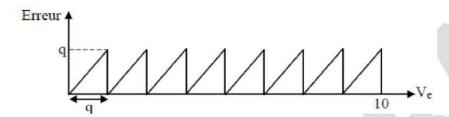

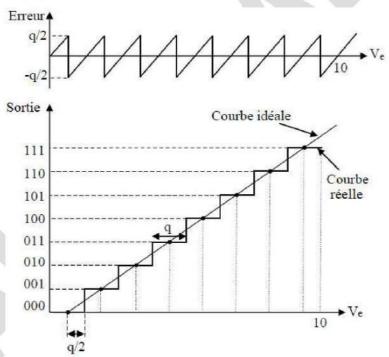

| Figure 5.5 : Exemple de l'erreur de quantification pour n égale à 3 bits                 | 59 |

| Figure 5.6 : Diminution de l'erreur                                                      | 59 |

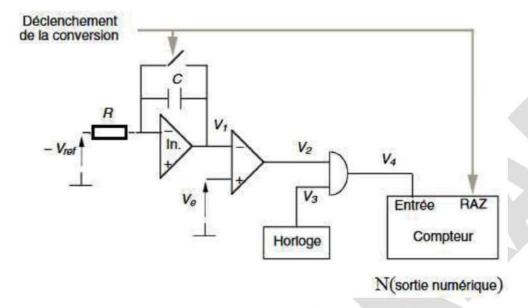

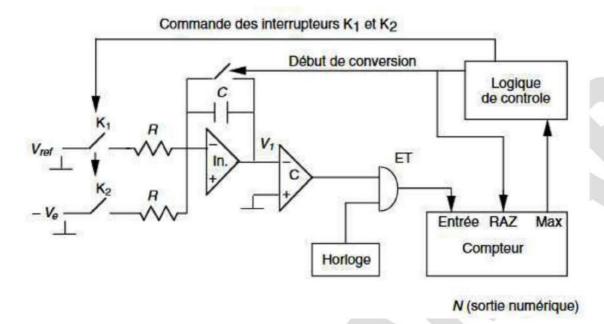

| Figure 5.7 : CAN à intégration simple rampe                                              | 60 |

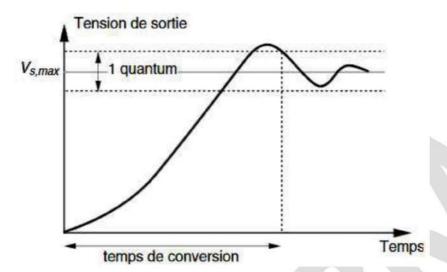

| Figure 5.8 : Diagramme des temps                                                         | 61 |

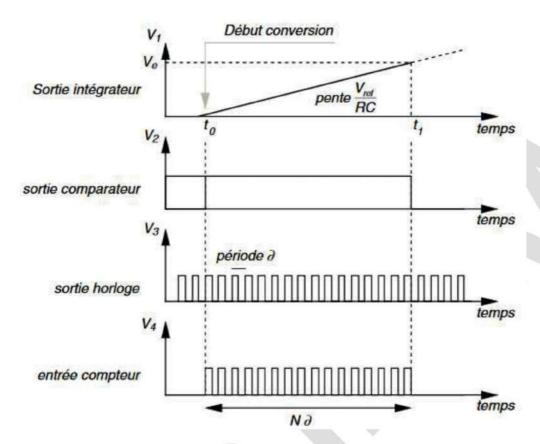

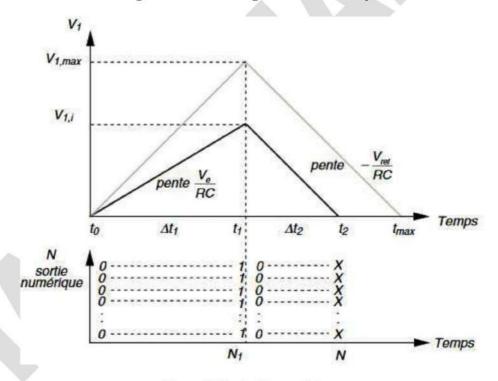

| Figure 5.9 : CAN à intégration double rampe                                              | 62 |

| Figure 5.10 : Sortie numérique                                                           | 62 |

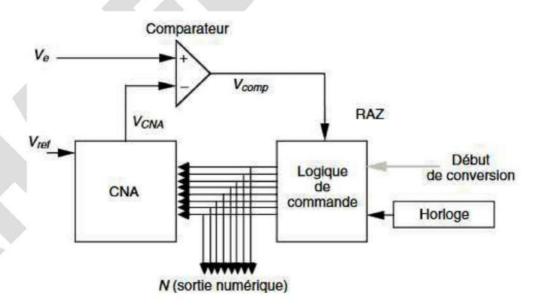

| Figure 5.11 : CAN à approximations successives                                           | 63 |

| Figure 5.12 : Diagramme des temps d'un CAN à approximations successives                  | 64 |

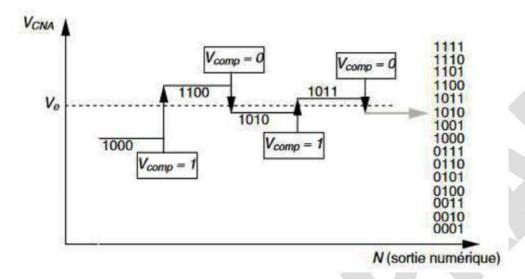

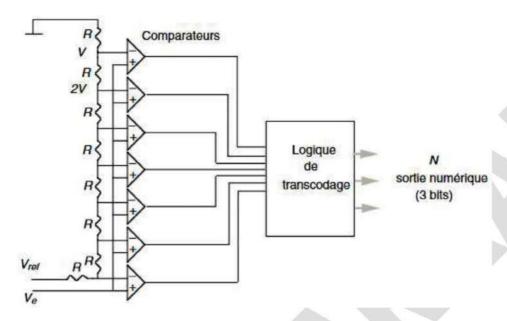

| Figure 5.13 : Schéma d'un convertisseur flash                                            | 65 |

| Figure 5.14 : Convertisseur flash à 2 bits                                               | 65 |

| Figure 5.15 : Allure d'un CAN flash à 2 bits                                             | 66 |

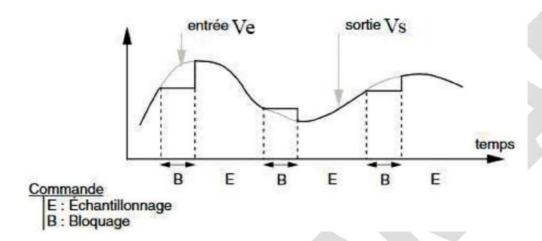

| Figure 5.16 : Représentation de l'échantillonnage et le blocage de la tension d'entrée   | 67 |

| Figure 5.17 : Principe d'un échantillonneur-bloqueur                                     | 67 |

| Figure 5.18 : Schéma fonctionnel d'un CNA                                                | 68 |

| Figure 5.19 : Courbe de transfert d'un CNA                                               | 69 |

| Figure 5.20 : Convertisseur CNA à résistances pondérées                                  | 70 |

| Figure 5.21 : CNA à réseau en échelleR-2R                                                | 71 |

| Figure 5.22 : Principe du calcul de Vs pour le CNA. (a) calcul pour la première cellule, |    |

| (b) calcul cumulé                                                                        | 71 |

| Figure 5.23 : Temps de conversion d'un CNA                                               | 73 |

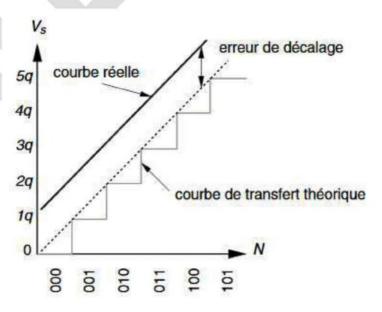

| Figure 5.24 : Erreur de décalage                                                         | 73 |

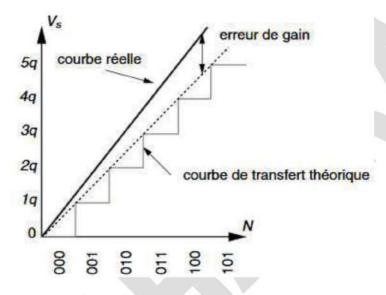

| Figure 5,25 : Erreur de gain                                                             | 74 |

| Chapitre 6 :                                                                             |    |

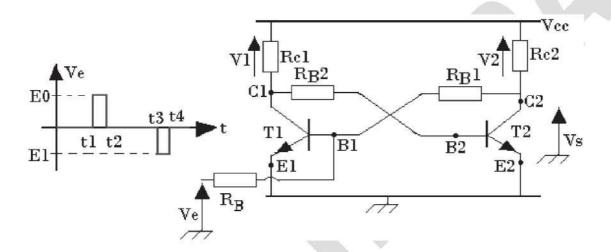

| Figure 6.1 : Circuit bistable à transistor                                               | 76 |

| Figure 6.2 : Chronogrammes de l'entrée et de la sortie du circuit bistable à transistor  | 77 |

| Figure 6.3 : Circuit bistable à AOP                                                      | 77 |

| Figure 6.4 : Chronogrammes de l'entrée et de la sortie du circuit bistable à AOP         | 79 |

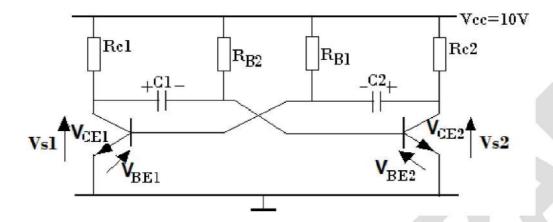

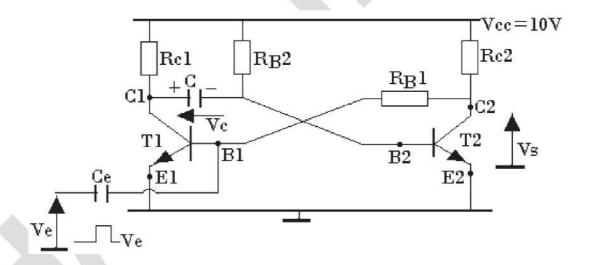

| Figure 6.5 : Astable à transistors                                                       | 80 |

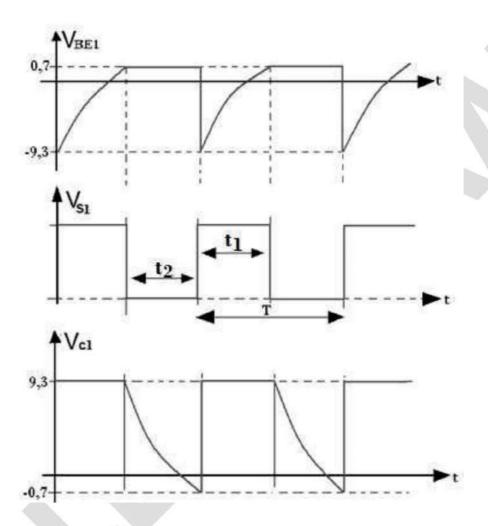

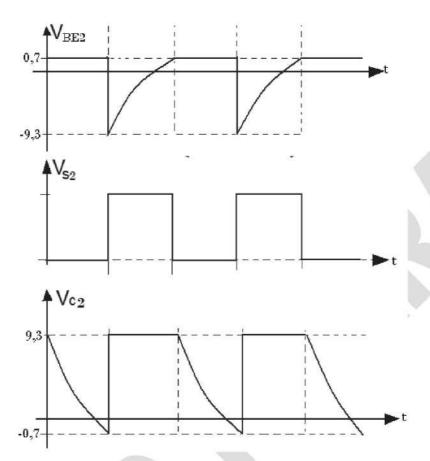

| Figure 6.6 : Signaux générés par le transistor 1                                         | 81 |

| Figure 6.7 : Signaux générés par le transistor 2                                         | 82 |

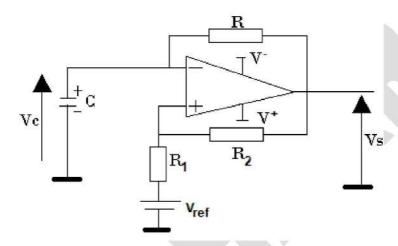

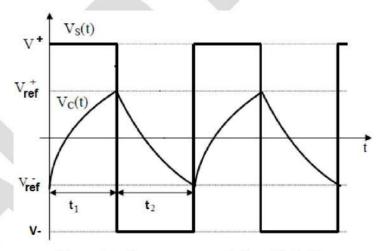

| Figure 6.8 : Montage astable à AOP                                                       | 83 |

| Figure 6.9 : Chronogrammes de l'astable à AOP                                            | 83 |

| Figure 6.10 : Monostable à transistors                                                       | 86  |

|----------------------------------------------------------------------------------------------|-----|

| Figure 6.11 : Chronogrammes du monostable à transistors                                      | 87  |

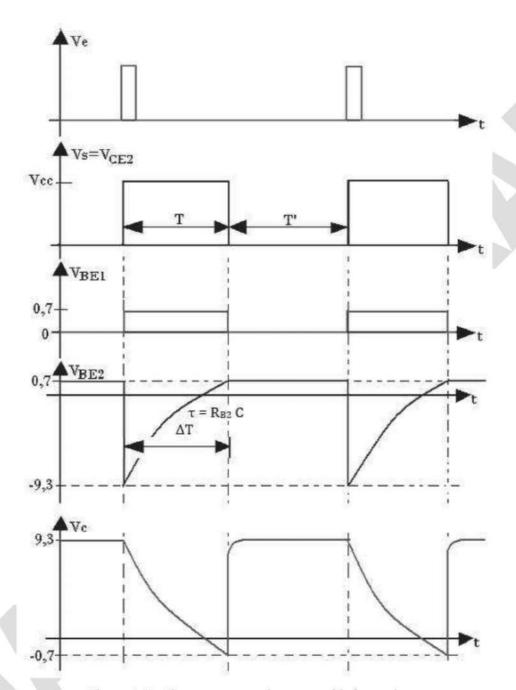

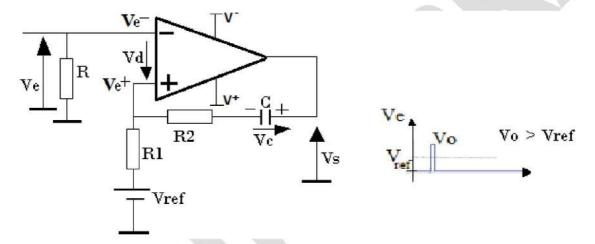

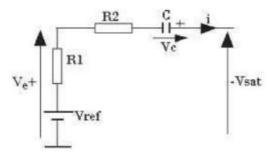

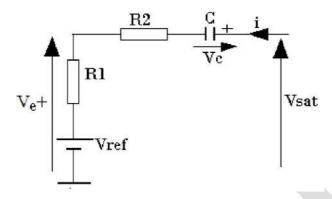

| Figure 6.12 : Montage monostable à AOP                                                       | 88  |

| Figure 6.13 : Chronogrammes du monostable à AOP                                              | 91  |

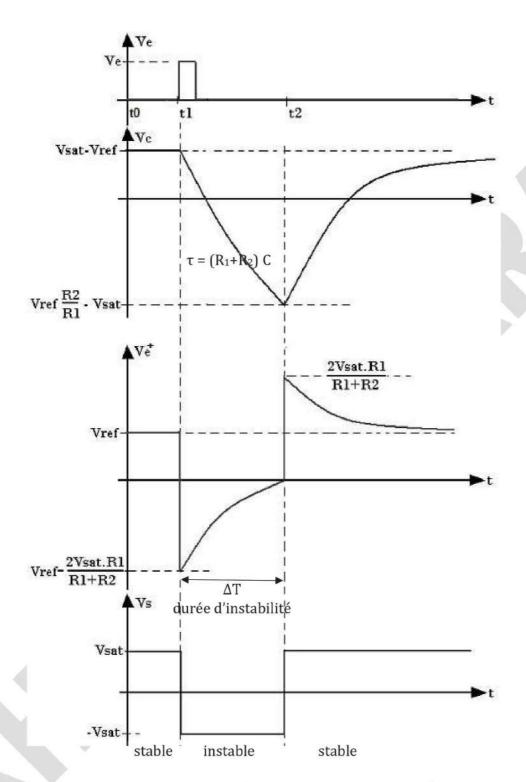

| Figure 6.14 : Circuit monostable à base du timer NE555                                       | 93  |

| Figure 6.15 : diagrammes de temps du monostable à timer NE555                                | 94  |

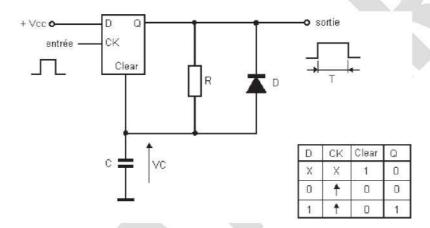

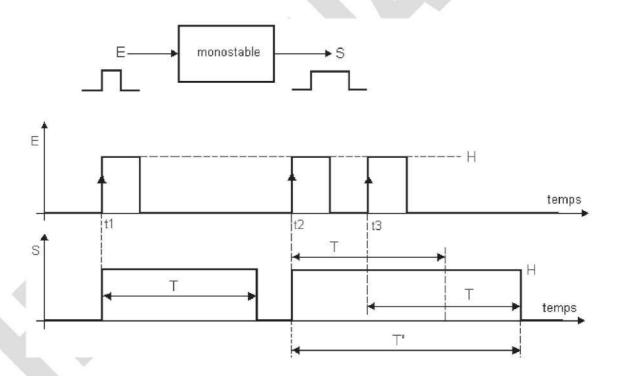

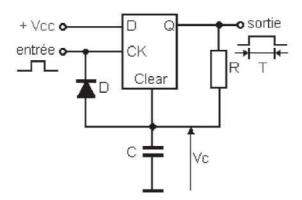

| Figure 6.16 : Monostable non redéclenchable                                                  | 95  |

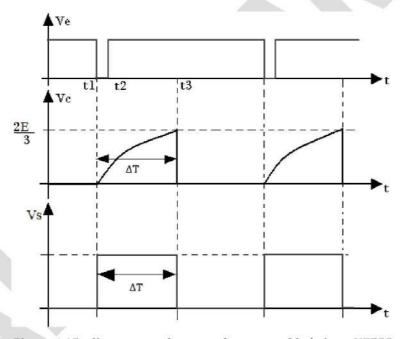

| Figure 6.17 : Chronogrammes du monostable non redeclenchable                                 | 95  |

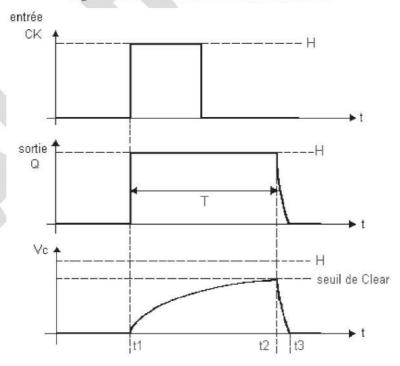

| Figure 6.18 : Chronogrammes du monostable redeclenchable                                     | 96  |

| Figure 6.19 : Monostable redéclenchable                                                      | 97  |

|                                                                                              |     |

| Chapitre 7 :                                                                                 |     |

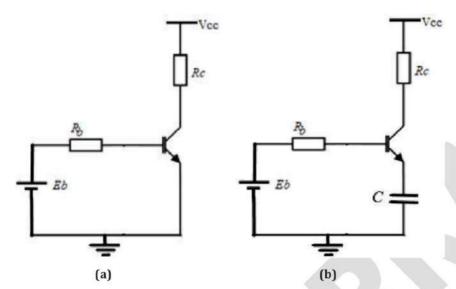

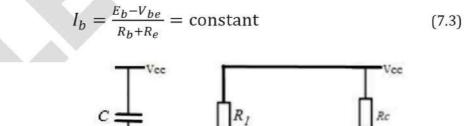

| Figure 7.1 : Charge à courant constant. (a) sans condensateur, (b) avec condensateur         | 99  |

| Figure 7.2 : Générateur de courant constant. (a) sans condensateur, (b) avec                 |     |

| condensateur                                                                                 | 99  |

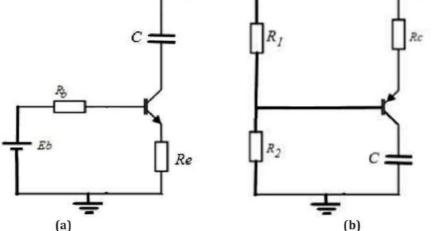

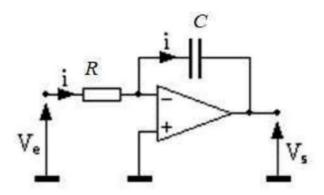

| Figure 7.3 : Intégrateur de Miller                                                           | 101 |

| Figure 7.4 : Principe de la génération d'un signal en dents de scie                          | 102 |

| Figure 7.5 : Chronogrammes de Vc(t)                                                          | 102 |

| Figure 7.6 : Montage intégrateur                                                             | 102 |

| Figure 7.7 : Signal triangulaire généré par l'intégrateur                                    | 104 |

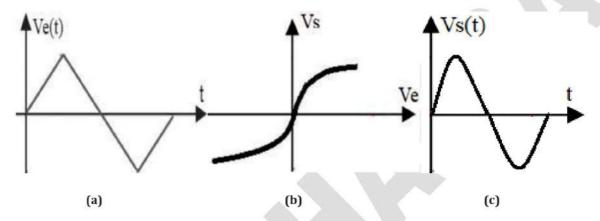

| Figure 7.8 : Principe de la conversion triangle-sinus. (a) Signal triangulaire, (b) fonction |     |

| de transfert, (c) signal sinusoïdal                                                          | 105 |

| Figure 7.9 : Schéma de la conversion triangle-sinus. (a) Montage, (b) passage du signal      |     |

| triangulaire au signal sinusoïdal                                                            | 106 |

| Figure 7.10 : Le timer NE555. (a) Brochage, (b) schéma synoptique fonctionnel                | 107 |

| Figure 7.11 : Montage à base du timer NE555 pour la génération de signal rectangulaire       | 108 |

| Figure 7.12 : Signal de sortie                                                               | 108 |

| Figure 7.13 : Circuit intégré 74121N brochage et architecture interne                        | 109 |

| Figure 7.14 : Générateur d'impulsions 30ns                                                   | 109 |

| Figure 7.15 : Montage du générateur multifonction intégré ICL 8038                           | 110 |

## Liste des tableaux

| Chapitre 2 :                                                      |    |

|-------------------------------------------------------------------|----|

| Tableau 2.1 : Valeurs de charge et de décharge                    | 17 |

| Chapitre 3:                                                       |    |

| Tableau 3.1 : Régimes de fonctionnement d'un transistor bipolaire | 29 |

| Chapitre 4 :                                                      |    |

| Tableau 4.1 : Table de vérité d'une bascule RS                    | 54 |

| Chapitre 5 :                                                      |    |

| Tableau 5.1 : Exemple de CAN à 3 bits                             | 64 |

# Introduction générale

Le développement des performances des circuits électroniques, a abouti à un essor considérable des techniques de traitement des signaux numériques. Ces techniques de traitement utilisent comme support de l'information des signaux modélisables sous forme d'impulsions. L'avènement des signaux impulsionnels a suscité la communauté scientifique à développer un sous-domaine de l'électronique, appelé « Electronique des impulsions ».

Le présent polycopié s'adresse aux étudiants de Licence 3ème année en Electronique. Le contenu est en adéquation avec le programme national du module « électronique des impulsions » arrêté par le ministère. Ce document constitue un renforcement des connaissances dans le domaine de l'électronique. Ce cours s'articule principalement sur la commutation. Il a pour objectif de donner à l'étudiant une compréhension des principes de base de l'électronique impulsionnelle, à travers différents types de circuits (circuits actifs en commutation, circuits de mise en formes, générateurs de signaux, etc.).

Pour que l'étudiant puisse comprendre et suivre ce cours, des connaissances préalables sont indispensables, à savoir, l'électronique fondamentale 1 et 2, et les fonctions de l'électronique. A l'issue de ce cours, l'étudiant acquerra les compétences nécessaires pour la génération de n'importe quel signal impulsionnel. En outre, il conféra à l'étudiant la capacité d'analyse du fonctionnement d'un système électronique analogique aussi complexe soit-il.

Ce cours est divisé en sept chapitres :

Chapitre 1. Définitions et caractéristiques de l'impulsion : Ce chapitre introduit les différents types de signaux, ainsi que les caractéristiques de l'impulsion (amplitude, période, rapport cyclique, temps caractéristiques, etc.).

**Chapitre 2. Circuit RC en commutation :** Dans ce chapitre, la charge et la décharge d'un condensateur est traitée en détail. L'expression générale de la charge et de la décharge est décrite ainsi que les formes des tensions d'un circuit RC.

**Chapitre 3. Composants actifs en commutation :** Ce chapitre traite la diode et le transistor en commutation. Le mode blocage et le mode saturation sont présentés, ainsi que le schéma équivalent du transistor en commutation.

**Chapitre 4. Circuits de mise en forme :** Les montages écrêteurs et détecteurs de crêtes à base de diodes sont présentés dans ce chapitre. Les amplificateurs opérationnels en régime non linéaire sont abordés.

Chapitre 5. Les convertisseurs analogiques numériques (CAN) et numériques analogiques (CNA): Dans ce chapitre la conversion analogique numérique (CAN), et numérique analogique (CNA) sont détaillées. Plusieurs exemples de CAN sont décrits: convertisseur à intégration simple et double rampe, convertisseur à approximations successives, convertisseur flash, et circuit échantillonneur-bloqueur. Par ailleurs, des exemples sur la CNA sont exposés: les convertisseurs à résistances pondérées, et les convertisseurs à réseau R/2R.

Chapitre 6. Circuits à deux états - Les multivibrateurs : Ce chapitre est consacré aux multivibrateurs. Le circuit bistable, le circuit monostable, ainsi que le circuit astable sont présentés avec différents montages (à transistors et à ampli-op). Le circuit intégré monostable, les monostables redéclenchables et non redéclenchables sont aussi abordés.

Chapitre 7. Les générateurs de fonctions : Ce dernier chapitre traite les générateurs des différents signaux. Le principe de génération d'un signal en rampe, d'un signal en dents de scie, d'un signal triangulaire, et sinusoïdal sont présentés. Les générateurs de signaux en utilisant des circuits intégrés (NE555, SN74121, ICL8038, etc) sont exposés.

# Définitions et caractéristiques de l'impulsion

### 1.1 Introduction

Un signal analogique est une grandeur physique qui peut prendre des valeurs continues dans le temps. Une impulsion est un signal electrique qui apparait de manière brève.

### 1.2 Types de signaux en électronique

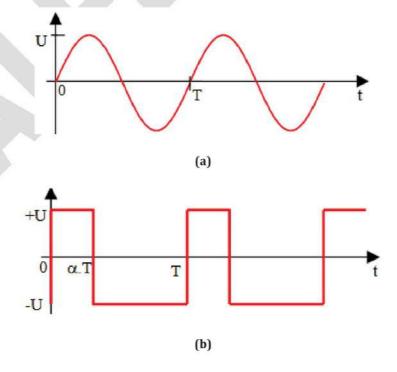

Un signal electrique peut prendre différentes formes [1]. La Figure 1.1 montre les types de signaux les plus connus.

Figure 1.1: Types de signaux. (a) sinusoïdal, (b) carré ou rectangulaire, (c) triangulaire, (d) dents de scie, et (e) impulsions

Tout signal variable dans le temps est appelé signal composite :

$$U(t) = Uc + U_A(t)$$

Tension composite Tension continue Tension alternative

Si Uc = 0, le Signal composite est un signal alternatif.

Un signal electrique est caractérisé par :

- Sa forme d'onde

- Son amplitude

- Sa période (ou sa fréquence)

### 1.3 Définitions

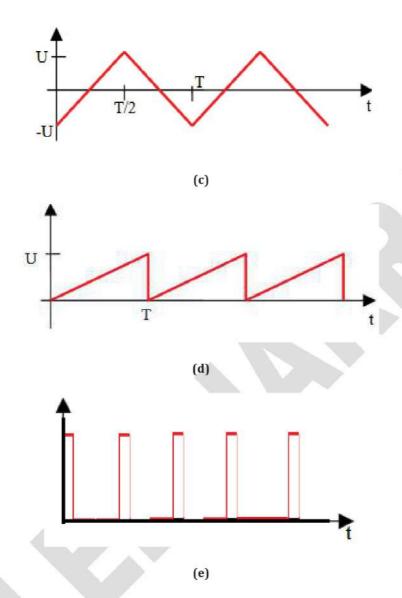

Plusieurs paramètres sont décrits dans un signal electrique, ils sont représentés dans la Figure 1.2. Dans ce qui suit les définitions de ces paramètres est abordée [2]:

a- Amplitude (A): Différence entre sa valeur maximale et sa valeur moyenne.

$$A = U_{\text{max}} - U_{\text{moy}} \tag{1.1}$$

- b- Crête: Valeur extrême d'un signal (positive ou négative).

- c- Période : Le temps que met un signal pour revenir à sa position de départ. Le temps durant lequel le signal se reproduit identique à lui-même.

- d- Signal alternatif: Signal dont l'amplitude varie en fonction du temps.

- e- Signal continu: Signal stable et constant dans le temps.

- f- Impulsion positive : brève tension positive qui apparait dans une courte période.

- g Impulsion négative : brève tension négative qui apparaît dans une courte période.

- h- Amplitude crête à crête (Acc) : Différence entre sa valeur maximale et sa valeur minimale.

$$A_{cc} = U_{max} - U_{min} \tag{1.2}$$

i- Valeur moyenne (Umoy):

$$U_{\text{moy}} = \frac{Surface \ algébrique \ du \ signal}{T} \tag{1.3}$$

$$U_{moy} = \frac{1}{T} \int_{0}^{T} U(t) dt$$

(1.4)

j- Valeur efficace (Ueff):

$$U_{eff}^{2} = \frac{1}{T} \int_{0}^{T} U^{2}(t) dt$$

(1.5)

Figure 1.2 : Valeurs caractéristiques d'un signal electrique

### 1.4 Signal carré ou rectangulaire

Les signaux carrés ou rectangulaires sont très utilisés en électronique particulièrement en électronique des impulsions [3].

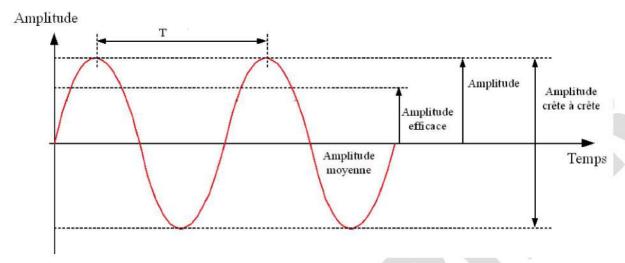

### 1.4.1 Signal positif

Ces signaux ont des valeurs uniquement positives.

Figure 1.3: Génération d'un signal strictement positif [0, E]

En fonction de la position de l'interrupteur K, on a (Figure 1.3):

Position A: Us = E

Position B: Us = 0

t₁ = t2 → Signal carré

$t_1 \neq t_2 \rightarrow Signal rectangulaire$

La tension de sortie prendra deux valeurs suivant la position de l'interrupteur K (0 ou E), et suivant les valeurs des demi-périodes, on génère un signal carré ou rectangulaire.

### 1.4.2 Signal positif et négatif

Ce type de signaux ont des valeurs positives et négatives.

Figure 1.4 : Génération d'un signal avec deux piles inversées

Si une pile inversée (tension continue négative) est insérée dans la branche B, le signal de sortie prendra des valeurs négatives. Us(t) oscillera entre -E2 et E1 (Figure 1.4).

### 1.4.3 Signal positif oscillant entre deux valeurs E1 et E2

Ce type de signaux ont des valeurs uniquement positives non nulles.

Figure 1.5 : Génération d'un signal positif avec deux piles branchées dans le même sens

Pour des tensions continues strictement positives E1 et E2, le signal de sortie Us(t) prendra que des tensions positives (Figure 1.5).

### 1.4.4 Signal négatif

Ce type de signaux ont des valeurs uniquement négatives.

Figure 1.6 : Génération d'un signal négatif avec une pile inversée

Dans le cas où la tension d'entrée E est négative, on aura un signal de sortie négatif (Figure 1.6).

D'après la figure 1.3 on a :

$T = t_1 + t_2$  (la période)

f = 1/T (la fréquence)

$t_1 = T_{ON} = temps de fermeture$

$t_2 = T_{OFF} = temps d'ouverture$

Si  $t_1 \rightarrow 0$  on aura un signal impulsionnel (train d'impulsions)

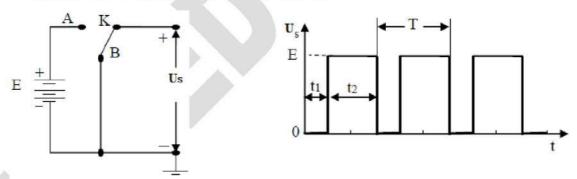

### 1.5 Caractéristiques de l'impulsion

Un signal impulsionnel rectangulaire est décrit avec plusieurs paramètres [1]:

- Amplitude de l'impulsion A

- Période T

- Durée de l'impulsion

- Temps haut (TH)

- Temps bas (T<sub>B</sub>)

Figure 1.7 : Paramètres décrivant une impulsion

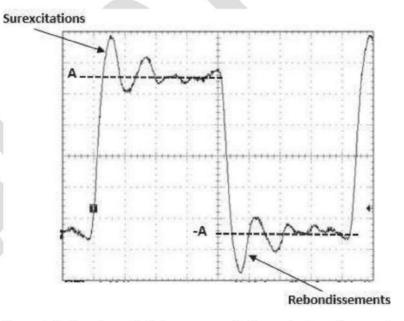

En pratique les signaux ne sont pas parfaits. Le passage d'un état à un autre n'est pas instantané. Lors de la montée nous constatons une surexcitation du signal qui dépasse légèrement la valeur maximale puis revient à cette valeur au régime permanant. De même lors de la descente, le signal ne se stabilise pas directement à sa valeur minimale. En effet il y a des rebondissements de ce signal qui se manifestent par un dépassement de la valeur minimal vers le bas et une remontée légère du signal. Ce phénomène tend à se stabiliser au régime permanant pour rester à sa valeur minimale (Figure 1.8).

Figure 1.8 : Signal carré réel avec surexcitations et rebondissements

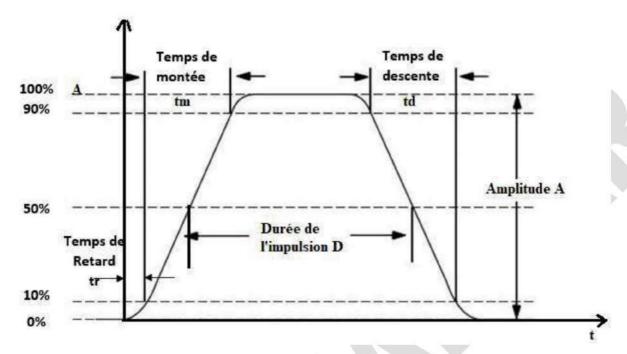

D'autres paramètres peuvent être décrits et estimés pour un signal electrique. Ces paramètres concernent la montée du signal et sa descente.

Figure 1.9 : Caractéristiques temporelles d'une impulsion

Temps de montée t<sub>m</sub> : Intervalle de passage de l'impulsion de 10% à 90% de la valeur maximale au front montant.

$$t_{\rm m} = t_{90\%} - t_{10\%}$$

(au front montant) (1.6)

Temps de descente t<sub>d</sub>: Intervalle de passage de l'impulsion de 90% à 10% de la valeur maximale au front descendant.

$$t_{\rm m} = t_{10\%} - t_{90\%} \text{ (au front descendant)} \tag{1.7}$$

Durée de l'impulsion D : Intervalle de temps pendant lequel l'impulsion dépasse 50% de la valeur maximale.

$$D = t_{50\%} \text{ (au front descendant)} - t_{50\%} \text{ (au front montant)}$$

(1.8)

- Temps de retard : C'est le temps que met l'impulsion pour arriver à 10% (tr =  $t_{10\%}$ ).

- Rapport cyclique R : Ce paramètres concerne essentiellement un signal carré ou rectangulaire. Il est décrit par le rapport entre le temps haut (TH) et sa période (T). Il prend ses valeurs dans l'intervalle [0,1] ou en pourcentage [0%, 100%]

$$R = \frac{D}{T} = \frac{T_H}{T} \tag{1.9}$$

## Circuit RC en commutation

### 2.1 Charge d'un condensateur

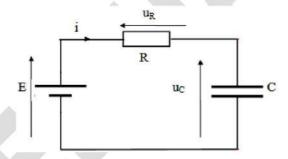

Soit le montage de la figure 2.1. Le condensateur C est alimenté par un générateur de tension E à travers une résistance R.

Figure 2.1: Montage de charge d'un condensateur

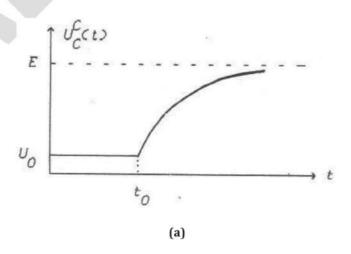

Le condensateur commence à se charger de sa valeur initiale U0 à travers R. U0 est la tension aux bornes de C avant le début de charge. Si le condensateur était initialement déchargé U0 = 0V [1].

On peut écrire:

$$E = U_c^c(t) + U_R(t) (2.1)$$

Telle que  $U_c^c$  la tension de charge du condensateur C.

$$U_R(t) = R \cdot i(t) \tag{2.2}$$

$$i_c = c \frac{dU_c}{dt} \tag{2.3}$$

$$E = \frac{1}{c} \int_{0}^{t} i(t) dt + R \cdot i(t)$$

(2.4)

$$E = Ri(t) + U_c^c (2.5)$$

$$E = RC\frac{dU_c^c}{dt} + U_c^c \tag{2.6}$$

Ceci est une équation différentielle du 1er ordre avec second membre.

La solution de l'équation est la somme de la solution de l'équation sans second membre et la solution particulière [1].

### 1) Solution sans second membre:

$$RC\frac{dU_c^c}{dt} + U_c^c = 0 (2.7)$$

$$\frac{dU_c^c}{dt} = -\frac{U_c^c}{RC} \tag{2.8}$$

$$\frac{dU_c^c}{U_c^c} = -\frac{1}{RC}dt\tag{2.9}$$

$$\int \frac{dU_c^c}{U_c^c} = -\frac{1}{RC} \int dt \tag{2.10}$$

$$\ln U_c^c = -\frac{1}{RC}t + K_1 \tag{2.11}$$

$$U_c^c = e^{-\left(-\frac{1}{RC}t + K_1\right)} (2.12)$$

$$= e^{K1} e^{-\frac{1}{RC}t} (2.13)$$

$$=K_2.e^{-\frac{t}{RC}} \tag{2.14}$$

### 2) Solution particulière:

La solution particulière :  $U_c^c = E$  (le condensateur aura atteint la tension maximale en fin de charge, régime permanent).

La solution de l'équation sera alors :

$$U_c^c = E + K_2 \cdot e^{-\frac{t}{RC}} (2.15)$$

### Recherche des constantes:

Conditions initiales :  $U_c^c(0) = Uo$  (tension au début de la charge). En remplaçant dans l'équation (1), on aura :

$$U0 = E + K2$$

(2.16)

$$K2 = U0-E$$

(2.17)

$$U_c^c(t) = E - (E - U_0) \cdot e^{-\frac{t}{RC}}$$

(2.18)

Si Uo = 0 (condensateur initialement déchargé):

$$U_c^c(t) = E(1 - e^{-\frac{t}{RC}})$$

(2.19)

Expression de la tension aux bornes de R. Selon la loi de maille on a :

$$E = Uc + U_R \tag{2.20}$$

$$U_R = E - Uc ag{2.21}$$

$$U_R(t) = (E - U_0) e^{-\frac{t}{RC}}$$

(2.22)

Les courbes des signaux aux bornes de C et de R sont illustrées dans la figure 2.2 [1].

Figure 2.2 : Courbes de variations de Uc(t),  $U_R(t)$ , et i(t) pendant la charge de C. (a) courbe de charge de C, (b) courbe de tension aux bornes de R, et (c) courbe du courant lors de la charge

### 2.2 Décharge d'un condensateur

Pour décharger le condensateur C, on met un court-circuit aux bornes du générateur E (E = 0V), ce qui donne le montage de la figure 2.3 [3].

Le condensateur se décharge à partir de sa valeur initiale à travers R.

Figure 2.3 : Montage de décharge d'un condensateur

L'équation de maille est :  $U_c^D(t) + U_R(t) = 0$ . Avec  $U_c^D$  la tension aux bornes de C lors de la décharge.

En suivant les mêmes étapes que lors de la charge, on aboutira à l'équation différentielle suivante [2] :

$$U_c^D(t) + RC\frac{dU_c}{dt} = 0 (2.23)$$

La solution de cette équation est la même que la solution sans second membre lors de l'étape de charge. Ce qui va donner la solution suivante :

$$U_c^D(t) = K.e^{-\frac{t}{RC}} \tag{2.24}$$

De la même manière, on cherchera la constante K.

à t =

$$0 \rightarrow U_c^D = U_0' = K$$

.

Avec  $U_0'$  la tension initiale juste avant le début de la décharge de C.

$$U_c^D(t) = U_0' e^{-\frac{t}{RC}} (2.25)$$

Et donc

$$U_R(t) = -U_0' e^{-\frac{t}{RC}} (2.26)$$

On pose  $t_0'$  l'instant de début de décharge.

Quand e(t) = E (la tension d'entrée du circuit) passe de E (charge) à 0 (décharge) à  $t'_0$

$$\Delta e = 0 - E = -E$$

$U_R(t)$  subit la même variation  $\Delta e = -E$  en passant de  $(E-U_0')$  à  $(-U_0')$ .  $U_c(t)$  ne subit aucune variation.

Quantité de charge emmagasinée q [4]:

$$q = C. U_c \ (coulomb) \tag{2.27}$$

Quantité d'énergie emmagasinée W [4]:

$$W = \frac{1}{2}C.U_c^2 \text{ (Joul)}$$

(2.28)

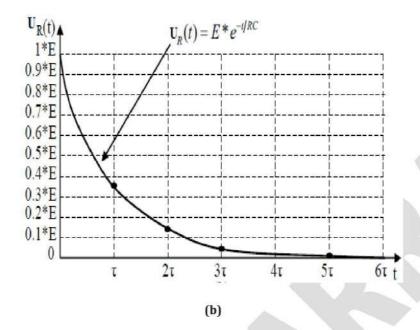

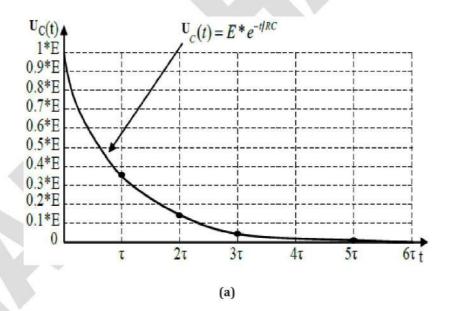

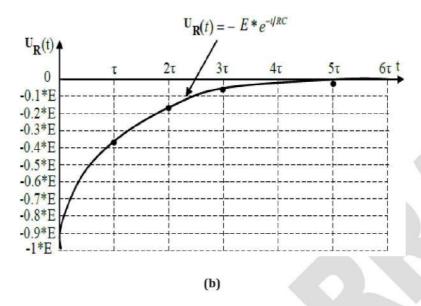

Figure 2.4 : Courbes de variations de Uc(t),  $U_R(t)$ , et i(t) pendant la décharge de C, (a) courbe de décharge du condensateur, (b) courbe de tension aux bornes de R lors de la décharge, et (c) courbe du courant lors de la décharge

### 2.3 Graphe universel

Si les temps  $t_0\,$  et  $t_0'\,$  sont éloignés. Le condensateur C aura le temps de se charger complètement pour E.

On pose  $U_0'=E$  (fin de charge et début de décharge). On suppose que U0=0 (C complètement déchargé).

Équation de charge :

$$U_c^c(t) = E(1 - e^{-\frac{t}{RC}})$$

(2.29)

Équation de décharge :

$$U_c^D(t) = E e^{-\frac{t}{RC}}$$

(2.30)

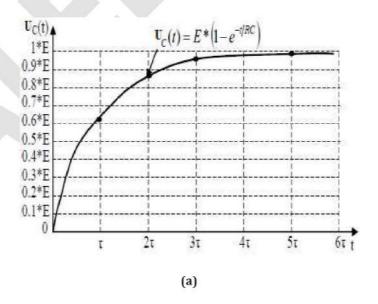

Si E = 1 V, on aura les variations de  $U_c(t)$  donnés dans le tableau 2.1 :

| t   | Charge: $1 - e^{-\frac{t}{RC}}$ | Décharge : $e^{-\frac{t}{RC}}$ |

|-----|---------------------------------|--------------------------------|

| RC  | 63%                             | 37%                            |

| 2RC | 86%                             | 14%                            |

| 3RC | 95%                             | 5%                             |

| 5RC | 99%                             | 1%                             |

Tableau 2.1 : Valeurs de charge et de décharge

$\tau = RC$

En pratique si  $t \ge 5 \tau$ , on suppose que la tension Uc(t) atteint sa valeur finale. On parle du régime permanant (figures 2.5 et 2.6) [2].

Figure 2.5 : Graphes universels de Uc(t),  $U_R(t)$ , pendant la charge de C, (a) graphe universel de la charge, (b) graphe universel de la tension aux bornes de R lors de la charge

Figure 2.6 : Graphes universels de Uc(t),  $U_R(t)$ , pendant la décharge de C, (a) graphe universel de la décharge, (b) graphe universel de la tension aux bornes de R lors de la décharge

### 2.4 Expression générale de l'équation de charge ou de décharge d'un condensateur

Si  $U_f$  est la tension finale de Uc quand t  $\rightarrow \infty$ , et si  $U_i$  la tension initiale de Uc (tension au début du processus de charge ou décharge).

$$U_c(t) = U_f - (U_f - U_i) e^{-\frac{t}{RC}}$$

(2.31)

L'équation générale aux bornes de C est comme suit :

Pour la charge : Si  $U_f = E$ ,  $U_i = U_\theta$  alors :

$$U_c^c(t) = E - (E - Uo).e^{-\frac{t}{RC}}$$

(2.32)

Pour la décharge : Si Uf = 0,  $Ui = U'_0$  alors :

$$U_c^D(t) = U_0' e^{-\frac{t}{RC}} (2.33)$$

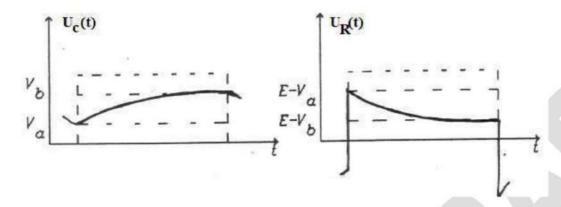

### 2.5 Tensions particulières

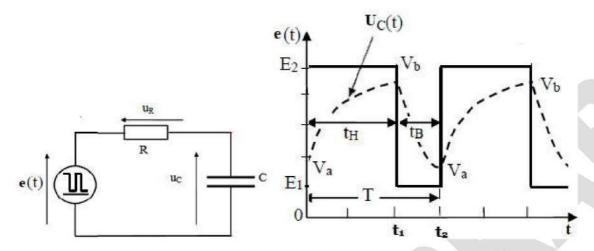

Soit le montage RC de la figure 2.7 avec e(t) signal rectangulaire dont les valeurs oscillantes entre E1 et E2. Les tensions particulière sont  $V_a$ , et  $V_b$ .  $V_b$  est la tension maximale de charge du condensateur C, et  $V_a$  est la tension minimale de décharge de C.

Figure 2.7 : Circuit RC avec tension d'entrée rectangulaire

Pendant la charge:

$$U_c^c(t) = E_2 - (E_2 - V_a) \cdot e^{-\frac{t}{RC}}$$

(2.34)

Pendant la décharge :

$$U_c^D(t) = E_1 - (E_1 - V_b). e^{-\frac{t}{RC}}$$

(2.35)

Aux instants de commutations on a :

$$\begin{cases} U_c^c(t_1) = V_b = E_2 - (E_2 - V_a). e^{-\frac{t_1}{RC}} \\ U_c^D(t_2) = V_a = E_1 - (E_1 - V_b). e^{-\frac{t_2}{RC}} \end{cases}$$

(2.36)

En posant  $\lambda_1 = e^{-\frac{t_1}{RC}}$  et  $\lambda_2 = e^{-\frac{t_2}{RC}}$

La résolution de ce système d'équations donnera les valeurs Va et Vb suivantes [1]:

$$\begin{cases} V_{a} = \frac{E_{1}(1-\lambda_{2})+E_{2}(1-\lambda_{1})\lambda_{2}}{1-\lambda_{1}\lambda_{2}} \\ V_{b} = \frac{E_{2}(1-\lambda_{1})+E_{1}(1-\lambda_{2})\lambda_{1}}{1-\lambda_{1}\lambda_{2}} \end{cases}$$

(2.37)

Plusieurs cas se présentent selon les durées t1 et t2

$$\underline{\mathbf{Cas 1:}} \ \mathbf{t_1} >> \implies \lambda_1 = e^{-\frac{t_1}{RC}} = 0$$

Dans ce cas le condensateur a tout le temps pour se charger jusqu'à E2 (ici Vb atteint E2).

$$\Rightarrow \begin{cases} V_{a} = E_{1}(1 - \lambda_{2}) + E_{2} \lambda_{2} \\ V_{b} = E_{2} \end{cases}$$

(2.38)

$\underline{\mathbf{Cas}\; \mathbf{2}:}\; \mathsf{t_2} >> \implies \lambda_2 \; \backsimeq \; 0$

Dans ce cas le condensateur a tout le temps pour se décharger jusqu'à  $E_1$  (ici  $V_a$  atteint  $E_1$ ).

$$\Rightarrow \begin{cases} V_a = E_1 \\ V_b = E_2(1 - \lambda_1) + E_1 \lambda_1 \end{cases}$$

(2.39)

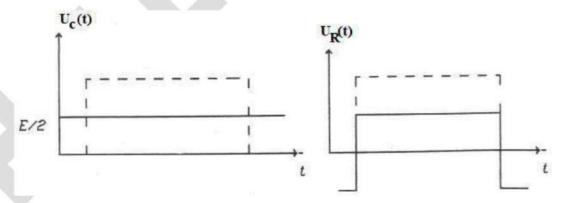

<u>Cas 3:</u>  $t_1 = t_2$  et  $E_1 = 0$ . Ici on suppose que  $t_2 = t_B$  (en changeant le repère des temps sur  $t_1$ ).

Dans ce cas e(t) est un signal carré avec une valeur inférieur nulle.

$$\Rightarrow \lambda_1 = \lambda_2$$

$$\begin{cases} V_{\rm a} = \frac{E_2 \lambda}{1+\lambda} \\ V_{\rm b} = \frac{E_2}{1+\lambda} \end{cases}$$

(2.40)

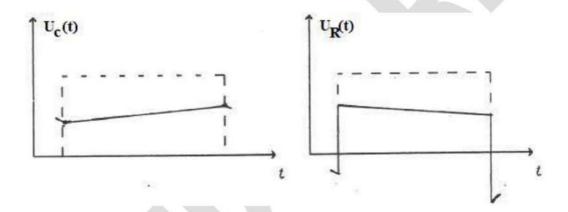

### 2.6 Formes des tensions d'un circuit RC

Les signaux (tensions) aux bornes de C et R changent et dépendent principalement de la constante de temps  $\tau = RC$  et de la période T . On a quatre cas  $(\tau << T, \tau = T, \tau >> T, \tau \rightarrow \infty)$ . Les figures 2.8, 2.9, 2.10, et 2.11 [1] montrent les différentes courbes de charge et décharge du condensateur ainsi que la tension aux bornes de R selon les valeurs de RC et de la période T. On peut remarquer que ces paramètres influent sur l'allure des chronogrammes.

Figure 2.8 : Constante de temps très faible  $\tau \ll T$ . La forme et l'amplitude Uc(t) est presque identique à celle de e(t).

Figure 2.9 : Constante de temps et période identiques  $\tau$  = T. La charge de C n'atteint jamais la tension maximale d'entrée (E), et sa décharge n'atteint jamais la valeur inférieure de e(t).

Figure 2.10 : Constante de temps très élevée  $\tau >> T$ . La forme de Uc(t) devient triangulaire et d'amplitude faible.

Figure 2.11 : Constante de temps infinie  $\tau \rightarrow \infty$ . Le signal Uc(t) est une constante égale à la moyenne de e(t).

# Composants actifs en commutation

### 3.1 Diode en commutation

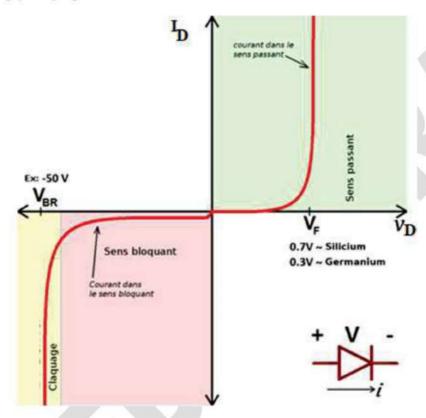

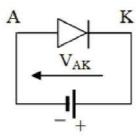

La diode est un dipôle non linéaire qui ne laisse passer le courant que dans un seul sens. Elle est construite avec une jonction PN. En mode commutation elle joue le rôle d'un interrupteur ou de commutateur [3].

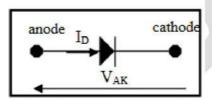

Figure 3.1 : Schéma d'une diode

Le courant qui traverse la diode suit un modèle exponentiel  $I_D = f(V_D)$  [1]:

$$I_{D} = I_{s} \left[ exp\left(\frac{eV_{D}}{KT}\right) - 1 \right]$$

(3.1)

Avec:

VD: Tension appliquée à la diode

Is: Courant de saturation

e: Charge de l'électron = - 1.6 10-19 C

K: Constante de Boltzmann = 1.38 10-23 J/K

### T: Température absolue, en °K

A la température ambiante T = 27°C (300 °K),  $\frac{e}{\kappa T} \cong 40$

→

$$I_D = I_s [exp(40V_D)-1]$$

Figure 3.2 : Caractéristique de la diode

### 3.1.1 Polarisation directe

Figure 3.3: Polarisation directe de la diode

La tension appliquée (VAK > 0) permet le passage d'un courant électrique de l'anode vers la cathode appelé courant direct.

Pour V > 0  $\exp(40 \text{ V}) >> 1 \rightarrow \text{ID} = \text{Is } \exp(40 \text{ V}).$

Dans le sens direct de la polarisation il y a présence de résistance dynamique  $\rho$  très faible. Quand la tension  $V_{AK} > V_{seuil}$ , le courant I<sub>D</sub> augmente et la tension ne change pas beaucoup (Figure 3.2).

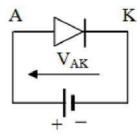

### 3.1.2 Polarisation inverse:

Figure 3.4 : Polarisation inverse de la diode

La tension appliquée ( $V_{AK}$  < 0) empêche le passage du courant. Le courant inverse est pratiquement nul.

En polarisation inverse, si la tension appliquée à la diode est inférieure à la tension de claquage inverse, exp(40 V<sub>D</sub>) << 1, dans ce cas la caractéristique est une droite horizontale.  $I_D$  = - Is. Dans cette zone de polarisation, la résistance inverse Ri est très élevée [5].

Pour des valeurs élevées de tensions, le courant inverse augmente de façon exponentielle jusqu'à claquage de la jonction. Ce claquage est réversible si la puissance dissipée est supportable, sinon la diode est détruite en raison de l'échauffement causé par le passage excessif du courant.

Pour une diode au silicium, le courant Is double quand la température augmente de 6°C, et pour une diode au germanium, le courant Is double quand la température augmente de 10°C [5].

### 3.1.3 Schémas équivalents de la diode

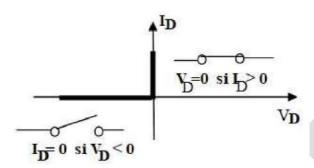

### 3.1.3.1 Caractéristique parfaite : approximation 1

Dans ce cas on néglige la tension de seuil et la résistance dynamique de la diode. La caractéristique est donnée en Figure 3.5. En polarisation directe la diode est passante dès qu'on applique une tension >0 aux bornes de la diode (V<sub>D</sub>=0, I<sub>D</sub>>0). En polarisation inverse la diode est bloquée (VD<0, ID=0).

Dans ce cas on parle de diode parfaite et se comporte comme un interrupteur (en directe c'est un court-circuit, et en inverse c'est un circuit ouvert).  $V_{seuil} = V_0 = 0$ .  $\rho = 0$ ,  $I_s = 0$ ,  $R_i = 0$ ∞ [6].

Figure 3.5 : Caractéristique parfaite de la diode

#### 3.1.3.2 Caractéristique idéalisée : approximation 2

Figure 3.6 : Schéma équivalent et caractéristique d'une diode idéalisée

Dans ce cas on néglige la résistance dynamique de la diode, mais on tient compte de la tension de seuil V<sub>0</sub> ≠ 0. La diode idéalisée est l'équivalent d'une diode parfaite en série avec une tension de V<sub>0</sub> (Figure 3.6).

En polarisation directe [6]:

- $V_D = V_0$  et  $I_D > 0$  (tension appliquée à la diode  $\geq V_0$ )

- $V_D < V_0$  et  $I_D = 0$  (tension appliquée à la diode  $< V_0$ )

En polarisation inverse :  $V_D < 0$  et  $I_D = 0$

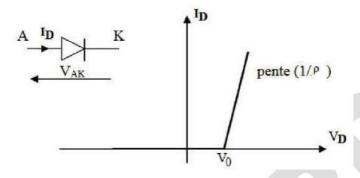

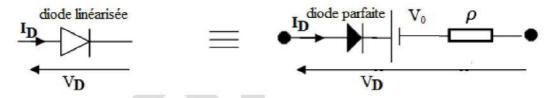

#### 3.1.3.3 Caractéristique linéarisée : approximation 3

La caractéristique de la diode peut se rapprocher par deux portions de droites. Dans ce cas on ne néglige rien ( $V_0 \neq 0, \rho \neq 0$ ).

La diode linéarisée est l'équivalent d'une diode parfaite en série avec une tension Vo et une résistance  $\rho$  [6].

Figure 3.7 : Caractéristique d'une diode linéarisée

En polarisation directe le schéma équivalent de la diode est donné par la Figure 3.8.

Figure 3.8 : Schéma équivalent d'une diode linéarisée en polarisation directe

En polarisation inverse la diode est équivalente à un circuit ouvert.

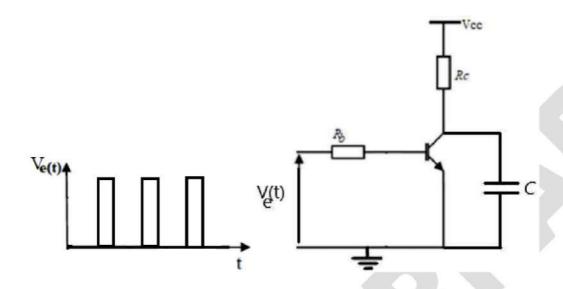

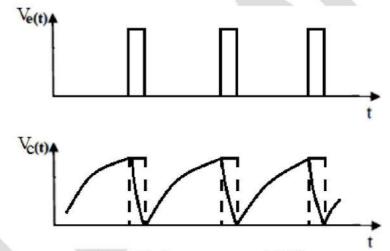

#### 3.2 Transistor en commutation

Un transistor est un composant semi-conducteur à 3 électrodes actives. Il permet de contrôler un courant ou une tension sur l'électrode de sortie (le collecteur) grâce à une électrode d'entrée (La base). Le transistor est constitué par deux jonctions P et N, selon l'agencement on distingue deux types NPN et PNP (Figure 3.9).

Figure 3.9: Transistor PNP et NPN

Un transistor est utilisé en commutation lorsque son mode de fonctionnement s'apparente à un interrupteur. En réalité sa polarisation ne lui permet que deux modes de fonctionnement par opposition au fonctionnement en régime linéaire (amplification).

Figure 3.10 : Schéma équivalent d'un transistor en commutation

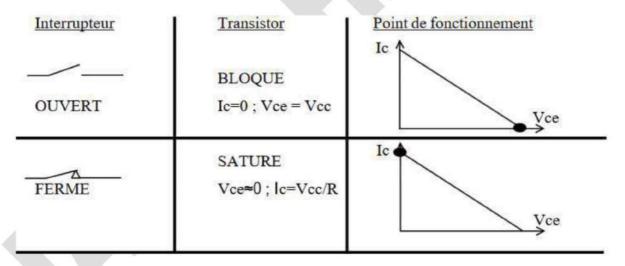

Le transistor peut fonctionner selon 3 régimes : bloqué, linéaire, saturé (Tableau 3.1).

| Mode bloqué                    | Mode linéaire                                                                                 | Mode saturé                    |  |

|--------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------|--|

| Les jonctions Emetteur-        | La jonction Base-Emetteur Les deux jonctions polarisée en direct, et la Emetteur-Base et Base |                                |  |

| Base                           |                                                                                               |                                |  |

| et Base-Collecteur sont        | jonction Base-Collecteur                                                                      | Collecteur) sont polarisées    |  |

| polarisées en inverse.         | polarisée en inverse.                                                                         | en direct.                     |  |

| $V_{BE} < 0$ et $V_{CB} > 0$ . | $V_{BE} > 0$ et $V_{CB} > 0$ .                                                                | $V_{BE} > 0$ et $V_{CB} < 0$ . |  |

Tableau 3.1 : Régimes de fonctionnement d'un transistor bipolaire

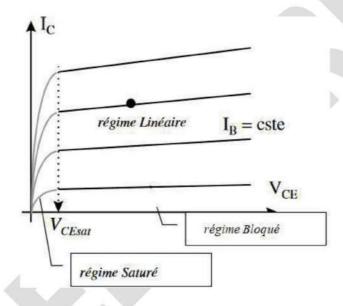

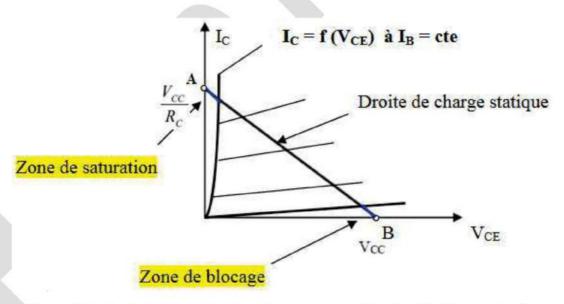

Figure 3.11 : Caractéristiques de sortie d'un transistor

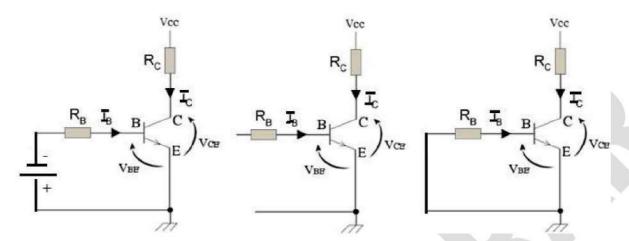

## 3.2.1 Mode bloqué

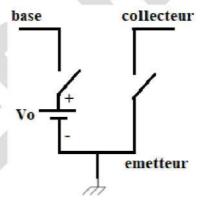

Pour bloquer un transistor on applique une tension ≤ 0. La Figure 3.12 montre les trois types de blocage d'un transistor.

Figure 3.12 : Montage d'un transistor en régime bloqué

Si la tension appliquée à la base du transistor  $\langle V_{BE} \rightarrow I_B = 0$ ,  $V_{CE} \approx V_{CC}$ , le point de fonctionnement se trouve en bas de la droite de charge (point B en Figure 3.15).

A l'état bloqué le transistor est un interrupteur ouvert (Figure 3.13) [1].

Figure 3.13 : Schéma équivalent d'un transistor en régime de blocage

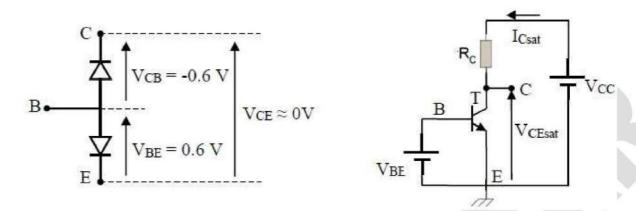

#### 3.2.2 Mode saturé

Le régime saturé est atteint quand on applique une tension à la base très élevée (VBE (appliquée) > V0 (seuil)), I<sub>B</sub>≠ 0, ce qui permet de placer le point de fonctionnement en haut de la droite de charge (point A en Figure 3.15) [1].

Figure 3.14 : Montage d'un transistor en régime saturé

$$\begin{cases} V_{BE} \approx V_{CB} \Longrightarrow V_{CE}(sat) = V_{CB} + V_{BE} \approx 0 \\ V_{CC} >> V_{CE}(sat). \end{cases}$$

(3.2)

$$I_{Csat} \approx \frac{V_{CC}}{R_C}$$

(3.3)

La tension V<sub>CE(sat)</sub> n'est pas vraiment nulle, mais est très faible, de l'ordre de 0.3V

Figure 3.15: Droite de charge d'un transistor en commutation. Point A (régime saturé), et point B (régime bloqué)

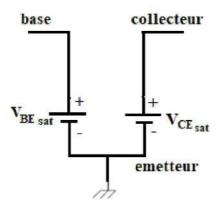

A l'état saturé, le transistor est un interrupteur fermé non parfait. Le circuit de base comporte  $V_{BEsat} > V0$  (Figure 3.16).

Figure 3.16 : Schéma équivalent d'un transistor en régime de saturation

Pour s'assurer de la saturation du transistor, on calcule Ic et  $I_B$  séparément. On sait que  $\beta$ (coefficient d'amplification du courant) est plus faible dans la zone de saturation que dans la zone linéaire  $\beta_{min}$ . La saturation est réalisée si [1]:

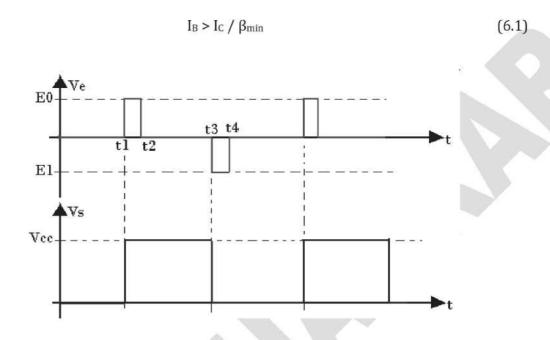

$$I_B > \frac{I_C}{\beta_{min}} \tag{3.4}$$

En pratique, il faut que I<sub>B</sub> soit 2 à 3 fois >  $\frac{I_C}{\beta_{min}}$

$$I_B = \alpha \frac{I_C}{\beta_{min}} \tag{3.5}$$

Avec  $\alpha$  coefficient de saturation  $\alpha$  = 2 à 3.

## Circuits de mise en forme

#### 4.1 Introduction

Les circuits de mise en forme sont des circuits qui permettent de transformer la forme d'un signal pour l'adapter à un autre étage d'un circuit électronique.

#### 4.2 Ecrêteur à diode simple

L'écrêtage désigne la suppression d'une partie ou la totalité les alternances positives ou négatives d'un signal alternatif.

#### 4.2.1 Ecrêteur à diode en série

Dans le montage de la Figure 4.1.b la diode considérée parfaite est en série avec le signal d'entrée e(t) [6].

Figure 4.1 : Ecrêteur à diode en série inférieur à zéro. (a) signal d'entrée, (b) circuit écrêteur, (c) signal de sortie, (d) caractéristique de transfert

L'écrêteur illustré dans la Figure 4.1 s'appelle écrêteur inférieur à 0 (< 0). En effet il écrête l'alternance négative. Si e(t) ≥ 0, la diode est passante (car polarisée en directe), elle se comportera comme un court-circuit (approximation 1). La sortie suivra l'entrée dans ce cas(s(t) = e(t)). Si e(t) < 0, la diode est bloquée et se comportera comme un circuit ouvert, et donc il n'y a plus de courant qui passe dans le circuit et la sortie s(t) = 0.

Si on inverse la diode on aura un écrêteur supérieur à zéro (>0), et les signaux de sortie et de transfert vont s'inverser (Figure 4.2).

Figure 4.2 : Ecrêteur à diode en série supérieur à zéro. (a) signal d'entrée, (b) circuit écrêteur, (c) signal de sortie, (d) caractéristique de transfert

#### 4.2.2 Ecrêteur à diode en parallèle

Dans ce genre de montage on met la diode à la sortie du circuit. La cathode de la diode est reliée à la masse [7].

- Si  $e(t) \ge 0$ , la diode conduit, elle se comporte comme un court-circuit, donc s(t) = 0.

- Si e(t) < 0, la diode est bloquée, elle se comporte comme un court-ouvert, donc s(t)= e(t).

Figure 4.3 : Ecrêteur à diode parallèle. (a) signal d'entrée, (b) circuit écrêteur, (c) signal de sortie, (d) caractéristique de transfert

#### 4.2.3 Ecrêteur à diode polarisée

Pour écrêter à un niveau supérieur à zéro (> 0) on ajoute une composante continue (DC) à la diode (en mettant en série avec la diode une pile).

#### 4.2.3.1 Ecrêteur à diode polarisée en série

Soit le circuit de la Figure 4.4. La diode est supposée parfaite. Une alimentation stabilisée de tension E est placée en série avec la diode. L'entrée de la diode est alimentée avec une tension de e(t) + E. Le circuit de la figure 4.4.b est équivalent à celui de la figure 4.4.a [7].

- Si  $e(t) + E \ge 0 \rightarrow e(t) \ge -E$ . La diode est passante, elle se comporte comme un courtcircuit.  $\rightarrow$  s(t) = e(t) + E.

- Si  $e(t) + E < 0 \rightarrow e(t) < -E$ . La diode est bloquée, elle se comporte comme un courtouvert.  $\rightarrow$  s(t) = 0. En effet aucun courant ne passe dans la résistance.

Figure 4.4 : Ecrêteur à diode polarisée en série. (a) circuit type, (b) équivalent du circuit, (c) signal d'entrée, (d) signal d'entrée de la diode, (e) la sortie, (f) caractéristique de transfert

#### 4.2.3.2 Ecrêteur à diode polarisée en parallèle

Le montage de la Figure 4.5 montre un circuit écrêteur à diode polarisée en parallèle. Dans ce cas on met la diode en série avec une pile, en sortie du circuit [1].

Si  $e(t) \ge E$ , la diode est passante (court-circuit)  $\rightarrow$  s(t) = E

Si e(t) < E, la diode est bloquée (circuit-ouvert), le courant qui passe dans le diode est nulle  $(i_R(t) = i_d(t) = 0) \rightarrow s(t) = e(t)$ .

Figure 4.5 : Ecrêteur à diode polarisée parallèle. (a) signal d'entrée, (b) circuit écrêteur, (c) signal de sortie, (d) caractéristique de transfert

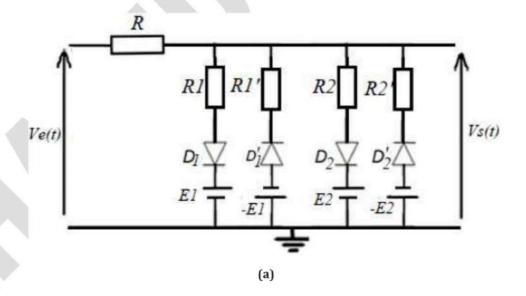

#### 4.2.4 Ecrêteur à deux diodes polarisées

Soit le circuit représenté en Figure 4.6. On veut écrêter un signal de part et d'autre de Esup et  $E_{inf}$  avec  $E_{sup} > E_{inf}$  [7].

- Si  $e(t) \ge E_{sup}$ . D1 conduit et D2 bloquée. D1 se comporte en court-circuit, et la branche D2 est en circuit-ouvert donc id2(t) = 0. La sortie s(t) est aux bornes de  $E_{sup}$ , donc s(t) $= E_{\text{sup}}.$

- Si - $E_{inf}$  < e(t) <  $E_{sup}$ . D1 et D2 sont bloquées, aucun courant ne passe dans le circuit. L'entrée est reliée directement à la sortie  $\rightarrow$  s(t) = e(t).

- Si  $e(t) \le -E_{inf}$ , D1 est bloquée et D2 conduit  $\rightarrow s(t) = -E_{inf}$

Figure 4.6 : Ecrêteur à 2 diodes polarisées. (a) signal d'entrée, (b) circuit écrêteur, (c) signal de sortie, (d) caractéristique de transfert

#### 4.3 Ecrêteur à diode zener

#### 4.3.1 Caractéristique de la diode zener

La diode zener est un cas particulier de la diode à jonction, où en directe se comporte comme une diode simple, et en inverse comme un stabilisateur de tension (Figure 4.7.a). La diode zener est surtout exploitée en polarisation inverse où elle est équivalente à une diode parfaire en série avec un générateur de tension Vz et une résistance inverse Rz [7].

Figure 4.7 : Diode zener. (a) Caractéristique, (b) schéma équivalent

#### 4.3.2 Ecrêteur à une diode zener

Soit le montage à diode zener de la Figure 4.8. L'entrée est un signal carré variant entre  $e_{min}$  et  $e_{max}$ . On suppose que Rz = 0 [1].

C'est un ecrêteur polarisé à 2 diodes (> Vz et < 0).

- Si  $e(t) \ge Vz$ , D1 est bloquée (circuit-ouvert), D2 est passante (court-circuit), s(t) = Vz.

- Si  $0 \le e(t) < Vz$ , D1 passante (court-circuit), D2 bloquée (circuit-ouvert), s(t) = 0.

- Si e(t) < 0, D1 passante (court-circuit), D2 bloquée (circuit-ouvert), s(t) = 0.

Figure 4.8 : Ecrêteur à une diode zener. (a) circuit, (b) circuit équivalent, (c) signal de sortie

#### 4.3.3 Ecrêteur à deux diodes zener tête-bêche

Pour écrêter à deux tensions différentes, on peut placer deux diodes zener en tête-bêche. La Figure 4.9 montre le circuit type de deux diodes zener placées en tête-bêche (Figure 4.9.a). Pour simplifier ce circuit, on peut le remplacer par son équivalent (Figure 4.9.b) [1].

Figure 4.9 : Ecrêteur à 2 diodes zener. (a) circuit, (b) circuit équivalent

Le fonctionnement de ce circuit est régi par les alternances du signal d'entrée. Il n'y a que 2 diodes qui fonctionnent dans chaque cas.

1er cas : Si e(t) > 0, le schéma des diodes zener est représenté par le schéma équivalent de la Figure 4.10.a.

- Si  $e(t) \ge Vz2$ , D1 et D2 sont passantes (court-circuit), s(t) = Vz2.

- Si e(t) < Vz2, D1 et D2 sont bloquées (circuit-ouvert), s(t) = e(t).

2<sup>eme</sup> cas : Si e(t) < 0, le schéma des diodes zener est représenté par le schéma équivalent de la Figure 4.10.b.

- Si  $e(t) \le -Vz1$ , D1 et D2 sont passantes (court-circuit), s(t) = -Vz1.

- Si e(t) > -Vz1, D1 et D2 sont bloquées (circuit-ouvert), s(t) = e(t).

Ce qui revient à dire que le circuit écrêteur à deux diodes zener montées en tête-bêche est un écrêteur polarisé à deux diodes >Vz2 et < -Vz1.

Figure 4.10 : Schémas équivalents du circuit selon les alternances du signal d'entrée. (a) pour e(t) > 0, (b) pour e(t) < 0, (c) sortie s(t)

#### 4.4 Détecteur de crête

#### 4.4.1 Détecteur de crête simple

Le circuit détecteur de crête permet de détecter la valeur crête d'un signal d'entrée, et donc il fournit un signal de sorti constant égale à la valeur maximale du signal d'entrée.

Le circuit présenté en Figure 4.11 donne un exemple d'un détecteur de crête [1].

Si e(t) > 0, la diode D est passante, et le condensateur C se charge jusqu'à la valeur crête de e(t) qui est  $e_{max}$ , et la diode reste toujours bloquée.  $s(t) = e_{max}$ .

Si e(t) < 0, la cathode de la diode est soumise à la tension  $e_{max}$  car le condensateur s'est chargé à emax. Donc la diode restera bloquée, et le condensateur ne se décharge pas, donc s(t) = emax.

Figure 4.11 : Détecteur de crête. (a) signal d'entrée e(t), (b) circuit détecteur, (c) sortie s(t)

Pour détecter la crête négative il suffit d'inverser la diode, ce qui permet de faire passer l'alternance négative.

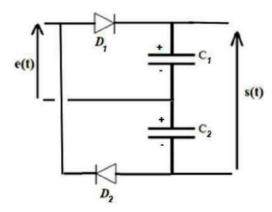

#### 4.4.2 Détecteur de crête-à-crête

Le détecteur de crête-à-crête fournit en sortie une tension égale à la valeur crête-à-crête de la tension d'entrée. Le circuit représenté en Figure 4.12 illustre un doubleur de tension [7].

- Si e(t) > 0, D2 bloquée, D1 conduit et C1 se charge jusqu'à emax.

- Si e(t) < 0, D1 bloquée, D2 conduit et C2 se charge jusqu'à emin.

Apres les deux alternances les deux condensateurs C1 et C2 seront chargés aux valeurs crêtes de la tension e(t). Ce qui va donner s(t) = Uc1 + Uc2

Si

$$|e_{max}| = |e_{min}| \rightarrow s(t) = 2.e_{max}$$

Figure 4.12 : Détecteur de crête-à-crête (doubleur de tension)

#### 4.5 Amplificateurs opérationnels en régime non linéaire

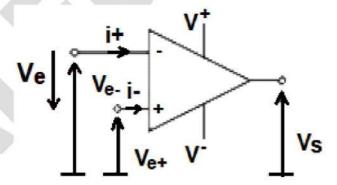

L'amplificateur opérationnel (AOP) est un amplificateur différentiel qui amplifie une différence de potentiel électrique présente à ses entrées ( $Ve = V_e^+ - V_e^-$ ). Le fonctionnement en régime non linéaire ou régime de commutation est conditionné par la contre réaction. Quand il n'y a pas de contre-réaction négative ou quand il y a réaction positive on parle de régime non linéaire [8].

Dans ce cas la sortie dépend que du signe de e :

- Si e > 0  $\rightarrow V_e^+ > V_e^- \Rightarrow Vs = V^+$

- Si e < 0  $\rightarrow$   $V_e^+$  <  $V_e^ \Rightarrow$  Vs =  $V^-$ On a aussi i+ = i- = 0

Figure 4.13 : Schéma d'un amplificateur opérationnel

#### 4.5.1 Comparateur à un seuil

Le comparateur à un seuil permet de comparer la tension d'entrée (Ve) par rapport à une tension de référence généralement continue (Vo). Il y a deux types inverseur et noninverseur [9].

#### 4.5.1.1 Comparateur à un seuil non-inverseur

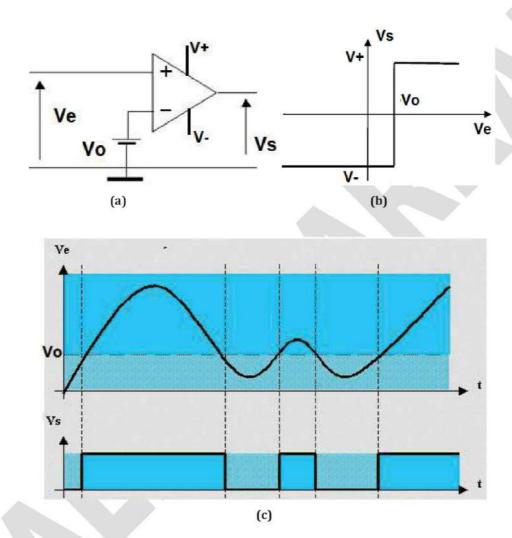

Dans ce genre de montages la tension d'entrée Ve est appliquée à l'entrée non-inverseuse (+), et la tension de référence Vo est appliquée à l'entrée inverseuse (-).

Figure 4.14 : Schéma d'un comparateur non-inverseur. (a) circuit, (b) caractéristique de transfert, (c) chronogrammes d'entrée et de sortie

Soit le montage représenté en Figure 4.14.a:

- Si Ve(t) > Vo  $\rightarrow$  Vs(t) =  $V^+$

- Si Ve(t) < Vo  $\rightarrow$  Vs(t) =  $V^-$

Si Vo =  $0 \rightarrow 0$ n parle de comparateur détecteur de passage par zéro.

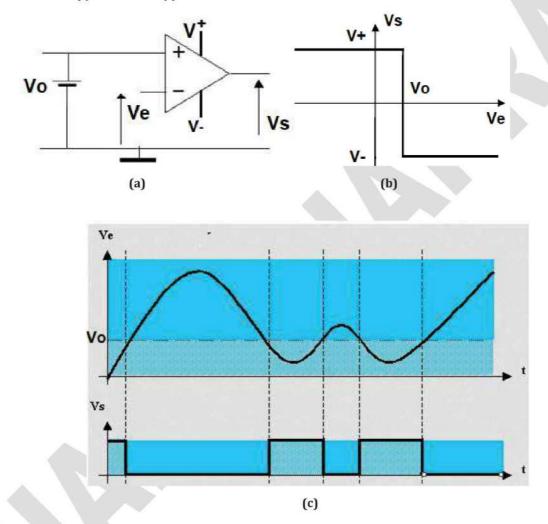

#### 4.5.1.2 Comparateur à un seuil inverseur

Dans ce genre de montages la tension de référence Vo est appliquée à l'entrée inverseuse (-), et la tension d'entrée Ve est appliquée à l'entrée + (non-inverseuse).

Soit le montage représenté en Figure 4.15.a [10]:

- Si Ve(t) < Vo  $\rightarrow$  Vs(t) =  $V^+$

- Si Ve(t) > Vo  $\rightarrow$  Vs(t) =  $V^-$

Figure 4.15 : Schéma d'un comparateur inverseur. (a) circuit, (b) caractéristique de transfert, (c) chronogrammes d'entrée et de sortie

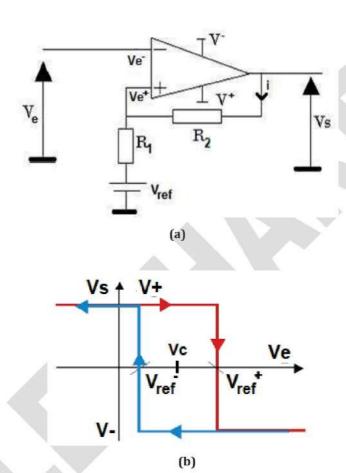

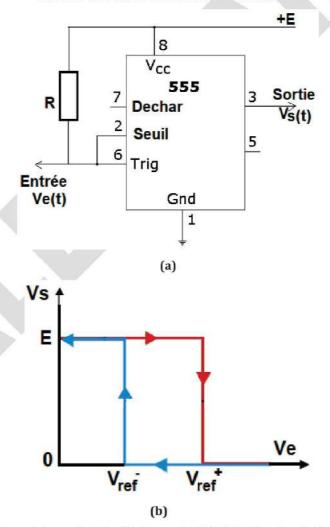

#### 4.5.2 Comparateur à hystérésis

Un comparateur à hystérésis est un comparateur à deux seuils (appelé aussi trigger de Schmitt) dont la tension de sortie Vs prend deux valeurs stables et distinctes  $V^+$  ou  $V^-$ , en fonction de deux seuils ( $V_{ref}^+$  ou  $V_{ref}^-$ ), de la tension d'entrée Ve [9].

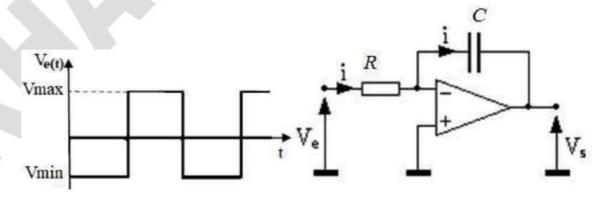

#### 4.5.3 Trigger de Schmitt à amplificateur opérationnel

#### 4.5.3.1 Trigger de Schmitt inverseur

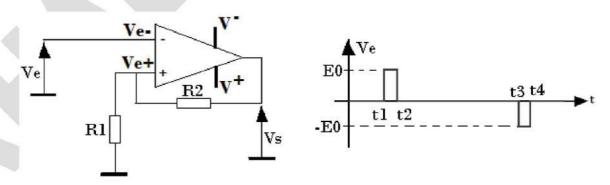

Dans le cas d'un montage à trigger de Schmitt inverseur, la tension d'entrée Ve(t) est appliquée à l'entrée inverseuse de l'AOP (Figure 4.16.a) [10].

Figure 4.16 : Trigger de Schmitt inverseur. (a) circuit à AOP, (b) Caractéristique de transfert

Les équations de mailles du circuit de la Figure 4.16.a donnent :

$$V_{ref} + (R1 + R2) i = Vs$$

(4.1)

$$\Rightarrow i = \frac{Vs - V_{ref}}{R1 + R2} \tag{4.2}$$

$$V_{R1} = R1 \times I \tag{4.3}$$

$$V_e^+ = V_{ref} + V_{RI} \tag{4.4}$$

$$V_e^+ = V_{ref} + R1 \left( \frac{V_{s-V_{ref}}}{R_{1} + R_{2}} \right) \tag{4.5}$$

En développant l'expression précédente, on aboutit à :

$$V_e^+ = \frac{R2}{R1 + R2} V_{ref} + \frac{R1}{R1 + R2} V_S \tag{4.6}$$

$$V_e^- = Ve(t) \tag{4.7}$$

- Condition 1 : Si  $V_e^+ > V_e^- \rightarrow Vs = V^+$

- Condition 2 : Si  $V_e^+ < V_e^- \rightarrow V_S = V^-$

Selon l'équation (4.6) on a :

$V_e^+ = V_{ref}^+$  (valeur de Ve(t) supérieure) pour Vs =  $V^+$  (car en remplaçant dans (4.6) Vs par  $V^+$ , Ve+ devient élevé et donc Ve+ =  $V_{ref}^+$ )

$V_e^+ = V_{ref}^-$  (valeur de Ve(t) inférieure) pour Vs =  $V^-$  (car en remplaçant dans (4.6) Vs par  $V^-$ ,  $V_e^+$  devient inférieure et donc  $V_{ref}^-$ )

Selon l'équation (4.6) et la condition 1 on a :

$$V_{ref}^{+} = \frac{R2}{R1 + R2} V_{ref} + \frac{R1}{R1 + R2} V^{+}$$

(4.8)

Selon l'équation (4.6) et la condition 2 on a :

$$V_{ref}^{-} = \frac{R2}{R1 + R2} V_{ref} + \frac{R1}{R1 + R2} V^{-}$$

(4.9)

Les tensions  $V_{ref}^+$  et  $V_{ref}^-$  sont les tensions de commutation du trigger de schmitt.

## Interprétation de la courbe (Figure 4.16.b) [1]:

On commence par les valeurs inférieures de Ve(t) et on augmente la tension. Tant que  $Ve(t) < V_{ref}^+$  la sortie  $Vs(t) = V^+$ . Des que  $Ve(t) > V_{ref}^+$ , la sortie tombe à  $V^-$ .

De même en commence à diminuer Ve(t): tant que  $Ve(t) > V_{ref}^-$ , la sortie  $Ve(t) = V^-$ . Dès que  $Ve(t) < V_{ref}^-$ , la sortie remonte à  $V^+$ .

La largeur de l'hystérésis est calculé par la différence des tensions référence.

$$\Delta V = V_{ref}^+ - V_{ref}^- \tag{4.10}$$

$$\Delta V = \frac{R1}{R1 + R2} (V^+ - V^-) \tag{4.11}$$

$$\operatorname{Si} V^{+} = -V^{-} \rightarrow \Delta V = \frac{2R1}{R1 + R2} V^{+}$$

(4.12)

La tension au centre de l'hystérésis Vc :

$$Vc = \frac{V_{ref}^{+} + V_{ref}^{-}}{2} \tag{4.13}$$

$$Vc = \frac{R1}{2(R1+R2)}(V^{+} - V^{-}) + \frac{R2}{R1+R2}V_{ref}$$

(4.14)

Si  $V^+ = -V^-$  alors:

$$Vc = \frac{R2}{R1 + R2} V_{ref} (4.15)$$

Si  $V_{ref}$  = 0 → Vc = 0, le trigger est dit centré.

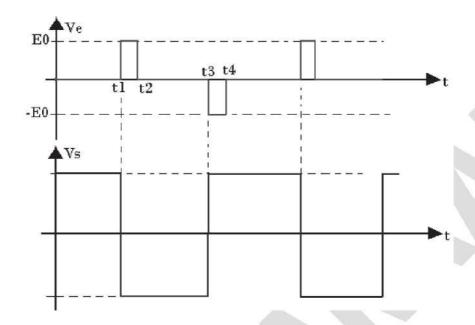

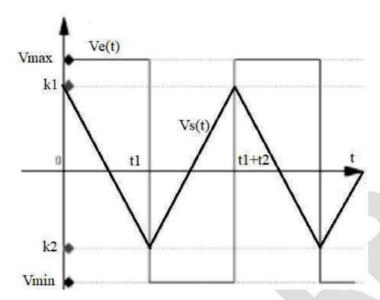

#### 4.5.3.2 Trigger de Schmitt non-inverseur

Dans le cas d'un montage à trigger de Schmitt non-inverseur, la tension d'entrée Ve(t) est appliquée à l'entrée non-inverseuse de l'AOP (Figure 4.17.a) [10].

Figure 4.17 : Trigger de Schmitt non-inverseur. (a) circuit à AOP, (b) Caractéristique de transfert

Les équations de mailles du circuit de la Figure 4.17.a donnent :

$$V_e^- = V_{ref} \tag{4.16}$$

$$V_e^+ = Ve + V_{R1} = Ve + R1 \times I \tag{4.17}$$

$$Ve = Vs - (R1 + R2)I$$

(4.18)

$$\Rightarrow i = \frac{Vs - Ve}{R1 + R2} \tag{4.19}$$

$$V_e^+ = Ve + R1 \left( \frac{Vs - Ve}{R1 + R2} \right) \tag{4.20}$$

$$V_e^+ = \frac{R^2}{R^{1+R^2}} Ve + \frac{R^1}{R^{1+R^2}} Vs \tag{4.21}$$

- Condition 1 :  $Si V_e^+ > V_{ref} \rightarrow Vs = V^+$

- Condition 2 :  $Si V_e^+ < V_{ref} \rightarrow Vs = V^-$

Le but est de déterminer les tensions de commutation de Ve pour que la sortie Vs bascule de  $V^-$  à  $V^+$  ou l'inverse.

Quelles sont donc les valeurs de  $V_{ref}^+$  et  $V_{ref}^-$ ?

Selon l'équation (4.21) et la condition 1 on a :

$$\frac{R2}{R1+R2}Ve + \frac{R1}{R1+R2}Vs > V_{ref}$$

(4.22)

$$Ve > \frac{R1+R2}{R2}V_{ref} - \frac{R1}{R2}V_{s}$$

(4.23)

Selon la condition 1 on a  $Vs = V^+$

$$Ve > \frac{R1+R2}{R2}V_{ref} - \frac{R1}{R2}V^{+}$$

(4.24)

Si on regarde le côté droit de l'inéquation on déduit que c'est une valeur faible, donc c'est  $V_{ref}^-$

$$V_{ref}^{-} = \frac{R1 + R2}{R2} V_{ref} - \frac{R1}{R2} V^{+}$$

(4.25)

De la même manière:

Selon l'équation (4.21) et la condition 2 on a :

$$\frac{R2}{R1 + R2}Ve + \frac{R1}{R1 + R2}Vs < V_{ref}$$

(4.26)

$$Ve < \frac{R1 + R2}{R2}V_{ref} - \frac{R1}{R2}V_{S} \tag{4.27}$$

Selon la condition 2 on a  $Vs = V^-$

$$Ve < \frac{R1 + R2}{R2}V_{ref} - \frac{R1}{R2}V^{-} \tag{4.28}$$

Si on regarde le côté droit de l'inéquation on déduit que c'est une valeur élevée, donc c'est  $V_{ref}^+$

$$V_{ref}^{+} = \frac{R1 + R2}{R2} V_{ref} - \frac{R1}{R2} V^{-} \tag{4.29}$$

$$\Delta V = V_{ref}^+ - V_{ref}^- \tag{4.30}$$

$$\Delta V = \frac{R1}{R2} (V^+ - V^-) \tag{4.31}$$

Si

$$V^+ = -V^- \rightarrow \Delta V = \frac{2R1}{R2}V^+$$

(4.32)

$$Vc = \frac{V_{ref}^+ + V_{ref}^-}{2} \tag{4.33}$$

$$Vc = \frac{R1 + R2}{R2} V_{ref} {(4.34)}$$

#### 4.5.3.3 Trigger de Schmitt à portes logiques

Il existe deux technologies de portes inverseuses TTL et CMOS qui diffèrent dans les valeurs des tensions de basculement de leurs états [1].

Pour des portes CMOS, Vol = 0, Voh = Vdd, et Vref = Vdd/2 avec Vdd tension d'alimentation  $\epsilon$  [3, 15] V.

Figure 4.18 : Caractéristiques des portes logiques. (a) porte inverseuse, (b) caractéristique de transfert pour porte TTL, et (c) pour CMOS

Figure 4.19 : Trigger de Schmitt à portes logiques. (a) circuit, (b) caractéristique de transfert

La résistance R4 introduit une réaction positive.

On suppose que Ve(t) est largement supérieur à zéro (> 0). La sortie de N1 est à l'état bas Vol et celle de N2 à l'état haut Voh. Par R4 cette tension est reportée sur l'entrée de N1 qui renforce l'état dû à la tension d'entrée.

Si Ve(t) descend suffisamment bas, la sortie N1 bascule à Voh et celle de N2 vers Vol. Le basculement inverse est le même (Figure 4.19).

D'après le théorème de MILLMAN on a [1]:

$$V_e'(t) = \frac{\frac{Ve}{R3} + \frac{Vs}{R4}}{\frac{1}{R3} + \frac{1}{R4}}$$

(4.35)

$$V_e'(t) = \frac{R3 \, Vs + R4 \, Ve}{R3 + R4} \tag{4.36}$$

Selon les formules précédentes on a :

$$V_{ref}^{+} = \frac{R3 + R4}{R4} V_{ref} - \frac{R3}{R4} V_{ol}$$

(4.37)

$$V_{ref}^{-} = \frac{R3 + R4}{R4} V_{ref} - \frac{R3}{R4} V_{oh} \tag{4.38}$$

$$V_{ref}^{+} = \frac{Vdd}{2} \left( 1 + \frac{R3}{R4} \right) \tag{4.39}$$

$$V_{ref}^{-} = \frac{Vdd}{2} \left( 1 - \frac{R3}{R4} \right) \tag{4.40}$$

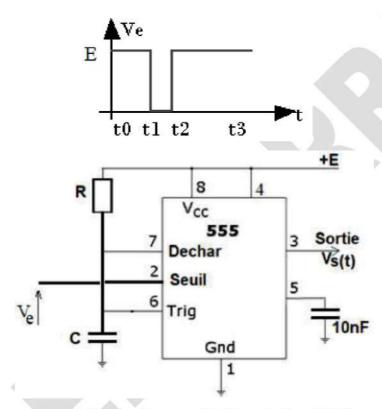

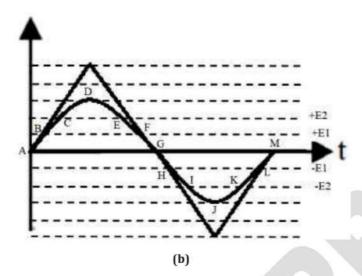

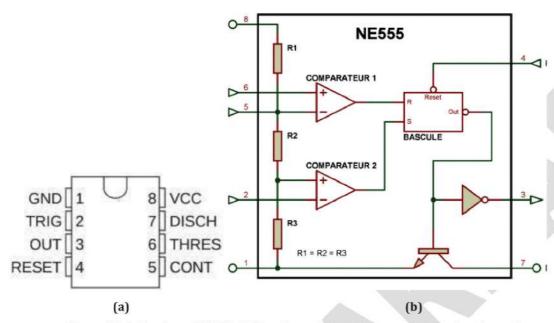

#### 4.5.3.4 Trigger de Schmitt à base du timer NE555

Le NE555 est un circuit intégré utilisé pour la temporisation. Il permet de générer des signaux rectangulaires (Figure 4.20). Le fonctionnement du timer (horloge) NE555 est

conditionné par la sortie de la bascule RS, qui elle-même conditionné par les sorties des comparateur 1 et 2 qui sont reliées aux entrée R et S respectivement.

Selon le principe du diviseur de tension, on a (Figure 4.20.b) [1]:

Si R1 = R2 = R3 = R, et Vcc = E, l'entrée inverseuse du 1<sup>er</sup> comparateur  $V_{e1}^- = \frac{2E}{3}$  V, et

l'entrée non-inverseuse du  $2^{\text{eme}}$  comparateur  $V_{e2}^+ = \frac{E}{3}$  V

La sortie de la bascule ne peut prendre que deux états 0 ou 1. La sortie Vs(t) = 0 ou E

Figure 4.20: Timer NE555. (a) Brochage, (b) schéma synoptique fonctionnel

#### Avec:

1: Masse

2: Declenchement

3: Sortie

4: RAZ

5: Commande

6: Seuil

7: decharge

8: Alimentation

| R | S | Q              | $ar{Q}$ |

|---|---|----------------|---------|

| 0 | 0 | Etat précédent |         |

| 0 | 1 | 1              | 0       |

| 1 | 0 | 0              | 1       |

| 1 | 1 | Interdit       |         |

Tableau 4.1 : Table de vérité d'une bascule RS

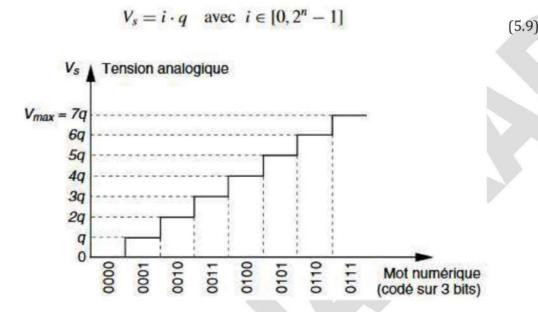

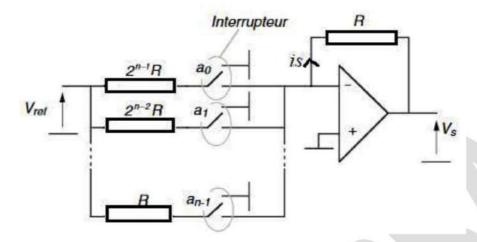

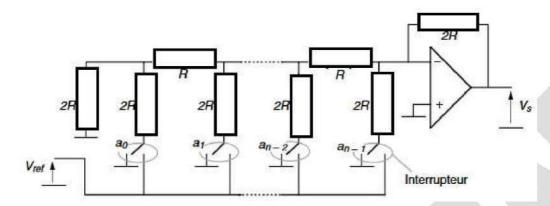

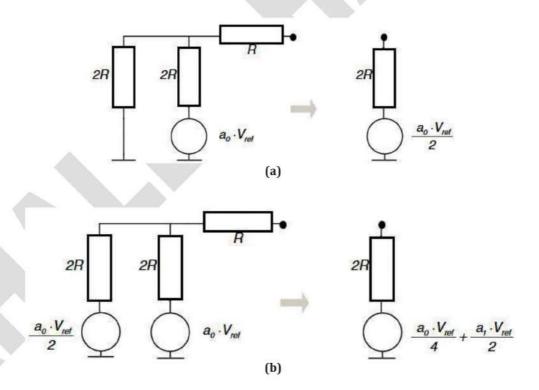

Figure 4.21 : Montage trigger de Schmitt à base du NE555. (a) le circuit, (b) caractéristique de transfert