#### Abstract

The present work reports the simulation and realization of a Digital Phase-Locked Loop (DPLL). The circuit consists of three major blocks: a Phase Frequency Detector (PFD), an RC Low-Pass Filter (LPF), and a Relaxation Voltage Controlled Oscillator (VCO). The analysis, design, and examination of each block were carried out, resulting in a successful assembly of the entire DPLL circuit. The designed PLL was simulated, measured, and then compared with the experimental observations using LM565 IC. The findings demonstrate the PLL capability to achieve frequency synchronization with minimal phase error at the desired frequency of 1 KHz, along with a wide lock-in range.

## Acknowledgment

I would like to express my gratitude to my primary supervisor **Prof. Mouloud CHALLAL** for his guidance and advice throughout this long journey. I would also like to acknowledge my co-supervisor **Dr. Abderrahmane Ouadi** for his mentorship in the project plan and his help in providing me with various laboratory equipment. I would like to express my special thanks to **Omar SAIDI** for his time and assistance, I have learned a lot from you and I appreciate your efforts. I am grateful to my family and my best friends for their encouragement that

motivated me to overcome the challenges.

## **Dedication**

"This work is dedicated to my beloved family and best friends, who believed in me and encouraged me on this long and difficult journey. Words cannot express how grateful I am to each and every one of you!"

## Contents

| Ab  | strac   | t                                             | i   |

|-----|---------|-----------------------------------------------|-----|

| Ac  | know    | ledgment                                      | ii  |

| De  | dicati  | ion                                           | iii |

| Co  | ntent   | ts                                            | v   |

| Lis | st of A | Abbreviations                                 | X   |

| Ge  | neral   | introduction                                  | 1   |

| 1   | Intro   | oduction to Phase Locked Loops                | 3   |

|     | 1.1     | Introduction                                  | 3   |

|     | 1.2     | Operating Principles of PLLs                  | 3   |

|     | 1.3     | PLL Types                                     | 5   |

|     | 1.4     | Building Blocks of PLL                        | 6   |

|     | 1.5     | Phase Detector                                | 6   |

|     |         | 1.5.1 Analog Phase Detectors                  | 6   |

|     |         | 1.5.1.1 Double balanced mixer phase detector  | 7   |

|     |         | 1.5.2 Digital Phase Detectors                 | 8   |

|     |         | 1.5.2.1 XOR Phase Detector                    | 8   |

|     |         |                                               | 10  |

|     | 1.6     | Ι                                             | 13  |

|     |         |                                               | 13  |

|     |         |                                               | 14  |

|     | 1.7     | 0                                             | 15  |

|     |         |                                               | 15  |

|     |         |                                               | 17  |

|     | 1.8     |                                               | 18  |

|     | 1.9     | <b>71</b>                                     | 19  |

|     |         | 11                                            | 21  |

|     | 1.11    | Conclusion                                    | 23  |

| 2   | Desi    | gn and Simulation of a Digital PLL            | 24  |

|     | 2.1     |                                               | 24  |

|     | 2.2     | Design of Phase Frequency Detector (PFD)      | 24  |

|     | 2.3     | Design of Voltage Controlled Oscillator (VCO) | 31  |

|     |         | 2.3.1 Schmitt trigger stage                   | 32  |

|    |        | 2.3.2 Integrator stage                                      | 34 |

|----|--------|-------------------------------------------------------------|----|

|    | 2.4    | Design of the Low-Pass Filter (LPF)                         | 44 |

|    | 2.5    | Entire DPLL Block                                           | 45 |

|    | 2.6    | DPLL Parameters                                             | 46 |

|    |        | 2.6.1 Lock-in Range                                         | 46 |

|    |        | 2.6.2 Settling Time                                         | 46 |

|    |        | 2.6.3 Power Consumption                                     | 47 |

|    | 2.7    | Colusion                                                    | 47 |

| 3  | Exp    | erimental Evaluation: Results and Discussion                | 48 |

|    | 3.1    | Introduction                                                | 48 |

|    | 3.2    | VCO Measurements                                            | 48 |

|    | 3.3    | Measurements of the Entire System                           | 51 |

|    | 3.4    | PLL performance comparison: Implemented PLL vs LM565 IC PLL | 54 |

|    | 3.5    | External Hardware-based 1PPS Signal Use                     | 56 |

|    | 3.6    | PCB Layout of the DPLL                                      | 61 |

|    | 3.7    | Conclusion                                                  | 63 |

| Ge | eneral | Conclusion                                                  | 64 |

| Aj | opend  | ix                                                          | 65 |

| Re | eferen | ces                                                         | 69 |

## **List of Figures**

| 1.1  | A Phase Locked Loop block diagram [2]                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Phase detector characteristics [2]                                                                                                                                                                         |

| 1.3  | Input and output waveforms of a phase detector [2].                                                                                                                                                        |

| 1.4  | VCO characteristics [2].                                                                                                                                                                                   |

| 1.5  | Schematics of a balanced mixer [3]                                                                                                                                                                         |

| 1.6  | Average output characteristics vs the phase error of a mixer. [2]                                                                                                                                          |

| 1.7  | XOR gate symbol. [2]                                                                                                                                                                                       |

| 1.8  | XOR gate operating as a PD. [2]                                                                                                                                                                            |

| 1.9  | Input-output characteristic of XOR PD. [2] 10                                                                                                                                                              |

| 1.10 | Input and output waveforms for a phase difference of $\phi_1 = 180^\circ$ . [2] 10                                                                                                                         |

| 1.11 | PLL block diagram with frequency acquisition aid. [2]                                                                                                                                                      |

|      | Phase Frequency Detector. [2]         11                                                                                                                                                                   |

| 1.13 | $Q_A$ and $Q_B$ states. [2]                                                                                                                                                                                |

| 1.14 | Case of phase difference and frequency difference. [2]                                                                                                                                                     |

| 1.15 | PFD implementation. [2]                                                                                                                                                                                    |

| 1.16 | Schematic of a lead-lag filter. [5]                                                                                                                                                                        |

| 1.17 | Bode plot of a lead-lag filter. [1]                                                                                                                                                                        |

| 1.18 | Schematic of an active lead-lag filter. [1]                                                                                                                                                                |

| 1.19 | Bode plot of an active lead-lag filter. [1]                                                                                                                                                                |

| 1.20 | Simple feedback system. [2]                                                                                                                                                                                |

|      | Barkhausen's criteria for oscillations. [2]                                                                                                                                                                |

|      | VCO tuning characteristic. [2]                                                                                                                                                                             |

| 1.23 | Linear model of simple PLL. [2]                                                                                                                                                                            |

| 1.24 | Frequency response of a high-gain second order PLL. [5]                                                                                                                                                    |

| 1.25 | Block diagram of a PLL synthesizer. [6]                                                                                                                                                                    |

| 1.26 | PLL as a synthesizer. [7]                                                                                                                                                                                  |

| 1.27 | FM demodulator using CD4046. [9]                                                                                                                                                                           |

| 2.1  | Schematic of phase frequency detector in Multisim                                                                                                                                                          |

| 2.1  | Case I: $V_{ref}$ (in red) leads $V_{fb}$ (in blue), $UP$ in green and $DN$ in yellow                                                                                                                      |

| 2.2  | Case II: $V_{ref}$ (in red) lags $V_{fb}$ (in blue), $UP$ in green and $DN$ in yellow                                                                                                                      |

| 2.3  | Case III: $V_{ref}$ (in red) and $V_{fb}$ (in blue) are in phase, UP in green and DN in yellow . 26<br>Case III: $V_{ref}$ (in red) and $V_{fb}$ (in blue) are in phase, UP in green and DN in yellow . 26 |

| 2.5  | Outputs $UP$ (in green) and $DN$ (in yellow) when $V_{ref}$ (in red) and $V_{fb}$ (in blue) are                                                                                                            |

| 2.5  | not equal in frequencies. $27$                                                                                                                                                                             |

| 2.6  | State diagram of the PFD. [1]                                                                                                                                                                              |

| 2.0  | Schematic of phase frequency detector with an output voltage                                                                                                                                               |

| 2.8  | Symbols of enhancement mode MOSFET. [10]                                                                                                                                                                   |

| 2.8  | Final schematic of a PFD with output voltage                                                                                                                                                               |

| 4.1  | r mui senemute of a r r D with output voluge                                                                                                                                                               |

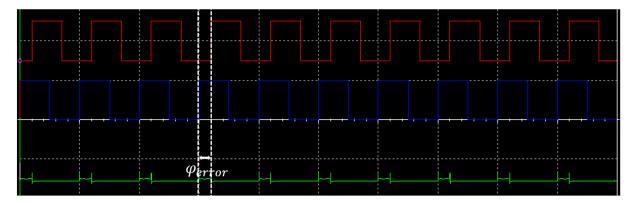

| 2.10 | Case I: PFD output when $V_{ref}$ is leading ( $\omega_{ref} = \omega_{feedback}$ and $\phi_{error} \neq 0$ )  | 31 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.11 | Case II: PFD output when $V_{ref}$ is lagging ( $\omega_{ref} = \omega_{feedback}$ and $\phi_{error} \neq 0$ ) | 31 |

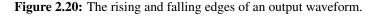

| 2.12 | Schematic of a relaxation VCO.                                                                                 | 32 |

| 2.13 | The Schmitt trigger stage in the VCO schematic                                                                 | 33 |

| 2.14 | Schematic of the integrator when $Q_1$ is open.                                                                | 34 |

| 2.15 | Schematic of the integrator when $Q_1$ is closed                                                               | 35 |

| 2.16 | Schematic of a relaxation VCO with a 1 <i>KHz</i> central frequency.                                           | 37 |

|      | Output signals for different control input voltage.                                                            | 38 |

| 2.18 | 1 KHz triangular and square waves generated at $2.5V$                                                          | 38 |

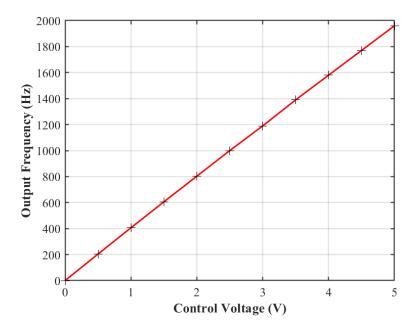

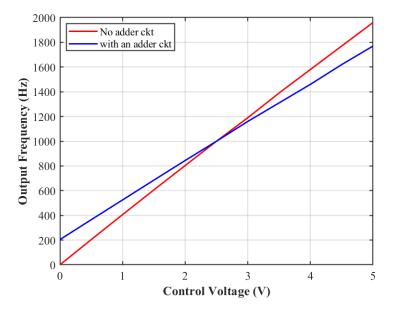

|      | Plot of $f_{out}$ versus $V_{ctrl}$ .                                                                          | 38 |

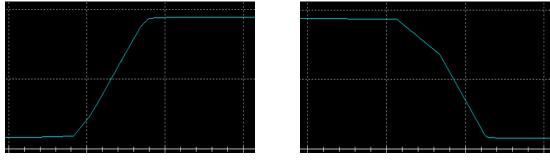

| 2.20 | The rising and falling edges of an output waveform.                                                            | 39 |

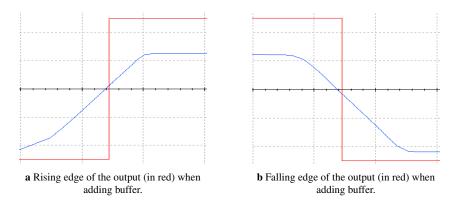

|      | Relaxation VCO with an additional buffer.                                                                      | 40 |

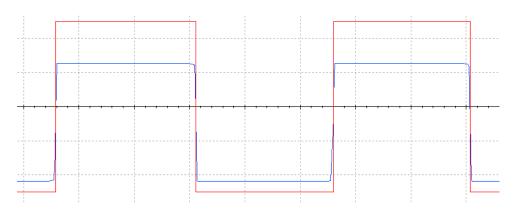

| 2.22 | 1 <i>KHz</i> output waveform with (in red) and without (in blue) a buffer.                                     | 40 |

|      | Effect of adding a buffer on an output signal's rising and falling edges                                       | 41 |

| 2.24 | Schematic of a non-inverting adder.                                                                            | 41 |

| 2.25 | Final schematic of the relaxation VCO.                                                                         | 42 |

|      | Plot of $f_{out}$ versus $V_{ctrl}$ when the non-inverting adder is used                                       | 43 |

|      | Schematic of a simple LPF.                                                                                     | 44 |

| 2.28 | PLL response (in green) versus the reference signal (in red) and the LPF output (in                            |    |

|      | cyan)                                                                                                          | 45 |

| 2.29 | Final schematic of the DPLL.                                                                                   | 46 |

|      |                                                                                                                | 40 |

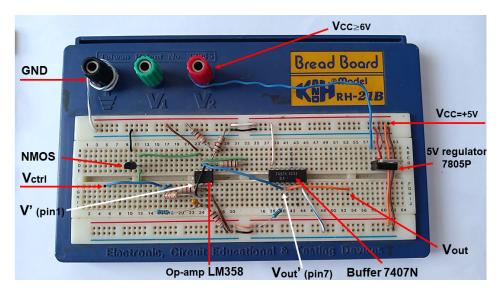

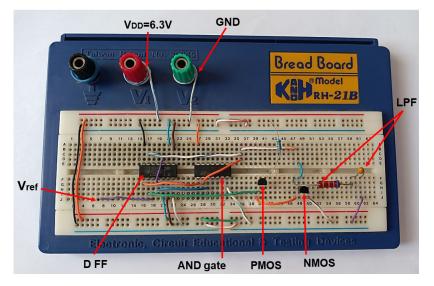

| 3.1  | Implementation of the VCO circuit.                                                                             | 48 |

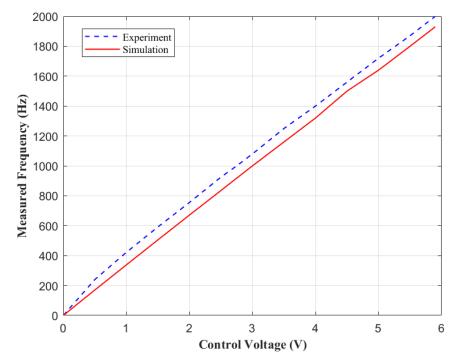

| 3.2  | Plot of $f_{out}$ versus $V_{ctrl}$ .                                                                          | 49 |

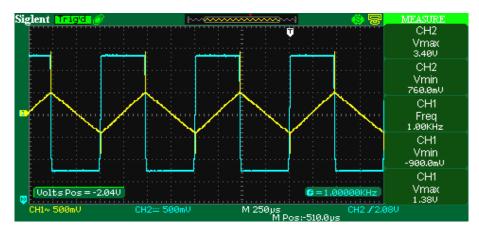

|      | 1KHz square and triangular output waveforms when the buffer is not used                                        | 50 |

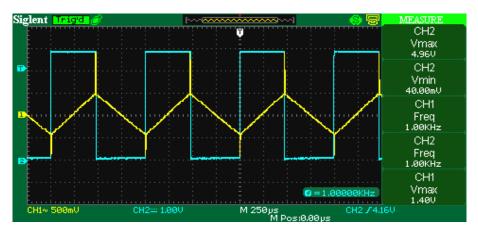

|      | 1KHz square and triangular output waveform when the buffer is used.                                            | 50 |

| 3.4  | Effect of adding a buffer on the rising edge of the output.                                                    | 51 |

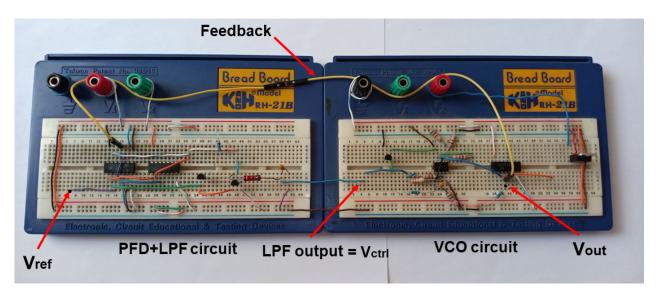

| 3.5  | Implementation of the PFD and the LPF circuit.                                                                 | 51 |

| 3.6  | Implementation of the DPLL circuit.                                                                            | 52 |

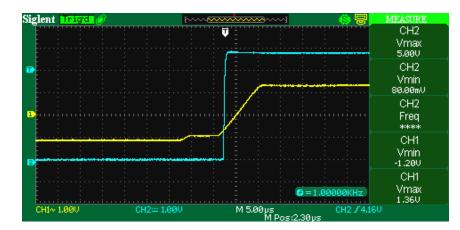

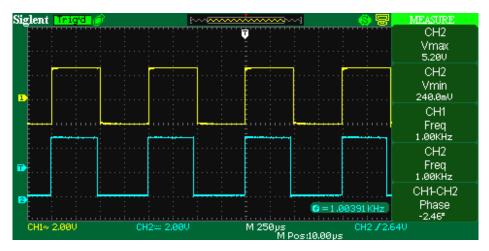

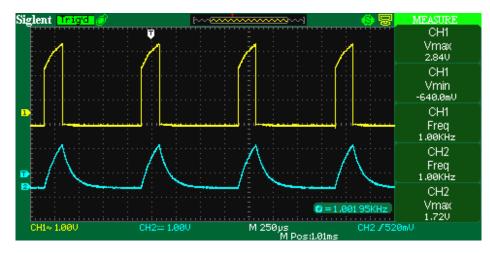

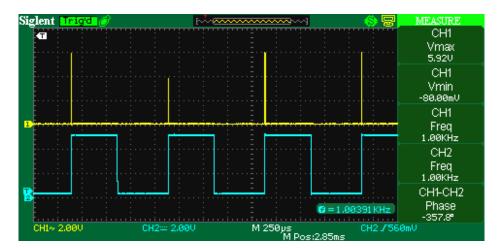

| 3.7  | The output signal (in blue) and the $1 KH_z$ reference (in yellow)                                             | 52 |

| 3.8  | PFD output (in yellow) and LPF output (in blue) at $f_{ref} = 1 KHz$                                           | 53 |

| 3.9  | DN signal (in yellow) and output signal (in blue) at $f_{ref} = 1 KHz$                                         | 53 |

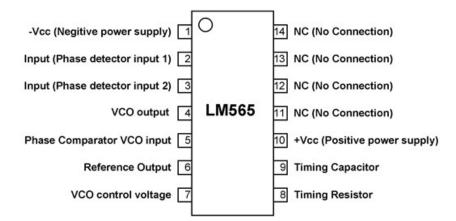

|      | LM565 PLL pin-out.                                                                                             | 54 |

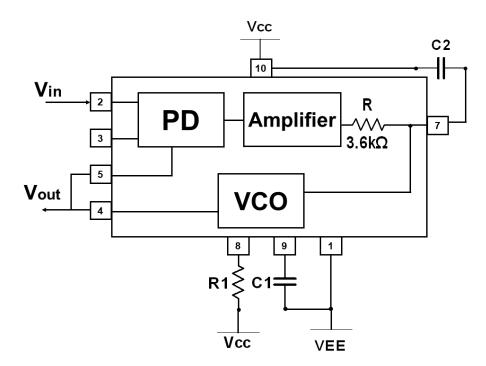

|      | Block diagram of LM565 IC PLL.                                                                                 | 55 |

|      | NEO-M8N GPS Module.                                                                                            | 56 |

|      | External GPS antenna.                                                                                          | 57 |

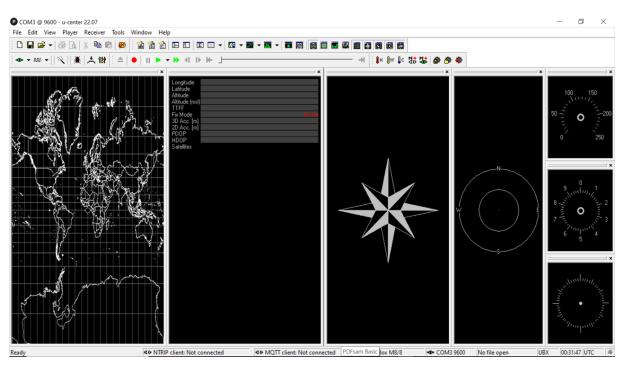

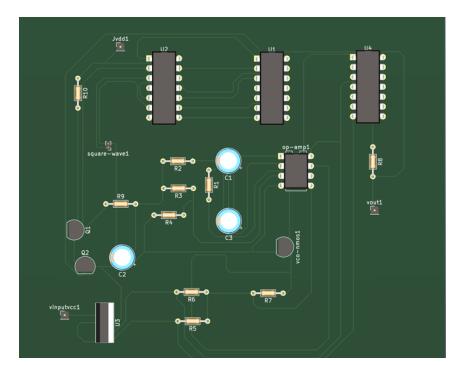

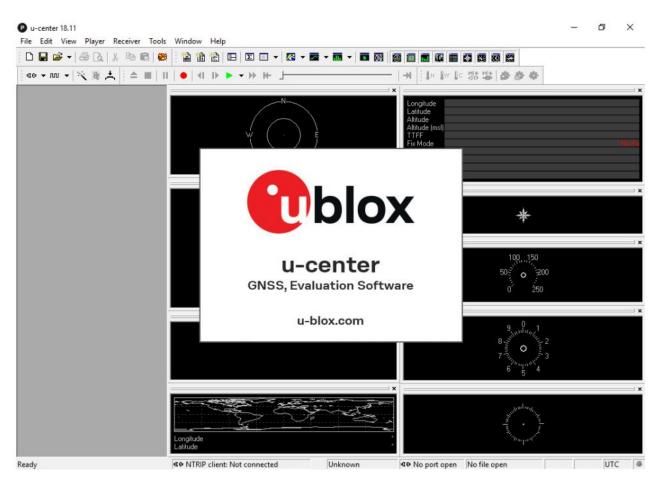

|      | U-center interface.                                                                                            | 58 |

|      | CH340 USB to TTL Converter Module.                                                                             | 58 |

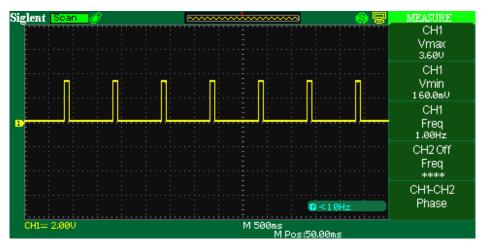

|      | The 1PPS GPS signal received by NEO-M8N                                                                        | 59 |

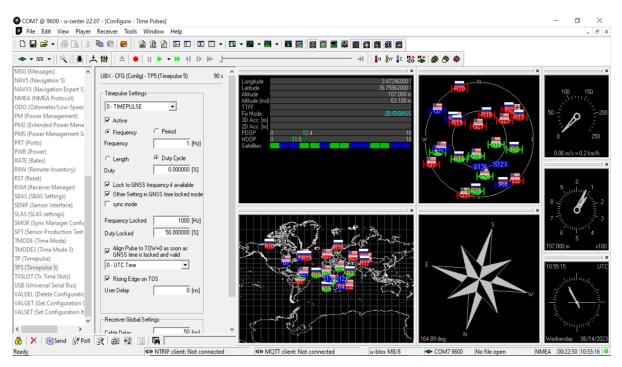

|      | The configuration of the TIMEPULSE parameters.                                                                 | 59 |

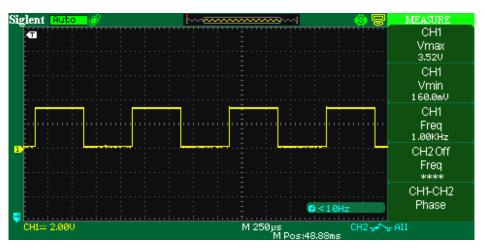

| 3.18 |                                                                                                                | 60 |

|      | PLL Output signal (in blue) and the GPS reference signal (in yellow).                                          | 60 |

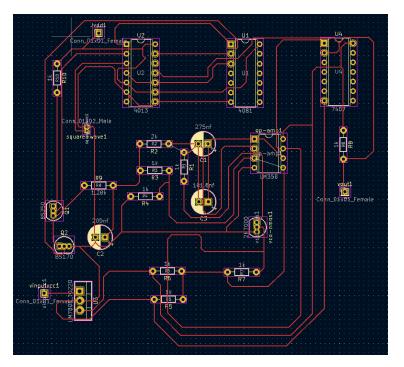

|      | PCB layout of the PLL.                                                                                         | 62 |

| 3.21 | 3D view of the DPLL PCB.                                                                                       | 62 |

| 1    | Multisim logo.                                                                                                 | 65 |

| 2    | U-center interface.                                                                                            | 66 |

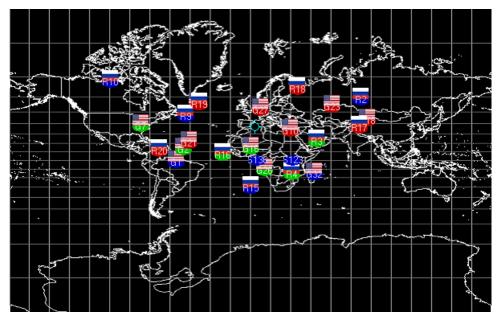

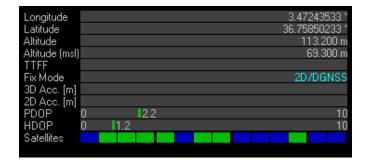

| 3    | The Satellites recognized by the GPS Receiver.                                                                 | 66 |

| 4    | Satellites Position in the sky.                                                                                | 67 |

| 5    | Positional coordinates of the experiment Lab.                                                                  | 67 |

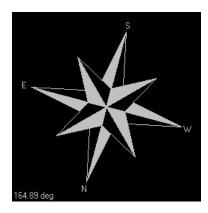

| 6 | Compass information                                                  | 67 |

|---|----------------------------------------------------------------------|----|

| 7 | The precise experiment timing information provided by the GPS module | 67 |

## **List of Tables**

| 1.1 | Truth table of an XOR gate                                                                  | 9  |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.1 | Tristate PFD                                                                                | 27 |

| 2.2 | States of UP, DN and $V_{ctrl}$ with respect to the voltage $V_{G_1S_1}$ and $V_{G_2S_2}$ . | 30 |

| 2.3 | VCO output frequency versus the applied control voltage.                                    | 37 |

| 2.4 | Measured VCO output frequency versus the applied control voltage                            | 43 |

| 2.5 | Calculation of the LPF parameters.                                                          | 45 |

| 3.1 | Measurements of the VCO output frequency versus the applied control voltage                 | 49 |

| 3.2 | Measurements of the phase error using the DPLL                                              | 54 |

| 3.3 | Measurements of the Phase error using LM565 PLL.                                            | 56 |

| 3.4 | Measurements of the Phase error using the 1PPS as a reference signal.                       | 61 |

## **List of Abbreviations**

ADPLL All Digital Phase Locked Loop APLL Analog Phase Locked Loop CMOS Complementary Metal Oxide Semiconductor **CP** Charge Pump **DFF** D Flip Flop **DN** Down **DPLL** Digital Phase Locked Loop FD Frequency Detector FM Frequency Modulation **GNSS** Global Navigation Satellite System GPS Global Positioning System **IF** Intermediate Frequency LF Loop Filter **LO** Local Oscillator LPF Low-Pass Filter NCO Numerically Controlled Oscillator PCB Printed Circuit Board **PD** Phase Detector **PFD** Phase Frequency Detector PLL Phase Locked Loop **PPS** Pulse Per Second **RF** Radio Frequency **SMD** Surface Mount Device **TDC** Time to Digital Converter **THT** Through-Hole Technology TTL Transistor-Transistor Logic **USB** Universal Serial Bus

# VCO Voltage Controlled OscillatorXOR Exclusive OR

## **General introduction**

Synchronization is a vital process in any communication system, it refers to the action of aligning the frequency and timing of a communication system's components. Synchronization ensures reliable communication between a transmitter and a receiver and allows them to communicate in harmony by transmitting and receiving signals accurately without suffering from transmission problems such as data loss, signal distortion, higher bit error rates...etc.

Achieving synchronization in communication systems involves the use of a precise reference clock and different circuits such as phase-locked loops (PLLs).

The reference clock aligns and coordinates the timing and frequency of the different components of the system. A common approach to obtain a precise clock is the use of GPS signals emitted by GPS satellites. The GPS satellites emit highly accurate 1PPS signals that are considered an available and reliable reference for synchronization purposes.

A Phase-Locked Loop plays an important role in the process of synchronization. It is is a feedback control system that generates an output signal whose frequency is aligned with that of a reference signal, ensuring that both signals either maintain a constant phase difference or have no phase difference. This is achieved by continuously comparing the phase and frequency of the input signals and adjusting its local oscillator until the synchronization is fulfilled. PLLs are of different types and are employed in a variety of applications.

In this project, we aim to design a Digital Phase Locked Loop (DPLL) that synchronizes with a clock reference of 1 KHz frequency. The project's work will be distributed across three comprehensive chapters, each addressing specific aspects to achieve the project's objective.

The following is a concise overview of each chapter's content and focus.

#### • Chapter 1:

In the first chapter, we will explore the theoretical foundation and the generalities related to Phase Locked Loops, including their operating principles, types and classes, major building blocks, performance characteristics, and their wide-ranging applications. This chapter will provide a comprehensive understanding of Phase Locked Loops, laying the groundwork for the next chapters.

#### • Chapter 2:

In this chapter, we will present the design and implementation of a Digital or Mixed-signal Phase Locked Loop (DPLL) using the simulation software Multisim. The design and implementation process of the DPLL will involve designing and simulating the three main blocks: PFD, LPF, and VCO. The performance and evaluation of the system will be examined by constructing and testing the whole system in simulation.

### • Chapter 3:

The last chapter will include the practical implementation of the PLL circuit and report the experimental results of testing the PLL ability to acquire the lock with the 1KHz reference signal and the 1PPS GPS signal captured by a GPS receiver. A comparison between the designed PLL and an IC PLL will also take place in this chapter.

## **Chapter 1**

## **Introduction to Phase Locked Loops**

### **1.1 Introduction**

A Phase Locked Loop, or a PLL, is a closed-loop feedback control circuit that generates an output signal whose phase is related to its input signal (also called reference signal). In other words, a PLL synchronizes the frequency of an output signal with a reference signal and ensures they have either a constant phase difference or no phase difference [1].

In modern technology, PLLs are often implemented as integrated circuits (ICs), where various components of the PLL are integrated into a single chip. This allows for easy implementation of the PLL in a wide range of electronic systems, with minimal external components required and hence a small compact package. PLLs are widely used in wireless or radio frequency (RF) applications, including WIFI routers, broadcast radios, televisions, and mobile phones.

In this chapter, we will cover the most important principles of Phase Locked Loops, including their operating principle, types and classes, building blocks, performance, applications and more.

## **1.2 Operating Principles of PLLs**

Phase Locked Loops are mainly used for synchronization, when two signals have a phase difference, the PLL causes the output signal to keep tracking the reference signal until the phase error between the two is zero or remains constant. The term "Locked" in PLL refers to the fact that the output signal is held in phase with the input signal, thus the locking process is the goal of using a PLL system [1].

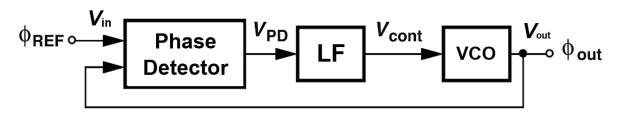

Understanding the operating principle of a PLL requires including the basic building blocks that construct it. The PLL consists of three main basic blocks:

- A phase detector (PD).

- A loop filter (LF).

- A voltage-controlled oscillator (VCO).

Figure 1.1 depicts a block diagram of a unity feedback PLL, where the input of the system is the reference signal's phase  $\phi_{ref}$  and the output is the VCO signal's phase  $\phi_{out}$ .

Figure 1.1: A Phase Locked Loop block diagram [2]

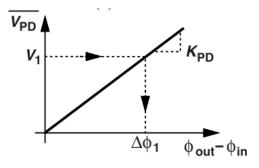

The Phase Detector (PD) is used to compare the output signal and the reference signal and then generates a voltage signal called  $V_{PD}$ , the average of this signal is proportional to the phase error (or phase difference)  $\phi_e$  as shown in Figure 1.2.

Figure 1.2: Phase detector characteristics [2].

In a simple mathematical equation, we can write:

$$\overline{V_{PD}}(t) = K_{PD}\phi_e \tag{1.1}$$

where  $K_{PD}$  is the gain of the Phase Detector. Its unit is (Volt/rad). Note that the proportionality  $K_{PD}$  is satisfied within a limited range.

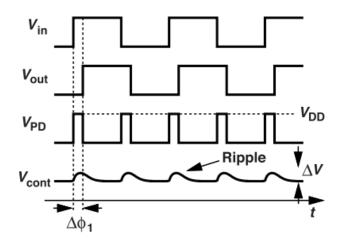

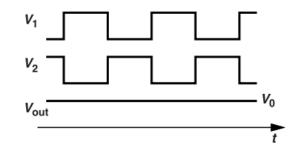

Figure 1.3: Input and output waveforms of a phase detector [2].

Figure 1.3 shows the output voltage  $V_{PD}$  of the PD and the control voltage  $V_{cont}$  generated by the LF when two digital input signals  $V_{in}$  and  $V_{out}$  are applied to the PLL. Note that these inputs are not in phase.

The output signal of the PD is an AC signal, which means that it is composed of a DC value and some harmonics that must be canceled by the Loop Filter (LF). The LF is responsible for extracting the control voltage  $V_{cont}$  which is the average value of the phase error signal  $V_{PD}(t)$ . In other words, the LF smooths and flattens the signal  $V_{PD}(t)$  and makes it look like a DC value [1].

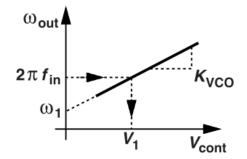

The Voltage Controlled Oscillator (VCO) is an electronic oscillator that generates an output signal whose frequency can be adjusted by varying the input voltage applied to it. In this case, the input signal that is controlling the VCO is  $V_{cont}$ . The angular frequency of a VCO is given by the following formula:

$$\omega_{out}(t) = K_{VCO}V_{cont} + \omega_0 \tag{1.2}$$

$\omega_0$  is the free running frequency of the VCO in (*rad*) and *K*<sub>VCO</sub> is the gain of the VCO, given in (*rad*.*Hz*/*Volt*) [1].

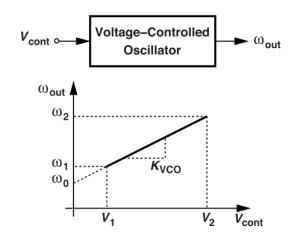

Figure 1.4: VCO characteristics [2].

The VCO characteristics are depicted in Figure 1.4, where there is a linear relationship between  $\omega_{out}$  and  $V_{cont}$ .

If the reference signal leads or lags the feedback signal, then an error signal is generated by the PD, which is then filtered by the LF, this will cause the VCO to either increase its frequency (when the input signal is leading) or decrease its frequency (when the input is lagging). Thus, the feedback loop in the PLL ensures that the phase difference  $\phi_e$  between the input and output signals remains constant or converges to zero, then the output signal will remain in phase with the input signal.

## 1.3 PLL Types

Phase Locked Loops are mainly classified into 3 categories: Analog PLLs, Digital PLLs, and All Digital PLLs. Each type is identified by the internal components that build up the PLL system [1].

• Analog Phase Locked Loop (APLL)

It's also known as a Linear PLL (LPLL), this type of PLL contains only analog devices. The Phase Detector (PD) is known as an analog multiplier (four quadrant multiplier). The Loop filter contains passive or active components like resistors and capacitors. Moreover, an analog VCO is integrated with the system to generate the desired frequencies.

• Digital Phase Locked Loop (DPLL)

This type of PLL contains both analog and digital components. A Digital PLL has a digital Phase Detector including XOR phase detector, JK flip-flop phase detector, Phase Frequency Detector (PFD). The loop filter is normally based on passive elements, and the VCO is analog in nature. Digital phase-locked loops are typically smaller than analog PLLs, due to their digital phase detector and loop filter.

#### • All Digital Phase Locked Loop (ADPLL)

This PLL does not contain any passive element, it is only built from digital components. The phase detector is digital and known as Time to Digital Converter (TDC), the loop filter is also digital. Concerning the VCO, it is replaced by an NCO which is a Numerically Controlled Oscillator.

We can also mention other types of PLL such as Software PLL and IC PLL.

In the software PLL, a hardware platform like a Digital Signal Processor (DSP) is needed to perform the required calculations. The signal processing algorithm takes a reference signal and a feedback signal from a local oscillator, calculates the phase difference between the two signals, and adjusts the frequency of the local oscillator to minimize the phase difference.

In the IC PLL, all components are integrated into a single chip. Some references are ADF4106 from Analog Devices and CD4046B, LM565 from Texas Instrument.

## 1.4 Building Blocks of PLL

As mentioned in the previous sections, a PLL is a feedback system that compares the phase of the input reference frequency to the phase of the output frequency and adjusts the output frequency based on this information. The PLL block diagram shown in Figure 1.1, represents the interconnection of the following circuit's building blocks: Phase Detector (PD), Loop Filter (LF), Voltage Controlled Oscillator (VCO), and a frequency Divider  $(\div N)$  for some applications. Understanding how these components work and interact will help us understand how a PLL can be utilized in a variety of applications. In the following sections, each block will be discussed in detail.

## 1.5 Phase Detector

A Phase Detector is an electronic circuit that compares the phases of two signals and produces an output signal that represents the phase difference between them. Phase detectors are used in many different applications, such as frequency synthesis and communications systems. There are several types of phase detectors, including analog and digital types. Analog phase detectors are usually built with operational amplifiers, diodes, or other analog components, whereas digital phase detectors are built with logic gates or other digital components.

### **1.5.1** Analog Phase Detectors

An analog multiplier is an electronic circuit that multiplies two analog signals together to produce an output signal that is proportional to their product.

#### 1.5.1.1 Double balanced mixer phase detector

One common type of analog phase detector is the balanced mixer, which is also known as the "Gilbert cell" phase detector. Figure 1.5 shows the circuit diagram of a balanced mixer.

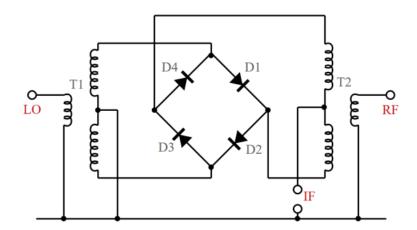

Figure 1.5: Schematics of a balanced mixer [3].

A balanced mixer is specifically designed to perform frequency conversion or mixing operations in radio frequency (RF) applications, it is used in Analog PLLs (APLL). This circuit has two input signals of different frequencies, the first input is applied at the RF node, this signal represents the reference signal. While the second input is applied at the LO (Local oscillator) node, note that this signal is the VCO output. The output signal is then produced at the IF nodes (Intermediate frequency), it is the sum and difference of the input frequencies [4].

Let's suppose that the RF and the LO inputs are sinusoidal, and are expressed as the following,

$$V_{RF}(t) = A_{RF}sin(\omega_{RF}t + \theta_{RF})$$

(1.3)

$$V_{LO}(t) = A_{LO}sin(\omega_{LO}t + \theta_{LO})$$

(1.4)

Then, the output signal  $V_{IF}(t)$  is the multiplication of  $V_{LO}(t)$  and  $V_{RF}(t)$ . Thus, the following equations are found.

$$V_{IF}(t) = V_{LO}(t) \times V_{LO}(t)$$

$$V_{IF}(t) = A_{LO}sin(\omega_{LO}t + \theta_{LO}) \times A_{RF}sin(\omega_{RF}t + \theta_{RF})$$

Some trigonometry manipulation leads to equation 1.5.

$$V_{IF}(t) = \frac{A_{LO}A_{RF}}{2} \left[ \cos((\omega_{LO} + \omega_{RF})t + \theta_{LO} + \theta_{RF}) + \cos((\omega_{LO} - \omega_{RF})t + \theta_{LO} - \theta_{RF}) \right]$$

(1.5)

Note that the signal  $V_{IF}(t)$  contains two terms. The first term is  $cos((\omega_{LO} + \omega_{RF})t + \theta_{LO} + \theta_{RF})$ , which is contains high-frequency harmonics since it is the sum of  $\omega_{LO}$  and  $\omega_{RF}$ .

This term will be filtered using the Loop Filter that comes after the PD block. The remaining term is the desired one, since  $cos((\omega_{LO} - \omega_{RF})t + \theta_{LO} - \theta_{RF})$  contains the difference of the signals' phases.

If the radian frequencies of  $V_{RF}(t)$  and  $V_{LO}(t)$  are equal, then the output signal after filtering becomes,

$$V_{IF}(t) = \frac{A_{LO}A_{RF}}{2}cos(\theta_{LO} - \theta_{RF})$$

(1.6)

Equation 1.6 clearly shows that the output signal is proportional to the phase difference between the input signals, thus the Gilbert cell detects the phase difference by generating an output signal that contains information about the phase error.

Equation 1.6 is plotted in Figure 1.6, it is clear when  $\phi_1$  (which is  $\theta_{LO} - \theta_{RF}$ ) is equal to *zero*, the PD loses its ability to measure the phase difference. The PD output reaches a maximum at  $\phi_1 = 90^\circ, 270^\circ...$  etc. [2]

Figure 1.6: Average output characteristics vs the phase error of a mixer. [2]

#### **1.5.2 Digital Phase Detectors**

A digital Phase Detector is a circuit that compares the phases of two digital signals and generates an output signal that represents their phase difference. The output signal is a pulse or a digital signal with two possible states, high and low, and with a certain pulse width. The width of the output pulse is proportional to the phase difference between the two input signals.

Digital PDs are more accurate, have a wider dynamic range, and are more immune to noise and interference. They are also easier to integrate into digital circuits. Digital PDs can be implemented using some logic circuits, including Exclusive OR (XOR) gates, JK flip flops, and phase frequency detectors PFD. We will mainly focus on the XOR phase detector and the PFD. [1]

#### 1.5.2.1 XOR Phase Detector

XOR is a digital logic gate that has two inputs, the output of an XOR is either a logical "1" or "HIGH" if the two input values are different, or a logical "0" or "LOW" if the two input are similar. The symbol and truth table for the XOR gate are shown respectively in Figure 1.7 and Table 1.1. [4]

Figure 1.7: XOR gate symbol. [2]

| <i>V</i> <sub>1</sub> | $V_2$ | Vout |

|-----------------------|-------|------|

| 0                     | 0     | 0    |

| 0                     | 1     | 1    |

| 1                     | 0     | 1    |

| 1                     | 1     | 0    |

Table 1.1: Truth table of an XOR gate

In Figure 1.7, the input  $V_1$  is the reference signal, while  $V_2$  is the feedback signal (output of the VCO), the output signal  $V_{out}$  is then fed to the LF.

Since the XOR gate outputs a logical "HIGH" if either of its inputs is 1, but not at the same time, it can be used as a phase detector to detect the phase difference between them.

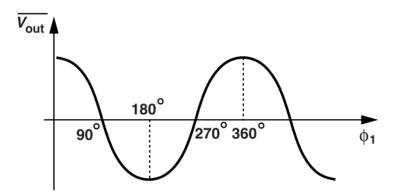

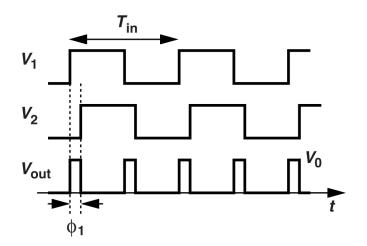

Let's suppose that the inputs  $V_1$  and  $V_2$  are applied to the XOR gate as shown in Figure 1.8, it is clearly shown the output signal  $V_{out}$  is "HIGH" only when  $V_1$  leads  $V_2$ , and therefore, the XOR PD is generating a series of pulses at *twice* the input frequency whose width is proportional to the phase error  $\phi_1$ . The computation of the average of  $V_{out}$  results in a linear relationship with  $\phi_1$ , this relationship is mentioned in the previous sections, it is the gain  $K_{PD}$ . [2]

Figure 1.8: XOR gate operating as a PD. [2]

The following equations define the relationship between the average of the PD output and the phase error.

$$\overline{V_{PD}} = \overline{V_{out}} = \frac{Area of the 2 pulses}{Period of V_{in}}$$

$$\overline{V_{PD}} = 2V_0 \frac{T\phi_1}{2\pi} \frac{1}{T}$$

$$\overline{V_{PD}} = \frac{V_0}{\pi} \phi_1 = K_{PD} \phi_1 \qquad (1.7)$$

Thus, if  $V_0$  is the voltage level of the output signal, the gain of the XOR phase detector is,

$$K_{PD} = \frac{V_0}{\pi} (Volt/rad) \tag{1.8}$$

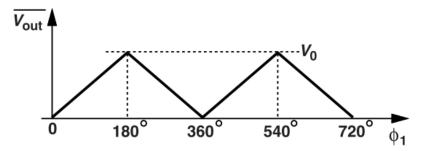

If we plot the characteristics of  $\overline{V_{PD}}$  versus  $\phi_1$ , we get the waveform shown in Figure 1.9

Figure 1.9: Input-output characteristic of XOR PD. [2]

Note that for  $\phi_1 = 0$ , the PD characteristic begins at zero which means that the two inputs are in phase. Then, the curve is linearly increasing as the phase error increases. Another important note is that the average  $\overline{V_{PD}}$  reaches its maximum  $V_0$  when the phase difference is exactly 180° (See Figure 1.10). After this point, the curve falls linearly, returning to zero at  $\phi_1 = 360^\circ$  and the behavior repeats and becomes periodic. [2]

**Figure 1.10:** Input and output waveforms for a phase difference of  $\phi_1 = 180^{\circ}$ . [2]

One drawback of the XOR PD is the limited phase range. This PD can only detect phase differences between  $0^{\circ}$  and  $180^{\circ}$  degrees as depicted in Figure 1.9. Beyond this range, the output becomes ambiguous because of the symmetry and cannot be used to determine the actual phase difference, which means that it will not be possible to know which signal is leading or lagging.

#### **1.5.2.2** Phase Frequency Detector (PFD)

A Phase Frequency Detector (PFD) is a digital circuit that compares the phase and frequency of the reference signal, which is fixed in frequency, and the feedback signal and produces an output signal that indicates the difference between the two. The ability to accurately measure and correct the phase and frequency of signals is an essential property of the PFD in PLL design.

Figure 1.11: PLL block diagram with frequency acquisition aid. [2]

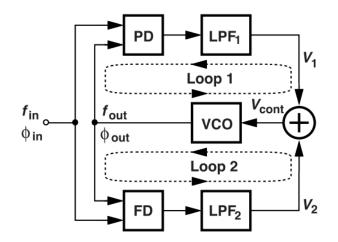

Basically, a PFD operates as a frequency detector FD and a phase detector PD at the same time. As illustrated in Figure 1.11, a PLL is realized with two loops that are interrelated and both share the same VCO.

In Loop 2, The FD measures the difference in frequency when  $f_{ref}$  and  $f_{out}$  are not equal, and then it adjusts the VCO with negative feedback. This will force  $f_{out}$  to converge toward  $f_{ref}$  until  $|f_{out} - f_{ref}| \approx 0$ . As  $|f_{out} - f_{ref}|$  converges to zero, then the PD in Loop 1 begins to generate a meaningful dc value that guarantees phase-locking. [2]

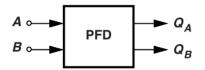

As shown in Figure 1.12, a PFD can be represented as a system whose inputs are the *reference signal* (*A*) and the *feedback signal* (*B*) and generates two outputs  $Q_A$  and  $Q_B$ , their state is either "LOW" or "HIGH" indicating which input signal that is leading or lagging.

Figure 1.12: Phase Frequency Detector. [2]

The PFD operation is based on two principles,

- 1. if  $Q_A$  and  $Q_B$  are LOW and a rising edge occurs on A, then  $Q_A$  goes HIGH while  $Q_B$  remains LOW.

- 2. If  $Q_A$  is HIGH and a rising edge occurs on *B*, then  $Q_A$  is LOW.

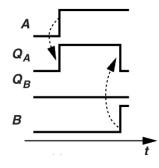

This concept is well illustrated in Figure 1.13.

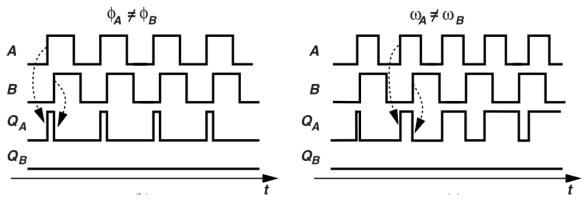

Figure 1.13:  $Q_A$  and  $Q_B$  states. [2]

To understand the concept of  $Q_A$  and  $Q_B$  states and their relationship with the phase error, two cases are considered.

If  $\omega_A = \omega_B$ , but  $\phi_A \neq \phi_B$ , as shown in Figure 1.14, since *A* leads *B*, the rising edge of *A* occurs first, then  $Q_A$  goes HIGH while  $Q_B$  remains LOW, once the rising edge of *B* occurs,  $Q_A$  goes LOW. This generates a pulse whose width is equal to the phase difference. Note that the same scenario will happen if *A* lags *B* resulting in a pulse on  $Q_B$ .

Now, if  $\omega_A \neq \omega_B$ , a series of pulses will be generated on  $Q_A$  if  $\omega_A > \omega_B$  thus  $Q_A$  exhibits a greater average than  $Q_B$ . The opposite happens if  $\omega_A < \omega_B$ . [2]

Figure 1.14: Case of phase difference and frequency difference. [2]

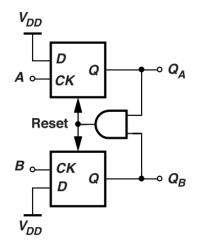

A basic PFD consists of two resettable D flip-flops and an AND gate. The *D* input of both DFFs is set at a logical ONE ( $V_{DD}$ ), the clock inputs are connected to signals *A* and *B*, where *A* and *B* are the reference and the feedback signals. The outputs of the two DFFs are  $Q_A$  and  $Q_B$ , they are also called *UP* and *DN*. These signals are connected to the inputs of the AND gate, the output of the latter is attached with *RESET* of the DFFs.

If A is leading then UP is HIGH and DN is LOW. However, If B is leading, then UP is LOW and DN is HIGH. If the two signals are in phase, then UP and DN will be HIGH, then the AND gate generates a ONE, forcing the DFFs to reset them.

Figure 1.15: PFD implementation. [2]

Most PFDs are not directly connected to the loop filter, another block is included between the two, it is called a Charge Pump (CP). More details will be provided about the design of the PFD and the CP in chapter 2.

### 1.6 Loop Filter

In PLL design, a loop filter is a crucial block in the circuit, it is placed between the PD and VCO. The primary function of the LF is to filter out the noise and the unwanted ac harmonics present at its input (harmonics from the output of the PD), to provide a smooth dc output that is proportional to the phase error.

The dc output is then fed to the VCO to regulate the feedback output frequency. Since the LF passes the low frequencies and blocks the higher frequencies, it is then considered a Low Pass Filter LPF. Several types of loop filters are used in PLL circuits, such as passive RC filters, active filters, and digital filters. The choice of filter type depends on the application and the PLL type. [1]

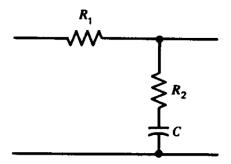

#### **1.6.1** Passive Filters

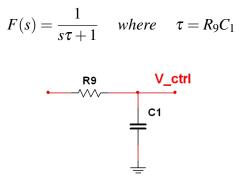

In many PLL designs, first-order loop filters are used, a common type of passive LPFs is the Lead-Lag filter. The schematic of the passive lead-lag filter is shown in Figure 2.27,

Figure 1.16: Schematic of a lead-lag filter. [5]

The transfer function F(s) of a lead-lag filter has a zero and a pole, it is given by the following

equations.

$$F(s) = \frac{1 + sR_2C}{1 + s(R_1 + R_2)C}$$

By replacing  $R_1C$  and  $R_2C$  by the time constants  $\tau_1$  and  $\tau_2$  respectively, the transfer function F(s) becomes

$$F(s) = \frac{1 + s\tau_2}{1 + s(\tau_1 + \tau_2)} \tag{1.9}$$

The frequency response function of a lead-lag filter has a pole at  $\omega = \frac{1}{(R_1+R_2)C}$  and a zero at  $\omega = \frac{1}{R_2C}$ . The pole produces a phase lag, while the zero provides a phase lead. The gain of the transfer function is calculated and given by,

$$|F(s)| = \sqrt{\frac{1 + \omega^2 (R_2 C)^2}{1 + \omega^2 (R_1 + R_2)^2 C^2}}$$

(1.10)

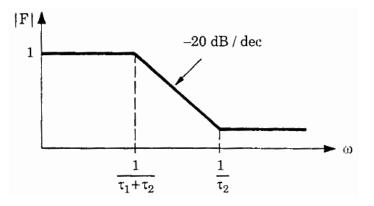

Therefore, at lower frequencies, the gain |F(s)| is 1. But at higher frequencies, the filter acts as a resistive divider with gain |F(s)| equal to  $\frac{R_2}{R_1+R_2}$ . Figure 1.17 depicts the bode diagram of an ideal lead-lag filter.

Figure 1.17: Bode plot of a lead-lag filter. [1]

#### **1.6.2** Active Filters

Active filters are another common type that helps to ensure the stability and accuracy of the system by removing unwanted noise and signals from the input and output signals. The schematic of the active lead-lag filter is shown in Figure 1.18.

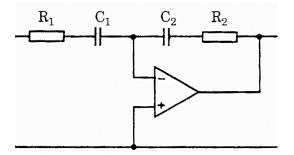

Figure 1.18: Schematic of an active lead-lag filter. [1]

The transfer function F(s) of the active lead-lag filter is similar to the passive's one, it is given by the following equations.

$$F(s) = K_a \frac{1 + sR_2C_2}{1 + sR_1C_1}$$

As it was done in the passive filer,  $R_1C_1$  and  $R_2C_2$  are replaced by the time constants  $\tau_1$  and  $\tau_2$  respectively, the transfer function F(s) is shown in equation 1.11. The term  $K_a$  represents is the gain, and it is equal to  $C_1/C_2$ .

$$F(s) = K_a \frac{1 + s\tau_2}{1 + s\tau_1}$$

(1.11)

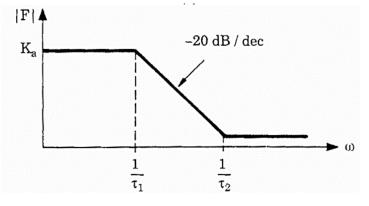

The amplitude response of the active lead-lag filter is depicted in Figure 1.19

Figure 1.19: Bode plot of an active lead-lag filter. [1]

### 1.7 Voltage Controlled Oscillator

Before jumping straight into VCOs, it is important to understand some generalities about oscillators. In the next subsection, some essential information related to oscillators is discussed.

#### 1.7.1 Generalities About Oscillators

An oscillator is an electronic circuit that is able to generate periodic signals, such as a sine wave, square wave, or triangle wave. In practice, an oscillator is a system that consists of an amplifier and negative feedback.

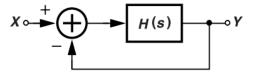

Figure 1.20: Simple feedback system. [2]

Figure 1.20 depicts the block diagram of a simple feedback system whose closed-loop transfer function is given by,

$$\frac{Y(s)}{X(s)} = \frac{H(s)}{1 + H(s)}$$

(1.12)

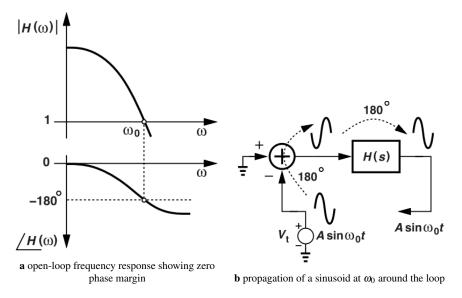

In order to create oscillations, the negative-feedback system should be unstable, this property is the necessary condition for an oscillation. It is clear that if the denominator is zero, this implies H(s) = -1. Therefore, If H(s) = -1 at a certain frequency  $\omega_0$ , that is  $H(j\omega_0) = -1$ , then the open-loop frequency response exhibits a unity magnitude and a 180° phase shift at  $\omega_0$ . These conditions are called "*Barkhausen's*" criteria for oscillation and are summarized in equation 1.13 and 1.14 and Figure 1.21a. [2]

$$|H(j\omega_0)| = 1 \tag{1.13}$$

$$\angle H(j\omega_0) = 180^\circ \tag{1.14}$$

In Figure 1.21b, an example of a sinusoid is shown, where it's really important to note that the feedback signal is in phase with the test voltage,  $V_t$ . Thus, the loop contains a 180° phase shift due to the negative feedback and another 180° phase shift due to the open loop transfer function H(s) resulting in the same sinusoid.

Figure 1.21: Barkhausen's criteria for oscillations. [2]

Different types of oscillators exist, the classification is based on the shape of the output waveform, the nature of the frequency of the output waveform...etc

If the shape is of concern, they can be divided into two groups: harmonic oscillators (also known as linear oscillators) and relaxation oscillators.

A harmonic oscillator is a circuit that generates a sinusoidal waveform at a fixed frequency. Reactive components, such as inductors or capacitors, and resistors, are typically used in the circuit. Examples of harmonic oscillators in electrical systems include LC oscillators, crystal oscillators, and RC oscillators. While a relaxation oscillator is a circuit that generates a non-sinusoidal waveform including triangular, square, and sawtooth waveforms. The circuit typically consists of a feedback loop that includes a non-linear element for switching, such as a diode or transistor, and a reactive component for storing and releasing energy, such as a capacitor.

Moreover, if the classification depends on the nature of the frequency of the output waveform, then two types are mentioned: fixed frequency oscillators and variable or tunable frequency oscillators. The tunable frequency oscillators allow the frequency of the output signal to be adjusted over a certain range by just tuning the applied voltage. One example of these oscillators is the voltage-controlled oscillator (VCO).

#### **1.7.2 VCO Parameters and Models**

As explained in the previous subsection, the frequency of an oscillator can be adjusted by either varying electronically a parameter within the oscillator, such as a resistance, a capacitance, or an inductance. This technique is used for fixed-frequency oscillators. If the control is a voltage quantity, we call the circuit a voltage-controlled oscillator (VCO).

The VCO is characterized by its tuning range and its gain, where the frequency is linearly proportional to the voltage applied to its control input. This relationship is described by equation 1.15, [2]

$$\omega_{out} = K_{VCO}V_{cont} + \omega_0 \tag{1.15}$$

where  $K_{VCO}$  is the "gain" of the VCO and is expressed in rad/s/V or Hz/V and  $\omega_0$  is the free running frequency of the VCO. Figure 1.22 depicts the VCO tuning range characteristics, where  $\omega_{out}$  varies linearly with  $V_{cont}$  in the range  $[V_1; V_2]$  with a slope  $K_{VCO}$ .

Figure 1.22: VCO tuning characteristic. [2]

Some important parameters of VCOs are the tuning range where the VCO must be adjustable over the range that the PLL is expected to operate over. The tuning gain is also of concern, it is the tuning shift for a given change in voltage. The gain of a VCO affects some of the overall loop design considerations and calculations. Phase noise is another essential performance parameter, it refers to the phase fluctuations or jitter in the output signal, the factors that effect the phase noise are device noise, power supply noise, and circuit non-idealities. [3]

According to Behzad Razavi [2, p. 45], VCOs can be represented by one of three models:

- 1. A static system characterized by  $\omega_{out} = K_{VCO}V_{cont} + \omega_0$  if the output frequency is of interest.

- 2. A system generating  $V_{out} = V_0 cos[\omega_0 t + K_{VCO} \int V_{cont}(t) dt]$  if the output waveform is of interest.

- 3. If the phase error  $\phi_e$  is of interest, It is an ideal integrator characterized by

$$\frac{\phi_e}{V_{cont}} = \frac{K_{VCO}}{s} \tag{1.16}$$

In PLL design, the last model is interesting, because it relates between the  $V_{cont}$  that is generated by the LF and the phase error  $\phi_e$  produced at the output of the VCO. The VCO can be modeled as an integrator because the output frequency is proportional to the integral of the control voltage  $V_{cont}$  over time. Note that this model provides a simple and intuitive way to analyze and design VCO circuits.

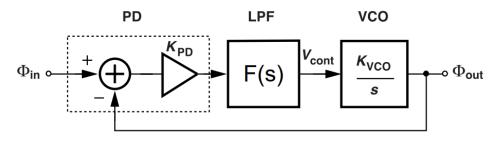

### **1.8 PLL Transfer Function**

In order to evaluate the stability of the PLL loop, the filtering properties, and the behavior of the loop in the time domain, the transfer function must be determined. The Transfer function H(s) which is defined as  $\phi_{out}/\phi_{in}$  is derived after modeling each block of the PLL loop.

- The mathematical model of the phase detector is simply a gain block  $K_{PD}$

- The loop filter is represented with its own transfer function F(s), it has been derived in equation 1.9 for a lead-lag filter.

- The VCO is considered an integrator with a gain  $K_{VCO}$ , thus its transfer function is  $K_{VCO}/s$

The figure shown below represents the linear model of a PLL, where each block is represented in the *s* domain.

Figure 1.23: Linear model of simple PLL. [2]

The depicted block diagram in Figure 1.23 allows to find the open loop transfer function, H'(s), it is given by the following formula,

$$H'(s) = \frac{K_{PD}K_{VCO}F(s)}{s} \tag{1.17}$$

It follows that the closed-loop transfer function is given by

$$H(s) = \frac{\phi_{out}}{\phi_{in}} = \frac{H'(s)}{1 + H'(s)} = \frac{\frac{K_{PD}K_{VCO}F(s)}{s}}{1 + \frac{K_{PD}K_{VCO}F(s)}{s}}$$

multiplying the numerator and the denominator by s results in equation 1.18

$$H(s) = \frac{K_{PD}K_{VCO}F(s)}{s + K_{PD}K_{VCO}F(s)}$$

(1.18)

Therefore, for a passive lead-lag filter, the closed-loop transfer function is

$$H(s) = \frac{K_{PD}K_{VCO}\frac{1+s\tau_2}{1+s(\tau_1+\tau_2)}}{s+K_{PD}K_{VCO}\frac{1+s\tau_2}{1+s(\tau_1+\tau_2)}}$$

(1.19)

In control theory, it is a common to write the denominator of H(s) in the normalized form, where

$$Denominator = s^2 + 2\zeta \omega_n s + \omega_n^2$$

$\omega_n$  is called the natural frequency and  $\zeta$  is the damping factor. So from the transfer function of the lead-lag filter given in equation 1.19, one can show that  $\omega_n$ ,  $\zeta$  and H(s) are as follows,

$$\omega_n = \sqrt{\frac{K_{PD}K_{VCO}}{\tau_1 + \tau_2}}, \quad \zeta = \frac{\omega_n}{2} \left(\tau_2 + \frac{1}{K_{PD}K_{VCO}}\right)$$

(1.20)

$$H(s) = \frac{s\omega_n \left(2\zeta - \frac{\omega_n}{K_{PD}K_{VCO}}\right)}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(1.21)

Another important parameter in the above equations is the *loop gain*, which is the product of the PFD gain and the VCO gain, that is  $K_{PD}K_{VCO}$ . The loop gain classifies the PLL system into a low-gain loop or a high-gain loop. If the condition,

$$K_{PD}K_{VCO} >> \omega_n$$

Then, the PLL is said to be a high-loop gain. Most PLLs are high-loop gain and this results to approximate equation 1.21 and get equation 1.22.

$$H(s) \approx \frac{2\zeta \omega_n s + \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

(1.22)

### **1.9 PLL Order and Type**

According to *GARDNER*, the PLL type is defined by the number of perfect integrators present in the loop. Since the VCO is modeled as an integrator, the PLL is always considered a Type I system. The type number increases if the LF includes an integrator.

The order of the PLL, on the other hand, is defined by the highest power of the transfer function's denominator, and thus by the number of poles.

If these definitions are applied to the previous PLL model, and from equation 1.22, we conclude that the system is a *type I second-order high-gain PLL* because the highest power in the denominator is 2 and there exists only one integrator (VCO). Second-order PLLs are usually simple to implement and have good performance.

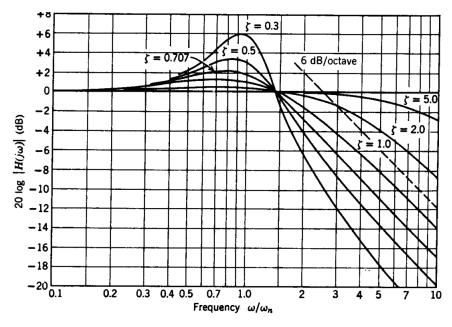

Figure 1.24 depicted below represents the bode plot of the transfer function H(s) in *dB* versus the ratio  $(\omega/\omega_n)$  for different  $\zeta$  values. This bode plot is valid for every second-order high-gain PLL.

Figure 1.24: Frequency response of a high-gain second order PLL. [5]

The response of the PLL in the figure is similar to that of a low-pass filter. Note that the damping factor  $\zeta$  has an important influence of the response.

The following points summarize the effect of  $\zeta$  on the performance of the PLL. [1,3]

• If *ζ* << 1

The transient response becomes oscillatory; the smaller the damping factor, the larger the overshoot.

•  $\zeta = 1$

The system is critically damped, the system responds quickly to changes in the input signal without overshoot.

•  $\zeta = \frac{\sqrt{2}}{2} = 0.707$

The system performance is similar to that of a second-order Butterworth low-pass filter. The response time is slower and the settling time is longer than in a critically damped system. However, the phase response is stable and does not exhibit overshoot.

•  $\zeta >> 1$

The transfer function H(s) flattens out, the response time is very slow and the settling time is very long. This means that the PLL may not be able to respond quickly to changes in the input signal.

The bandwidth of a second-order PLL is frequently defined as the radian frequency  $\omega_{3dB}$  at which the phase response of the PLL loop filter reaches -3dB. It is commonly known as the "3 dB bandwidth."

The bandwidth is computed by solving equation 1.23 for  $\omega$ .

$$|H(j\omega)|^2 = 0.5 \tag{1.23}$$

The solution of equation 1.23 is given by  $\omega_{3dB}$  as follows,

$$\omega_{3dB} = \omega_n \left[ 1 + 2\zeta^2 + \sqrt{(1 + 2\zeta^2)^2 + 1} \right]^{1/2}$$

(1.24)

The 3dB bandwidth indicates the frequency at which the PLL gain begins to decrease. At frequencies above the 3dB bandwidth, the gain of the PLL decreases as frequency increases, this results in filtering out the high-frequency noise and disturbances in the input signal. [1]

## 1.10 PLL Applications

PLLs have a wide range of applications in electronics and communication. A PLL's output can be used to generate a stable clock signal, recover data from a noisy signal, synthesize a new frequency, control the speed of a motor...etc. In this section, we discuss some of these applications.

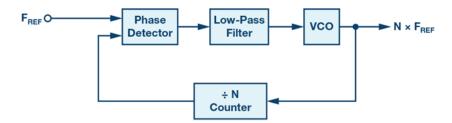

#### • Frequency synthesis

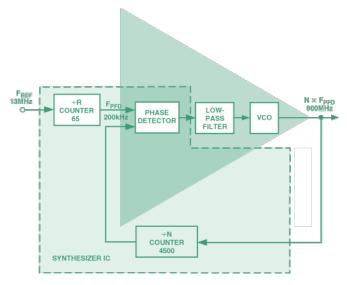

PLLs allow designers to generate an output signal with a frequency that is a multiple of the reference signal frequency. Figure 1.25 shows the block diagram of a synthesizer. Note that the feedback is not unity anymore, it contains a feedback divider that will generate  $N \times f_{ref}$  if it is in parallel with the open loop.

Figure 1.25: Block diagram of a PLL synthesizer. [6]

This application is really useful in radio communication, where different frequencies are required for different channels. It is also used to generate local oscillator (LO) signals for the up and down conversion of RF signals. Figure 1.26 shows how a 900 MHz output frequency is generated starting from a 13 MHz reference frequency.

First, a series input counter *R* reduces the reference  $f_{ref}$  by a factor of 65, the frequency present at the input of the PFD is given by  $f_{PFD} = f_{ref}/R = 13 MHz/65 = 200 KHz$ . Then, this frequency is now synthesized with the help of another counter *N* that multiplies  $f_{PFD}$  by *N*, therefore,  $f_{out} = N \times f_{PFD} = 200 KHz \times 4500 = 900 MHz$ .

Figure 1.26: PLL as a synthesizer. [7]

#### • FM demodulation

The function of a PLL FM demodulator is based on comparing the phase of the input FM signal with a stable reference signal, generated by a crystal oscillator. The phase detector's output is filtered by the LF and fed back to the VCO, which adjusts its frequency to keep a constant phase relationship with the input signal. This feedback loop causes the oscillator to track the variations in the frequency of the FM signal, and the frequency difference between the oscillator and the input signal is the demodulated output. [8]

PLL FM demodulators have many advantages over other FM demodulation techniques. They are less susceptible to noise and distortion and produce a more stable output signal. Most importantly, they can be easily implemented using integrated circuits, making FM demodulation a low-cost solution. [8]

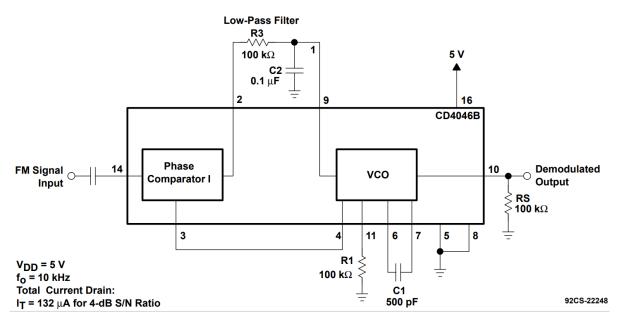

LM565 and CD4046 are some common PLL ICs that may be used as FM demodulators or frequency synthesizers.

Figure 1.27 shows an example of the connections of the CD4046B as an FM demodulator. For this example, an FM signal consisting of a 10 kHz carrier frequency was modulated by a 400 Hz audio signal. Note that the VCO center frequency is equal to the FM carrier frequency, thus an XOR PD is used (XOR PD is also referred to as Type I PD).

Figure 1.27: FM demodulator using CD4046. [9]

#### • Frequency and phase tracking

PLLs can be used to track and maintain the frequency and phase of a signal in real-time, which is important in applications such as radar, sonar, and GPS systems. For instance, in a GPS system, a PLL can be used to track the frequency and phase of the GPS signal and adjust the timing of the receiver to match the GPS signal. This allows the GPS receiver to accurately determine the location and timing information.

## 1.11 Conclusion

In this introductory chapter, many essential concepts related to Phase Locked Loops design were explained. We have discussed the operating principles of PLLs, and the different types of PLLs (ADPLL, DPLL, APLL). We have also explored the characteristics of the phase detector (analog and digital), loop filters and their transfer functions, and oscillator types including voltage-controlled oscillators.

Moreover, the transfer function and dynamics of second-order PLLs and their corresponding formulas were shown. Finally, we have examined some of the many applications of PLLs, such as clock generation, frequency synthesis, and demodulation. we also conclude that it is extremely important to understand these principles before starting the design and the implementation of any phase-locked loop. In the next chapter, the design and simulation of a digital PLL (DPLL) will be covered.

## **Chapter 2**

## **Design and Simulation of a Digital PLL**

## 2.1 Introduction

As discussed in the previous chapter, Phase Locked Loops are widely used in communication systems for their ability to synchronize signals and track frequency offsets. PLLs are also of different types such as Analog PLL (APLL), Digital or Mixed-signal PLL (DPLL), All Digital PLL (ADPLL)...etc

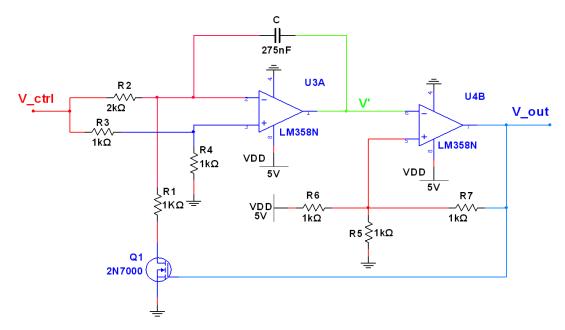

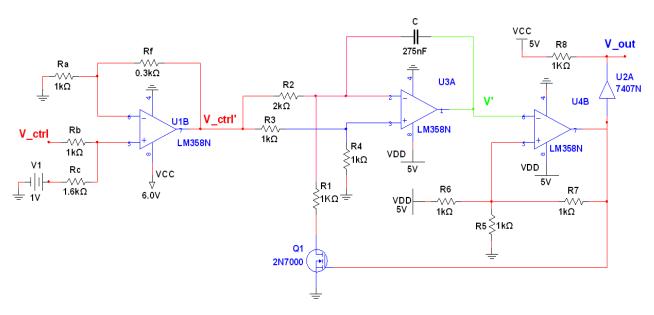

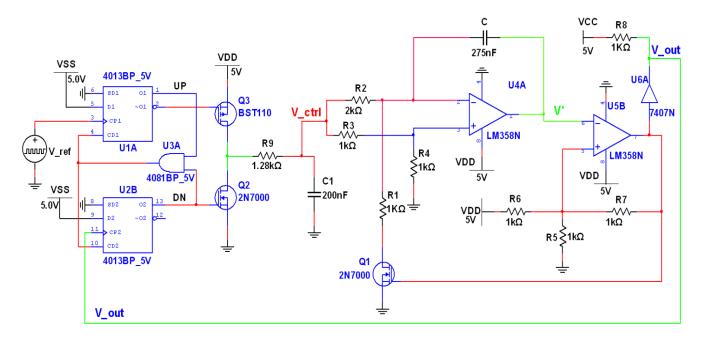

In this chapter, we present the design and implementation of a Digital or Mixed-signal Phase Locked Loop (DPLL) for GPS synchronization. Our objective is to design a DPLL that synchronizes with a 1  $KH_z$  reference signal and achieve high precision and stability. The design and implementation of the DPLL involve designing and simulating each block diagram in open loop, which means designing the PFD, the VCO, and the LF separately and discussing their performance. Then, the closed loop DPLL system is constructed to study its behavior and to determine its ability to synchronize with the 1  $KH_z$  reference signal. The simulation and design procedures are carried out using **Multisim** software, which is a powerful tool for simulating, analyzing and providing reasonably accurate predictions of the PLL circuit behavior. Some details regarding this software are provided in the Appendix.

## **2.2** Design of Phase Frequency Detector (PFD)

The first building block in the DPLL is the PD. Multiple PDs exist as it was mentioned in Chapter 1 such as XOR PD, JK PD, and PFD... Since we are dealing with digital signals, The optimal type that should be selected in the design is the PFD or a Type IV PD [1].

The PFD detects the phase and the frequency difference with high accuracy compared to the other PDs. Moreover, it has a wide lock-in range, which means it can detect phase differences over a large range of frequencies. On top of that, it provides information about the phase relationship between the input signals, indicating which signal is leading or lagging.

PFDs are frequently employed in digital phase-locked loops, they are circuits that produce a stable output signal. The phase and frequency of the output signal and the reference signal are compared by the PFD, and a control signal is generated to adjust the output signal to track the reference signal.

In Multisim environment, we start by setting the parameters of the reference signal, whose frequency is 1 KHz and its duty cycle is 50%. This is done by selecting a PULSE\_VOLTAGE generator from

the SIGNAL\_VOLTAGE\_SOURCES section. We have also created another PULSE\_VOLTAGE generator for the second input and it refers to the feedback signal. The feedback signal parameters are similar to that of the reference, which means that the frequency is also 1 *KHz* and its duty cycle is 50%.

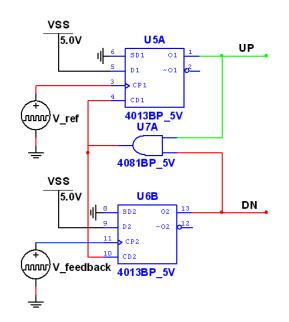

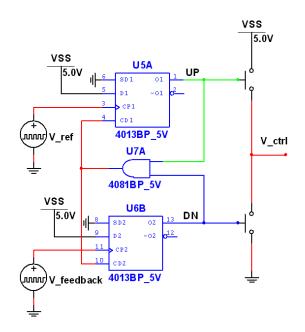

Figure 2.1 depicts the circuit of a PFD, where 2 D flip-flops (**4013BP**) and one AND gate (**4081BP**) are used. These ICs were selected because they belong to the CMOS family, which is a widely used digital logic technology for its low power consumption and high noise immunity.

Figure 2.1: Schematic of phase frequency detector in Multisim.

The **4013BP** is a digital integrated circuit (IC) that contains four D flip-flops. Each flip-flop has a single data input (*D*), a clock input (*CLK*), a clear input (*CLR*), and complementary outputs (*Q* and  $\overline{Q}$ ). The chip operates with a power supply voltage of 5V and is typically used for data storage and for timing control.

**4081BP** is a commonly used IC that provides simple and reliable logical AND operations in digital logic circuits, it contains four two-input AND gates and operates with a power supply voltage of 5V.

Note that the reference signal is connected to the (CLK) pin of the 1st D flip-flop, and the feedback signal is connected to the (CLK) pin of the 2nd D flip-flop. This PFD outputs two signals, UP and DN which are fed to the inputs of the AND gate, then its output is connected to (CLR) pin of each FF.

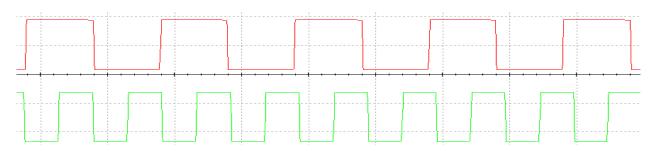

The basic operation of a PFD involves comparing the rising and falling edges of the input signals to detect phase differences. Thus, three cases are discussed.

• If V<sub>ref</sub> leads V<sub>feedback</sub>

The rising edge of  $V_{ref}$  occurs first, then *UP* goes HIGH while *DN* remains LOW, once the rising edge of *DN* occurs, *UP* goes LOW. This generates a pulse whose width is equal to the phase difference as shown in Figure 2.2.

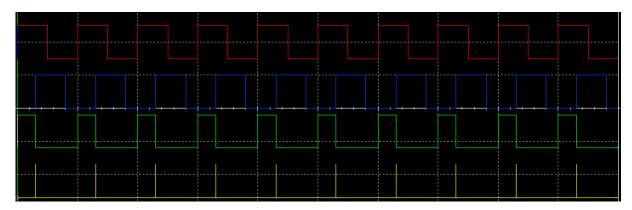

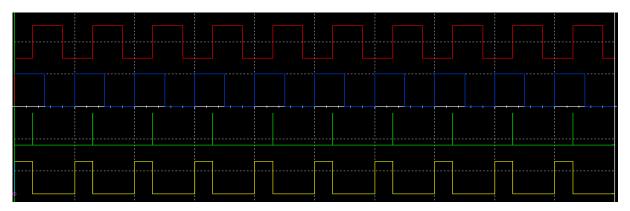

**Figure 2.2:** Case I:  $V_{ref}$  (in red) leads  $V_{fb}$  (in blue), UP in green and DN in yellow.

• If V<sub>ref</sub> lags V<sub>feedback</sub>

The inverse happens, DN goes HIGH while UP remains LOW, once the rising edge of UP occurs, DN goes LOW. This also generates a pulse whose width is equal to the phase difference as shown in Figure 2.3.

Figure 2.3: Case II:  $V_{ref}$  (in red) lags  $V_{fb}$  (in blue), UP in green and DN in yellow.

#### • If V<sub>ref</sub> and V<sub>feedback</sub> are in phase

When both  $V_{ref}$  and  $V_{fb}$  are in phase, UP and DN are high, the AND gate will then reset the 2 D flip flops and make them low as depicted in Figure 2.4. note that UP and DN are not perfectly zero, some glitches appear at each rising edge, this is due to the delay of the D FF.

Figure 2.4: Case III:  $V_{ref}$  (in red) and  $V_{fb}$  (in blue) are in phase, UP in green and DN in yellow.

Note that these results are obtained when the frequencies of the two inputs are equal, but there is a phase difference between them, this phase error is detected by the PFD.

If the frequency of the feedback signal is set to another frequency, say 800 Hz, the output signals *UP* and *DN* are depicted in Figure 2.5.

Figure 2.5: Outputs UP (in green) and DN (in yellow) when  $V_{ref}$  (in red) and  $V_{fb}$  (in blue) are not equal in frequencies.

Since the frequency of the reference signal is higher than that of the feedback, the PFD detects this difference by generating pulses in the UP signal, while DN stays low. On the other hand, if the frequency of the reference signal is lower, the pulses will be generated in the DN signal, and UP remains low. We conclude that the PFD is a circuit that detects both the phase and frequency difference between two input signals by knowing which signal is leading or lagging.

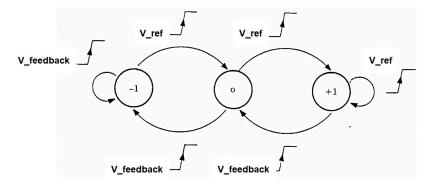

PFD is usually referred to as a tristate PFD, which means that the PFD has three outputs: UP, DN, and *RESET*. When  $V_{ref}$  is leading, then UP is high and the PFD is on "state +1". On the other hand, if  $V_{fb}$  is leading, then DN is high and the PFD is switched to "state -1". However, when both  $V_{ref}$  and  $V_{fb}$  are in phase, UP and DN are high, the AND gate output goes high to reset them, thus *RST* is activated, we say that the PFD is on "state 0". These results are summarized in Table 2.1 and in Figure 2.6

| V <sub>ref</sub> | $V_{fb}$ | UP | DN | State |

|------------------|----------|----|----|-------|

| Leading          | Lagging  | 1  | 0  | +1    |

| Lagging          | Leading  | 0  | 1  | -1    |

| In phase         | In phase | 0  | 0  | 0     |

Table 2.1: Tristate PFD

Figure 2.6: State diagram of the PFD. [1]

PFDs are classified into two types according to the output, a PFD can either have:

- Voltage output that represents the phase difference between the two input signals.

- Current output that is proportional to the phase difference between the input signals, such PFD is said to have a *charge pump* output.

In this design, the first approach is implemented. A PFD with voltage output is simpler to design and implement than a PFD with current output, as it does not require an additional charge pump circuit. They have wide operating frequency range and they can be easily integrated with other PLL components, such as loop filters and VCOs.

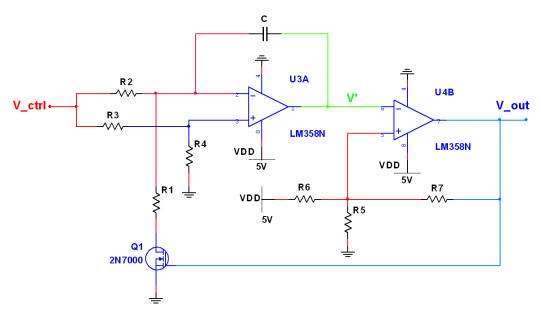

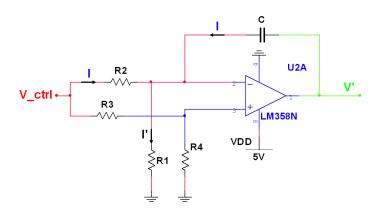

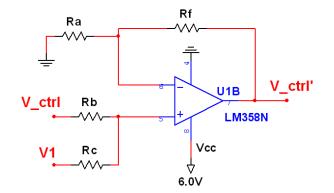

To create such type of PFD, it is required to design some switches that control the output voltage  $V_{ctrl}$ . Figure 2.7 depicts the schematic that represents the final circuit of the PFD. The concept of this circuit is easy, if the PD is on *state* +1, the *UP* is high and *DN* is low, this leads to closing the upper switch and opening the lower one, thus  $V_{ctrl}$  is connected to  $V_{cc}$ . On the other hand, if the PD is on *state* -1, the *DN* is high and *UP* is low, this results in closing the lower switch and opening the upper one, therefore,  $V_{ctrl}$  is connected to *GND*. Finally, if *state* 0 is activated, both *UP* and *DN* are low, the switches are opened and  $V_{ctrl}$  will be in a "floating" state, this state is also known as high-impedance output state.

Figure 2.7: Schematic of phase frequency detector with an output voltage.

The design of the switches requires using MOSFETs since they have many advantages. MOSFETs have a **high input impedance**, so they draw very little current from the driving circuitry. They also have **low ON resistance**, which results in low power dissipation and low voltage drop across them. Most importantly, MOSFETs have **fast switching speeds**, making them suitable for use in PLL applications. Finally, MOSFETs are easily **controlled using a voltage signal** such as *UP* and *DN*. [10]

The upper switch in Figure 2.7 is replaced with an Enhancement-mode PMOS transistor, while the lower one is replaced by an Enhancement-mode NMOS transistor.

The NMOS transistor is ON if it's in the saturation or linear region. This condition is fulfilled if the voltage between the GATE and the SOURCE  $V_{GS}$  is much greater than  $V_{TH}$  the threshold voltage of the transistor ( $V_{GS} > V_{TH}$ ). The NMOS is then treated as a low resistance  $R_{DS}$  or a closed switch [10].

Unlike NMOS, The PMOS transistor is in the saturation region if the voltage between the GATE and the SOURCE  $V_{GS}$  is much higher than  $V_{TH}$  the threshold voltage of the transistor ( $V_{GS} > V_{TH}$ ). But since  $V_{TH}$  is negative, the Gate potential should be more negative with respect to the Source [10].

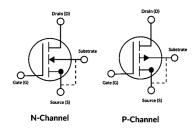

Figure 2.8 shows the conventional symbols of PMOS and NMOS transistors. It's important to mention that in an NMOS transistor, the conventional current flows from the Drain D to the Source S when the transistor is turned on. However, in a PMOS transistor when turned on, the conventional current flows from the Source S to the Drain D.

Figure 2.8: Symbols of enhancement mode MOSFET. [10]

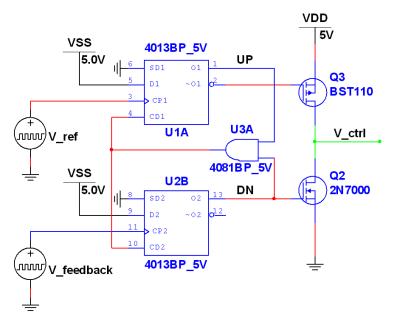

The final schematic of the PFD with an output voltage is depicted in Figure 2.9, where the NMOS transistor **2N7000** and the PMOS transistor **BST110** were used with a power supply  $V_{DD}$  of 5*Volts*.

Figure 2.9: Final schematic of a PFD with output voltage.

The **2N7000** is an N-channel MOSFET transistor that is widely used in electronic circuits. It is a small signal transistor with a maximum voltage of 60 volts and a maximum current of 200 mA. The 2N7000 is used in our application as a switch to control the flow of current in the PFD. The typical threshold voltage of the 2N7000 MOSFET is around 2.1 volts, its resistance when being ON is  $5\Omega$ , and it is considered to be a fast transistor [11].

The **BST110** is also a small signal transistor with a maximum voltage of 50 volts and a maximum current of 250 mA. It is commonly used in electronic circuits as a switch or amplifier. The typical threshold voltage of the BST110 is around -1.5 volts, which means that a negative voltage must be applied to the gate to turn the transistor ON. Its maximum resistance when being ON is  $10\Omega$  The switching time of the BST110 is also similar to the 2N7000, typically in the range of a few nanoseconds [12].

For the PMOS transistor, the Source  $S_1$  is connected to  $V_{DD}$ , and its Gate  $G_1$  is connected to  $\overline{UP}$ , the complement of the signal UP. Concerning the NMOS, its Source  $S_2$  is grounded while its Gate  $G_1$  is connected to DN.

The connections among the signals UP and DN and the Gates  $G_1$  and  $G_2$  (which are the Gate pins of the PMOS and NMOS transistors respectively) are summarized in table 2.2.

| V <sub>ref</sub> | $V_{fb}$ | UP | DN | $V_{G_1}$ | $V_{G_2}$ | V <sub>ctrl</sub> |

|------------------|----------|----|----|-----------|-----------|-------------------|

| Leading          | Lagging  | 1  | 0  | 0         | 0         | +5 V              |

| Lagging          | Leading  | 0  | 1  | +5 V      | +5 V      | 0 V               |

| In phase         | In phase | 0  | 0  | +5 V      | 0         | High Z            |

**Table 2.2:** States of UP, DN and  $V_{ctrl}$  with respect to the voltage  $V_{G_1S_1}$  and  $V_{G_2S_2}$ .

According to logic circuit design, the potentials  $V_{G_1}$  and  $V_{G_2}$  depend on the variables *UP* and *DN*. Note that the potentials  $V_{S_1}$  and  $V_{S_2}$  are fixed to +5 volts and 0 volt respectively. From Table 2.2, it is clear that  $V_{G_1}$  is the complement of *UP*, whereas  $V_{G_2}$  is equal to *DN*. Therefore,

$$V_{G_2} = \overline{UP}$$

$V_{G_2} = DN$

This explains why the Gate  $G_1$  is connected to the complementary output of the first D FF and the Gate  $G_2$  is directly connected to the output of the second D FF.

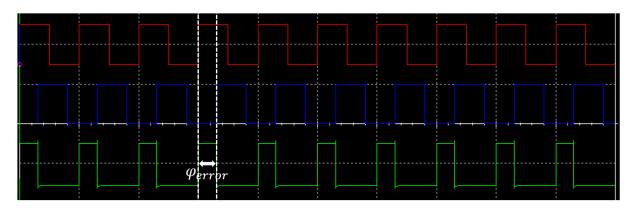

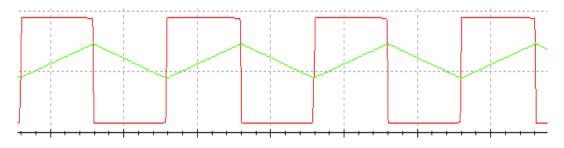

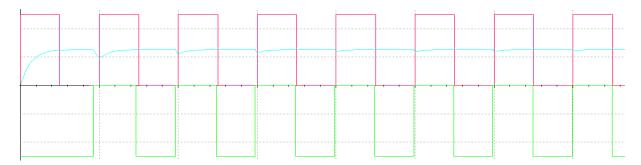

The PFD was tested in a simulation where it was first supposed that  $V_{ref}$  is leading, and then  $V_{ref}$  is lagging. Figures 2.10 and 2.11 show the variation of  $V_{ctrl}$  and the detection process of the PFD after simulation with Multisim.

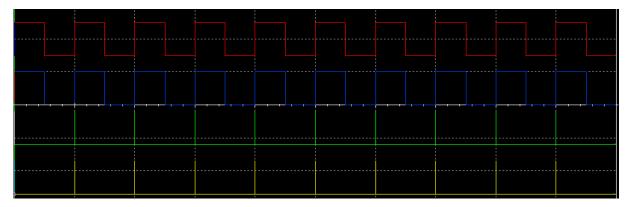

**Figure 2.10:** Case I: PFD output when  $V_{ref}$  is leading ( $\omega_{ref} = \omega_{feedback}$  and  $\phi_{error} \neq 0$ ).

**Figure 2.11:** Case II: PFD output when  $V_{ref}$  is lagging ( $\omega_{ref} = \omega_{feedback}$  and  $\phi_{error} \neq 0$ ).

As it is shown in Figure 2.10, whenever  $V_{ref}$  proceeds, the PFD generates pulses of 5 volts amplitude and width of  $\phi_{error}$  to increase the frequency of the VCO until the feedback signal track the reference. However, case II, depicted in Figure 2.11, deals with the inverse scenario, the PFD generates pulses of 0 volt amplitude and width of  $\phi_{error}$  to decrease the frequency of the VCO until the feedback signal is locked with the reference. Hence, if the inputs' frequencies change, the PFD keeps detecting the differences and generates pulses to either decrease or increase the VCO output frequency to match the reference one.

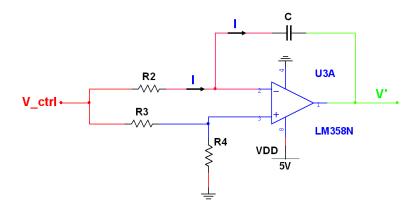

## 2.3 Design of Voltage Controlled Oscillator (VCO)

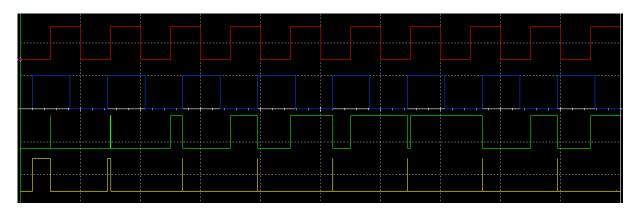

The VCO is the building block that is responsible for generating the output signal that must be synchronized with the reference signal. The VCO is controlled by the *Control voltage*  $V_{ctrl}$  which

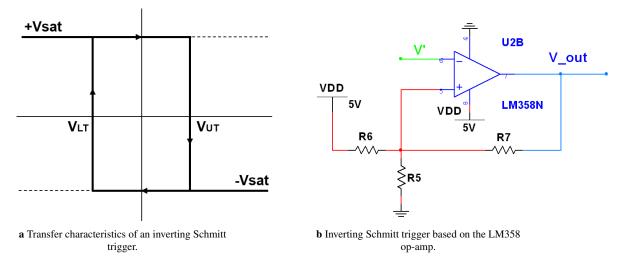

represents the dc output voltage generated by the LF. As discussed in Chapter 1, numerous types of VCO exist. But, since we aim to design a DPLL, a VCO that generates digital output voltages is needed. Thus, the type of VCO that was selected is the relaxation VCO. Relaxation VCOs can generate square, triangular, and sawtooth waveforms.