# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

### UNIVERSITE M'HAMED BOUGARA-BOUMERDES

## Institut de Génie Electrique et Electronique

## Thèse de Doctorat

Présentée par :

### **Boualem DJEZZAR**

En vue de l'obtention du diplôme de **DOCTORAT** en :

Filière : Génie Electrique et Electrotechnique

Option: Microélectronique

### **TITRE**

## ETUDE DES EFFETS NBTI ET PBTI SUR LA FIABILITE DES DISPOSITIFS MOS

## Devant le jury composé de :

| Mr | BENFDILA  | Arezki  | Professeur | UMMTO | Président          |

|----|-----------|---------|------------|-------|--------------------|

| Mr | KECHOUANE | Mohamed | Professeur | USTHB | Examinateur        |

| Mr | BENTARZI  | Hamid   | Professeur | UMBB  | Examinateur        |

| Mr | KRIBES    | Youcef  | MCA        | UMBB  | Directeur de thèse |

### **ACKNOWLEDGEMENTS**

This work has been carried out at Microelectronics and Nanotechnology Division (DMN) of CDTA (Centre de Développement des Technologies Avancées) in collaboration with Génie Electrique et Electronique Institute of UMBB (Université M'hamed Bougara Boumerdes).

I would first like to thank my thesis adviser, Dr. Youcef Kribes, for the support and the fruitful discussions he provided me during the course of this thesis. His continuous encouragement and valuable advises constituted the driving force of this work.

I gratefully want to thank my thesis committee members, Prof. Benfdila Arezki, Prof. Kechouane Mohamed, and Prof. Bentarzi Hamid, for their reading of the thesis and useful suggestions. Their insight helped me to improve the completeness of the thesis.

I would like to give a special thanks to CDS team members, Dr. Hakim Tahi, Mr. Abdelmadjid Benabdelmoumene, Miss Amel Chenouf, Mr. Boumediene Zatout, and Mr. Mohamed Goudjil, for their assistance with experimental development and for the many useful technical discussions. Thanks also to the proof-readers of this thesis, Dr. Sofiane Soukane, Dr. Marhoun Ferhat, and Dr. Abdelkrim Kamel Oudjida for their efforts in minimizing the typos. My thanks go also to DMN members for their support, particularly Mr. Hadj El Arbi Fayçal and Dr. Serhane Rafik.

Finally, I would like to thank my family members. Here, the special thanks go to my wife and kids, Fatima and Youcef, for their support during the preparation of this thesis.

This work has been supported by the High Education and Scientific Research Ministry of Algeria under the National Funding of Research (FNR) contract number 22/CDS/DMN/ CDTA/2011.

### الملخص

الدمج المتسارع للمركبات الإلكترونية أدى إلى تخفيض كبير لسمك عازل القطب (Gate) للمقحل (ترانزستور) من عقدة تكنولوجية إلى أخرى. هذا أدى إلى إرتفاع الحقل الكهربائي للقطب و كذا ارتفاع حرارة الدارات المدمجة أثناء عملها. (Reliability) على كفاءة (Reliability) الدارات المدمجة، خصوصا مشكل الإختلال من الحرارة والاستقطاب السالب/الموجب (N/PBTI) (Negative/Positive Bias temperature Instability). بالطبع BTI يؤثر على عمل الدارة المدمجة و كذلك على مدة صلاحيتها باستحداث أفخاخ (Traps) على مستوى السطح الفاصل بين السلكون و ثاني أوكسيد السلكون (Si/SiO<sub>2</sub>) و داخل ثاني أوكسيد السلكون (SiO<sub>2</sub>). إن فهم ميكانيزمات تكون هذه الأفخاخ مهم جدًا لتصميم نمودج للتدهور "NBTI" و التنبؤ به و بمدة صلاحية الدارات المدمجة. لهذا السبب يأتي هذا البحث المخصص لتشخيص الكهربائي للتدهور "NBTI" باستعمال طرق و تصاميم جديدة من أجل فهم و تحليل جيد للأفخاخ المتسببة في التدهور، منه تطوير نمودج فعّال للتنبؤ بمدة صلاحية المكونات الكهربائية و الدارات المدمجة.

بهذا الصدد، نطرح طريقة جديدة، المسماة NBTI. هذه الطريقة ترتكز أساسًا على تقنية ضخ الشُحنات بإستعمال تواترات السلكون على الطائر"، لقياس التدهور NBTI. هذه الطريقة ترتكز أساسًا على تقنية ضخ الشُحنات بإستعمال تواترات منخفضة وعالية. بهذه الوسيلة يمكن إستخراج و فصل كثافة الأفخاخ الموجودة على سطح الفاصل  $(\Delta N_{it})$  والموجودة داخل ثاني أوكسيد السلكون قرب السطح الفاصل  $(\Delta N_{bt})$  و كذا مساهمتهما في إنحراف تواتر العتبة  $(\Delta V_{th})$  بدون اللجوء إلى إستعمال طرق أخرى مكملة و إضافية.

إضافة إلى ما سبق، فإننا تمكنًا من استكشاف و تتبع كيفية نشوء و تطور وتوزع كثافة ( $\Delta N_{it}$ ) بدلالة طول قناة المقحل (ترانزستور), حيث أنّ ( $\Delta N_{it}$ )، المُحدثة من طرف "Stress NBTI"، موزعة بطريقة غير منتظمة داخل قناة المقحل. نتائج التجارب بيّنت أنّ التدهور ينتشر و يبدأ انتشاره من أطراف قناة المقحل، أي من جهة "Source /Drain" نحو مركزها، هذا الانتشار يتسارع بفعل الحرارة و الحقل الكهربائي، حيث هذا الأخير يسبب تسارع أكبر من الذي تسببه الحرارة، كما أن المقاحل ذات قنوات قصيرة تتدهور سريعا من المقاحل ذات قنوات طويلة.

أخيرا قمنا بتمشيط الأفخاخ الموجودة في ثاني أوكسيد السلكون القريب من السطح الفاصل ( $\Delta N_{bt}$ ) بدلالة العمق (z) في المقحل (MOSFET). فحسب نتائج التجارب، فإن القوة (z) لدالة القوة (z)، التي تحاكي التطور الزمني ل (z)، وكذا طاقة النشاط الظاهري (z) تنخفضان بفعل الحرارة و الحقل الكهربائي. من جهة أخرى، العزم القطبي الظاهر و طاقة النشاط (مستقلة عن الحقل الكهربائي) يُظهران ارتباطا خطيًا مع العمق (z)، هذا الأخير يمكنه تفسير تغيّر z0 و z1 بالفعل إن إنخفاضهما يمكن أن يعود الى مساهمة تراكمية لعدة أفخاخ ذات طاقات نشيطة و عزوم أقطاب مختلفة، حيث قمنا بإقتراح إنّ هذه الأفخاخ تنتمي إلى عائلة العيوب z1 z2 (أو مركز z3 مركب هيدروجيني).

المفاتيح: NBTI، أفخاخ السطح الفاصل، أفخاخ "Border traps"، ضخ الشُحنات، OTFOT، انتشار التدهور، توزع أفقي للأفخاخ، توزع عمودي للأفخاخ، الأوكسيد القريب من السطح الفاصل.

### RESUME

La miniaturisation des composants électroniques a entraîné une réduction accélérée de l'épaisseur du diélectrique de la grille des transistors d'un nœud technologique à un autre. Ceci a induit une augmentation du champ électrique de la grille ainsi qu'une augmentation de la température de fonctionnement des circuits intégrés (Cl's). En conséquence, plusieurs problèmes de fiabilité des Cl's sont apparus, en particulier Negative/Positive Bias Temperature Instability (N/PBTI). En effet, le BTI influence le fonctionnement des Cl's ainsi que leurs durées de vie en créant des pièges à l'interface (Si/SiO<sub>2</sub>) et dans l'oxyde de grille. De ce fait, la compréhension des mécanismes de formation des pièges, créés à l'interface substrat/isolant et dans la région d'oxyde près de l'interface, est importante et utile pour la modélisation de la dégradation NBTI et la prédiction de la durée de vie des composants. Ainsi donc, l'objectif de cette thèse est la caractérisation électrique de la dégradation NBTI en utilisant de nouvelles méthodes et de nouveaux concepts afin de mieux appréhender et analyser les pièges impliqués dans la dégradation NBTI, et par voie de conséquence développer des modèles fiables pour prédire la durée de vie des dispositifs.

A cet effet, nous proposons une nouvelle méthode, nommée On The Fly Oxide Trap (OTFOT), pour extraire la dégradation NBTI. En utilisant le pompage de charge à haute et basse fréquences. La méthode OTFOT permet d'extraire et de séparer les densités des pièges d'interface ( $\Delta N_{it}$ ) et d'oxyde prés de l'interface « border trap » ( $\Delta N_{bt}$ ) et aussi leurs contributions à la dérive de la tension de seuil ( $\Delta V_{th}$ ) sans recourir à d'autres méthodes complémentaires.

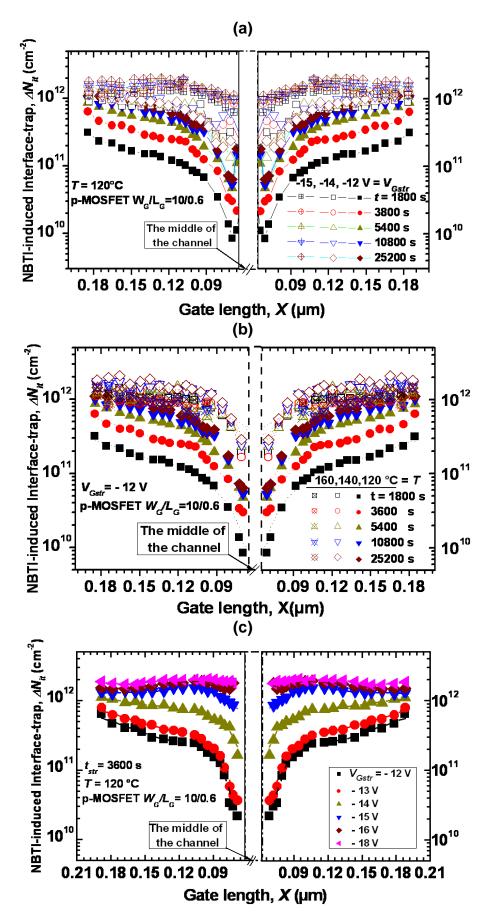

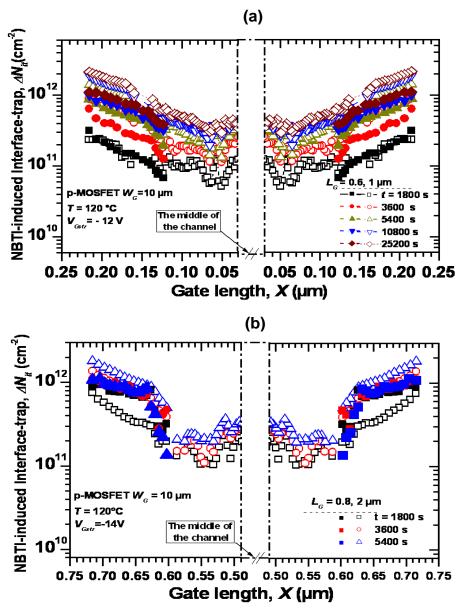

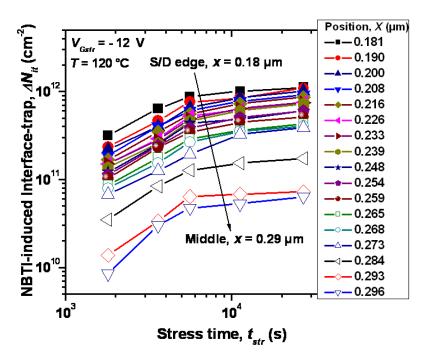

De plus, nous avons exploré la génération et l'évolution de la distribution de  $\Delta N_{it}$  en fonction de la longueur du canal. Nous avons trouvé que la densité  $\Delta N_{it}$ , induite par le stress NBTI, n'est pas uniforme le long du canal. Les résultats expérimentaux révèlent une propagation de la dégradation. Cette dernière commence à partir des bords source/drain et puis pénètre au centre du canal. Elle est accélérée par la température et le champ électrique jusqu'à la saturation. Cependant, l'accélération par le champ électrique et plus important que celle de la température. Aussi, les transistors à canaux courts se dégradent plus rapidement que ceux à canaux longs.

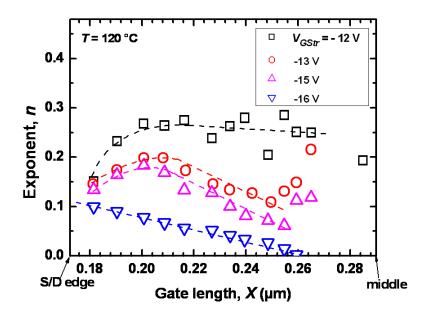

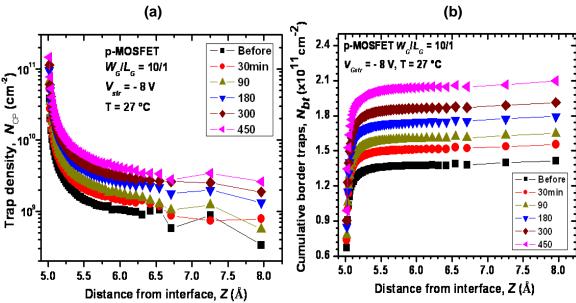

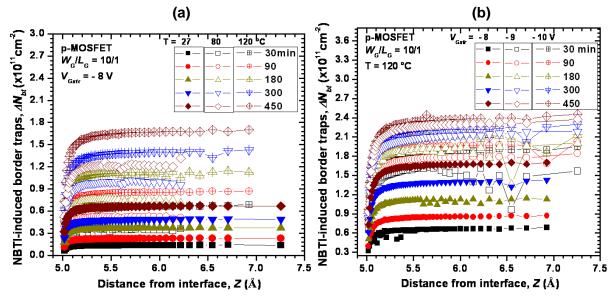

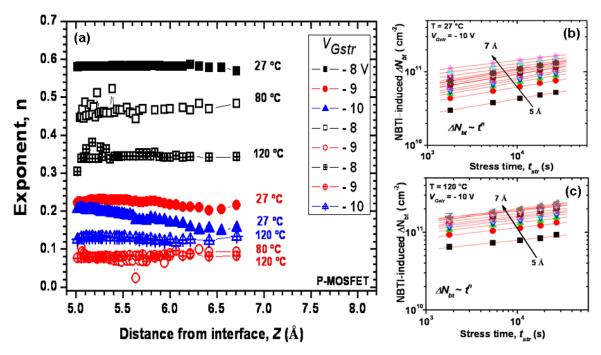

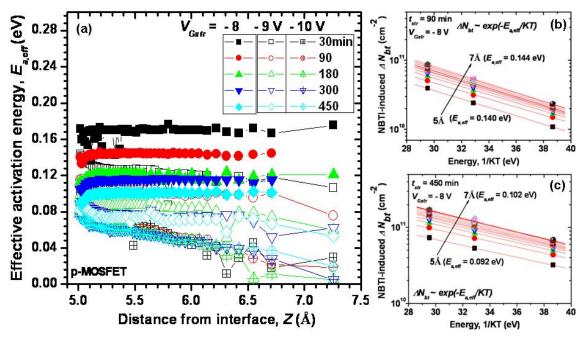

Finalement, Nous avons aussi scanné le profile de  $\Delta N_{bt}$  en fonction de la profondeur (Z) dans l'oxyde de grille prés de l'interface des transistors PMOS. Selon nos données expérimentales, l'exposant (n) de la loi en puissance ( $t^n$ ) qui gère l'évolution temporelle de  $\Delta N_{bt}$ , ainsi que l'énergie apparente d'activation ( $E_{a,eff}$ ) diminuent avec la température (T) et la tension ( $V_{Gstr}$ ) de stress. En outre, le moment dipolaire effectif ( $a_{eff}$ ) et l'énergie d'activation ( $E_a$ ) (indépendante du champ électrique) ont montré une dépendance linéaire avec Z. Ceci peut expliquer la variation de n et  $E_{a,eff}$  avec T et  $V_{Gstr}$ . En effet, leur diminution peut être causée par la contribution cumulative des pièges ayant différentes énergies d'activation et différents moments dipolaires. Nous avons suggéré que ces pièges sont probablement liés à la famille de défauts  $O_{3-x}Si_xSi_zH$  (ou le centre complexe  $P_b$  hydrogéné) localisé dans la région suboxyde prés de l'interface.

*Mots clés*: NBTI, Pièges d'interface, "Border-trap", Pompage de charge, OTFOT, Propagation de la dégradation, Distribution latérale, Profile vertical, Oxyde prés de l'interface.

### **ABSTRACT**

The continuous device shrinking has accelerated the reduction of the gate dielectric from technology node to another. This fact has induced a gate electric field increase and enhanced the IC's working temperature. As a consequence, many reliability issues have been taken place, especially Negative/Positive Bias Temperature Instability (N/PBTI). Indeed, the BTI impacts IC's working as well as their life times by creating traps at the interface (Si/SiO<sub>2</sub>) and in the gate oxide. Therefore, understanding the mechanisms of trap formation at the dielectric/substrate interface and interfacial region is useful for NBTI modelling and life time prediction. The aim of this thesis is the electrical characterization of the NBTI degradation by using new methods and concepts in order to better analyze the traps involved in NBTI and subsequent development of reliable models.

We propose a new method, named on the fly oxide trap (OTFOT), to extract NBTI degradation in MOS transistors. Using alternatively high and low frequencies, OTFOT method separates and extracts the interface trap ( $\Delta N_{tt}$ ) and border trap ( $\Delta N_{bt}$ ) densities independently and also their contributions to the threshold voltage shift ( $\Delta V_{th}$ ), without needing additional methods.

In addition, we have investigated the generation and evolution of  $\Delta N_{it}$  distribution with respect to the transistor gate length. We have found that NBTI-induced  $\Delta N_{it}$  is not uniform along the channel length. The experimental results reveal an evident propagation of the NBTI degradation. This propagation starts from source/drain channel edges and penetrates into the channel center. It is accelerated by temperature and electric field until saturation. However, field-accelerated propagation seems more important than temperature-accelerated one. Moreover, transistors with shorter channel length degrade more rapidly than those with longer channel length.

*Index-Terms*: NBTI, Interface-trap, Border-trap, Charge-pumping, OTFOT, Lateral distribution, Vertical profiling, interfacial oxide layer.

### **ACRONYMS**

BTI Bias Temperature Instability BTS Bias temperature stress Boron-hydrogen bond B–H C-P Charge-pumping

Centre de Développement des Technologies Avancées CDTA Caractérisation des dispositifs à semi-conducteurs CDS

Complementary metal oxide semiconductor CMOS

C-V Capacitance-voltage characteristics DCIV DC current-voltage characteristics

Microelectronics and Nanotechnology Division DMN

DOS Density of state distribution DRR Dispersive-reaction-rate

DSO Digital scope DUT Device under test

Equivalent oxide thickness EOT

Electron paramagnetic resonance **EPR**

Electron spin resonance **ESR** National Funding of Research **FNR**

GC Geometric component

**GPIB** General Purpose Interface Bus Genie Electric et Electronic Institute **GEEI**

$h^{+}$ Hole carriers

Н Neutral atomic hydrogen  $H_2$ Hydrogen molecule  $H^{+}$ Hydrogen ion . . . Hot carrier injection HCI

HBr Hydrogen bromide

HDL Harry-Diamond-Laboratories **HPSMU** High power source monitor units

IC's Integrated circuits

Gaussian-like CP-current characteristics  $I_{CP}-V_I$

$I_{DS}$ - $V_{GS}$ Transfer characteristics  $I_{DS}$ - $V_{DS}$ Direct characteristics ISiT

Institut SiliziumTechnologie

LabVIEW Laboratory Virtual Instrument Engineering Workbench

LPCVD Low pressure chemical vapour deposition

LOCOS Local oxidation of silicon Lightly doped drain LDD

MFCP Multi-frequency charge pumping Metal oxide semiconductor MOS

Metal oxide semiconductor field effect transistor MOSFET

MPE Multiphonon emission

**MPFAT** Multiphonon-field-assisted tunneling

MSM Measure/stress/measure

NBTI **Negative Bias Temperature Instability**

OTF On the fly

OTFIT On the fly interface-trap  $OTF-V_{th}$ On the fly threshold voltage

OTFOT On the fly oxide trap PBTI ... Positive Bias Temperature Instability

PARES ... Process and reliability evaluation structures

PEV ... Process evaluation vehicle

PID ... Proportional integral derivative

P-H ... Phosphorous -hydrogen bonds

POCL<sub>3</sub> ... Phosphorous oxychloride

P<sub>b</sub>-H ... Saturated interface dangling bond

PGU ... Pulse generator unit

$O_{3-x}Si_xSi-H$  ...  $P_b$  center hydrogen complex

R-D ... Reaction-diffusion

RDD ... Reaction-dispersive-diffusion

RIE ... Reactive ion etching

RTNO ... Rapid thermal-nitrided oxides SDR ... Spin dependent recombination

Si ... Silicon

Si/SiO<sub>2</sub> ... Silicon/silicon dioxide interface

$SiO_x$ , ... Interfacial oxide region (transition region,  $SiO_x$ , x < 2)

SiO<sub>2</sub> ... Silicon dioxide

Si-H ... Silicon-Hydrogen Bond

SILC ... Stress-induced leakage current

SMU ... Source monitor units

SiON ... Nitrided oxide

HfSiON ... Halfnium Nitrided oxide

HK ... High k

TDDB ... Time-Dependent Dielectric Breakdown TDDS ... Time-dependent defect spectroscopy

TEOS ... Tetra-ethyl-ortho-silicate

TFT ... Thin film transistor

$(Si_3 \equiv Si^{\bullet})$  ...  $P_b$  and  $P_{b0}$  center defects

$(Si_2O \equiv Si^{\bullet})$  ...  $P_{b1}$  center defect  $(O_3 \equiv Si^{\bullet})$  ... E' center defect

UMBB ... Université M'hamed Bougara Boumerdes

VMU ... Voltage monitor units

VSU ... Voltage source units

WKB ... Wenzel-Kramers-Brillouin

ZTC ... Zero temperature coefficient

## LIST OF SYMBOLS

| Symbol              | Unit                              | Description                                                    |

|---------------------|-----------------------------------|----------------------------------------------------------------|

| $A_{G}$             | cm <sup>2</sup>                   | Gate area                                                      |

| $a_{eff}$           | q. Å                              | Effective dipole moment                                        |

| $a_0$               | q. Å                              | Effective dipole moment at $Z_0$                               |

| $C_{OX}$            | F/cm <sup>2</sup>                 | Oxide capacitance                                              |

| $C_{Dep}$           | F/cm <sup>2</sup>                 | Capacitance of the depletion layer                             |

| $C_{fb}$            | F/cm <sup>2</sup>                 | Flatband capacitance                                           |

| D <sub>it</sub>     | cm <sup>-2</sup> eV <sup>-1</sup> | Density of interface state                                     |

| E <sub>a,eff</sub>  | eV                                | Apparent activation energy                                     |

| E <sub>a</sub>      | eV                                | Activation energy                                              |

| $E_i$               | eV                                | Midgap energy                                                  |

| $E_{em,e}$          | eV                                | electron emission energy level                                 |

| $E_{\mathrm{em},h}$ | eV                                | hole emission energy level                                     |

| E <sub>inv</sub>    | eV                                | Lower energy bound sensed by CP                                |

| $E_{ m acc}$        | eV                                | Upper energy bound sensed by CP                                |

| ∆E*                 | eV                                | Band energy scanned in the oxide                               |

| $E_{a,f}$           | eV                                | Activation energy of forward reaction                          |

| $E_{a,r}$           | eV                                | Activation energy of reverse reaction                          |

| $E_D$               | eV                                | Combined activation energy for $D_{H2}$ , $k_H$ , and $k_{H2}$ |

| $E_0$               | eV                                | Activation energy at Z <sub>0</sub>                            |

| $E_{g0}$            | eV                                | Energy bandgap at $T = 0 K$                                    |

| E <sub>am</sub>     | eV                                | Median activation energy                                       |

| E <sub>ox</sub>     | V/cm                              | Oxide electric field                                           |

| E <sub>ref</sub>    | V/cm                              | reference electric field                                       |

| E <sub>c</sub>      | V/cm                              | Electric field due to the inversion layer carriers             |

| E <sub>L</sub>      | V/cm                              | Lateral electric field                                         |

| f                   | Hz                                | Frequency                                                      |

| $f_H$               | Hz<br>Hz                          | High frequency                                                 |

| $f_L$ $f_i$         | П                                 | Low frequency                                                  |

|                     | -<br>A/V                          | Occupation function of the state <i>i</i> Transconductance     |

| g <sub>m</sub>      | A/V<br>A/V                        | Maximum transconductance                                       |

| g <sub>m,max</sub>  |                                   |                                                                |

| l <u>i</u>          | J.s                               | Planck's constant                                              |

| ļı                  | J.s                               | Reduced Planck's constant( $h/2\pi$ )                          |

| l <sub>off</sub>    | A                                 | Off current                                                    |

| I <sub>Dlin</sub>   | A                                 | Linear drain current                                           |

| I <sub>Dsat</sub>   | A                                 | Saturation drain current                                       |

| I <sub>CP</sub>     | A                                 | Charge pumping current                                         |

| I <sub>CP,H</sub>   | A                                 | Maximum CP-current at f                                        |

| I <sub>CP,L</sub>   | A                                 | Maximum CP-current at $f_L$                                    |

| $\Delta l_{CP}$     | A                                 | NBTI induced <i>CP</i> -current degradation                    |

| $\Delta l_{Geo}$    | A<br>eV /K                        | NBTI-induced Geometric component current                       |

| K                   |                                   | Boltmann's constant                                            |

| $K_{ij}$            | s <sup>-1</sup>                   | Transition rates from state $f_i$ to state $f_j$ .             |

| $k_{H}$             | cm <sup>2</sup> /s                | Generation rate of H <sub>2</sub>                              |

| $k_{H_2}$           | s <sup>-1</sup>                   | Dissociation rate of $H_2$                                     |

| $L_{\it eff}$       | cm                                | Effective gate length                                          |

| L <sub>G</sub>      | cm                                | Gate length                                                    |

| ΔL                  | cm                                | LDD overlap                                                    |

| $m_{n(p)}$          | kg                                | Effective mass of electron(hole) in the dielectric             |

| $N_0$               | cm <sup>-2</sup>                  | Initial saturated Si-H bonds                                   |

| N <sub>it</sub>     | cm <sup>-2</sup>                  | Interface trap density                                         |

| n                   | 5.11                              | onado hap donon,                                               |

| $N_{CP}$                                                         | cm <sup>-2</sup>                     | Trap density measured by charge pumping                                                        |

|------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------|

| $N_H^{(0)}$                                                      | cm <sup>-3</sup>                     | Hydrogen density at the interface                                                              |

| $N_H$                                                            | cm <sup>-3</sup>                     | Diffusing hydrogen atom density                                                                |

|                                                                  | cm <sup>-3</sup>                     |                                                                                                |

| $N_{H^+}$                                                        |                                      | Hydrogen ion                                                                                   |

| $N_{H_2}$                                                        | cm <sup>-3</sup>                     | Hydrogen molecule density                                                                      |

| n                                                                | -<br>3                               | Power-law time exponent                                                                        |

| n <sub>i</sub>                                                   | cm <sup>-3</sup><br>cm <sup>-3</sup> | Intrinsic carrier concentration in silicon Concentration of detrapping states at substrate     |

| n <sub>s</sub><br>n <sub>G</sub>                                 | cm <sup>-3</sup>                     | Concentration of detrapping states at substrate  Concentration of detrapping states at poly-Si |

| N <sub>D</sub>                                                   | cm <sup>-3</sup>                     | Substrate doping                                                                               |

| $\Delta N_{it}$                                                  | cm <sup>-2</sup>                     | NBTI-induced interface trap density                                                            |

| $\Delta N_{ot}$                                                  | cm <sup>-2</sup>                     | NBTI-induced oxide trap density                                                                |

| $\Delta N_{bt}$                                                  | cm <sup>-2</sup>                     | NBTI-induced border trap density                                                               |

| $\Delta N_{ht}$                                                  | cm <sup>-2</sup>                     | NBTI-induced hole trap density                                                                 |

| $n_T$                                                            | cm <sup>-3</sup> eV <sup>-1</sup>    | Volume density of the oxide-trap                                                               |

| $N_{t}$                                                          | cm <sup>-2</sup>                     | Total density of localized states                                                              |

| q                                                                | С                                    | Electron charge                                                                                |

| $Q_{ss}$                                                         | C                                    | Surface state charge                                                                           |

| $egin{aligned} Q_{it} \ Q_{ot} \end{aligned}$                    | C<br>C<br>C                          | Interface-trapped charge Oxide-trapped charge                                                  |

| $Q_{bt}$                                                         | C                                    | Border charge                                                                                  |

| $Q_{CP}$                                                         | Č                                    | Charge recombined per cycle                                                                    |

| $Q_{CP,H}$                                                       | С                                    | Charge recombined per cycle at $f_H$                                                           |

| $Q_{CP,L}$                                                       | С                                    | Charge recombined per cycle at $f_L$                                                           |

| $Q_f$                                                            | C<br>C<br>C<br>C<br>C<br>C           | Fixed charge                                                                                   |

| $Q_m$                                                            | C                                    | Mobile oxide charge                                                                            |

| $egin{aligned} Q_{\mathit{inv}} \ Q_{\mathcal{T}} \end{aligned}$ | C                                    | Mobile charge of the inversion layer<br>Total charge in the Si/SiO <sub>2</sub> system         |

| S                                                                | decade/V                             | Subthreshold slope                                                                             |

| SS                                                               | V/decade                             | Subthreshold swing                                                                             |

| t                                                                | S                                    | Time                                                                                           |

| $t_{str}$                                                        | S                                    | Stress time                                                                                    |

| $t_{em,e}$                                                       | S                                    | Electron emission time                                                                         |

| $t_{em,h}$                                                       | S                                    | Hole emission time Rise time                                                                   |

| $t_r$ $t_f$                                                      | s<br>s                               | Fall time                                                                                      |

| $t_{acc}$                                                        | S                                    | Electron capture time during accumulation of pMOSFET                                           |

| t <sub>inv</sub>                                                 | S                                    | Hole capture time during inversion of pMOSFET                                                  |

| $T_H$                                                            | S                                    | High level voltage duration                                                                    |

| $T_L$                                                            | S                                    | Low level voltage duration                                                                     |

| $T T_0$                                                          | °C<br>°C                             | temperature<br>Reference temperature                                                           |

| T <sub>S</sub>                                                   | -                                    | Tunneling probability of holes from Si/SiO <sub>2</sub> to trap                                |

| $T_{G}$                                                          | -                                    | Tunneling probability from trap to poly                                                        |

| $T_{ox}$                                                         | Å                                    | Gate oxide thickness                                                                           |

| $V_{th0}$                                                        | V                                    | Unstressed threshold voltage                                                                   |

| $V_{th}$                                                         | V                                    | Threshold voltage                                                                              |

| $V_{fb}$                                                         | V<br>V                               | Flatband voltage                                                                               |

| V <sub>L</sub><br>V <sub>H</sub>                                 | V<br>V                               | Pulse low level voltage Pulse high level voltage                                               |

| $\Delta V_{th}$                                                  | V                                    | NBTI-induced threshold voltage shift                                                           |

| $\Delta V_{G}$                                                   | V                                    | Pulse amplitude                                                                                |

| $V_D$                                                            | V                                    | Drain voltage                                                                                  |

| Vs                                                               | V                                    | Source voltage                                                                                 |

| $V_{G}$                                                          | V                                    | Gate voltage                                                                                   |

| $V_R$                                                            | V<br>V                               | Reverse voltage                                                                                |

| $V_{Gstr} \ V_{GS}$                                              | V<br>V                               | Stress voltage Gate/source voltage                                                             |

| • 68                                                             | v                                    | Cato/obtito voltage                                                                            |

| $V_{DS}$                              | V                                                                                                  | Drain/source voltage                                                                  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| $\Delta V_{it}$                       | V                                                                                                  | Voltage shift induced by interface-trap                                               |

| $\Delta V_{bt}$                       | V                                                                                                  | Voltage shift induced by border-trap                                                  |

| $\Delta V_{ot}$                       | V                                                                                                  | Voltage shift induced by oxide-trap                                                   |

| $W_{G}$                               | ců                                                                                                 | Gate width                                                                            |

| Z                                     | Å                                                                                                  | Depth distance in the oxide                                                           |

| $Z_0$                                 | Å<br>Å                                                                                             | Interface roughness thickness ( $Z_0 \sim 3.2 \text{ Å}$ )                            |

| Z <sub>max</sub><br>Z                 | Å                                                                                                  | Maximum depth in the gate oxide<br>Minimum distance                                   |

| $Z_{min}^{CP} \ Z_{n(p)}^{CP}$        | Å                                                                                                  | Maximum CP tunneling depth of electron(hole)                                          |

|                                       | V/°C                                                                                               |                                                                                       |

| $\stackrel{lpha}{eta}$                | V/ C                                                                                               | Threshold voltage temperature coefficient                                             |

| •                                     | Å                                                                                                  | Dispersion parameter                                                                  |

| $rac{\delta}{\delta'}$               | A                                                                                                  | Length of Si-H bond (1.5 Å) Dirac function                                            |

| -                                     | F.cm <sup>-1</sup>                                                                                 | Permittivity of the silicon                                                           |

| $\mathcal{E}_{Si}$                    | F.cm <sup>-1</sup>                                                                                 |                                                                                       |

| $\mathcal{E}_0$                       | F.CIII                                                                                             | Permittivity of the air Dielectric constant of the silicon                            |

| $\mathcal{E}_{SC}$                    |                                                                                                    |                                                                                       |

| $\mathcal{E}_{OX}$                    | -1/                                                                                                | Dielectric constant of the oxide                                                      |

| $\phi_{F}$                            | eV                                                                                                 | Fermi-level energy                                                                    |

| $\phi_{ms}$                           | eV<br>eV                                                                                           | Metal-semiconductor work function  Energy barrier height for (electron)hole tunneling |

| $\stackrel{\phi_{n(p)}}{\mathcal{X}}$ | eV                                                                                                 | Semiconductor electron affinity                                                       |

| $\chi_i$                              | eV                                                                                                 | Insulator electron affinity                                                           |

|                                       | Å                                                                                                  | ·                                                                                     |

| $\lambda_{n(p)}$                      |                                                                                                    | Attenuation coefficient for electron (hole)                                           |

| γ                                     | cm/V                                                                                               | field accelerator factor                                                              |

| $\mu_{\scriptscriptstyle 0}$          | $cm^2V^{-1}s^{-1}$                                                                                 | Low vertical electric field mobility                                                  |

| $\mu_{	ext{eff}}$                     | cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup><br>cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | Carrier effective mobility                                                            |

| $\mu_{H^+}$                           |                                                                                                    | Hydrogen ion mobility                                                                 |

| ν                                     | Hz                                                                                                 | Attempt frequency                                                                     |

| $V_{sat}$                             | cm/s                                                                                               | Saturation velocity                                                                   |

| $\mathcal{V}_{thp}$                   | cm/s                                                                                               | Thermal velocity of hole                                                              |

| $\mathcal{V}_{thn}$                   | cm/s                                                                                               | Thermal velocity of electron                                                          |

| $ ho_{ht}$                            | cm <sup>-3</sup>                                                                                   | Density of trapped holes                                                              |

| $\sigma_n$                            | cm <sup>2</sup>                                                                                    | Capture cross section of electron                                                     |

| $\sigma_{p}$                          | cm <sup>2</sup>                                                                                    | Capture cross section of hole                                                         |

| σ                                     | eV                                                                                                 | Spread of trap energy distribution                                                    |

| au                                    | S                                                                                                  | Electron transit time from source to drain                                            |

### **PREAMBLE**

The metal-oxide-semiconductor field oxide transistor (MOSFET) was invented in 1960 and integrated circuits (ICs) using these new transistors which were commercially available few years later. Since that time, IC manufacturing faced major yield and reliability concerns. At the beginning, quality targets were believed to be reached and products to be free of defects or systematic failures, after final packaging. The constantly growing complexity of IC products and the increasing cost incurred by loss of operation caused by failures have made reliability, maintainability, availability, and safety, critical points. Consequently, today expectations is that IC products are not only free from defects and systematic failures at time t = 0 (when they are used at the first time), but also perform the required function without failure for a stated time interval. However, the question of whether a given item will operate without failures during a stated period of time cannot be answered by a simple yes or no, on the basis of a compliance test. Experience has shown that only a probability for this occurrence can be given. Therefore, reliability is the probability that the item will perform its required function under given conditions for a defined time interval.

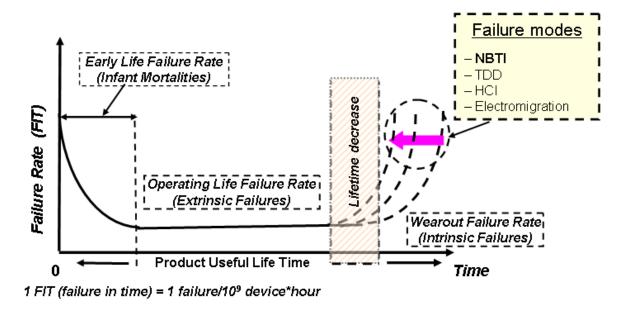

As reliability issues become nowadays more critical parameter in IC fabrication, modeling is increasingly requested to provide design tools not only to achieve better device performance, but also more robust reliability margins. Modeling is required for the theoretical investigation of the failure mechanisms and their root causes, but also it is needed to explore their relationships with front- and back-end-of-the-line technology on one hand and with design needs and test effectiveness on the other hand. Since failures are mostly related to the presence of defects and traps in active and passive layers, modeling is expected not only to investigate the intrinsic defects associated with new materials and their interfaces, but also extrinsic defect creation mechanisms during wafers processing, such as plasma damage and ion implantation induced damage in gate stacks. **Figure 1** illustrates the failure rate over time for a given set of devices. The failure follows distribution referred as bath tub curve.

Figure 1: Reliability Bath Tub Curve

Early failures (infant mortalities) occur primarily to process defects, such as the introduction of extrinsic impurities, improper deposition bonding materials, or the deposition of excess material causing an errant conduction pathway. Once these devices have failed, the failure rate level becomes constant for the useful lifetime of the device. Wearout mechanisms begin to increase at the end and play a significant role. However, failure modes, such as hot carrier injection (HCI), time dependent dielectric breakdown (TDDB), electromigration, and negative bias temperature instability (NBTI), shift the right edge of the bath tub to the left causing reduction of the useful life time (or end of life).

However, among all failure modes, the root causes of NBTI are still under a controversial debate. While most researchers agree that the creation of oxide and interface charges is at the origin of NBTI, models are often different. It has been revealed that the degradation is particularly difficult to predict under dynamic (stress and recovery) bias conditions. Lacking a suitable model for the description of the degradation under arbitrary bias conditions, the degradation of a transistor in a realistic circuit setting is hard to predict. Model development is particularly slowed down by the difficulties of fitting the experimental data. As such, model evaluation is closely tied to the development and detailed understanding of fundamental physical mechanisms of trap creation and annealing during wafer processing as well as under operating conditions. This predictive model for BTI (p-MOSFET and n-MOSFET) can assist design for reliability through electrical simulation and behavioral level modeling of degradation to check impact on analog/digital circuits.

## CONTENTS

| Acknowledgement                                               | i   |

|---------------------------------------------------------------|-----|

| الملخص                                                        | ii  |

| Résumé                                                        | iii |

| Abstract                                                      | iv  |

| ACRONYMS                                                      | V   |

| List of Symbols                                               | vii |

| Preamble                                                      | х   |

| Contents                                                      | xii |

| Introduction                                                  | 1   |

| CHAPTER I: NBTI MODELS AND RELATED-DEFECT IN MOSFET DEVICES   |     |

| I.1 Introduction                                              | 7   |

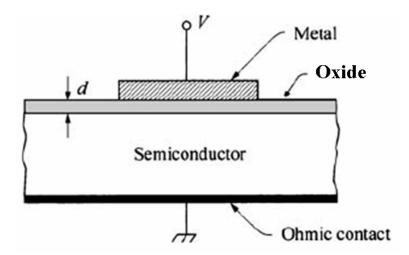

| I.2- Metal Oxide Semiconductor (MOS) system                   | 7   |

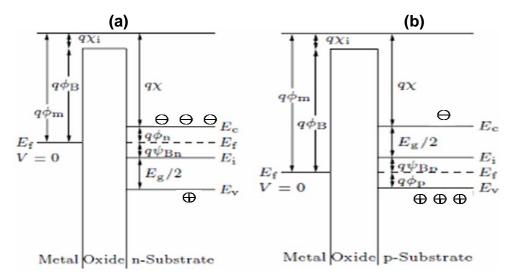

| I.2.1- Ideal case                                             | 7   |

| I.2.2- Non-ideal case                                         | 9   |

| I.3- Metal Oxide Semiconductor Field Transistor (MOSFET)      | 10  |

| I.3.1- Principles of operation                                | 10  |

| I.3.2- Charge of the inversion layer                          | 12  |

| I.3.3- Drain current                                          | 12  |

| I.4- Microstructures of Defects in Si-SiO <sub>2</sub> System | 13  |

| I.4.1- Defects at the Si/SiO <sub>2</sub> interface           | 14  |

| I.4.2- Amphoteric nature of interface traps                   | 16  |

| I.4.3- Defect in SiO <sub>2</sub> oxide                       | 17  |

| I.4.4- Interfacial sub-oxide region                           | 18  |

| I.4.5- Border traps                                           | 19  |

| I.4.6- Hydrogen-related defect                                | 20  |

| I.5- NBTI Reaction-Diffusion (R-D) Model                      | 22  |

| I.5.1- Stage 1                                                | 23  |

| I.5.2- Stage 2                                                           | 23 |

|--------------------------------------------------------------------------|----|

| I.5.3- Stage 3                                                           | 23 |

| I.5.4- Case of H <sup>+</sup> diffusion                                  | 24 |

| I.5.5- Case of H <sub>2</sub> diffusion                                  | 25 |

| I.5.6- R-D model for NBTI relaxation phase                               | 25 |

| I.5.7- Generalized R-D model                                             | 26 |

| I.5.8- Physical hole-assisted, field-enhanced, thermal Si-H dissociation | 27 |

| I.6- Reaction-Diffusion (R-D) Variant Models                             | 29 |

| I.6.1- Reaction-dispersive-diffusion (RDD) model                         | 29 |

| I.6.2- Dispersive-reaction-rate (DRR) model                              | 30 |

| I.6.3- Hole-trapping in R-D model                                        | 3′ |

| I.7- NBTI Two-Stage Model                                                | 34 |

| I.8- NBTI Gate Oxide Thickness Dependence                                | 38 |

| I.9- Discussion                                                          | 39 |

| I.10- Conclusion                                                         | 4  |

| CHAPTER II: NBTI CHARACTERIZATION METHODS                                |    |

| II.1- Introduction                                                       | 42 |

| II.2- Charge-Pumping ( <i>C-P</i> ) Technique                            | 42 |

| II.2.1- Charge-pumping current model                                     | 4: |

| II.2.2- Trap profiling by charge-pumping technique                       | 4  |

| II.3- Transistor Drain Current for Different Modes                       | 4  |

| II.3.1- Drain current in linear mode                                     | 4  |

| II.3.2- Drain current in saturation mode                                 | 5  |

| II.3.3- Drain current in subthreshold mode                               | 5  |

| II.4- Classical Measure-Stress-Measure (MSM)                             | 5  |

| II.5- Parameter Extraction of MSM Methods                                | 5  |

| II.5.1- Measure around V <sub>th</sub> methods                           | 5  |

| II.5.2- Subthreshold Swing (SS) method                                   | 5  |

| II.5.3- ΔV <sub>th</sub> and ΔSS extraction                              | 5  |

| II.6- On The Fly $V_{th}$ (OTF- $V_{th}$ ) Methods                              | 54 |

|---------------------------------------------------------------------------------|----|

| II.6.1- One point on the fly method                                             | 55 |

| II.6.2- Three points on the fly method                                          | 55 |

| II.7- On The Fly Interface Trap (OTFIT)                                         | 58 |

| II.8- Conclusion                                                                | 59 |

| CHAPTER III: EXPERIMENT DETAILS                                                 |    |

| III.1- Introduction                                                             | 60 |

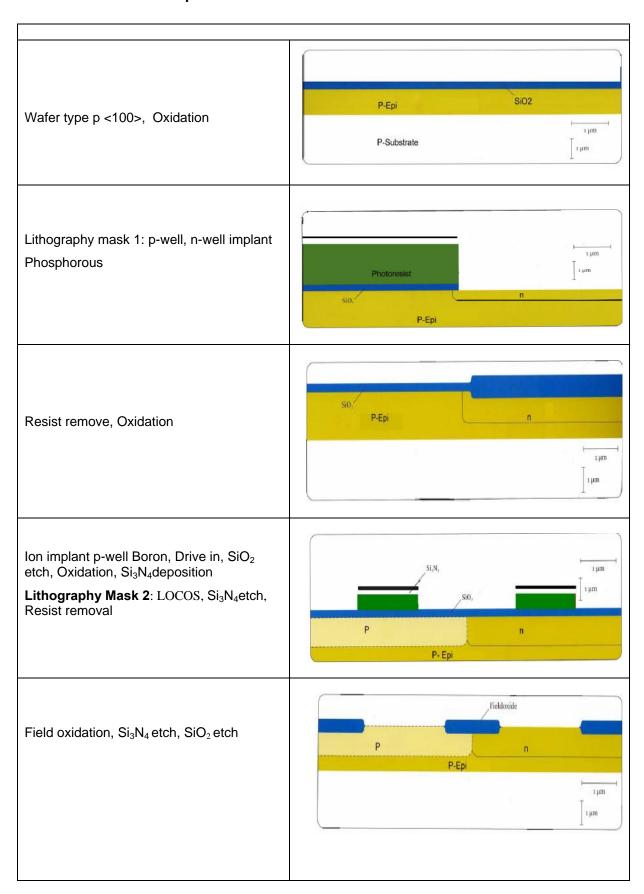

| III.2- Devices and Process Details                                              | 60 |

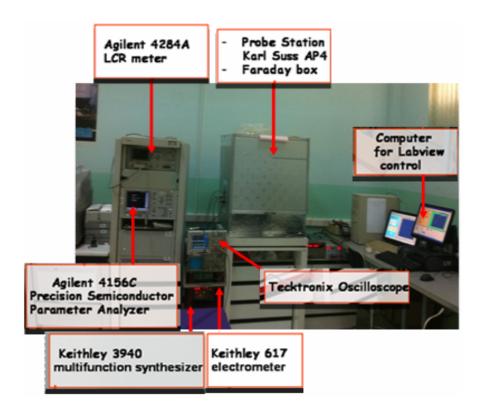

| III.3- Measurement Setup Details                                                | 61 |

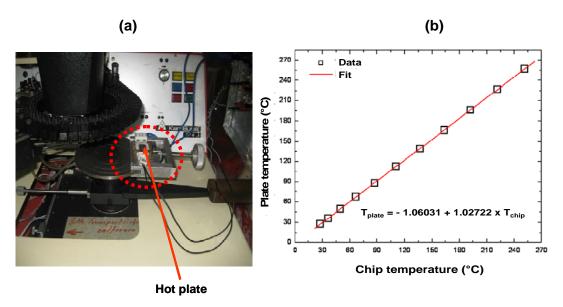

| III.3.1- Hot plate                                                              | 63 |

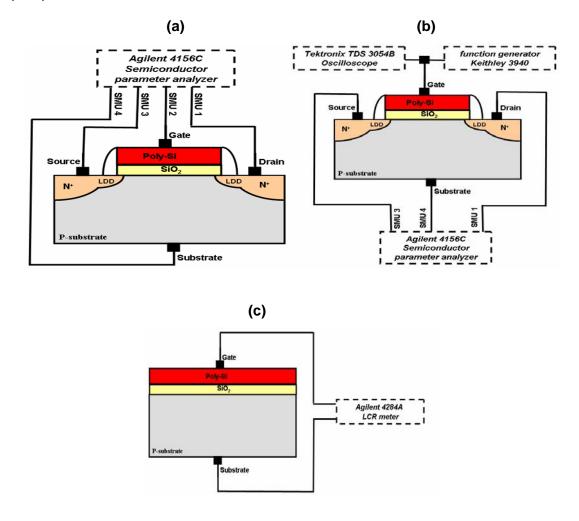

| III.3.2- Standard electrical techniques                                         | 63 |

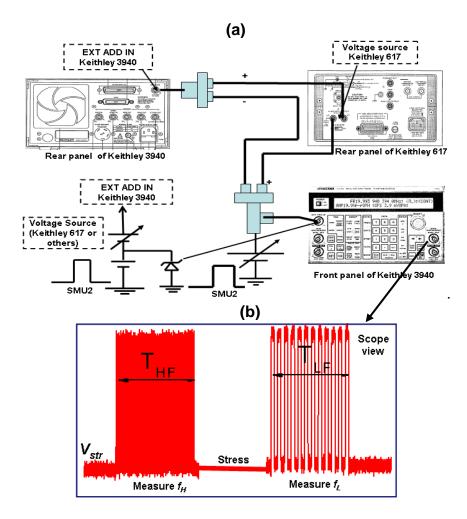

| III.3.3- Special setup                                                          | 65 |

| III.4- Characterization Before NBTI Stress                                      | 66 |

| III.4.1- Current-Voltage (I <sub>DS</sub> -V <sub>GS</sub> ) characteristics    | 66 |

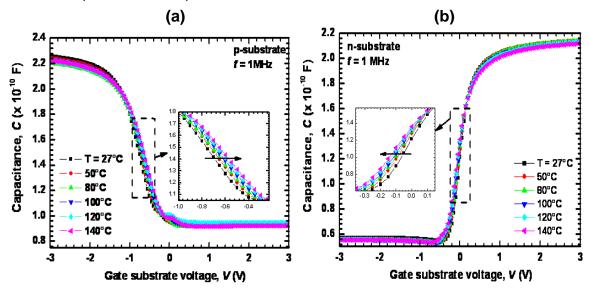

| III.4.2- Capacitance-Voltage (C-V) characteristics                              | 68 |

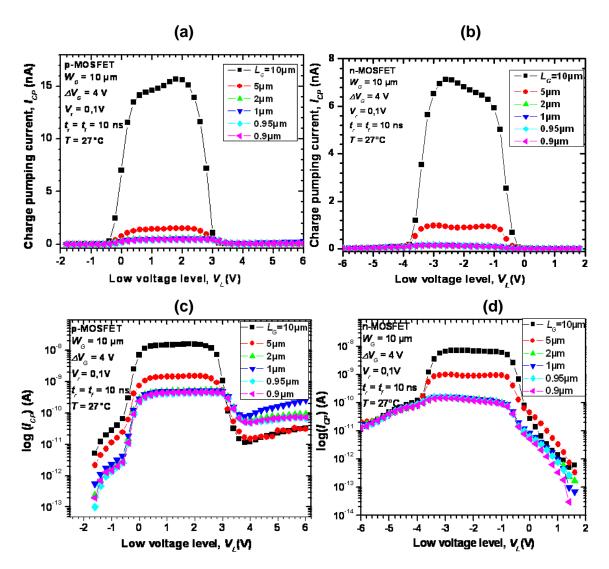

| III.4.3- Charge-Pumping (C-P) characteristics                                   | 68 |

| III.5- Temperature Effect on MOS Device Characteristics                         | 69 |

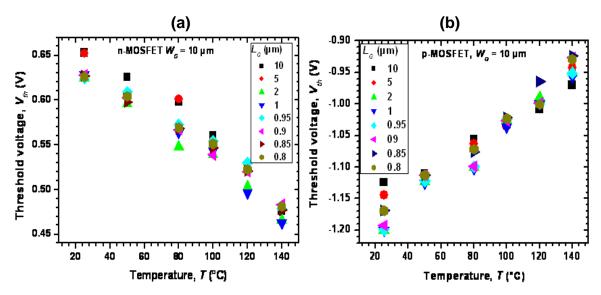

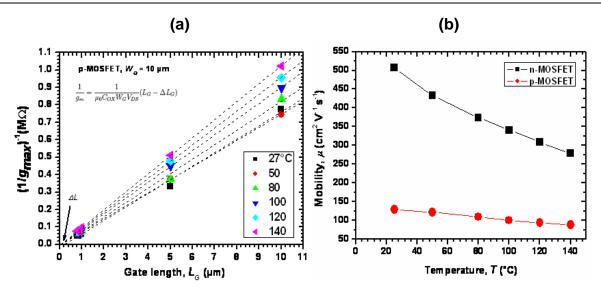

| III.5.1- Temperature effect on I <sub>DS</sub> -V <sub>GS</sub> characteristics | 69 |

| III.5.2- Temperature effect on C-V characteristics                              | 72 |

| III.5.3- Temperature effect on C-P characteristics                              | 74 |

| III.6- Bias Temperature Combined Stress on MOS Devices                          | 74 |

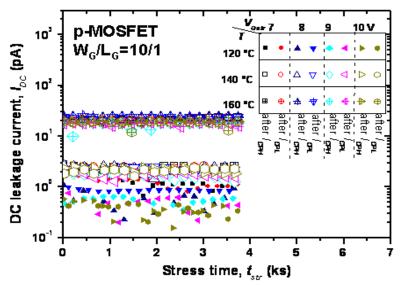

| III.6.1- BTI and Mobile ionic charge                                            | 75 |

| III.6.2- NBTI versus PBTI in p-MOS and n-MOS transistors                        | 76 |

| III.7- Conclusion.                                                              | 80 |

| CHAPTER IV: ON THE FLY OXIDE TRAP METHOD (OTFOT): EXTRACTION AND                |    |

| Analysis of NBTI Degradation Parameters                                         |    |

| IV.1- Introduction.                                                             | 81 |

| IV.2- Theory and Concept of OTFOT Method                                        | 82 |

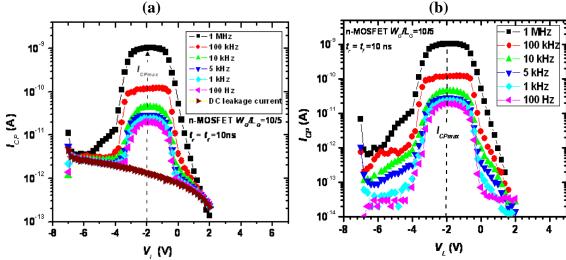

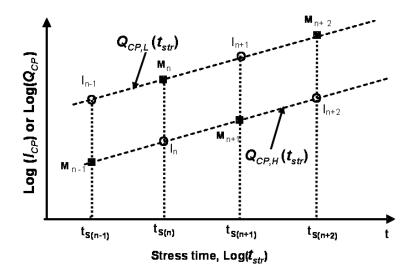

| IV 2.1. Charge recombined per cycle $\Omega_{co} = l_{co}/f$ Characteristics    | 82 |

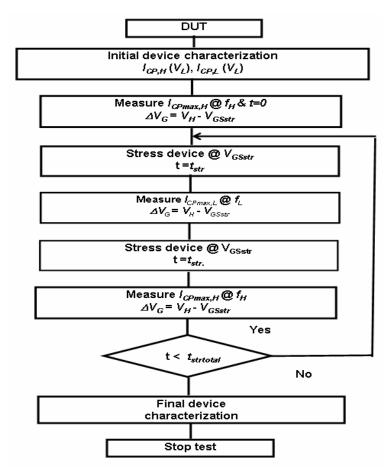

| IV.2.2- Measure/stress/measure (M/S/M) protocol of OTFOT method           | 83   |

|---------------------------------------------------------------------------|------|

| IV.2.3- OTFOT method Equations                                            | 85   |

| IV.3- Experimental Conditions                                             | 87   |

| IV.4- NBTI-induced Interface and Oxide Traps                              | 88   |

| IV.5- Time, Temperature, and Electric Field Dependence of NBTI            | 92   |

| IV.5.1- NBTI-Time dependence                                              | . 93 |

| IV.5.2- NBTI-Temperature dependence                                       | 94   |

| IV.5.2- NBTI-field dependence                                             | 96   |

| IV.6- Empirical Life Time Estimation                                      | 98   |

| IV.7- Gate Length Dependence of NBTI                                      | . 98 |

| IV.8- Geometric Component Effect in OTF CP-Based Methods                  | 100  |

| IV.9- NBTI Effect in LDD Region                                           | 102  |

| IV.10- Discussion                                                         | 104  |

| IV.11- Conclusion.                                                        | 105  |

| CHAPTER V: NBTI PERMANENT COMPONENT PROPAGATION CONCEPT                   |      |

| V.1-Introduction                                                          | 106  |

| Part I: Lateral Propagation of the Permanent Component                    | 107  |

| V.2- Lateral Profiling Experiments                                        | 107  |

| V.2.1- Lateral profiling before NBTI stress                               | 108  |

| V.2.2- Lateral profiling After NBTI stress                                | 108  |

| V.3- NBTI-Induced Interface-Trap Propagation                              | 109  |

| V.4- Time, Temperature, and Electric Field Dependence of △N <sub>it</sub> | 113  |

| V.5- <i>∆N<sub>it</sub></i> Propagation Result Analysis and Discussion    | 116  |

| Part II: Vertical Propagation of the Permanent Component                  | 118  |

| V.6- Vertical Profiling Experiments                                       | 118  |

| V.6.1- Vertical profiling before NBTI stress                              | 118  |

| V.6.2- Vertical profiling after NBTI stress                               | 119  |

| V.6.3- Extraction method of border-trap density                           | 120  |

| V.6- Depth Profiling of NBTI-Induced Border-Trap                          | 121  |

| V.7-Time and Temperature Dependence of $\Delta N_{bt}$                   | 123 |

|--------------------------------------------------------------------------|-----|

| V.7.1- Time dependence of NBTI-induced $\Delta N_{bt}$                   | 123 |

| V.7.2- Temperature dependence of NBTI                                    | 123 |

| V.7.3- $a_{eff}$ and $E_a$ distributions in the interfacial oxide layer  | 125 |

| V.8- Possible Defect Precursors Related to NBTI-Induced △N <sub>bt</sub> | 127 |

| V.9- △N <sub>bt</sub> profile Result Analysis and Discussion             | 130 |

| V.10- Conclusion                                                         | 131 |

| VI- CONCLUSIONS AND PERSPECTIVES                                         |     |

| VI.1- Conclusion and Perspectives                                        | 133 |

| References                                                               | 135 |

| List of Own Publications Related to this Work                            | 146 |

| Appendices                                                               | 147 |

| Appendix A                                                               | 147 |

| Appendix B                                                               | 151 |

| Appendix C                                                               | 154 |

| Appendix D                                                               | 158 |

| Appendix E                                                               | 167 |

### INTRODUCTION

Since its invention, metal oxide semiconductor field effect transistor (MOSFET) has revolutionized semiconductor industry. It has allowed the development of the integrated circuits by placing a large number of transistors on a single chip. As predicted by Moore's law [1], the integration complexity has doubled every 18 months, affecting many aspects of our life. The continuous downsizing of the device has greatly advanced the semiconductor industry by increasing the performance, decreasing the power consumption, and reducing the manufacturing cost per transistor of IC components. This makes products smaller, faster, and cheaper. At present, there are more than a billion of transistors in microprocessor. This integration has been drained by reducing the transistor critical elements such as the channel gate length and the gate dielectric thickness. However, when the gate oxide thickness had reached the 1 nm range and the gate length the 100 nm in the early 2000s, the conventional MOSFET scaling trend began to run out. The deviation from conventional scaling was firstly caused by the exponentially increase of the gate leakage current. Conventional scaling also required a continuous reduction of the chip supply voltage  $(V_{DD})$  as the gate oxide thickness was scaled to maintain a constant oxide electric field, and consequently it also required a corresponding device threshold voltage  $(V_{th})$  reduction. Due to the non-scaling subthreshold slope of the MOSFET, a reduced device  $V_{th}$  unavoidably induced subthreshold leakage current increase, which started to become itself another large portion of total chip power. For these reasons, conventional geometrical scaling had to come to run out. However, performance enhancements did not stop in the early 2000s but keep still going due to introduction of three main innovations in the recent CMOS technology nodes: channel strain engineering for mobility enhancement (90 and 65 nm nodes), high-k/metal gate technology for reduced gate leakage current (45 and 32 nodes), tri-gate device architecture for improved electrostatic control (22 nm node). Actually, the aggressive scaling of MOS transistor toward 22 nm technology node has arisen a statistical (device to device, die to die, wafer to wafer, etc.) fluctuation of transistor parameters. These fluctuations, in nano-dimensions, could have been easily ignored in micron-size transistors of 1990s, but cannot be avoided in nano-scale transistors studied in current MOS technology.

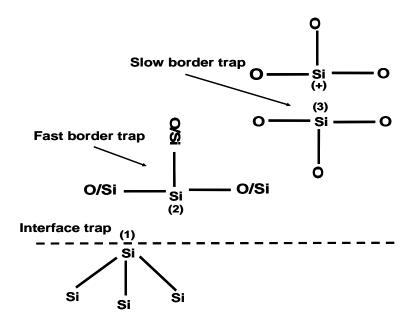

Additionally, defects in the Si-SiO<sub>2</sub> system were always a source of instabilities of MOS devices and their long term reliability. They are either pre-existing in the Si-SiO<sub>2</sub> system due to poor fabrication process or induced by stress. Historically, the pre-existing defects as such the mobile ions  $(Q_m)$ , fixed oxide charge  $(Q_t)$ , and oxide traps  $(Q_{ot})$  were the major obstacles in the development of stable MOSFETs in the 60s. However, after the identification of its origin, it has been eliminated by the combination of cleanroom environment, deionized water and gettering processes. The fixed oxide charge in the bulk oxide, residing close to the interface with silicon substrate, can be minimized by appropriate oxidation recipes, and has been well controlled. In addition, defects are formed not only within the bulk of the amorphous oxide structures, but also at the Si/SiO<sub>2</sub> interface  $(Q_{tt})$  e.g., dangling bonds. This is mainly due to the lattice mismatch between two dissimilar materials combined together. However, interfacial defects cannot be removed or reduced, like bulk defects, through any sort of purification. At the Si/SiO<sub>2</sub> interface of a MOS transistor, interfacial defects (dangling Si-bonds) are passivated by using hydrogen (Si-H), which only provides a time-zero solution. However, under high

electric field and elevated temperature, interface and oxide properties may degrade by different modes:

- Gate dielectric film may breakdown under high field, and completely loses the insulating property. Dielectric breakdown is a long-standing subject in the study of IC's. The defect related transistor instabilities discussed above; formation of oxide defects and their subsequent alignment can increase the gate leakage current to such an extent that the dielectric film will no longer be effective in insulating the gate of a MOS structure, hence inducing dielectric breakdown of transistors. It is easy to see that as the oxide thickness scales down the oxide sustains less voltage. In practice, MOSFET operates at voltages much lower than the dielectric breakdown voltage, but there is still a finite probability of breakdown. Time dependent dielectric breakdown (TDDB) is a key transistor reliability issue in modern MOS transistor, which often limits its operating lifetime [2-4].

- Another failure mode is the hot carrier injection (HCI), which induces non-uniform generation of defects near the drain of MOS transistors [5]. HCI was the most critical reliability issue in the 80s and early 90s, and was extensively studied since then. It occurs when high voltage is present on both gate and drain terminal, a lot of carriers are flowing in the channel, and there is high longitudinal electric field near the drain region. Carriers are accelerated in this high-field region, and the carrier temperature increases. If the carriers gain sufficient energy, they can cross the energy barrier of the silicon/oxide interface and get injected into the insulator. Typically the maximum hot carrier generation occurs when gate voltage is around half of the drain voltage. This bias condition only occurs when the transistor is switching from off state to on state or *vice versa*. The attempt to minimize HCI led to the development of lightly doped drain (LDD) structure, the nitrided silicon oxide gate dielectric, and is one of the motivations for the scaling of supply voltage. As the supply voltage has scaled to around 1 V, which is less than the bandgap of silicon, hot carriers are much less a reliability concern to current technologies, though it is still regularly examined.

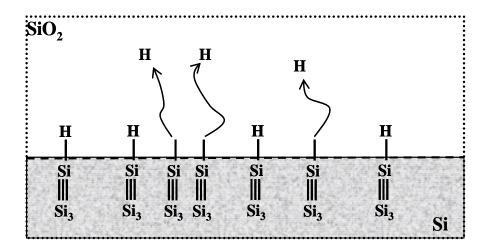

- The saturated interface dangling bonds (Si-H) break, which allows to dangling bond to reappear again during the operation of a transistor, inducing time-dependent instabilities in the transistor parameters, which is one of the major reliability concerns in current MOSFET technology. Such interface defect related instability is dominant in p-MOSFET and associated with negative bias temperature instability (NBTI) phenomenon.

Moreover, the introduction of new materials within MOS structure such as high-k gate dielectric and oxide nitride to reduce gate leakage current [6] and metal gate to avoid poly-depletion effects [7] have generated additional issues related to defects in the oxide material during NBTI stress. Consequently, hole trapping into oxide defects has become an additional NBTI mechanism and electron trapping into oxide defects of n-MOSFET associated with positive bias temperature instability (PBTI) [8]. According to the International Technology Roadmap for Semiconductor prediction [9], the physical gate length of CMOS devices can be expected to scale down to 7 nm before it approaches the physical limitation, the reliability concerns become one of the major barrier preventing the technology to scale down further. One of the consequences of non-ideal scaling in the below-100 nm technology nodes is that the electric field in the gate dielectric becomes significantly large, which accelerates the intrinsic failure mechanisms like TDDB, HCI, and so on. As the device dimensions shrink, the number of transistors per area increases, therefore in turn, the on-chip power density increases. The increasing leakage

current makes the power dissipation situation even worse. In fact, the high temperature in the circuits due to the high power density accelerates intrinsic failure mechanisms such as NBTI and PBTI. In a word, the decreasing reliability trend in advanced technology nodes is worsened due to the high gate dielectric electric field and power density in devices and circuits.

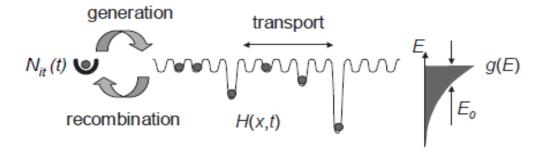

BTI is a wearout mechanism resulting in the generation of traps at the Si/SiO<sub>2</sub> interface and in the oxide under high gate voltage ( $V_G$ ) at elevated temperature. The worst degradation is observed occurring in p-MOS transistor under negative gate bias stress. In these stress conditions, the degradation is called NBTI. Typically, the NBTI stress conditions lie below a temperature of 200°C and below an electric field of ~ 5-8 MV/cm in inversion regime ( $V_G$  < 0 for p-MOSFET). Higher electric fields cause additional degradation due to stress induced leakage current (SILC) and should be avoided to capture pure (or intrinsic) NBTI damage. The most important manifestations of the NBTI degradation consist of an increase of the threshold voltage ( $V_{th}$ ) and off current ( $I_{Off}$ ), and a decrease of linear drain current ( $I_{Dlin}$ ) and saturation drain current ( $I_{Dsat}$ ), transconductance ( $g_m$ ), subthreshold slope (S), and channel carrier mobility ( $\mu_{eff}$ )

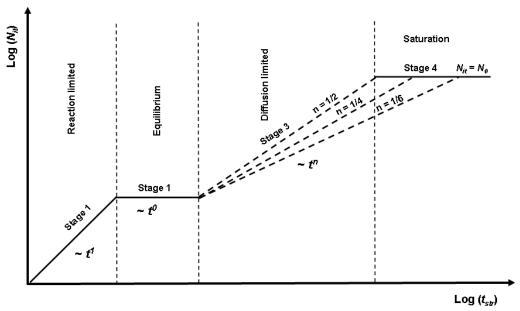

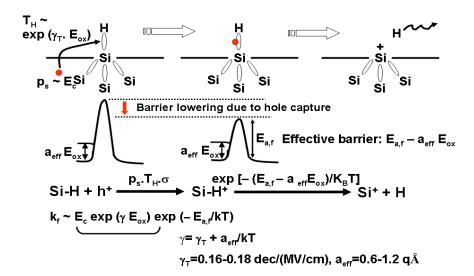

Historically, the effect of NBTI on the surface states ( $Q_{ss}$ ) was observed for the first time in the sixties by Miura et al. [10] and investigated in more details by Deal et al. [11]. However, a physical interpretation of the phenomenon started arising in 1977, when Jeppson and Svenssons proposed for the first time the Reaction-Diffusion (R-D) model to explain the NBTI-induced surface-trap growth [12]. The R-D model assumes that the gate bias initiates a field-dependent reaction at the Si/SiO<sub>2</sub> interface that generates interface traps by breaking the passivated Silicon-Hydrogen (Si-H) bonds. It can reproduce the power-law dependence of the surface trap generation without making pre-assumption on surface bonds. Even if the R-D model of Jeppson and Svenssons [12] explained the time powerlaw dependence of NBTI degradation, the exact mechanisms behind such behavior were still unclear and the causes of bond dissociation unspecified. Alam et al. [13-18] were the first to link temperature and electric field to R-D framework. Indeed, as the NBTI degradation is enhanced by high negative electric field at the interface, holes of the inverted layer of the p-MOSFET participate to Si-H bonds dissociation [14-17,19,20]. The released hydrogen species diffuse away from the interface and dimerize to form  $H_2$  molecule [19,21], subsequently explaining the observed 1/6 power-law time exponent in the experimental data [14-18]. In addition, this model gives a consistent interpretation of interface trap creation dependence on nitrogen [17,18].

However, if only holes are playing an essential role in NBTI degradation for p-MOSFET in inversion regime and since n-MOSFET biased in accumulation regime also have holes at the surface, they should show similar degradation of threshold voltage. However, they do not [22,23]. To explain this behavior, Tsetseris *et al.* [24,25] have proposed the interaction between the positive hydrogen ion ( $H^+$ ) at the interface and the Si-H bonds. Based on first-principal calculation [24], they conclude that it is more difficult for boron-hydrogen bonds to be broken in p-substrates. Thus, the different behavior of p-versus n-MOSFETs in this model is due to the ease or difficulty of breaking P–H and B-H bonds in the Si substrate. Threshold voltage shifts in this case are due to interface traps, oxide charge, and a change in the substrate doping density after P–H or B-H depassivation. Another explanation involves the interface and oxide charge states [26]. Interface traps, being acceptors in the upper half of the band gap and donors in the lower half affect threshold voltage shifts in n- and p-MOSFETs differently.

At inversion, the n-MOSFET has negative and the p-MOSFET has positive interface trap charge. Since the oxide charge is positive in both cases, then p-MOSFET is more severely affected [26].

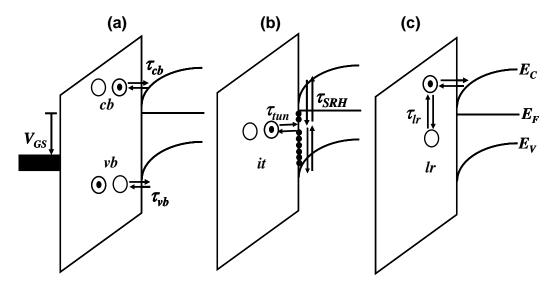

Later, it has been shown that reaction-diffusion theory presents inconsistency regarding the relaxation phase of NBTI [27-29]. That fact has led to the development of several extended and modified R-D models [30-40]. Assuming two different diffusion coefficients; fast diffusion in the oxide and slow diffusion in the polysilicon, Alam et al. [31] proposed a model named "two-region R-D model". The authors were motivated by the actual gate oxides which are a few nanometers thick making the interpretation based on the diffusion of hydrogen into the oxide questionable. Hence, they suggested that the diffusion process not only occurs in the oxide, but inside the polysilicon as well. This model was expected to explain the much larger observed recovery range, but actually this range is slightly increased. Other groups [30,32] proposed two-interface R-D model, in which a released atomic hydrogen diffuse in the oxide until reaching the polySi/oxide, where a second chemical reaction takes place at the interface creating  $H_2$  molecule. Since the diffusivity in the oxide is considered to be very high compared to the diffusivity in the polysilicon, the hydrogen stacked in the oxide is able to cause a fast initial recovery. However, for long stress times, this higher oxide diffusivity locks the hydrogen in the polysilicon. This means that the short recovery effect vanishes. In addition, immediate dimerization in the oxide was suggested in [21,34], where both H and  $H_2$  diffuse in the oxide, hence affecting the initial stress phase, but the relaxation is still the same compared to the standard R-D model. Some authors [35-37] proposed dispersive distribution of Si-H bond energy at the interface. At the beginning, the weaker Si-H bonds break, followed later by the breakage of the strong one at longer stress time or higher voltage. The charge pumping (C-P) technique, which is an appropriate tool for interface trap measurements, revealed a small recovery of interface trap after NBTI stress. This amount is not able to explain the overall recovery of the NBTI-induced threshold voltage shift. That is why the interface traps are considered as permanent component once created [35,37-40]. Dispersive hydrogen transport, so-called reaction-dispersive-diffusion (RDD) model, was also suggested to explain the long recovery tails observed in experiments [41, 42]. In this model, the hydrogen concentration is divided into a contribution of free hydrogen in a conduction state and hydrogen setting at trap with a deeper energy level, which needs to be thermally activated prior to be able to diffuse. Therefore, only hydrogen located at the interface is allowed to re-passivate the dangling bond which delays the reverse rate since most of the hydrogen is trapped.

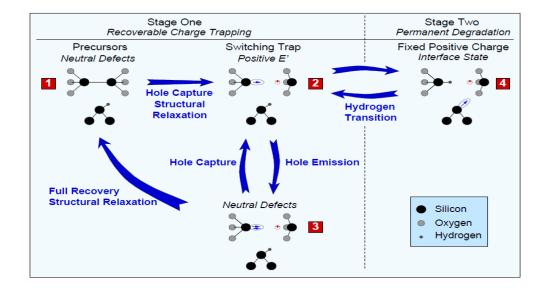

Dispersion of the defect creation is also assumed in R-D theory based models to improve the quality of the prediction [21, 42-44]. However, these models do not take into account the frequently observed correlation between the created interface states and the oxide charges [45,46]. Consequently, they often fail to reproduce the temperature and voltage dependence of the overall degradation behavior, especially the relaxation phase. In fact, investigations of the universal recovery have revealed that there exists a permanent component in addition to a recoverable component, each one of them is caused by its own physical mechanism [28,41]. The appearance of oxide traps and interface traps was explained by independent processes adding up into the two components, i.e. the recoverable and the more or less permanent part of the BTI degradation. As a result, hole trapping into defects was suggested as the recoverable component and assumed to be due to elastic tunneling of holes into preexisting traps [35]. By contrast, a hydrogen reaction like the Si-H bond breakage in the

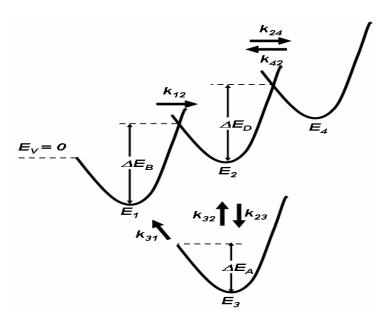

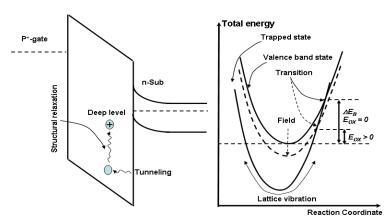

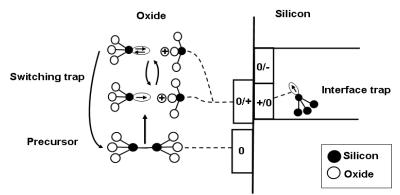

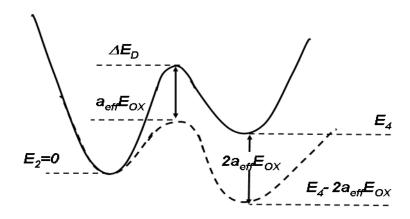

R-D model was ascribed to the permanent component. However, Grasser et al. [46] recognized that the recorded threshold voltage curves follow the same pattern at different stress temperatures and voltages. Therefore, these curves can be scaled so that they overlap for the stress and the relaxation phase. As a consequence, both mechanisms were assumed to be coupled and therefore do not take place independently. In fact, they proposed a so-called two-stage model [29], which is based on fourwell-energy model, as an alternative to R-D and its variants. In the first stage, the model assumes an inelastic tunneling of holes into deep traps, inducing E' defect creation which can be repeatedly charged and discharged by electrons tunneling in or out of its dangling bond. The associated switching behavior is in agreement with the experimental observations of relaxation component. In the second stage, the switching trap interacts with Si-H bonds, detaching the hydrogen and leaving an interface trap. Thus, the switching trap acts as a catalyst to interface state generation [29]. More recently, the two stage model has been severely criticized regarding the duration of stress time [47,48]. Indeed, the two stage model has extensively been studied for short stress time (<1s) [29,49] and recovery followed short stress time. However, when the model was extended to longer stress time, its predictions showed discrepancies with experimental observations [47]. It was concluded that there are no combination of input parameters that reproduces the observed DC, AC, and duty cycle stress dependent NBTI degradation [47]. As an alternative, Mahapatra et al. [48] suggested a framework based on H/H<sub>2</sub> conversion R-D model, in which uncorrelated contribution from interface trap generation and recovery, together with hole trapping and detrapping in preexisting and generated bulk oxide traps, are involved in NBTI phenomena.

In spite of the above-cited models proposed in several publications, no model can nowadays successfully explain all features of the BTI phenomenon. However, it is widely accepted that there are two components responsible for NBTI; permanent and recoverable components [51,52]. Regarding the origin of these components, the scientific opinion is divided whether hole trapping is insignificant and only the interface traps degrade and recover [14,48], or the switching trap drives the interface state generation [29], or interface trap generation leads to the formation of a positive oxide trapped charge [12]. While some authors [29] claim that both components are coupled, others don't find any apparent relationship between them (uncorrelated) [48,50]. One component is fast and generally attributed to recoverable NBTI, while the second is permanent [22,40]. The fast component is ascribed to hole trapping/detrapping into/from hole oxide traps [53,54]. Since, the recoverable component is fast, only fast measurement could capture it. That is why, Ming-Fu Li et al. [54,55] proposed fast electrical measurement methods to overcome the measurement delay and reduce the relaxation effect of the classical methods [56,57]. They showed that the power-law time exponent (n) dependence of NBTI degradation is highly affected by the measurement methods [53,54]. However, this has not resolved the controversial debate regarding the NBTI components as well as the exponent, n. Indeed Gasser et al. [58] have later shown that the so-called permanent actually is not so permanent and is recoverable at large timescale. This quasi-permanent component is itself constituted of two subcomponents, one attributed to the interface traps and the other to slower switching oxide traps [58]. More recently, based on spin dependent recombination (SDR), Aichinger et al. [59,60] have identified the microstructure defects of the quasi-permanent component. Besides the conventional  $P_{b0}$  center for

interface traps, they have also evidenced  $P_b$  center-hydrogen complexes for slower switching oxide traps.

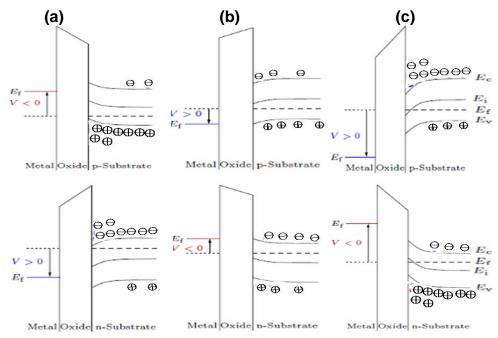

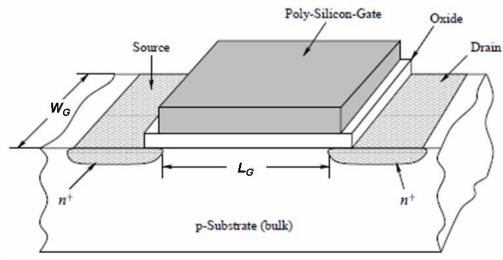

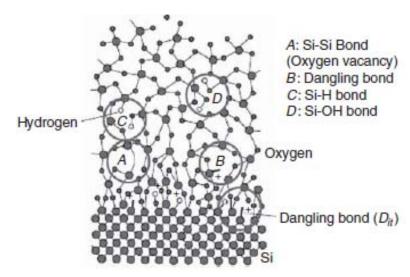

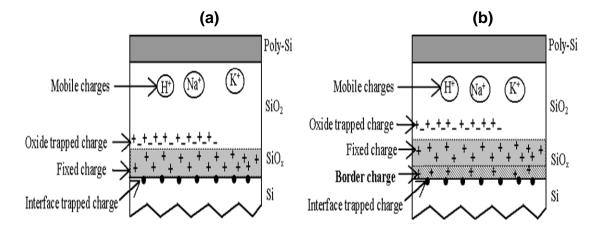

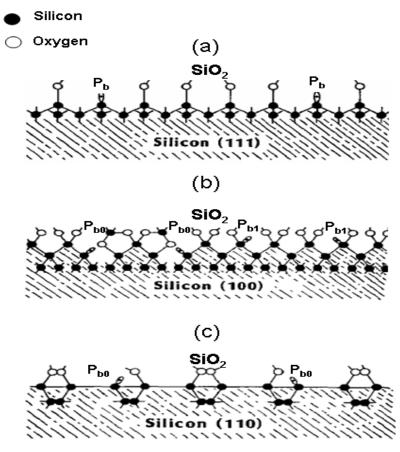

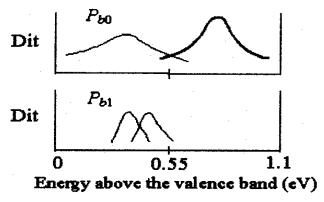

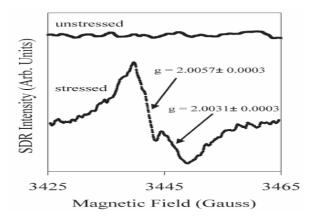

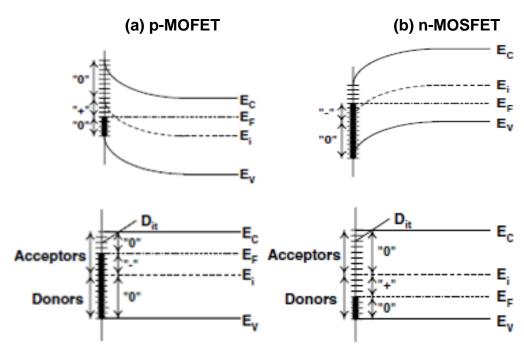

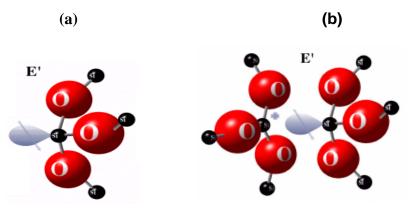

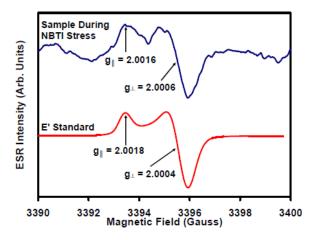

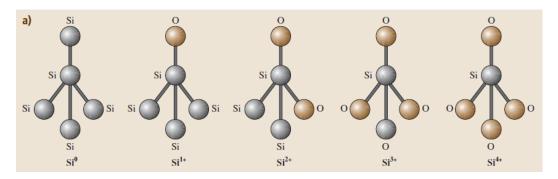

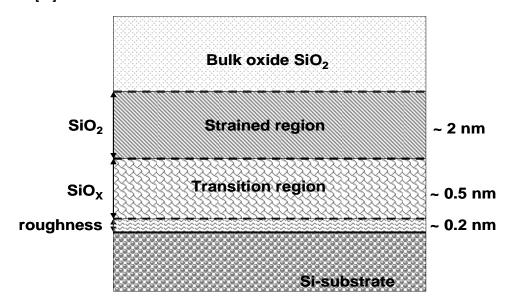

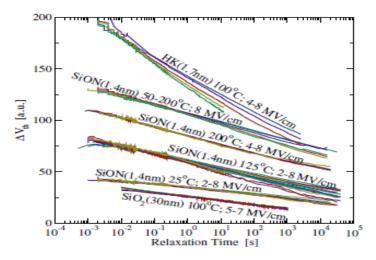

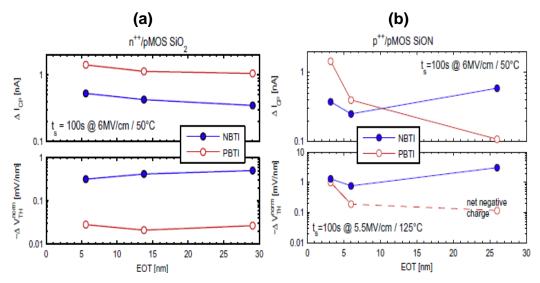

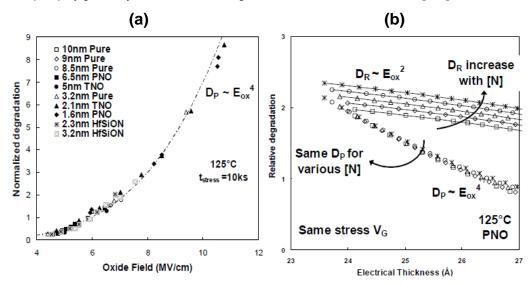

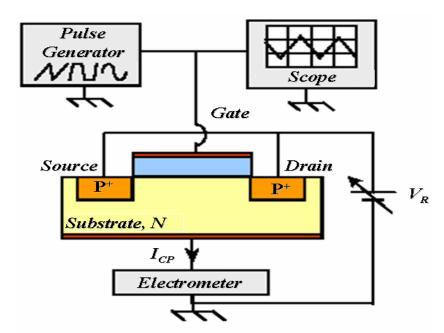

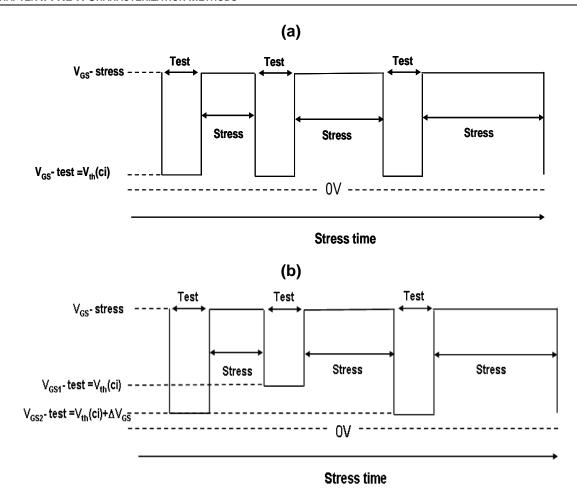

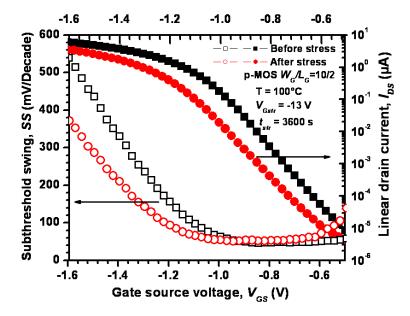

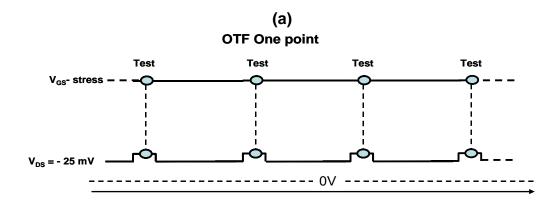

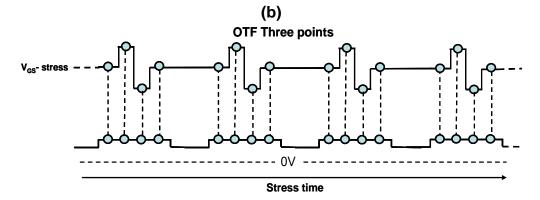

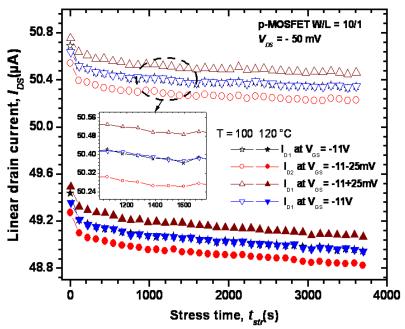

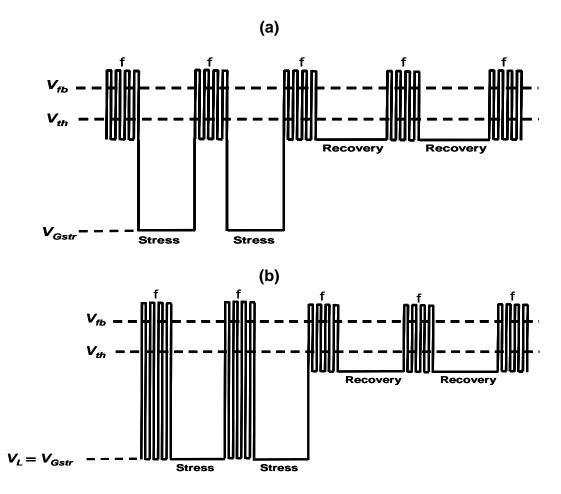

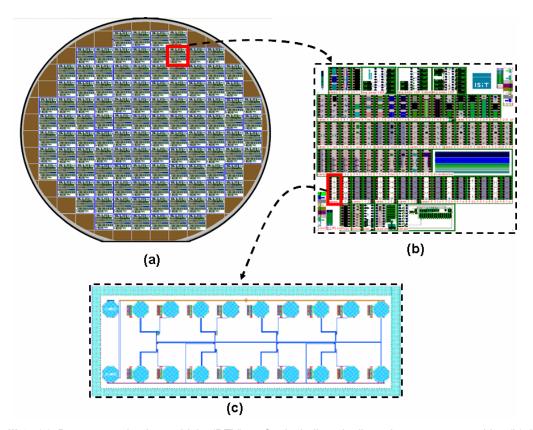

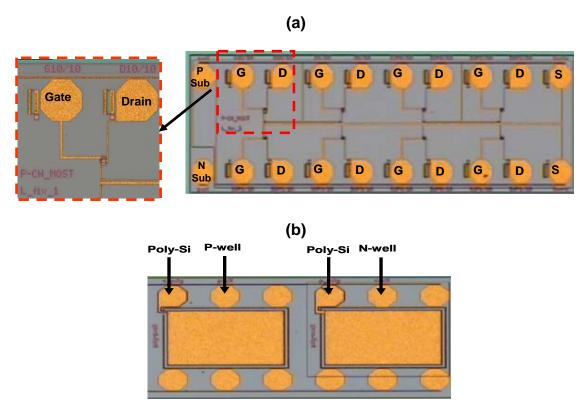

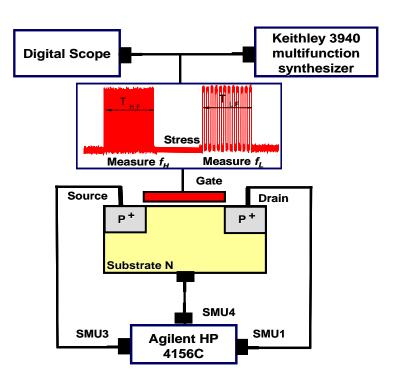

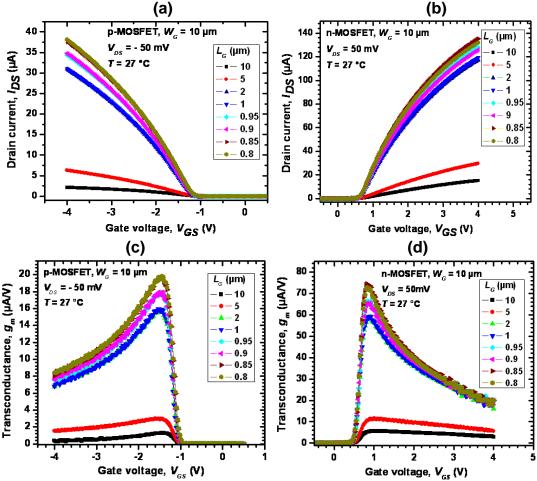

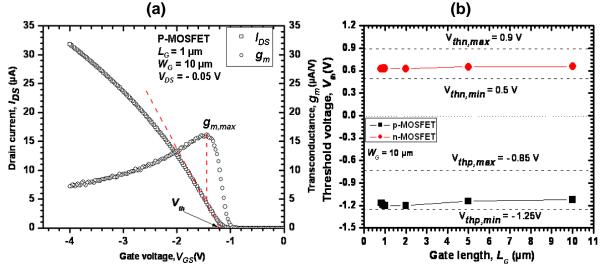

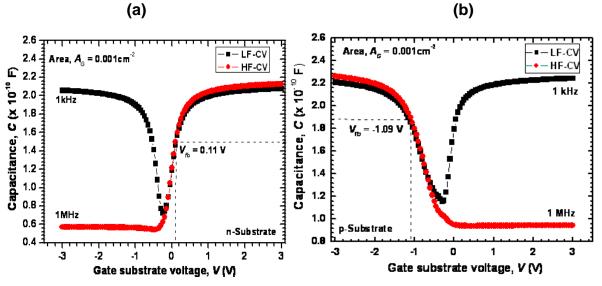

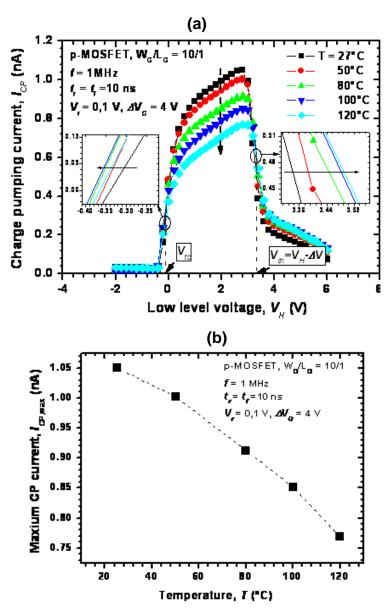

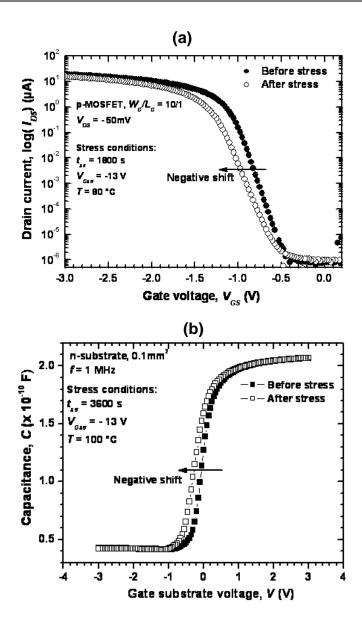

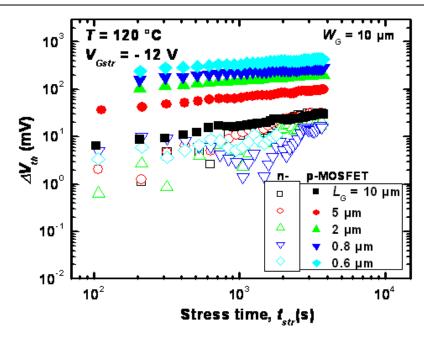

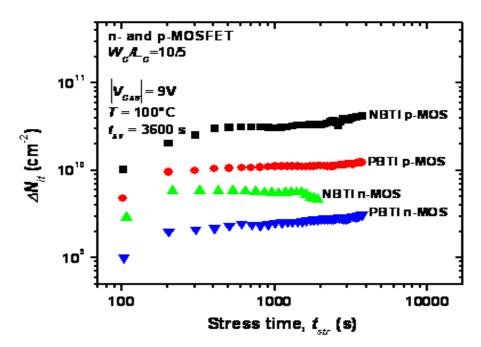

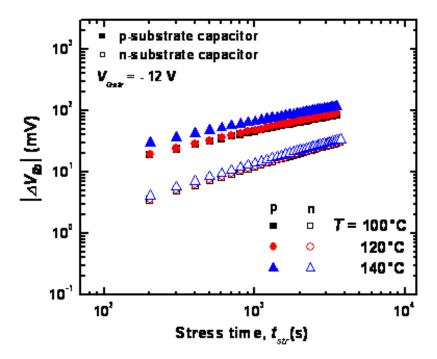

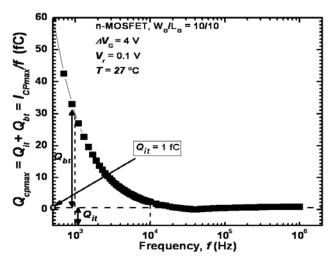

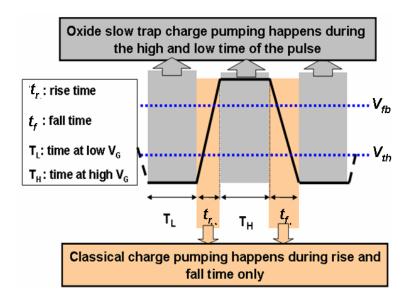

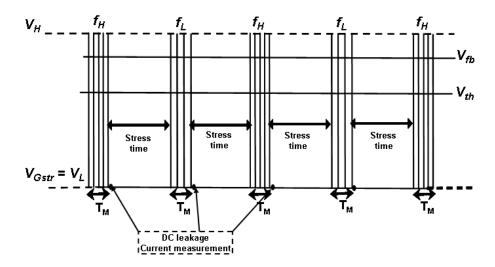

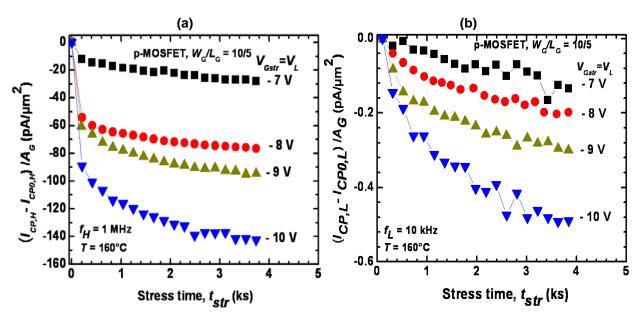

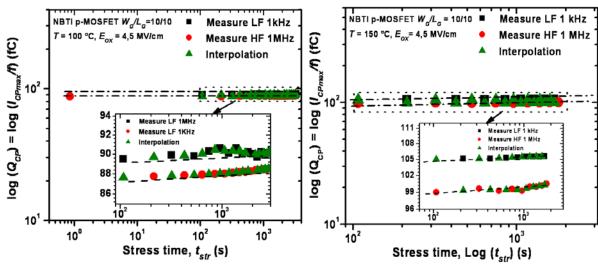

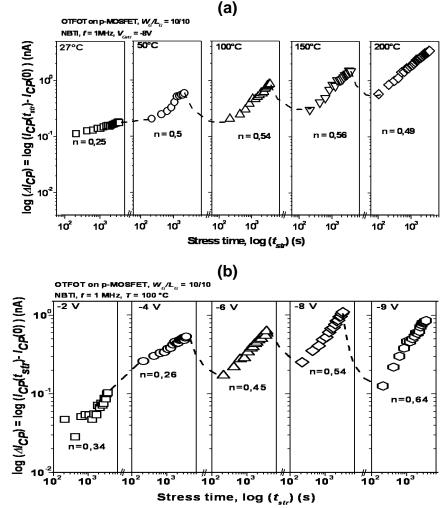

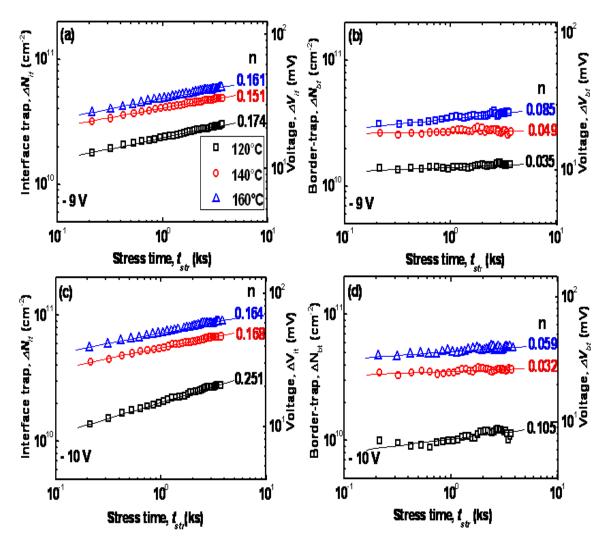

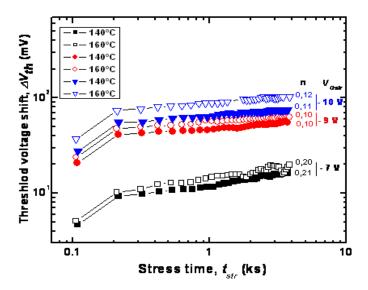

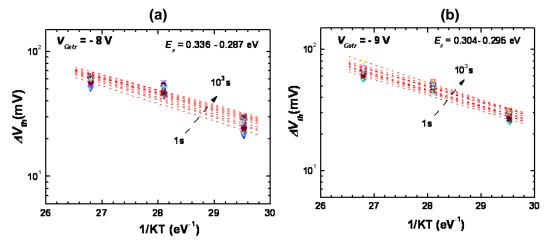

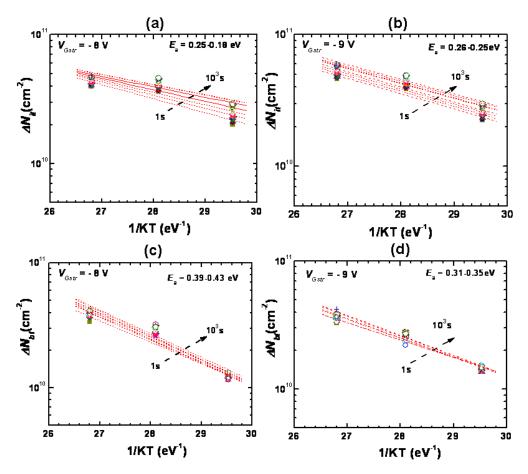

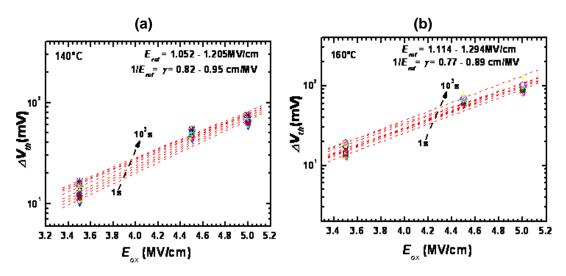

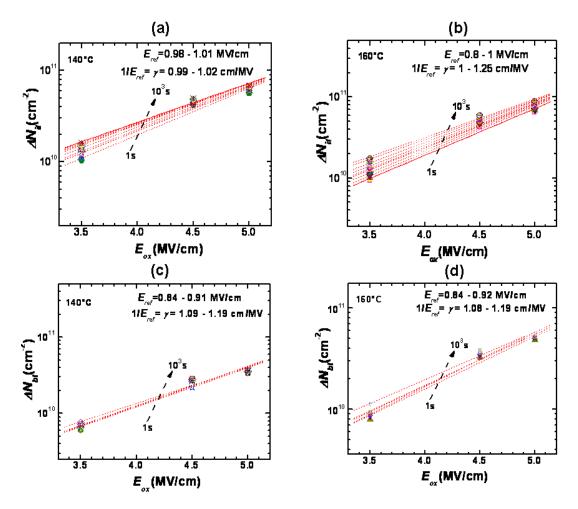

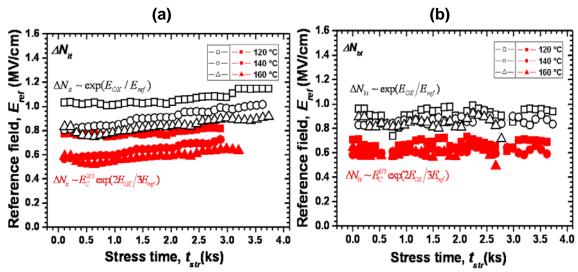

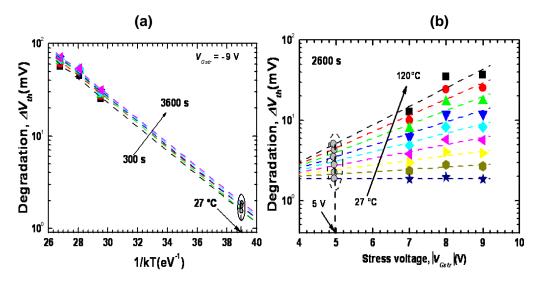

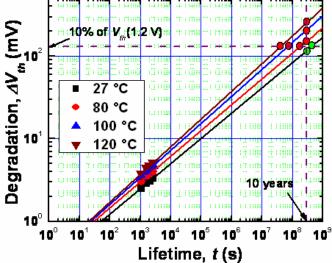

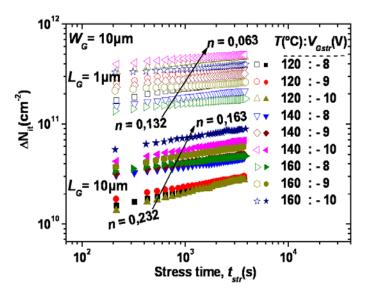

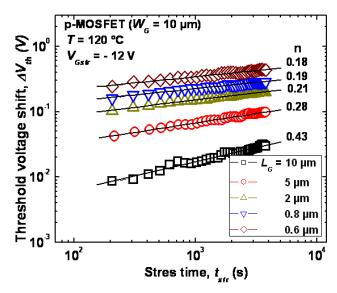

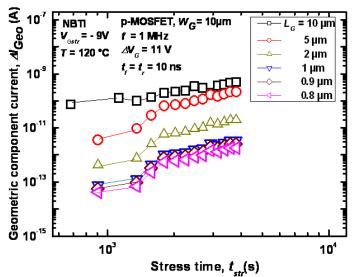

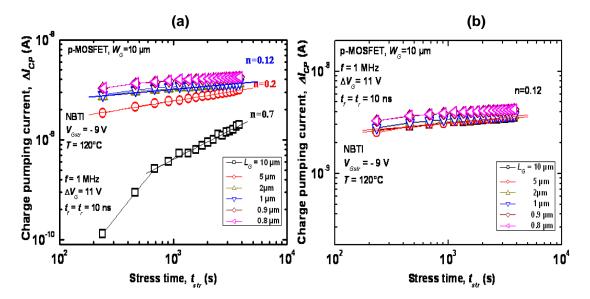

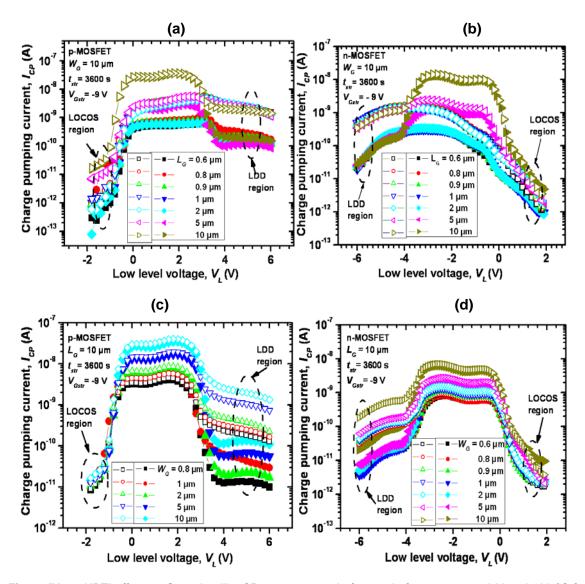

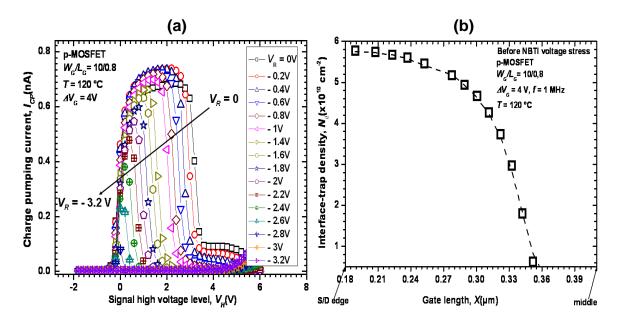

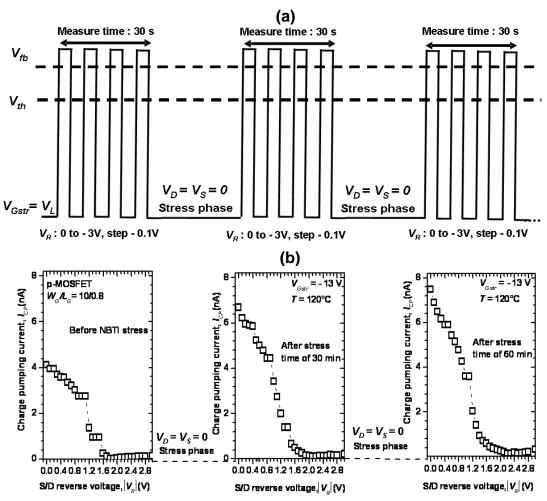

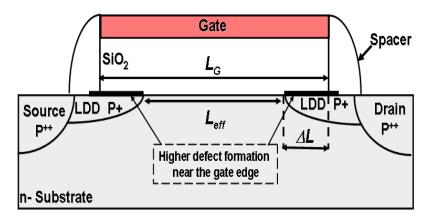

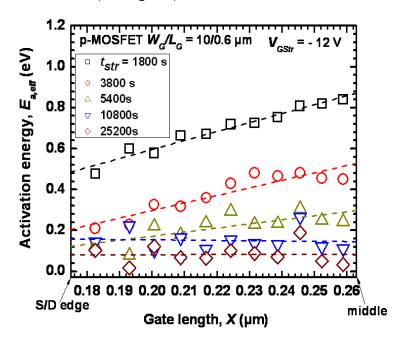

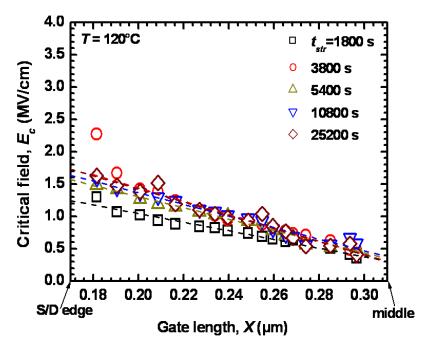

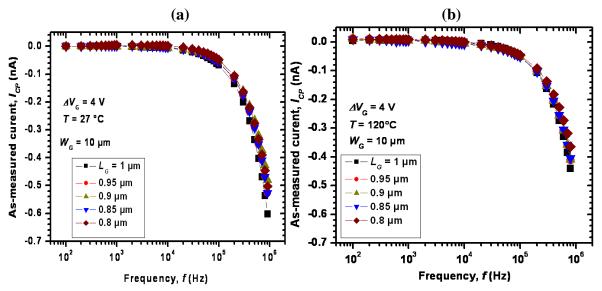

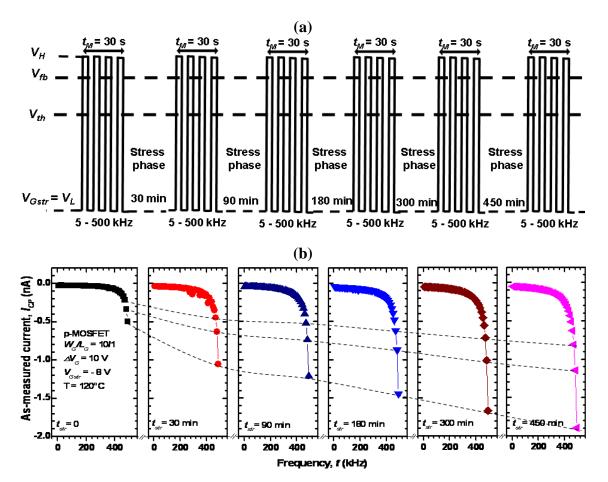

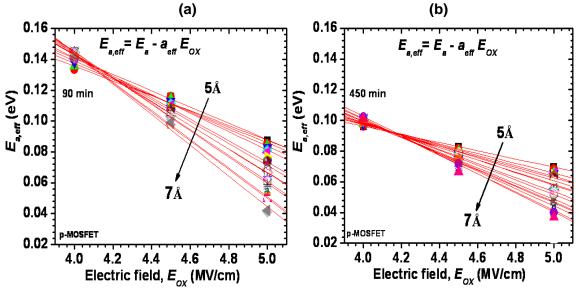

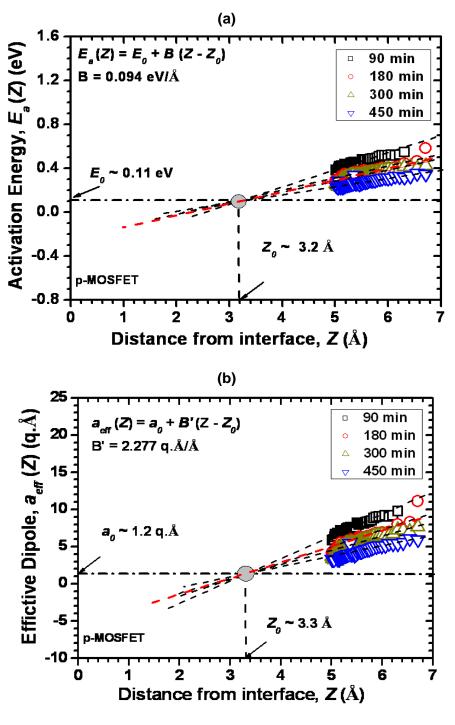

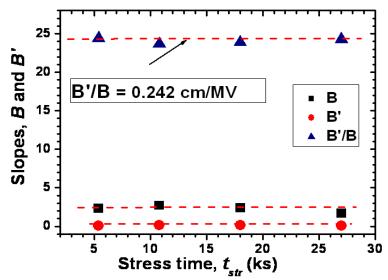

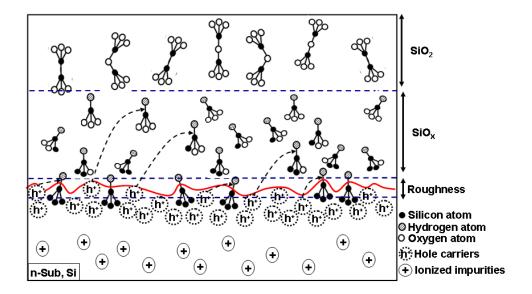

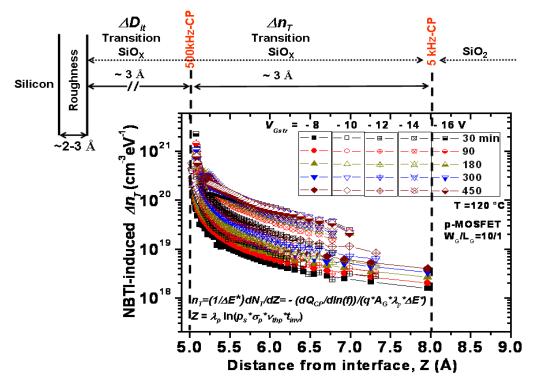

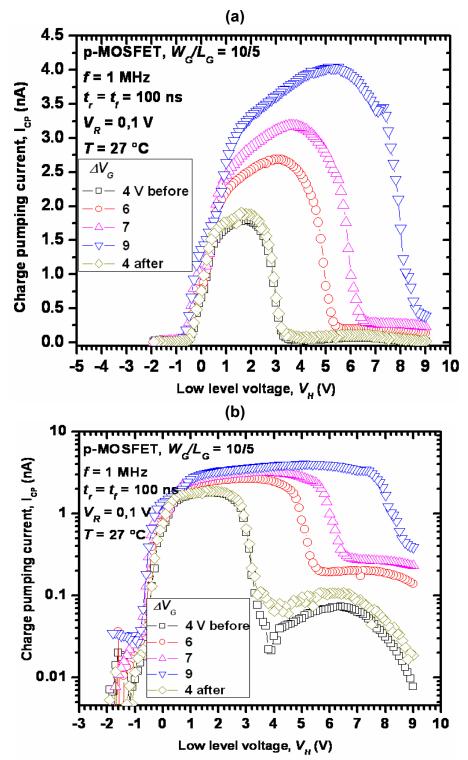

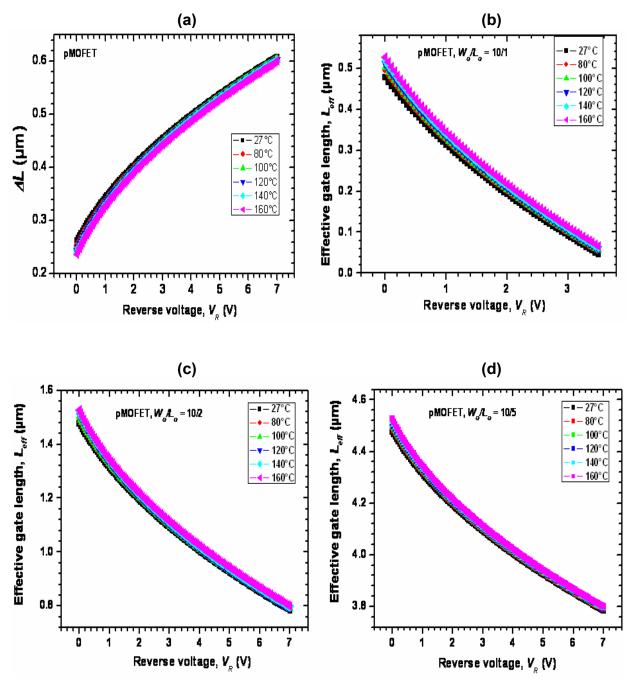

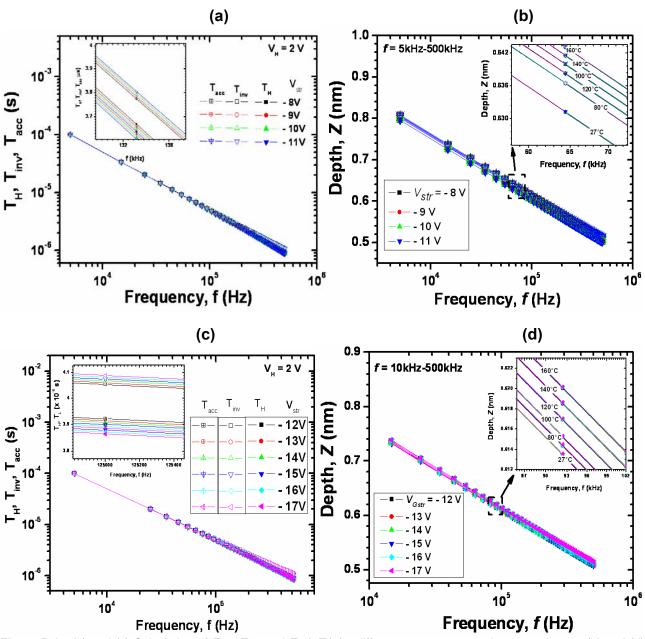

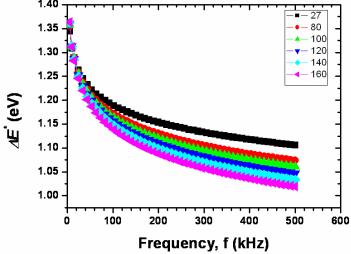

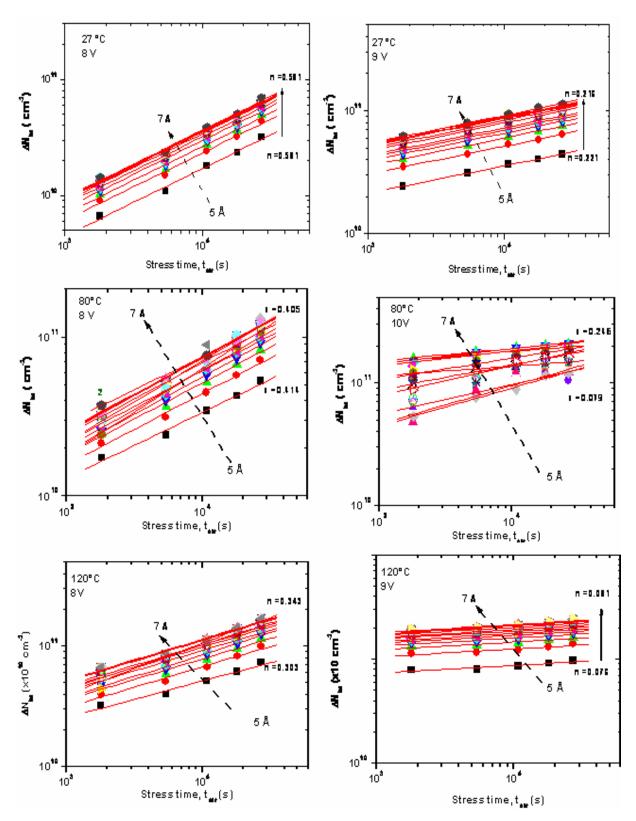

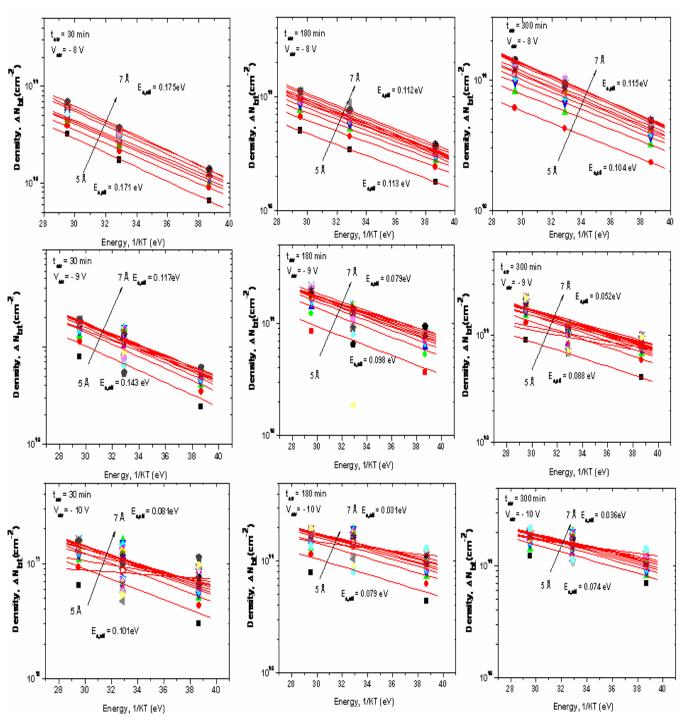

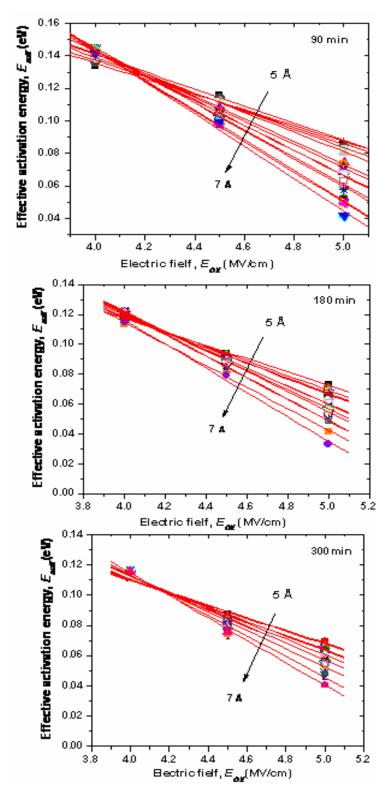

In summary, although many of its different aspects have been recently revealed and discussed. NBTI degradation is still the most controversial topic in reliability community. In fact, several experiments were performed on different technologies using a large variety of sophisticated measurement to properly capture the degradation and to identify its origin. Also, different models have arisen from large amount of data to explain the NBTI features such as the power law exponent, relaxation, the AC behavior, and process effects. All this effort was and is still oriented toward developing know-how as well as know-why to make better predictions for long term reliability and longer useful lifetime of devices under use conditions. In spite of the enormous effort, there is, unfortunately, no consensus regarding the correct physical interpretation of NBTI and theoretical understanding of the degradation phenomena necessary for lifetime projection.