### National Institute of Electricity and Electronics INELEC - BOUMERDES DEPARTMENT OF RESEARCH

Presented in partial fulfilment of the requirements of the

## DEGREE OF MAGISTER

in Applied Electronics

by

Rachid BOUDERBALA

### Charge-Extraction Technique for Studying the Surface-States in MOS Devices

Defended on November 14, 1992 before the jury: President: Dr M. BENZOHRA, Professeur, USTO. Members: Dr V. MITRA, Professeur, INELEC. Dr A. OUADJAOUT, UDTS. Dr K. HARICHE, INELEC. Dr A. ABBABOU, USTHB.

### ACKNOWLEDGEMENTS

I would like to express my most sincere gratitude to my research adviser Dr. Ved Mitra for his untiring and continued interest and supervision throughout the project without which the present work could not be possible. The experience that I have gained under his able guidance is a valuable addition to my academic attainments.

I am especially grateful to Mr. Moufek, Director general of the institute for providing all the necessary research facilities and encouragement throughout this project. I am equally thankful to Dr. K. Harriche, head of research department for providing constant motivation and support. I must express my thankfulness to Dr. H. Bourdoucen for encouragement and useful suggestions from time to time. Thanks go to Mr. Y. Kribes for useful discussions and for providing us commercial devices. I must also acknowledge the cooperation and help by way of mutual discussions that I received from my collegue, A. Benfdila with whom much of this work was done in collaboration. Special thanks go to Dr. A. Amrouche (CDTA), for providing microscope prober and devices used in this work. I am further indebted to H. Bentarzi whose presence as my collegue in the research group has been a source of inspiration and useful discussions. In addition, I would like to thank all the staff members who provided all support needed to achieve this work. Finally, all this would have been impossible without the patience and continuous encouragements of my family.

### PREFACE

The advancement in the fabrication technology of integration circuits and accordingly the reduction of feature size to micron and sub-micron range in VLSI using MOS technology has given rise to a new problem of hot electrons induced degradation of the device characteristics. Therefore the most current researches are directed towards the study of hot electrons and hot electrons induced effects in small channel MOS devices. An important aspect in such studies is the occurrence of traps at the Si-SiO2 interface. Although a number of methods are now available to study the density and density distribution of these surface traps, but so far none of the methods is privileged to be called a universal method in the sense that it can be applied to all the MOS structures without any constraint. For example capacitance and conductance methods can be used in large area MOS capacitors. The charge pumping method can be used only in such MOSFET which satisfy certain geometrical condition according to which channel width to channel length ratio is quite larger than unity. Development of such a method, which could be equally applicable to MOS capacitors as well as to

MOSFETs without any geometric constraint, is yet to come out and in fact this was the motivation before our research adviser Dr. V. Mitra while assigning the present research project to us.

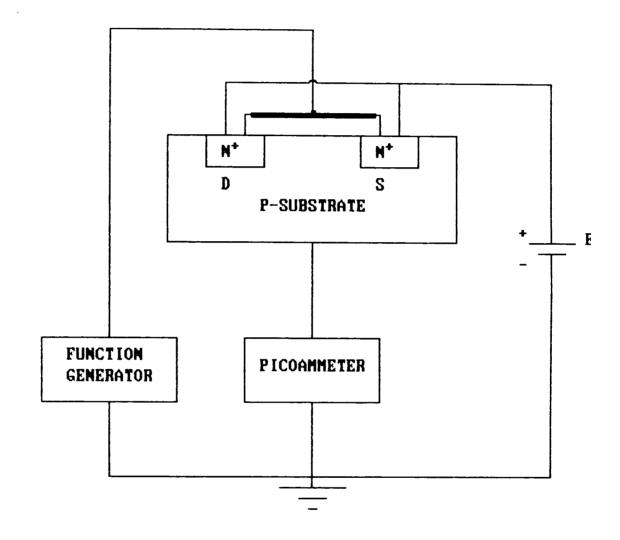

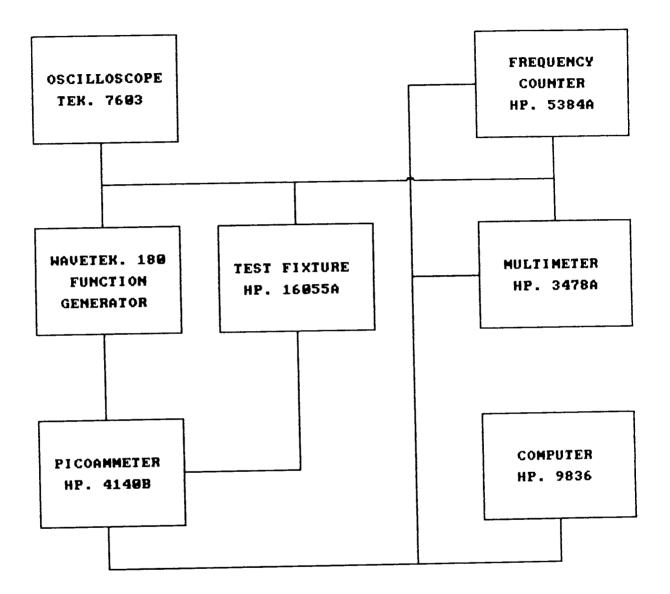

Obviously such a research project would be quite befitting to the need of the current technological and scientific development. However one more consideration, which had to be borne in mind and which laid a constraint on our research project, was the equipment facility available to us. The semiconductor research laboratory of INELEC, which was in use for the characterization of electronic devices before our admission, had two capital equipments of research standard, namely, a picoammeter (HP 4140B) and an HP 9836 computer besides some of other subsidiary measuring meters. All the above considerations and constraints then left before us almost a unique choice for our research project, that is, the study of surface states in MOS devices using charge pumping technique which requires mainly measurement of substrate current with precision.

However, the complete project had still many hurdles before it could be undertaken. Besides the need of a number of additional subsidiary measuring instruments and accessories having H.P. compatibility which were to be collected from various resources both inside and outside this institute, the main hurdle was how to procure MOS devices of known parameters. It was in fact a great challenge before us particularly in the period during which the sole fabrication

• . .

laboratory of this country, located at ENIE, SIDI-BELABBES, kept its fabrication work suspended due to certain reasons. We had no other option except to accept the challenge and struggle in search of a suitable source for the required devices outside our country.

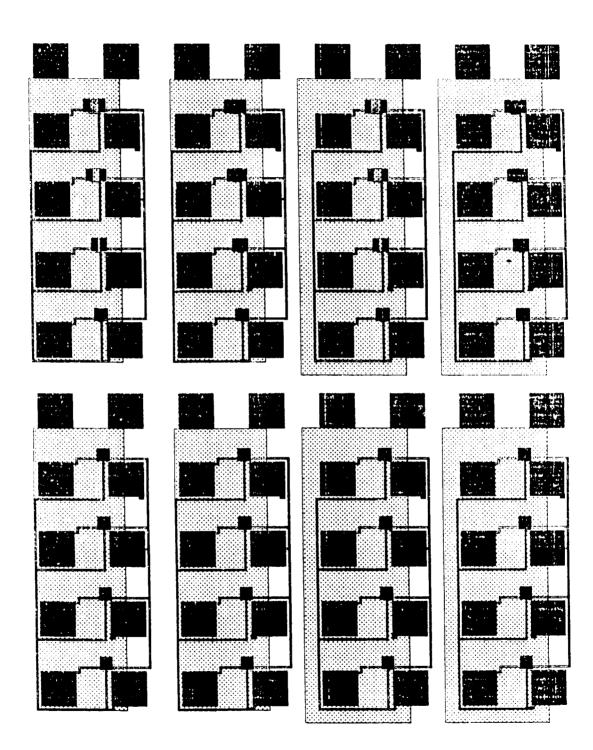

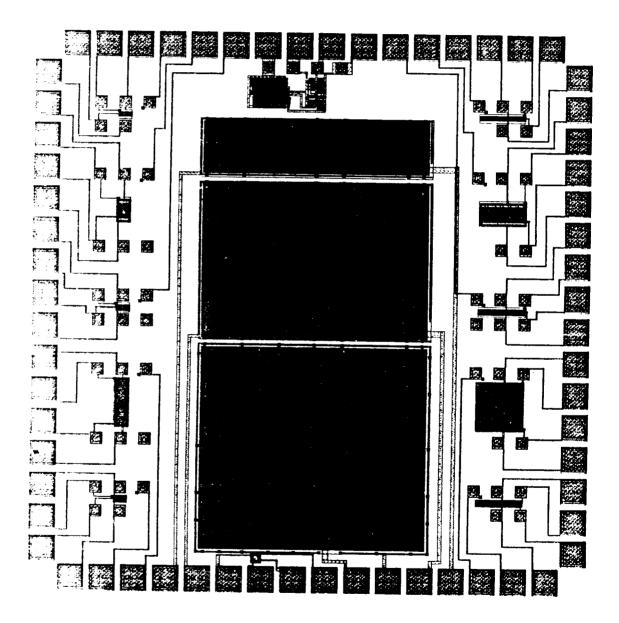

After a long struggle we came in contact with certain researchers of Centre de Developement des Technologies Avancees (CDTA) Alger. This centre is engaged in the IC design by way of undertaking different design projects. The ICs so designed are then got fabricated by them in European Silicon Structures (ES2) France which is internationally reputed for IC fabrication. We utilized this opportunity and requested the concerned CDTA personnels to undertake a design project as per requirements of MOS devices needed by us. At last we succeeded in the procurement of MOS devices of our research requirements but not before initial six months of our research period. Some of these devices were in the chip form and needed a special microscope prober for their use which was also lent to us by CDTA. However we were not sure of eliminating all the external influences on the device during experimentation with this microscope prober inspite of covering it within a Faraday box designed and fabricated by ourselves in the metal shop of INELEC. Therefore we got a number of devices encapsulated by ES2 so that they could be safely used within the test fixture (HP 16055A) supplied by H.P. along with the picoammeter.

During the same period of our initial struggle we could

arrange other subsidiary H.P. compatible instruments and accessories enabling us to use the picoammeter, after necessary interfacing with the H.P. computer and other instruments, in its automated mode to yields necessary data for the implementation of charge pumping technique and the alternative technique which was eventually developed during the course of our research investigations.

In fact when we now look back on our initial struggle and extra efforts for arranging the equipment and devices for our research, we do not regret spending this period of six months on this part of our research project. We rather feel fully contented with our this additional training and experience that we have received from our research adviser and that has given us extra confidence for undertaking any large scale sophisticated research project. It is really a matter of great contentment and satisfaction for us to see that all work done and results obtained by us have made use of equipment and devices which satisfy full research sanctity and standard. We will feel furthermore contented if our efforts and labour could prove fruitful in achieving even a part of the expectations and motivation of our research adviser with which he assigned this research project to us.

On July, 22th 1992. R. BOUDERBALA

### TABLE OF CONTENTS

| CHAPTER | 1 | : INTRODUCTION1                                 |

|---------|---|-------------------------------------------------|

| CHAPTER | 2 | : MOS STRUCTURE                                 |

|         |   | 2.1 Mos Structure: Qualitative Description8     |

|         |   | 2.2 Ideal Mos Structure                         |

|         |   | 2.3 Different Biasings of Ideal Mos Structure10 |

|         |   | 2.4 C-V Characteristics of a Mos Capacitor13    |

|         |   | <b>2.5</b> Real Mos Structure                   |

| CHAPTER | 3 | : OXIDE AND INTERFACE PROPERTIES                |

|         |   | 3.1 Silicon Dioxide in Mos Devices              |

|         |   | 3.2 The Nature of Interface Trap and            |

|         |   | Oxide Charge                                    |

|         |   | 3.2.1 Interface Trapped Charges                 |

|         |   | <b>3.2.2</b> Oxide Charge                       |

|         |   | 3.3 Influence of the Interface Trap charges     |

|         |   | on the Electrical Characteristics               |

|         |   | of Mos Devices                                  |

|         |   | <b>3.3.1</b> Degradation                        |

|         |   | 3.3.2 Effect of Interface Traps on              |

|         |   | Electrical Characteristics                      |

|         |   | 3.3.3 Effect of Interface Traps on              |

|         |   | C-V Curves                                      |

• •

|           | 3.4 Control of Interface Trap Density            |

|-----------|--------------------------------------------------|

| CHAPTER 4 | : MEASUREMENT TECHNIQUES OF INTERFACE            |

|           | TRAPPED CHARGES43                                |

|           | <b>4.1</b> Introduction                          |

|           | 4.2 Interface Traps Density Extraction Methods44 |

|           | <b>4.2.1</b> Determination of VFB48              |

|           | 4.2.2 Accuracy and Limits of Interface Trap      |

|           | Density Extraction by C-V Methods51              |

|           | <b>4.3</b> Conductance Method                    |

|           | <b>4.3.1</b> General Principle55                 |

|           | 4.4 Deep-Level Transient Spectroscopy60          |

|           | <b>4.5</b> Other Methods                         |

| CHAPTER 5 | : CHARGE PUMPING TECHNIQUE                       |

|           | <b>5.1</b> Introduction                          |

|           | <b>5.2</b> Basic Principle                       |

|           | 5.3 Methods of Measurements                      |

|           | 5.4 Groeseneken et al Model                      |

|           | 5.5 Limitations                                  |

|           | 5.6 Other Developments in Charge Pumping         |

|           | Technique                                        |

| CHAPTER 6 | : MEASUREMENTS AND EXPERIMENTAL RESULTS112       |

|           | <b>6.1</b> Introduction                          |

|           | 6.2 Measuring Equipment                          |

|           | 6.3 Experimental Devices                         |

|           | 6.4 Charge Pumping Experiments                   |

|           | <b>6.4.1</b> Experimental Set-Up                 |

|           | 6.4.2 Results and Discussion                     |

. . .

|                   | <b>6.4.3</b> Conclusion145                  |  |

|-------------------|---------------------------------------------|--|

|                   | 6.5 An Alternative Experimental Approach145 |  |

| CHAPTER 7         | : CHARGE EXTRACTION TECHNIQUE FOR STUDYING  |  |

|                   | THE INTERFACE TRAPS IN MOS DEVICES          |  |

|                   | 7.1 Introduction                            |  |

|                   | 7.2 Theoretical Model                       |  |

|                   | 7.3 Experimental Measurements               |  |

|                   | 7.4 Results and Discussion                  |  |

|                   | 7.5 Conclusion                              |  |

| CHAPTER 8         | : CONCLUSION                                |  |

|                   |                                             |  |

| <b>REFERENCES</b> |                                             |  |

CHAPTER 1

### INTRODUCTION

Surfaces of solids and interfaces between materials play an important role in a wide variety of phenomena. Because of the scientific importance and the economic impact of these phenomena, considerable efforts have been devoted to their study.

In 1935, Liandrat [1] proposed that the conductivity of a thin semiconductor layer could be modulated by an external field. The use of this field effect experiment provided a useful tool for the examination of some of the fundamental properties of semiconductor properties. The existence of a quantum states on a free semiconductor surface was demonstrated by Shockley and Pearson [2] in 1948 by a field effect experiment. The results of their experiment clearly demonstrated the importance of surface traps in determining

-1-

the degree of modulation that could be obtained in a surface field controlled device. Frosh and Derrick [3] found in 1957 that silicon dioxide acts as an effective barrier against commonly used impurities, thus preventing them from reaching the underlying silicon. This discovery is important because it forms the basis of present-day integrated circuit technology. Therefore, free surfaces are no more used, they have been replaced in 1960 by the solid-solid interface between the semiconductor and the grown oxide film of known composition and structure. This process is termed as oxide passivation. However the oxide layer so developed on the silicon surface is not free from different kinds of charge. The presence of these charges in the oxide alter the characteristics of the device developed underneath the protecting oxide layer by planar technology. In order to study the effect of the surface charge, it became important to know the structure of the surface, covering the devices fabricated by planar technology. The complete surface-structure is such in which a metal film is deposited over a SiO<sub>2</sub> layer protecting the silicon This metal-oxidesubstrate. semiconductor briefly knwon as MOS structure is important in the study of various effects. Such studies eventually gave rise to the following three important devices which involve MOS structure.

-2-

1.Metal-oxide-semiconductor diode (MOS diode).

2.Metal-oxide-semiconductor field effect transistor (MOSFET).

3.Gate controlled P-N junction.

A detailed account of MOS structure will be presented in chapter 2.

Various types of charges, located in the silicon oxide layer and at the silicon-oxide interface have been found to cause instabilities and adversely affect the electrical characteristics of the devices. Their impact on the device performance and lifetime is becoming more pronounced as the device geometry is being reduced especially in short-channel MOSFET, while the power supply is not changed. In general, the origin of these charges has usually been linked with a disruption of the periodicity of the silicon lattice near the Si-SiO<sub>2</sub> interface. The level of these charges varies with different processing conditions depending on the oxidation rate, the crystal orientation, and oxide preparation. These charges within the MOS structure have been a subject of many investigations. The positive fixed charge, high electron trap density and large interface trap density act to decrease the carrier mobilities at the Si-SiO2 interface by coulombic scattering. Reduced surface carrier mobilities are directly reflected in reduced MOS transistor transconductance [4]. The electron traps and interface traps are

-3-

also responsible for increased flicker noise measured in MOS transistors [5]. Subsequent techniques in controlling their density and their distribution in the energy band-gap have made possible the current widespread use of MOS devices in integrated circuit technology. Device characteristics affected by such charges include: threshold voltage, effective mobilities, current gain, junction leakage, frequency noise, and drain junction breakdown voltage all of which may affect the device performance and stability to some degree [4]. Such an influence is observed as a distortion and shift in the shape of the C-V curve. Most of the reliable results which have been obtained so far in thermally oxidized silicon, show that the doping type and concentration have a little effect on the variation of the density of the interface traps. However, a strong dependence on silicon orientation has been observed affecting the value of the trap density significantly in increasing order.

The understanding and characterization of Si-SiO<sub>2</sub> interface traps and their effect on MOS device performance is important in the present semiconductor technology. Thus, extensive research has been carried out on the nature, effect and the measurement of the interface trap properties. Various methods have been developed to determine the interface trap distribution. Of particular importance are the

-4-

conventional measurement techniques [6,7,8,9], the temperature method [10] and the DLTS technique [11]. However, some of these methods are unsatisfactory from the viewpoints of the sensitivity and/or the spectroscopic determination of the interface properties. Recently, a new method called charge pumping technique has been developed for studying the interface properties [12]. This technique [12] utilizes the dc substrate-current which is supposed to arise from charging and discharging of the interface traps at the Si-SiO2 interface and appears to be quite promising for the extraction of the interface-trap density. However, the charge pumping technique is thought to suffer with certain limitations [13,14,15].

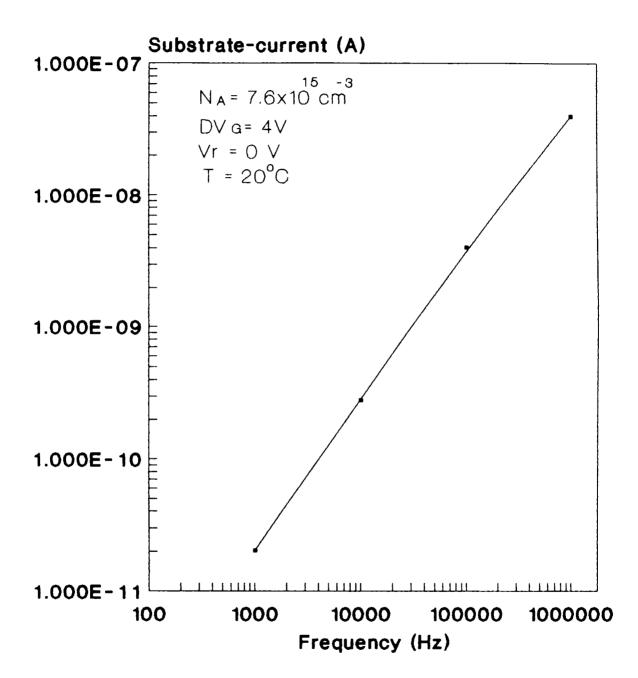

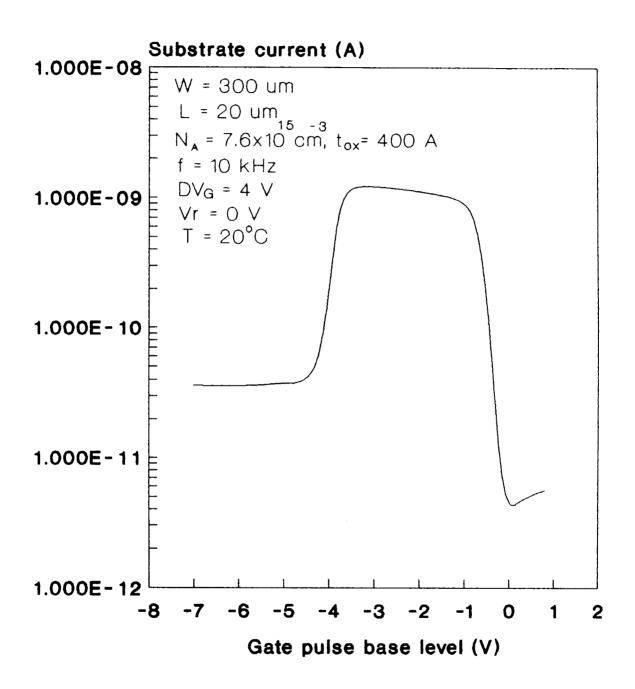

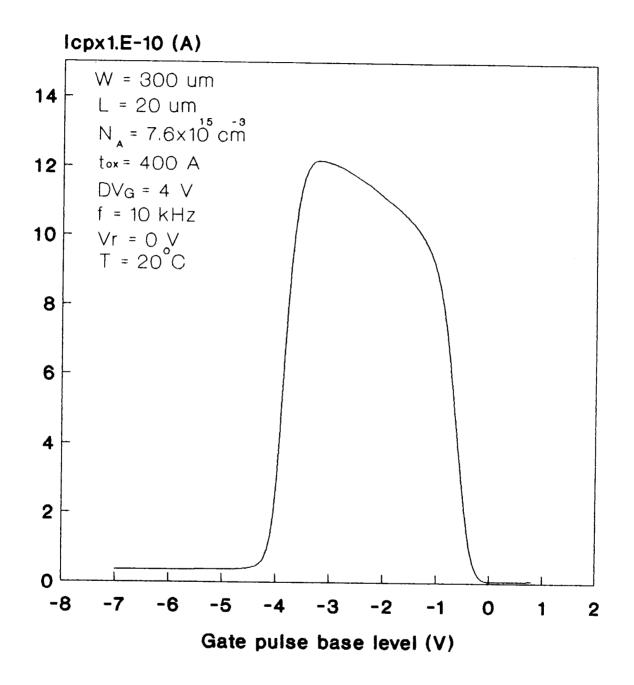

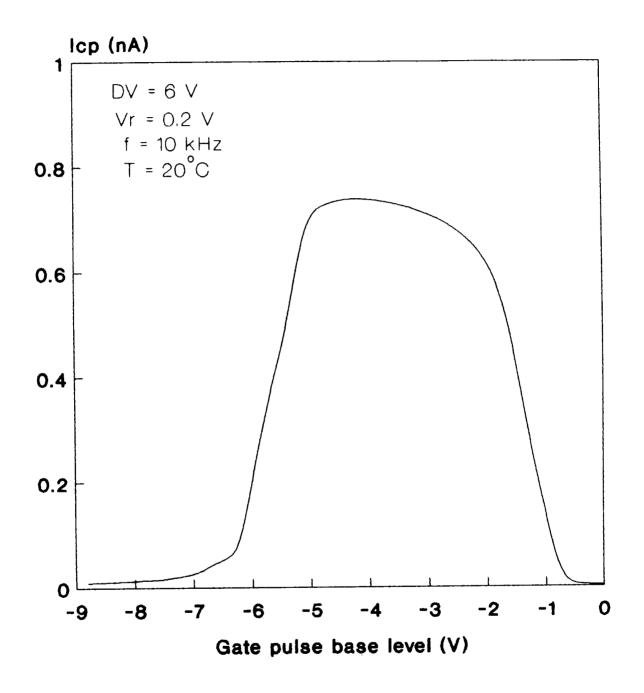

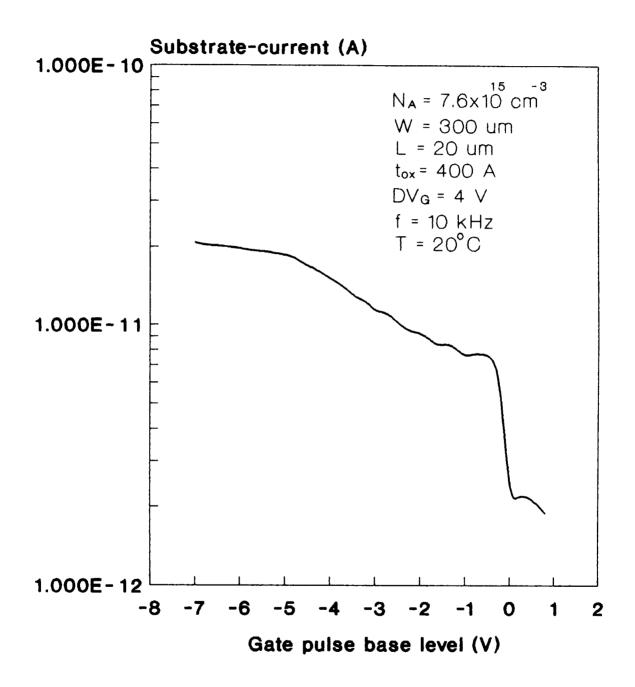

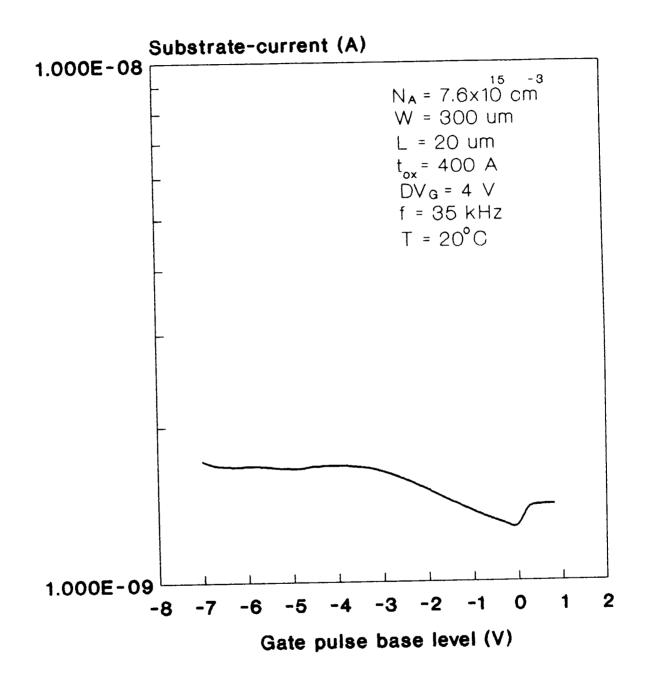

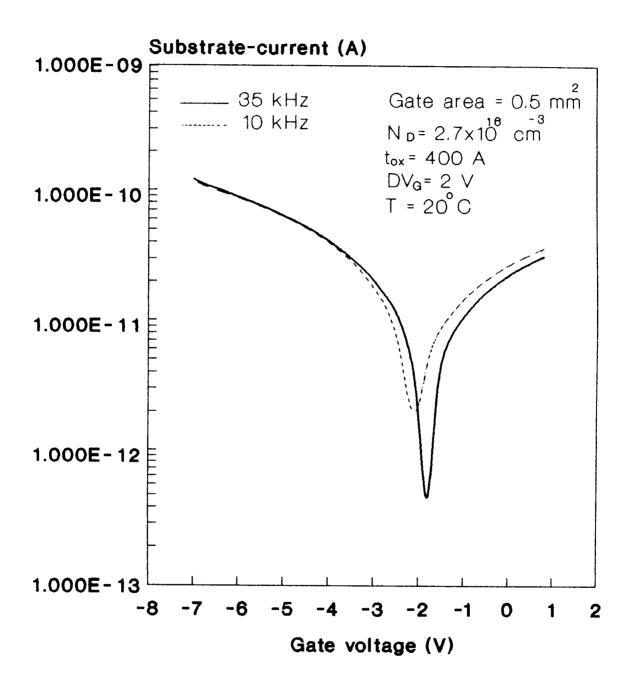

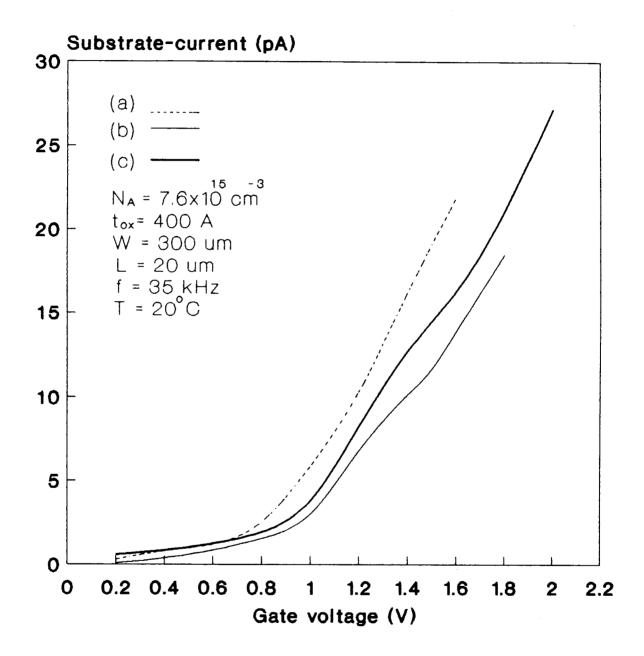

During the course of experimentation with the charge pumping technique, we observed a significant amount of substrate-current when the surface-region of the device is under the depletion regime. This substrate-current distinguishes itself from the oxide leakage-current arising from any of the commonly known processes [16]. There is a strong evidence that the resulting current is due to the non-steady state emission regime of carriers. These results led to the development of an alternative approach to the charge pumping technique for studying the interface traps in a MOSFET which is free from certain limitations. This new approach , which may be better called charge-extraction technique, can be

-5-

equally applied to MOS diodes without imposing any constraint on the device geometry.

The present thesis is devoted to give a comprehensive account of the charge pumping technique, scope and exploration of an alternative approach and accomplishment and development of a new technique called charge extraction technique for studying the interface properties of MOS devices. The whole thesis is presented in the form of 8 chapters. After introducing the subject in the present chapter, chapter 2 is devoted to the background study of the MOS structure itself covering all its essential features, characteristics and aspects which are relevant in the further development of the subject. In chapter 3, the properties of the Si-SiO2 and, in particular, all those factors which contribute to the non-ideality of MOS structure are examined and their effect on the electrical characteristics are discussed. We end this chapter by examining briefly the impact that the fabrication technology may have on the generation and/ or on the reduction of these electrically active defects. Chapter 4 is centred around the capacitance methods. All those techniques, which are common in use such as the differentiation method [7], the integration method [17], the conductance method [9], and the DLTS technique [11], are presented in details whereas the others, which are more or less of historical interest only, are presented

-6-

briefly. Chapter 5 introduces the basic concepts needed to identify, understand, and analyse the phenomenon of charge pumping technique which is followed by a mathematical analysis and a few limitations of the technique. A brief account of the other developments on charge pumping technique is also presented. Chapter 6 covers the required instrumentation for the implementation and use of the charge pumping technique along with the details concerning the actual devices and the measuring set-up. The experimental results of the charge pumping technique are presented and discussed. Finally, the results obtained by the new technique are discussed and compared to those found by the charge pumping technique [12]. In Chapter 7, a theory of the new technique, called charge-extraction technique for studying the interface traps in MOS devices, is presented. Finally chapter 8 concludes with a discussion on the usefulness and future scope of the work presented in this thesis.

### MOS STRUCTURE

#### 2.1 MOS STRUCTURE: Qualitative Description

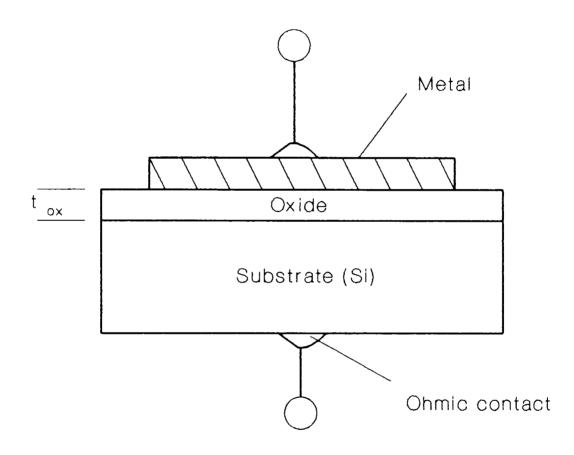

The MOS structure which is a particular form of the MIS structure, is one of the simplest heterostructure. It consists of an oxide layer usually thermally grown on a silicon substrate, an electrode called a gate made by vacuum deposition of a metal or by the deposition of polysilicon and an ohmic contact to the silicon substrate. Such a structure is shown on Fig. 2.1. The electrical properties of this structure will be discussed in relation with the application of the biasing voltage.

#### 2.2 IDBAL MOS STRUCTURE

The ideal MOS structure is generally defined by the absence of any contact potential or work function difference between metal and semiconductor, and the absence of any

-8-

Fig. 2.1. Cross section of an MOS capacitor.

charge within the oxide or at the oxide-semiconductor interface.

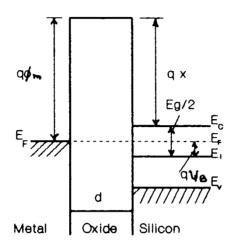

At zero applied bias the bands are flat (Figure 2.2) and we have for both types of substrate (p- or n-type) the following condition:

$$\phi_{ms} = \phi_m - \left(\chi + \frac{E_g}{2q} \neq \psi_B\right) = 0 \qquad (2.1)$$

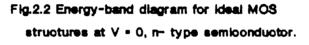

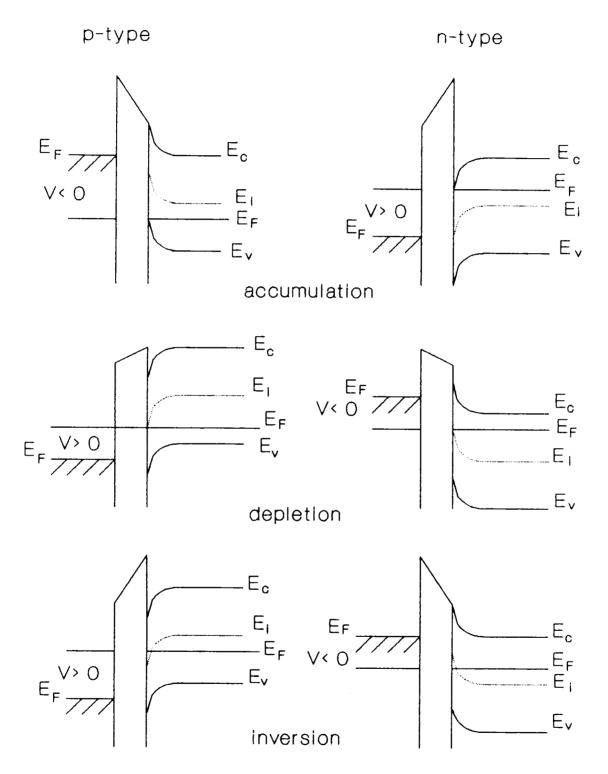

(the minus (-) and positive (+) signs inside the second term on the right hand side of the above equation stand for n-type and p-type respectively ) where  $\phi_m$  is the total work function;  $\chi$  the semiconductor electron affinity; Ec the energy of the lower edge of the conduction band; Ev the energy of the upper edge of the valence band; Eg the band gap; q the electronic charge; and  $\psi_a$  the potential difference between the Fermi level and the intrinsic Fermi level E1. Figure 2.2 illustrates the energy-band diagram of an ideal MOS structure. An applied voltage at the gate plate causes the bands to be bent downward or upward depending on the sign of this gate voltage. Figure 2.3 shows the energyband diagram at the surface of a p-type semiconductor under the action of positive gate voltage producing a surface potential  $\psi_{\bullet}$ .

#### 2.3 DIFFERENT BIASINGS OF IDEAL MOS STRUCTURE

There are three regimes of interest when the MOS

-10-

#### Fig.2.3 Energy-band diagram at the surface of of a p-type semiconductor.

capacitor is under biasing.

In the accumulation regime, the MOS capacitor is biased in such a way that the majority carriers are attracted towards the gate. For a p-type silicon, when a negative bias on the gate is applied, the negatives charges on the gate attract holes to the silicon surface to form an accumulation layer. The thickness of such layer depends on the bias and doping density, and is comparable to Debye length. Because of the increase in the concentration of holes, the Fermi level near the silicon surface will move to a position closer to the valence band edge.

When the gate bias is made positive with respect to flat-bands, holes are repelled from the silicon surface. As this process continues, the positive gate charges are balanced not by electrons, but by negative acceptor ions in the silicon surface depletion layer, so called because holes have been depleted from this surface region. As gate bias increases, the depletion layer widens to provide more acceptors ions to balance the gate charge. The Fermi level near the silicon surface will move to a position closer to the center of the forbidden region: This describes the depletion regime.

Finally, with increasingly positive applied voltage, the surface depletion region will continue to widen until electrons appear at the silicon surface in great numbers. The appearance of these electrons is a consequence of thermal

-12-

equilibrium. As holes are repelled from the silicon surface by the applied gate bias, electron density must increase and then form a thin inversion layer located very near the Si-SiO<sub>2</sub> interface depending on bias and doping density. Once inversion occurs, any further increase in positive gate charge is balanced almost entirely by the addition of electrons to the inversion layer, and the depletion layer no longer increases further in width. The Fermi level near the silicon surface will now lie closer to the conduction band edge. This describes the inversion regime. Figure 2.4 shows the energy-band diagram and the corresponding regimes for both n-type and p-type semiconductors.

#### 2.4 C-V CHARACTERISTICS OF A MOS CAPACITOR

An MOS capacitor consists of a parallel plate capacitor with one electrode a metallic plate, called the gate and the other electrode, the silicon. The two electrodes are separated by a thin layer of SiO<sub>2</sub>.

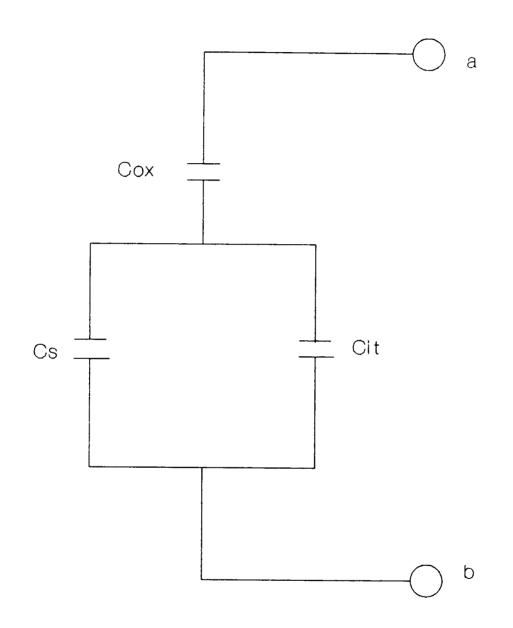

The MOS capacitor can be electrically modeled as an oxide, semiconductor, and interface state capacitance as shown in Fig. 2.5.

In the absence of any work-function difference, the applied gate voltage VG will appear partly across the insulator and partly across the silicon. Thus,

$$V_{g} = V_{ox} + \psi_{s} \tag{2.2}$$

# Fig. 2.4. Energy-band diagram for ideal MOS structure when V = 0 for both n-type and p-type semiconductors (after[16]).

Fig. 2.5 Electrical model of MOS capacitor.

where  $V_{ox}$ , the potential difference across the insulator, is given by

$$V_{ox} = \frac{Q_s}{C_{ox}} \quad , \tag{2.3}$$

where  $Q_{B}$  is the surface charge and  $C_{ox}$  the oxide-capacitance.

For a given insulator thickness  $t_{ox}$ , the value of the oxide capacitance  $C_{ox}$  is a constant given by

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} , \qquad (2.4)$$

where  $\epsilon_{ox}$  is the dielectric constant. For a uniformly doped n-type substrate (Na),  $Q_{\Xi}$  can be found by solving Poisson's equation in a semiconductor and is given by [16]:

$$Q_{s} = \pm \sqrt{2q\epsilon_{si}\frac{kT}{q}} \{ N_{d} \{ \exp\left(\frac{-q\psi_{s}}{kT}\right) + \frac{q\psi_{s}}{kT} - 1 \} + \frac{n_{i}^{2}}{N_{d}} \left\{ \exp\left(\frac{q\psi_{s}}{kT}\right) - \frac{q\psi_{s}}{kT} - 1 \right\} \}^{\frac{1}{2}} , \qquad (2.5)$$

where  $\epsilon_{st}$  is the dielectric constant of silicon, n1 the intrinsic carrier density of silicon, and kT/q the thermal voltage. The total capacitance C per unit area of the system

is given by

$$C = \frac{C_{ox}C_s}{C_{ox} + C_s}$$

(2.6)

where  $C_{\bullet}$  the semiconductor capacitance, appearing in series to  $C_{ox}$ , is non-linear and much more difficult to be evaluated. This capacitance is a function of the total semiconductor space-charge  $Q_{\bullet}$  and  $\psi_{\bullet}$  and is given by

$$C_s = \partial \frac{Q_s}{\partial \psi_s} \tag{2.7}$$

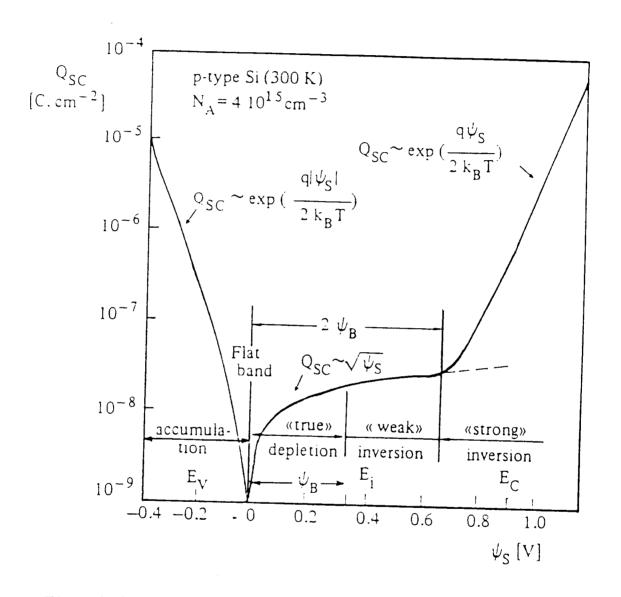

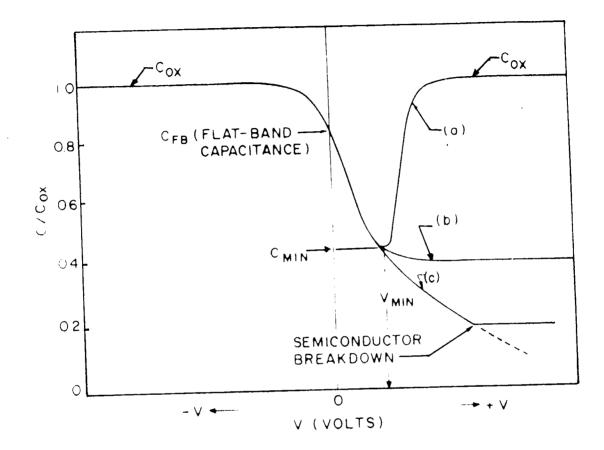

Figure 2.6 shows the variation of the space-charge density  $Q_{\bullet}$  as function of the surface-potential  $\psi_{\bullet}$ . Combination of Eqs. (2.2), (2.3), (2.6), and (2.7) gives the complete description of the MOS device, and can be used to calculate low frequency C-V curves. Figure 2.7 shows a low frequency C-V curve calculated this way. The various regions, accumulation, depletion, weak inversion, and strong inversion and the surface band bending associated with each are shown. The low and high frequency C-V curves are practically identical in accumulation, depletion, and most of weak inversion because in these regions, minority carrier concentration in the depletion layer is negligibly small as compared to majority carrier concentration. The major difference between low and high frequency C-V curves occurs in weak to strong

Fig.2.6 Space-charge density Qs in the semiconductor as a function of surface potential Us for p-type silicon, (After [16]).

Fig.2.7 Normalized high and low frequency capacitance as a function of gate bias for an ideal p-type MOS strucure (After [16]).

inversion where minority carrier concentration in the depletion layer becomes comparable to and exceeds majority carrier concentration. Minority carrier effect cannot be neglected in these regions.

For  $(\psi_{\bullet} = 0)$ , we have the flat-band condition, and  $Q_{\bullet}$  is zero. In the case of an n-type substrate, the accumulation charge is negative when  $\psi_{\bullet} < 0$  and is given by

$$Q_{acc} \approx -Q_s \quad . \tag{2.8}$$

For  $\psi_{\bullet}>0,$  the semiconductor charge is positive and can be written as

$$Q_D + Q_{inv} \approx + Q_s \quad , \tag{2.9}$$

where QD is the depletion charge, and Qinv is the inversion charge. In the depletion approximation  $(\psi_s > \frac{3kT}{q})$ , the depletion charge, QD can be written as

$$Q_D \approx \sqrt{2q\epsilon_{si}N_d\psi_s} \quad . \tag{2.10}$$

and the C-V characteristic of the MOS capacitor takes the following form:

$$\frac{C}{C_{ox}} = \left(1 + \frac{2\epsilon_{ox}^2 \epsilon_o V_G}{q N_D \epsilon_{si} t_{ox}^2}\right)^{-\frac{1}{2}}, \qquad (2.11)$$

which is valid only for the depletion or weak inversion at the semiconductor surface.

For  $\frac{3kT}{q} < \psi_s < \phi_B$ , the inversion charge is negligible compared to the depletion charge. However, in the weak inversion, where  $\phi_B < \psi_s < 2\phi_B$ , the inversion charge increases rapidly, and  $Q_{uuv} \approx Q_D$  at the onset of strong inversion where  $\psi_s = 2\phi_B$ . In the strong inversion where  $\psi_s > 2\phi_B$ , the surface-potential remains essentially constant since  $Q_{inv}$  increases exponentially with  $\psi_s$ , and is given by

$$Q_{inv} \approx \sqrt{2q\epsilon_{si}\frac{kT}{q}\cdot\frac{n_i^2}{N_d}\exp\left(\frac{q\psi_s}{kT}\right)} \qquad (2.12)$$

Since the surface-potential is essentially pinned at  $\sim 2\phi_{g}$  in strong inversion, the depletion charge is also fixed, and is given by

$$Q_D \approx \sqrt{2q\epsilon_{si}N_d(2\phi_B)} \qquad (2.13)$$

In the presence of interface charges at the Si-SO<sub>2</sub> interface of the MOS capacitor, charge neutrality requires:

$$Q_{g} + Q_{s} + Q_{u} = 0$$

, (2.14)

where  $Q_{\Theta}$  and  $Q_{\bullet}$  represent charges at the gate and in the semiconductor, respectively. Hence the capacitance is not the same but contains an additional interface trap capacitance, Cit. The interface trap capacitance, Cit is a function of the energy density of interface traps (Dit), measurement frequency ( $\omega$ ), and surface-potential ( $\psi_{\bullet}$ ).

The semiconductor and interface trap capacitances are functions of  $\psi_{\bullet}$ . In addition, the interface traps and minority carriers in the inversion charge are controlled by frequency dependent Shockley Hall Read (SHR) generation-recombination processes. To prevent deep depletion of the substrate, all C-V measurements were started from the condition of strong inversion and swept to accumulation. At high frequency (say 100kHz), SHR generation-recombination processes are too slow to control the interface traps or inversion charge, and the contribution of Dit and Qinv are negligible. Because the charges follow the slowly changing gate bias and mirrors some of the applied electric field, the effect of Vo on band bending is reduced. A larger swing is required to achieve the same band bending. Therefore, the capacitance measured at high frequency, CHF, is simply given by

$$C_{HF} = \left[\frac{1}{C_{ox}} + \frac{1}{C_{s}(\omega)}\right]^{-1} , \qquad (2.15)$$

where  $C_{s}(\omega)$  is the effective semiconductor capacitance at

high frequency and is approximated by the capacitance due only to the accumulation charge for  $\psi_{,}>0$ , and is given by

$$C_s(\omega)_{HF} \cong \frac{\partial Q_{acc}}{\partial \psi_s}$$

, (2.16)

or due only to the depletion charge for  $\psi_{s}<0,$  and is given by

$$C_{s}(\omega)_{HF} \cong \frac{\partial Q_{D}}{\partial \psi_{s}}$$

(2.17)

The quasi-static capacitance which is equivalent to the low frequency,  $C_{Q_B}$ , is measured from the displacement current, Ia, due to a ramped bias voltage. The displacement current Ia flowing through the MOS capacitor in response to a time varying voltage V is related to the differential capacitance  $C_B$  by

$$I_d = C_{Qs} \frac{dV}{dt} \quad , \qquad (2.18)$$

and can be written as

$$C_{LF} = C_{Qs} = \left(\frac{1}{C_{ox}} + \frac{1}{C_s + C_{it}}\right)^{-1} , \qquad (2.18)$$

which is simply the total capacitance due to all the compo-

nents.

#### 2.5 REAL MOS STRUCTURE

The Fermi level plays an important role in formulating equilibrium conditions when two different systems of different energies are brought into contact. The combined system will be in thermal equilibrium only when Er is the same in both parts. In general, the Fermi levels of different systems are different, then on contact there will be a flow of electrons from the system with higher initial Er to the system with the lower initial Er. This electron flow will continue until equality of the Fermi energies of the two systems is achieved. When no further net transfer of electrons occurs from one material to the other, the Fermi levels are equal. The bands are flat in the bulk semiconductor with the exception of the surface-region. The position of the Fermi level depends on the properties of the crystal and remains in its position despite band-bending. To bring the silicon surface to a flat-band condition or zero band-bending of such structure, it is necessary to apply an amount of gate voltage required to compensate for the difference in the work functions. This required voltage is called a flat-band voltage and is simply given by:

$$V_{FB} = \phi_{ms} \tag{2.19}$$

There are a number of phenomena, so far neglected in the analysis of a metal-oxide semiconductor structure, such as the existence of metal-semiconductor work function difference, and various types of charges at the interface. For the ideal MOS diode, it was assumed that the work-function difference in Eq. (2.1) is zero. If the value of  $\phi_{me}$  is not zero, and if there exists an interface trap charge density Q<sub>1t</sub> at the Si-SiO<sub>2</sub> interface, the external bias will be distributed across the oxide and the surface layer, such that

$$V_{G} = V_{ox} + \psi_{s} + \phi_{ms} \quad . \tag{2.20}$$

The effect of work-function difference  $\phi_{ms}$  and of interface trap charge density Qit can be cancelled by applying a gate potential equal to the flat-band voltage

$$V_{FB} = \phi_{ms} - \frac{Q_u}{C_{ox}} \quad . \tag{2.21}$$

Oxide charge is an important parameter in devices. The oxide charges can be mobile ions or fixed charges, which are spatially distributed in the oxide bulk with charge density p(x) which varies with distance. Fixed oxide charge Qr, is positive charge, primarly due to structural defects in the oxide depending on various processes such as oxidation ambient, temperature, cooling conditions, and on silicon crystal

orientation. This charge induces an image charge in the silicon surface. Therefore, the experimental capacitance-voltage curve will be displaced from the ideal theoretical curve by an amount

$$V_{FB} = \frac{Q_f t_{ox}}{\epsilon_o \epsilon_{ox}} \quad . \tag{2.22}$$

In electrical measurements Qr can be regarded as a charge sheet located at the Si-SiO2 interface. The mobile ionic charge Qm, most commonly is caused by the presence of ionized alkali metal atoms such as sodium or potassium. This type of charge is located either at the metal-SiO2 interface or at the Si-SiO2 interface and can move from one edge to the other of the oxide layer under thermal-electrical stressing. Thus, the resulting movement causes a change in the electrical characteristics. In the case of one layer, the corresponding voltage that ensures flat-band voltage is given by [16]:

$$\partial V_{FB} = -\rho(x) \frac{x \, dx}{\epsilon_o \epsilon_{ox}}$$

(2.23)

The effects of all layers comprised between x = 0 and  $t_{ox}$  are added, and the gate voltage required to compensate this shift is given by [16]:

$$V_{FB} = -\int_{0}^{t_{ox}} \frac{\rho(x) x dx}{\epsilon_{o} \epsilon_{ox}} \quad . \tag{2.24}$$

The total flat-band voltage, including the effect of work-function difference, interface trap charge and distributed oxide charge is then given by [16]:

$$V_{FB} = \phi_{ms} - \frac{Q_u}{C_{ox}} - \int_0^{t_{ox}} \frac{\rho(x) x \, dx}{\epsilon_o \epsilon_{ox}} \quad . \tag{2.25}$$

# OXIDE AND INTERFACE PROPERTIES

### 3.1 SILICON DIOXIDE IN MOS DEVICES

Silicon MOS devices have achieved widespread acceptance and use throughout the microelectronics industry, which can be directly attributed to the many well-known advantages of silicon planar technology and, in particular, to the ease with which a silicon substrate can be thermally oxidized to form silicon dioxide, which can be used both as an insulating layer and a mask against the diffusion of impurities into the substrate itself.

The direct surface reaction of single-crystal silicon with oxygen to form thermal silicon dioxide (oxide) has several properties that are useful in the formation of Metal-Oxide-Semiconductor (MOS) devices. These properties have facilitated the manufacture of high performance MOS

-28-

transistors with high transconductance, high gate input resistance, good reproducibility, and fair stability [13,16,18]. In particular, the direct reaction of silicon with oxygen creates a sharp Si-SiO2 interface with few dangling bonds. Since oxidation preserves the structure of the underlying silicon lattice, MOS devices have high surface carrier mobilities which are proportional to MOS transistor transconductance. Silicon dioxide has a large bandgap of approximately 8 eV that creates a 3.2 eV barrier to electrons and a 3.7 eV barrier to holes from silicon. Since oxide is an excellent insulator, MOS devices also have a large gate input resistance. Due to the strength of the Si-O bond, oxides are able to sustain large electric fields up to 12 Mv/cm. Finally, the kinetics of oxidation are well explained by the classical Deal and Grove model [19] and are easily controlled to give reproducible and uniform oxide thicknesses.

To achieve more complex and higher performance integrated circuits, the trend has been to scale down device geometries; especially, channel lengths and widths are decreased to increase circuit density, and gate dielectrics are thinned to maintain long channel characteristics. However, in order to maintain compatibility, the power supply voltage has remained constant resulting in high electric

-29-

fields and hot carriers that can damage MOS devices. In particular, exposing the MOS structure to ionizing radiation or to hot carriers has been shown to generate interface states and trapped charge in the gate oxide, which degrade device characteristics and eventually cause device failure [20]. This effect is especially troublesome in small geometry devices where large fields can accelerate carriers to high energies to overcome the Si-SO2 interface potential barrier and getting trapped in the SiO2 or generating interface traps. Although thick oxides are reasonable diffusion barriers to dopants, thin gate oxides are especially poor barriers to boron diffusion which complicates the use of p+ doped polysilicon gates in MOS devices [21]. Recent interest has focussed on thin oxides (<200 A) for potential VLSI applications [22]. However, reducing oxide thicknesses introduces undesirable features while removing some of the disadvantages of using thicker oxides. Such problems have prompted more investigation in thin-gate oxide technology. Since mobile alkali ions can cause unpredictable flatband voltages shifts and dielectric stability, therefore special care is necessary to avoid alkali ion contamination during fabrication of MOS devices. Finally, the electrical strength of a silicon dioxide film is limited by the weakest region. In thin oxides, typical surface and interface irregularities can severely limit the electrical strength of the film

-30-

defects caused by radiation or similar bond-breaking process. They are located at Si-SiO<sub>2</sub> interface with energies falling, within the silicon bandgap. Interface trapped charge is in electrical communication with the underlying silicon and can thus be charged or discharged, depending on the surface potential and, consequently, will vary with the applied gate voltage. The total amount of interface trapped charge will also depend greatly on their distribution in energy throughout the bandgap and whether they are acceptor or donor types. Most of the interface trapped charge can be neutralized by low temperature ( $450^{\circ}$ C) hydrogen annealing. Since Q<sub>14</sub> is distributed through the energy bandgap another quantity the interface trap density D<sub>14</sub> can be defined [16]:

$$D_{ii} = \frac{1}{q} \left( \frac{dQ_{ii}}{dE} \right) \quad . \tag{2.1}$$

The density of interface traps can vary according to several factors such as silicon orientation [25].

### 3.2.2 Oxide Charges

There are three types of oxide charge  $Q_0$ , that are technologically important. The first type, oxide fixed charge  $Q_f$ is positive, and is primarly due to structural defect (ionized silicon ) in the oxide layer less than 25 A from the Si-SiO2 interface. The density of this charge, whose origin is related to the oxidation process, depends on oxidation ambient temperature, cooling conditions, and on silicon orientation which affects the value of Qr significantly, in an increasing order: (100)<(110)<(111) [26]. This density of fixed charge differs greatly from the interface trapped charge density in that its magnitude, for all practical purpose, is not a function of the applied gate voltage or surface potential in the silicon near the interface because the energy levels of the states associated with the fixed oxide charge density lie outside of the forbidden bandgap, so that their probability of occupancy will not be affected as the Fermi level sweeps across the forbidden band with variations in the applied gate voltage. Their ionized state gives rise to a positive charge which shifts the measured C-V curve by:

$$\Delta V = -\frac{Q_f}{C_{ox}} \tag{2.2}$$

relative to a theoretical curve.

Unlike interface trapped charge, fixed oxide charge is not in electrical communication with the underlying silicon. Since fixed oxide charge density can not be determined in the presence of moderate densities of interface trap charge, it is only measured after a low temperature hydrogen treatment which minimizes interface trap density.

-33-

The second type, oxide trapped charge Qot may be positive or negative due to holes or electrons trapped in the bulk of the oxide. Trapping may result from ionizing radiation, avalanche injection, or other similar processes. Unlike fixed charge, oxide trapped charge is generally annealed out by low temperature (<500°C) treatment, although neutral traps may remain.

The third type, mobile ionic charge Qm, most commonly is caused by the presence of ionized alkali metal atoms such as sodium or potassium. This type of charge is located either at the metal-SiO<sub>2</sub> interface, where it originally entered the oxide layer, or at the Si-SiO<sub>2</sub> interface, where it has drifted under an applied field. Drift can occur because such ions are mobile in SiO<sub>2</sub> at relatively low temperature and their number is limited by emission from the interface [13].

## 3.3 INFLUENCE OF THE INTERFACE TRAP CHARGES ON

### THE BLECTRICAL CHARACTERISTICS OF MOS DEVICES

### 3.3.1 Degradation

With the advancement of microelectronics technology, the study and use of MOS structure is becoming increasingly important. It is partly because MOSFETs have certain definite advantage over bipolar transistor on account of being unipolar and majority carrier devices. Partly it is due to additional advantage of MOS technology over the bipolar

-34-

technology which lies in the use of MOSFET as resistor also requiring much less space and low cost.

In CMOS technology the power dissipation can be tremendously reduced. However, with the reduction of feature-size in MOS technology especially in the submicron range, a serious problem is encountered due to degradation of device characteristics by hot-electrons. These degradations are many fold. The degradation may be in the substrate on the top of which the surface channel is produced, it may be in the oxide, or in the oxide-semiconductor interface. Among these three the most important is the degradation in the interface. This interface already carries some undesirable elements by way of defects, irregularity etc. due to mismatching of lattice in oxide formation over the semiconductor. These irregularities and defects on the interface give rise to surface states which lie within the bandgap. Its impact on the device performance and lifetime is becoming more pronounced as the device geometry is being reduced while the power supply is not changed. This results in electric fields in MOSFETs large enough to energize carriers flowing in the channel and to increase the generation of hot carriers. These hot carriers cause damage by way of creating interface states and trapping of the charge in the oxide. The combination of the two types of damage leads to a gradual degradations of electrical characteristics of MOSFETs

-35-

and eventual circuit failure. The hot carrier trapping mechanism includes bulk oxide trapping and interface trap generation involving both holes and hot electrons. It is believed that interface trap generation is the main cause of degradation.

# 3.3.2 Effect of Interface Traps on Electrical Characteristics

These interface traps can easily exchange charge with silicon substrate and act as surface recombination the centers; thereby causing a considerable increase in the leakage currents observed at the drain junction. These high drain junction leakage currents are undesirable because they decrease the sensitivity of a MOSFET to a weak signal and more power is consumed by the device than necessary for optimum performance. This leakage current is increased by an increase in Dit. Interface traps also act as scattering centers at the Si-SiO2 interface; thereby reducing the effective carrier mobility in the channel and the fieldeffect mobility by immobilizing a portion of the carriers that would otherwise contribute to channel conductivity. Similarly, this effect can also contribute to a change in threshold voltage. The threshold voltage is increased in n-channel and decreased in p-channel devices. Interface traps can affect the drain junction breakdown voltage by

-36-

reducing the drain bias range over which the device can be operated. Besides they are responsible for the low-frequency (1/f) noise in MOS devices. This noise occurs because interface trap level occupancy fluctuates randomly. The resulting fluctuation in interface traps causes a corresponding fluctuation in channel charge density and thus channel conductance. This so-called flicker noise is dominated by interface traps for Dit above about  $10^{11} cm^{-2} eV^{-1}$  and is determined by the volume of the channel for less than this value. Increasing channel volume decreases flicker noise power. The oxide fixed charge greatly affects the flat-band voltage and the threshold voltage of MOS capacitors and MOSFETs. Oxide fixed charge will tend to oppose the effect of interface traps in both n-channel and p-channel devices. It will not have any serious effects on most other important electrical characteristics. However, the effect of interface traps becomes increasingly important as degradation progresses. Therefore, the understanding and characterization of Si-SiO2 interface traps and their effect in MOS device performance is important in the design of VLSI devices. One of the main reason why considerable disagreement still exists concerning the physical mechanisms of hot carrier degradation is believed to be the lack of a reliable technique to evaluate the damage at the interface caused by electrical stress or

-37-

radiation. Indeed, most of the studies have mainly based their conclusions about the nature of the degradation on the shift in current characteristics of the devices.

## 3.3.3 Effect of Interface Traps on C-V Curves

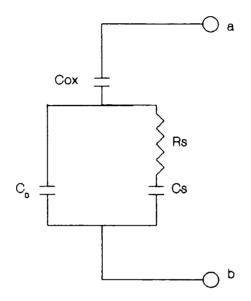

The influence of interface traps can be seen from the simplified equivalent circuit shown in Fig.3.1. The capacity of the semiconductor consists of two parallel parts, the space-charge capacity Cp and the interface trap capacity C<sub>2</sub> which has the interface trap resistance  $R_{2}$  in series. The quantities Cp, C<sub>2</sub>, and  $R_{2}$  are dependent on surface-potential and change when the surface field is changed. Cp can be calculated for each value of the surface-potential.

The interface trap parameters are unknown and have to be determined for each surface-potential by measuring the MOS capacitor, the MOS conductance or both. However, the impedance of the MOS capacitor is no longer similar to that of pure capacitance: a loss mechanism involved in carrier capture and remission gives rise to the occurence of a conductance in parallel to the MOS capacitance. In practice, the information contained in capacitance measurements is difficult to extract because the semiconductor capacitance  $C_D$ , affected by interface traps, occurs in series with the oxide capacitance,  $C_{OX}$ . It is known that only interface traps within a small energy range of the order of kT on either

-38-

side of the Fermi level contribute to the capacitance. For this to be confirmed, the change of surface-potential due to the applied ac voltage has to be less than kT/q. Since kT is about 26 meV at room temperature, compared to a width of the entire forbidden band equal to 1.1 eV, it is obvious that this technique can be used to probe the energy distribution of interface traps.

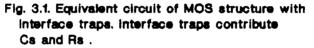

The influence of interface traps on the MOS curve is shown in Fig.3.2a. This influence is threefold: (a) The interface traps give an additional capacitance  $\Delta C$ . (b) They cause a frequency dispersion of the curve. (c) They change the voltage axis by changing the dependence of  $\psi_{\bullet}$  on voltage V.

The additional capacitance and the frequency dispersion is obvious from Fig. 3.2a. The influence on the voltage is explained in Fig.3.2b. When interface traps are present, the electric field  $E_{ox}$  in the oxide is higher than the field in the semiconductor surface. Therefore, more charges in the metal electrode are necessary to create a certain surface fields  $E_{\bullet}$  in the silicon. Thus, the voltage that sets up this value of surface-potential  $\psi_{\bullet}$  is higher by  $\Delta V$ .

## 3.4 CONTROL OF INTERFACE TRAP DENSITY

The dominant parameters controlling the interface properties are the technological parameters for the oxide

-39-

growth. The oxide growth proceeds by three consecutive reactions, which are the transfer of oxygen into the oxide already formed, the diffusion of oxygen through the oxide, and the reaction of oxygen with silicon at the interface to form SiO<sub>2</sub>.

Interface traps and oxide fixed charge characteristic of thermally grown SiO<sub>2</sub> can adversely affect device performance if their densities are not controlled. The influence is compounded by the fact that their densities can change with time during device life, thus posing a stability problem. To optimise device performance and stability, one must be able to control the oxide and interfacial properties during fabrication and keep these properties stable during device operation.

The interface trap level density can be controlled or minimized by using a high oxidation temperature and a (100) orientation, but it must be reduced further by annealing. There are two annealing methods effective for reducing Die after thermal oxidation: the low temperature postmetallization anneal [25,27] and the high temperature postoxidation anneal [26]. Both of these methods are widely used. It was shown [26] that Die and Qr produced by thermal oxidation have the same silicon surface orientation dependence. The lowest values of Qr and Die are obtained for (100) orientation, and the higher values were consistently measured for

-41-

(111) silicon. The (100) orientation is the most widely used in integrated circuit technology.

It is also possible to reduce oxide trapping by making a suitable design for the geometry of the structure to avoid high fields due to hot carrier in short-channel. Therefore, many device structures have been proposed to improve MOSFET performance with higher response speed, lower power consumption, more reliable operation, and higher handling capability.

# MEASUREMENT TECHNIQUES OF INTERFACE TRAPPED CHARGES

### 4.1 INTRODUCTION

A number of techniques for the measurement of trapped charge on the Si-SiO<sub>2</sub> interface of MOS structures are available. Most of them employ the device in the form of a MOS capacitor and are based on the measurement of capacitance and conductance as a function of bias voltage, frequency, and temperature. In general these techniques, including all those which are better suited to MOS capacitors [6-9] as well as those which are solely based on MOS transistor function itself [28,29,30] are not only limitedly applicable because of a lack of sensitivity, incomplete information or inability to treat non-uniform spatial distribution. A very few techniques use measurement of substrate current [31,32]. Recently, it has been shown that the charge pumping technique [12], which utilizes the substrate current in a MOSFET, for the determination of the interface properties, is capable of independently providing the amount of the charges that have been trapped in the Si-SiO<sub>2</sub>. This technique will be described in chapter 5.

The discussion of experimental techniques in this chapter will be centered around the capacitance methods. All of these techniques, which are more common in use such as the differentiation method by Terman [7], the integration method by Berglund [17], the conductance method [9], and the DLTS technique [11], will be presented in details whereas the others which are more or less of historical interest will be presented only briefly in this chapter.

### 4.2 INTERFACE TRAPS DENSITY EXTRACTION METHODS

The interface trap density between flatband  $(\psi_{\bullet}=0)$  and the onset of the strong inversion  $(\psi_{\bullet}=2\phi_{\bullet})$  can be accurately extracted from C-V measurements by the following three methods:

1. The Terman method [7] is based on the comparison between the hypothetical high frequency C-V curve with interface traps to and an ideal C-V curve. The ideal curve is calculated for the same doping density and oxide thickness but without interface traps. This ideal C-V curve is calculated by the help of Eq.(2.15). However, the capacitance  $C_{\pi}$  in Eq.(2.15) is a known function of band bending  $\psi_{\eta}$ , and hence

-44-

can be calculated with the help of Eqs.(2.5) and (2.7). Therefore, a theoretical plot of CHF versus  $\psi_{\bullet}$  is made and compared with the measured plot of CHF versus Vo. The amount of stretchout, as measured by  $\Delta V$  between the ideal and the measured high frequency C-V curves at a particular surface-potential, determines the interface trap density Dit. The additional charge,  $\Delta Q_u$ , generated by interface traps is given by [7]:

$$\Delta Q_{ii} = C_{ox} \Delta V \quad , \tag{4.1}$$

where  $C_{ox}$  is the capacitance per unit area of oxide-layer. The interface traps density per unit surface potential  $(\Delta \psi_s = leV)$  is given by [7]:

$$D_{ii} = \frac{1}{q} \frac{dQ_{ii}}{d\psi_s} , \qquad (4.2)$$

where q is the electron charge.

2. The low frequency method proposed by Berglund [17], makes it possible to determine the conductor surface-potential  $\psi_s$ as a function of the applied voltage Vg directly from low-frequency differential capacitance measurement, and no differentiation is required to determine the density of interface traps, Dit. In the low-frequency, the surface potential corresponding to the bias voltage can be determined without assuming a doping profile. Since an incremental increase in Vo causes an incremental increase in  $\psi$ , through a capacitive voltage divider ( see Fig.2.5) one can write

$$\partial \psi_s = \frac{C_{ox}}{C_{ox} + C_s + C_u} \partial V_G \qquad (4.3)$$

Rearranging Eq.(4.3) in terms of  $C_{LF}$  given by Eq.(2.18) and integrating under the condition that  $\psi_{s}=0$  at  $V_{G}=V_{FB}$  yields

$$\psi_{s} = \int_{V_{FB}}^{V_{G}} \left( 1 - \frac{C_{LF}}{C_{ox}} \right) dV_{G} \qquad (4.4)$$

Equation (4.4) indicates that the surface potential at any applied voltage can be determined by integrating a curve of  $\left(1-\frac{c_{12}}{c_{12}}\right)$ . It is important to notice that Eq.(4.4) is valid only when the interface traps are in equilibrium at all times during the measurement of C(V). The energy density of interface traps, Dit (states/cm<sup>2</sup>eV), can be expressed in terms of the capacitance Cit of the interface traps as

$$D_{u}(\psi_{s}) = \frac{C_{u}(\psi_{s})}{q} \qquad (4.5)$$

Solving Eq.(2.18) for  $C_{1t}$  and replacing in Eq.(4.5) gives

$$D_{it}(\psi_s) = \frac{1}{q} \cdot \{ (\frac{1}{C_{LF}} - \frac{1}{C_{ox}})^{-1} - C_s(\psi_s) \} , \quad (4.6)$$

where  $C_{*}(\psi_{*})$  is the semiconductor capacitance.

Determination of Dit( $\psi_{\bullet}$ ) from Eq.(4.6) needs Cox, CLF and C<sub>a</sub>( $\psi_{\bullet}$ ). Whereas Cox can be obtained from the oxide-data and CLF from the experimental C-V curve, the quantity C<sub>a</sub>( $\psi_{\bullet}$ ) needs certain manipulation. This quantity C<sub>a</sub>( $\psi_{\bullet}$ ) can be obtained with the help of Eqs.(2.5) and (2.7) if the surface-potential  $\psi_{\bullet}$  is known. The determination of CLF from low-frequency C-V curves also needs the value of  $\psi_{\bullet}$ . The value of  $\psi_{\bullet}$  is obtained with the help of Eq.(4.4) provided the flatband voltage VFB, which form the lower limit of the integral of Eq.(4.4) is known. Therefore main quantity of Lit Provided the remains to be worked out in the determination of Dit is VFB. The determination of VFB will be described later in this section.

3. The energy density of interface traps also can be calculated by using both high and low frequency CV curves. Assuming that no traps contribute any capacitance at high frequency, from Eq.(2.15) we can obtain a measured value of  $C_{\bullet}$  given by

-47-

$$C_{s}(V_{G}) = \left\{ \frac{1}{C_{HF}(V_{G})} - \frac{1}{C_{ox}} \right\}^{-1} . \qquad (4.7)$$

Therefore, by substituting for  $C_{*}(V_{c})$  in Eq.(4.6), Dit becomes

$$D_{ii} = \frac{1}{q} \left\{ \left( \frac{1}{C_{LF}} - \frac{1}{C_{ox}} \right)^{-1} - \left( \frac{1}{C_{HF}} - \frac{1}{C_{ox}} \right)^{-1} \right\} \quad .$$

(4.8)

The distribution of interface traps in the bandgap is determined by calculating the surface potential  $\psi_{a}$  at which  $C_{LF}$ and  $C_{HF}$  are measured and as stated earlier  $\psi_{a}$  can be obtained with the help of Eq.(4.4) provided the flatband voltage VFB is known.

### 4.2.1 Determination of VFB

The LFCV and HFCV measurements are used to extract the flat-band voltage, VFB, as needed in Eq.(4.4) for the determination of  $\psi_{\bullet}$  and hence the density of interface traps Dit. However, before VFB can be determined, it needs knowledge of another quantity the flat-band capacitance CFB which itself is a function of the substrate doping concentration N<sub>☉</sub>. The semiconductor capacitance acquires a minimum value (C<sub>☉</sub>)min when the depletion layer acquires the maximum width Wmmax so that

$$(C_s)_{\min} = \frac{\epsilon_s A}{W_{\max}} , \qquad (4.9)$$

and

$$W_{\max} = \left[\frac{4\epsilon_s |\phi_B|}{qN_s}\right]^{\frac{1}{2}} , \qquad (4.10)$$

where  $\epsilon_{\bullet}$  is the silicon dielectric constant and A the device area. The bulk potential  $|\phi_{\bullet}|$  can be represented in terms of the substrate doping concentration N<sub>s</sub> and intrinsic concentration n<sub>1</sub> as

$$\left|\phi_{B}\right| = \frac{kT}{q} \ln\left(\frac{N_{s}}{n_{i}}\right) \quad , \qquad (4.11)$$

where k is the Boltzmann constant and T the temperature in Kelvin. Using Eq.(2.15), the minimum capacitance in a HFCV curve can be written as:

$$(C_{HF})_{\min} = \left[\frac{1}{C_{ox}} + \frac{1}{(C_s)_{\min}}\right]^{-1}$$

(4.12)

Substituting and eliminating  $\phi_p$ ,  $W_{max}$ , and  $C_{a}$  give the following relationship for N<sub>a</sub>:

$$N_{s} = \frac{4kT}{q^{2}\epsilon_{s}A^{2}} \left(\frac{C_{ox}(C_{HF})_{\min}}{C_{ox} - (C_{HF})_{\min}}\right)^{2} \ln \frac{N_{s}}{n_{i}} \quad .$$

(4.13)

The capacitance of the MOS device at  $\psi_s=0$ , which is called the flatband capacitance CFB, is built up of two capacitors. These two capacitors, one of which is the oxide capacitance  $C_{ox}$  and another the flatband capacitance of semiconductor CFBS, are connected in parallel and so

$$C_{FB} = \frac{C_{ox}C_{FBS}}{C_{ox} + C_{FBS}} \quad . \tag{4.14}$$

In fact the flatband capacitance of the semiconductor is the capacitance of the surface layer of the substrate within a distance equal to the Debye length Lp from the interface so that

$$C_{FBS} = \frac{\epsilon_s A}{L_D} \quad , \tag{4.15}$$

where Lp is given by

$$L_D = \left(\frac{kT\epsilon_s}{q^2N_s}\right)^{\frac{1}{2}} \quad . \tag{4.16}$$

The nearest gate voltage corresponding to the capacitance CFB on the HFCV curve is the required value of the flatband voltage VFB. The value of VFB so obtained can be used in Eq.(4.4) to obtain a relation between  $\psi$ , and VG which in turn can be utilized to obtain the value of CHF and CLF from their respective experimentally measured HFCV and LFCV curves. Finally after knowing CHF and CLF at any desired value of  $\psi$ , the corresponding value of Dit can be obtained using either of the relations (4.6) or (4.8).

As the determination of D<sub>1t</sub> involves the use of several relations, of which some are in closed form and others are not such as Eq.(4.13), the whole analysis needs a certain program to be developed which after using the stored data can yield automatically the values of D<sub>1t</sub> at different values of  $\psi_{1}$ .

# 4.2.2 Accuracy and Limits of Interface Trap Density Extraction by C-V Methods

The extraction of interface density from the capacitance methods has several limitations in accuracy. In Terman method [7], one source of error is the need of a theoretical C-V curve which makes use of a certain assumed doping profile. Spatial nonuniformities at the charge distribution in the oxide along the interfacial plane also can cause an error in the calculated  $C_{\bullet}(\psi_{\bullet})$ . Another error is failure to measure a true high frequency C-V curve, particularly a

-51-

problem near flatband or in accumulation. As flatband is approached, majority carrier density increases, making capture more rapid and interface trap time constant shorter. The determination of  $C_{ox}$  also causes a problem, since in the case of an oxide, generally we consider the highest value of the measured capacitance at the lowest frequency. However, its main advantage lies in the rapidity and the great simplicity. It becomes quite inaccurate and unreliable for low interface trap density (less than  $10^{11}cm^{-2}eV^{-1}$ ), because the shifting between the theoretical and experimental C-V curves is very small to be exploited.

Like the high frequency capacitance method, the Berglund method [17] needs a theoretical estimate of semiconductor capacitance C<sub>2</sub>, which is most easily done when assuming doping profile. Usually this profile is nonuniform due to impurity redistribution during oxidation process. Such doping nonuniformity leads to an underestimate of D<sub>1</sub> ( error in extracting D<sub>1</sub> ). A more serious error occurs when the theoretical C<sub>2</sub> is subtracted from the measured ( C<sub>2</sub> + C<sub>1</sub> ). Therefore, an error in  $\psi_{2}$  leads to the use of a value of C<sub>2</sub> corresponding to the wrong band bending. This error will be most serious where (C<sub>1</sub>t/C<sub>2</sub>) is small or where C<sub>2</sub> is a rapid function of band bending. Another serious error is due to the wrong calculation of VFB at the matching point where  $\psi_{2}=0$ , which can produce erratic D<sub>1</sub>t values, especially around flatband and accumulation regions, and occasionally

-52-

near strong inversion. However, both methods suffer from the inaccuracy introduced by an assumed doping profile.

The combined high-low frequency method [8] is able to extract Cit as a difference in measured capacitance without assuming any particular doping profile and the need for a theoretical computation of C<sub>s</sub> is eliminated. Since the interface trap density is calculated from the difference in HFCV and QSCV ( or LFCV ), the method erroneously counts inversion charge (Qinv) as interface traps. As inversion is approached, the HFCV does not include capacitance due to the inversion layer, since minority carriers do not respond. However, the LFCV curve does contain this inversion laver capacitance CI; thereby counting CI as interface trap capacitance. The difference taken between LFCV and HFCV curve therefore includes this term ( Cit + CI ). The value of the interface traps density Dit extracted from this capacitance will be in error unless Cr is negligible compared to Cit. This error becomes intolerable and places a limit on the surface potential at the onset of strong inversion. Towards accumulation, both HFCV and LFCV increase as  $C_{\bullet}$  increases. Therefore,  $C_{1t}$  is difficult to extract as a small difference between two large numbers. This places a limit on the surface potential at flatband. The most reliable measurement of interface trap density is at midgap where  $\psi_{1} = \phi_{2}$  ( in the range extending from mid-depletion to weak inversion ). This method is effective only with a large

-53-

gate area. Its main advantage is that  $C_{\bullet}$  is determined experimentally from a high frequency C-V measurement for the same gate bias at which ( $C_{\bullet} + C_{1t}$ ) is measured using a LFCV measurement. Therefore, the subtracted  $C_{\bullet}$  automatically corresponds to the correct band bending.

### 4.3 CONDUCTANCE METHOD

method has been proposed by E.H. Nicollian and This Goetzberger [9]. It is based on the steady state loss due to the capture and emission of carriers by interface traps. This energy loss is measured as an equivalent parallel conductance Gp. This conductance related to the loss is proportional to the capacitance  $C_{\bullet}$  ( associated to the interface traps ) and inversely proportional to the characteristic time  $\tau$ . This technique provides more and accurate information about interface traps, particularly when the density is low such as in thermally oxidized Si-SiO2 system. A fundamental property of this advanced technique is not only the capacitance, but also the conductance or the phase. Both are related by the Kramers-Kronig relation. Interface trap density and capture cross section are obtained from measurements of the MOS admittance as a function of voltage and frequency of the gate bias. However, a large number of measurements are required to achieve such detailed results,

-54-

and only that portion of the energy gap which lies between mid-gap and the Fermi level can be conveniently probed with this technique.

# 4.3.1 General Principle

The principle of the MOS conductance technique can be easily understood by the simplified equivalent circuit shown in Fig.3.1. It consists of measuring the admittance of the MOS structure at different frequencies while keeping the bias voltage and temperature constants, and to extract the equivalent parallel conductance  $G_p$ . The measured admittance  $Y_m$  of the MOS capacitor is given by

$$Y_m = G_m + j \omega C_m \quad , \tag{4.17}$$

where  $G_m$  is the measured equivalent parallel conductance,  $C_m$  the measured capacitance, and  $\omega$  the angular frequency of the applied gate voltage signal. Converting this admittance to an impedance, subtracting out of it the reactance of the oxide capacitance, and converting back to an admittance yields the required equivalent parallel conductance  $G_p$  as its real part. Thus

$$\frac{G_{p}}{\omega} = \frac{\omega C_{ox}^{2} G_{m}}{G_{m}^{2} + \omega^{2} (C_{ox} - C_{m})^{2}} , \qquad (4.18)$$

where  $C_{ox}$  is the oxide capacitance measured in strong accumulation at low frequencies. Therefore, the variation of  $G_P/\omega$  with bias or frequency can be easily plotted. It can be easily shown [9] that the equivalent parallel capacitance C of a single-level interface-state near the conduction band is

$$C = \frac{C_s}{1 + \omega^2 \tau^2} , \qquad (4.19)$$

and the equivalent parallel conductance  $G_P$  is

$$G_{p} = \frac{C_{s}\omega^{2}\tau}{1+\omega^{2}\tau^{2}} , \qquad (4.20a)$$

so that

$$\frac{G_p}{\omega} = \frac{C_s \omega \tau}{1 + \omega^2 \tau^2} , \qquad (4.20b)$$

where  $\tau$  is the interface-trap life time whose value is  $R_{\bullet}C_{\bullet}$ ; C<sub> $\bullet$ </sub> and R<sub> $\bullet$ </sub> being the capacitance and resistance associated with the interface traps which are functions of surface potential.

This interface-state RC network appears in parallel with the semiconductor depletion-layer capacitance Cp, as shown in Fig.3.1.  $G_P$  is divided by  $\omega$  to make Eq.(4.20b) symmetrical

in wt.

Using the simplified circuit shown in Fig.3.1, the equivalent parallel capacitance is

$$C_{p} = C_{D} + \frac{C_{s}}{1 + \omega^{2} \tau^{2}} \quad . \tag{4.21}$$

where CD is the semiconductor depletion-layer capacitance. Equation (4.21) describes the capacitance dispersion and is the basis of Terman's method. To extract C<sub>2</sub> and  $\tau$  from C<sub>p</sub> using Eq.(4.21), CD must be known and can be calculated using an estimated doping density. On the other hand, Eq.(4.20b) does not contain CD and depends only on the interface trap branch of the equivalent circuit. At a given bias, G<sub>p</sub>/ $\omega$  can be measured as a function of frequency. A plot of G<sub>p</sub>/ $\omega$  versus  $\omega\tau$  will go through a maximum when  $\omega\tau = 1$  which gives directly  $\tau$ . The value of G<sub>p</sub>/ $\omega$  at the maximum is C<sub>2</sub>/2. Thus, the equivalent parallel conductance corrected for C<sub>ox</sub> gives C<sub>2</sub> and  $\tau = R_*C_*$  directly from the measured conductance. Once C<sub>2</sub> is known, the interface trap

$$D_{ii} = \frac{C_{i}}{qA} , \qquad (4.22)$$

where A is the area of the device.

However, in practice the interface traps are observed to

be comprised of many levels so closely spaced in energy that they cannot be distinguished as separate levels. Thus, they appear as a continuum over the band gap of the silicon. For the continuum of traps or states, the real part of the admittance is given by [9]:

$$\frac{G_p}{\omega} = \frac{q D_u}{2\omega\tau_m} \ln\left(1 + \omega^2 \tau_m^2\right) \quad . \tag{4.23}$$

$G_{\mathbf{p}}$  is directly related to Dit. The maximum value  $(G_{\mathbf{p}}/\omega)_{\max}$ of  $G_{\mathbf{p}}/\omega$  is approximately 0.4qDit at  $\tau = \tau_m$  such that  $\omega \tau_m = 1.98$ . Therefore, the value of Dit is obtained from

$$D_{u} = \frac{1}{0.4q} \left(\frac{G_{p}}{\omega}\right)_{\max} \quad . \tag{4.24}$$

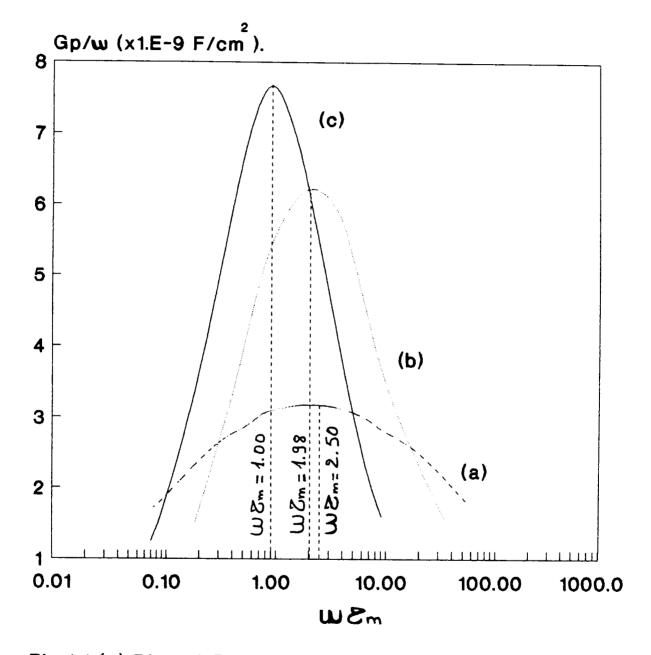

These relations, however, are only approximately true because they are derived from a single-level equivalent circuit. For more precise results, the statistical model equations have to be used [9]. Figure 4.1 shows the expected

Fig.4.1 (a) Plot of Gp/w versus logwz illustrating the observed interface trap time constant. Curve (b) for a continuum interface trap. Curve (c) for a single-level interface trap (after [9]).

$G_{\rm P}/\omega$  for a single level, continuum, and the statistical model. From Fig.4.1, it is seen that the peak of the  $G_{\rm P}/\omega$  curves is lower than is expected from the simple formula and occurs when  $\omega \tau_{\rm max} = 2.5$ . This condition  $\omega \tau_{\rm max} = 2.5$  is used to find  $\tau_{\rm max}$  from the frequency at which the measured  $G_{\rm P}/\omega$  versus frequency curve goes through a maximum at each bias.

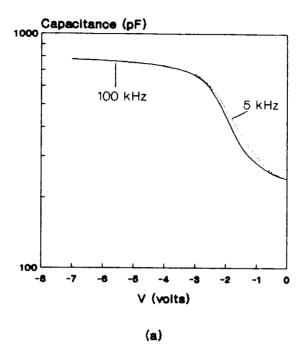

The conductance method is more sensitive than the capacitance methods because  $C_{\bullet}$  is measured directly, not as a difference between  $C_{P}$  and  $C_{D}$ . This is illustrated in Fig.4.2, which shows the measured capacitance and conductance. Taking difference in capacitances leads to round-off error in computing  $C_{\bullet}$ . Moreover, because  $C_{D}$  is larger near flatband than near midgap, this error will be more severe near flatband and puts a limit on how close in energy to the majority band edge  $D_{1t}$  can be extracted. The relative error of the conductance method depends on the relative error of measuring  $C_{\bullet x}$ ,  $C_{m}$ ,  $G_{m}$ , and  $\omega$ .

#### 4.4 DEEP-LEVEL TRANSIENT SPECTROSCOPY

The Deep-Level Transient Spectroscopy (DLTS) which was initially developed for MOS capacitors has also been extended for MOS transistors [29]. The DLTS developed by D.V lang [11] is based on the physics of the high-frequency capacitance transients method [33]. This technique is used to obtain information about an impurity level in the depletion region of a Shottky barrier or a p-n junction by

-60-

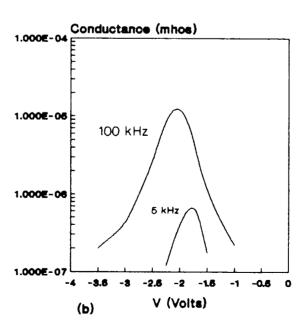

observing the capacitance transient associated with the return to thermal equilibrium of the occupation of the level following an initial non-equilibrium condition. The principle is simple; after an appropriate variation of the reverse bias of the junction from Vo to V1 with  $|V_1| < |V_0|$  during a time t<sub>P</sub>, one obtains a transient capacitance associated to the carrier emission of the defect filled during the t<sub>P</sub> as shown in Fig.4.3a. The electron emission is mirrored in the capacitance change, consequently all information about the concentrations, energy levels, and capture cross sections of these traps results from the capacitance changes.

By applying a large reverse-bias (quiescent state) to the sample, a wide space charge region is created where majority carrier traps are emptied. When a zero or small negative bias pulse is applied, the traps are filled with majority carriers from the bulk population. When the filling pulse is removed, the traps emit carriers to their respective band edge. Since the electronic transitions in the space charge region are essentially due to emission process (depleted of free carriers), the time constant for this emission process is controlled via a change of junction capacitance  $\Delta C$ . These filled energy states return to their initial condition if a thermal stimulation is provided. The trap occupancy will change as a result of a change in the equilibrium conditions. In general this change will be a time dependent

-62-

Fig.4.3 Typical time dependence involved in pulsed bias capacitance transients for (a) majority- and (b) minority carrier traps.

exponential function.

To detect minority carrier traps, an injection pulse (forward filling pulse) is used in a p-n junction to fill the minority carrier traps with minority carriers as shown in Fig.4.3b.

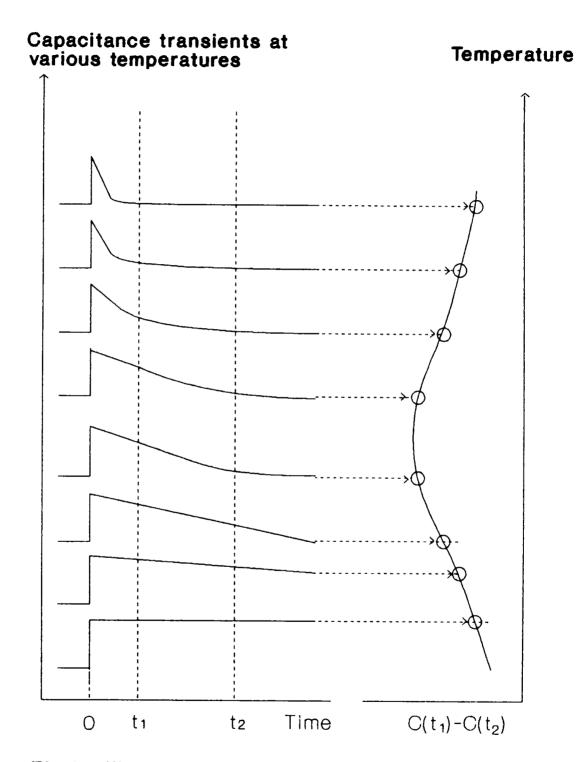

The method is based upon the production of a rate window which was originally implemented by a double boxcar integrator [34]. The use of a double boxcar to select the rate window is illustrated in Fig.4.4. The transient signals are fed into this device with gates at preassigned time  $t_1$ , and  $t_2$  and produce an output proportional to their average difference. The change in capacitance between  $t_1$  and  $t_2$  is called the DLTS signal, and is given by [11]:

$$\Delta C = C(t_1) - C(t_2) , \qquad (4.25)$$

and the normalized DLTS signal S(T) is defined as follows :

$$S(T) = \frac{C(t_1) - C(t_2)}{\Delta C(0)} , \qquad (4.26)$$

where  $\Delta C(0)$  is the capacitance change at t = 0 due to a saturating injection pulse and is given by

$$\Delta C(0) = C(\infty) - C(0) \tag{4.27}$$

Fig.4.4 Illustration of how a double boxcar is used to define the rate window.

where  $C(\infty)$  and C(0) are given respectively by [35]:

$$C(\infty) = \sqrt{\frac{N_{D}q \in A^{2}}{2(V_{i} - V)}} , \qquad (4.28)$$

and

$$C(0) = C(\infty) \left[ 1 - \frac{N_T}{2N_D} \right] ,$$

(4.29)

where A is the area of the junction,  $\epsilon$  the permitivity of the dielectric constant of the depleted material, V<sub>1</sub> the built-in bias voltage of the junction, V the externally applied voltage, q the charge of the electron, N<sub>D</sub> the density of ionized doping centers, and N<sub>T</sub> the trap concentration. If the capacitance is assumed to be exponential with time constant  $\tau$  then

$$S(T) = \exp\left(-\frac{t_1}{\tau}\right) - \exp\left(-\frac{t_2}{\tau}\right) , \qquad (4.30)$$

where the temperature dependence of  $\tau$  is given by the emission probability or thermal emission rate. The emission rates for an electron and a hole at equilibrium are given respectively by [36,37]:

$$e_n = v_{th} \sigma_n n_i \exp\left(\frac{E_T - E_i}{kT}\right) , \qquad (4.31)$$

and

$$e_{p} = v_{th} \sigma_{p} n_{i} \exp\left(\frac{E_{i} - E_{T}}{kT}\right) , \qquad (4.32)$$

where  $v_{th}$  is the thermal velocity of the carriers, n1 the intrinsic carrier concentration, ET the energy level of the center,  $\sigma_n(\sigma_p)$  the capture cross section, which describes the effectiveness of the center to capture an electron (hole), k the Boltzmann constant, and T the absolute temperature. Equation (4.30) can also be written as:

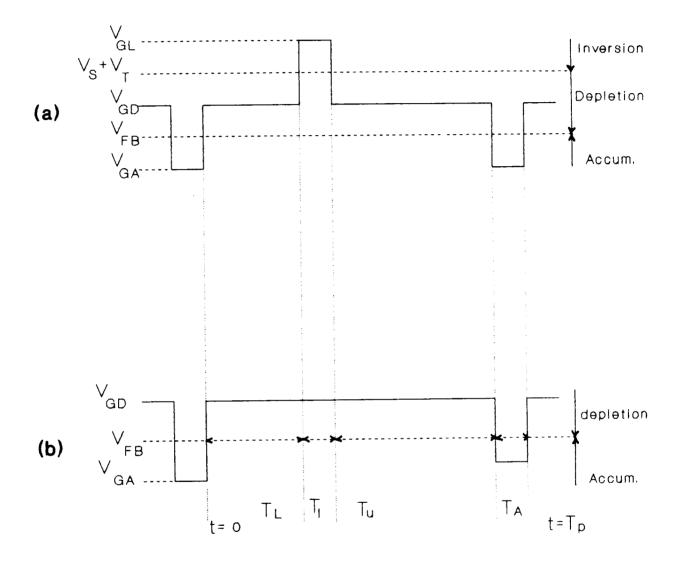

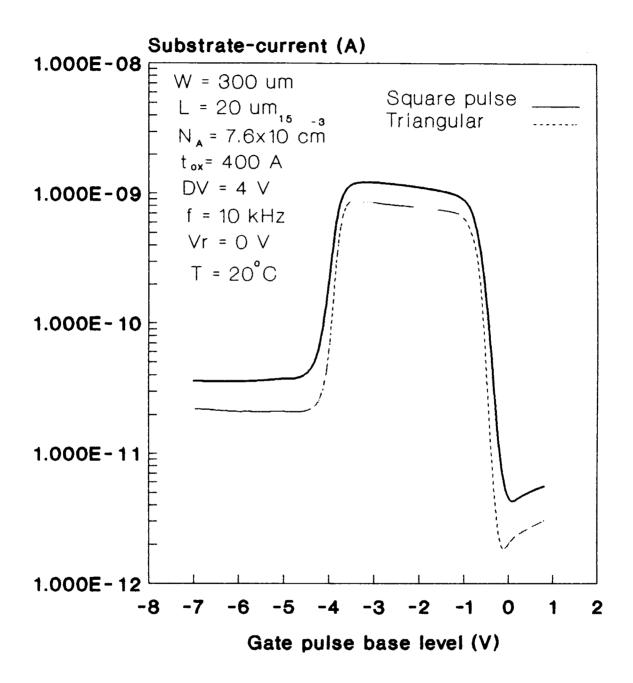

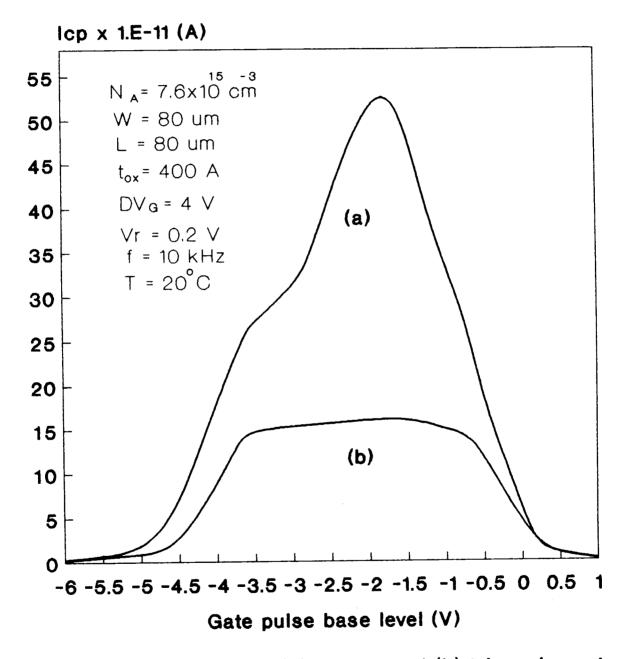

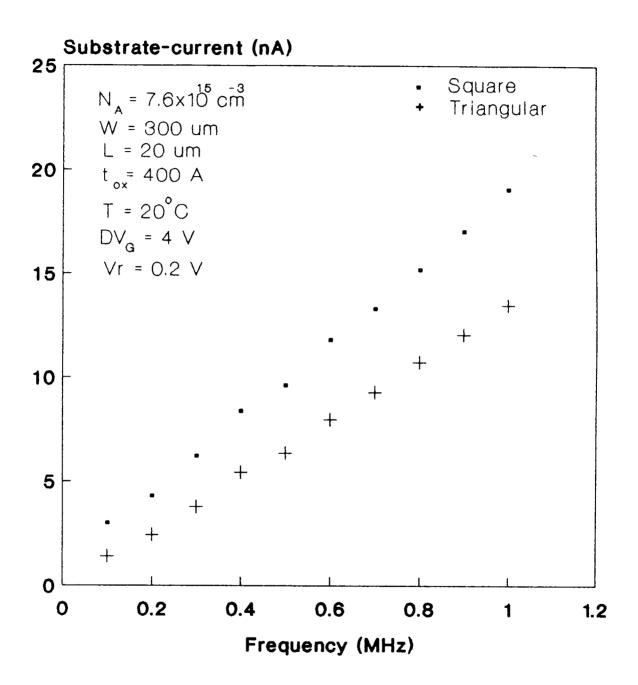

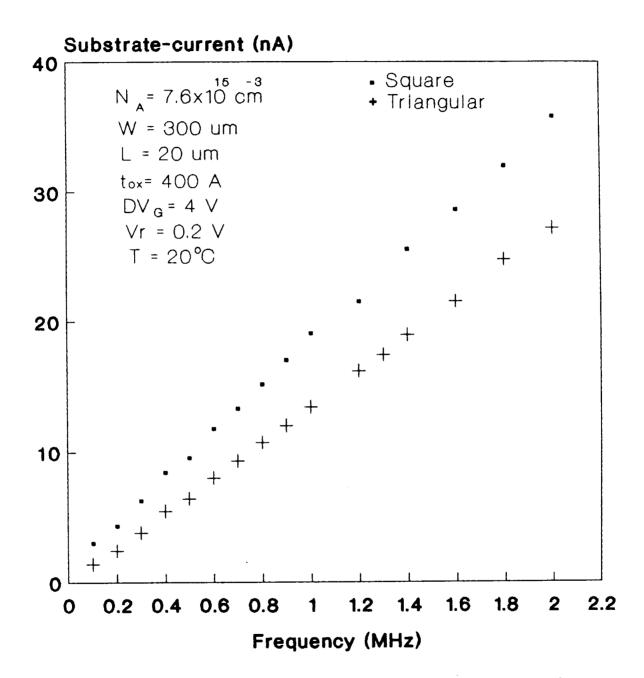

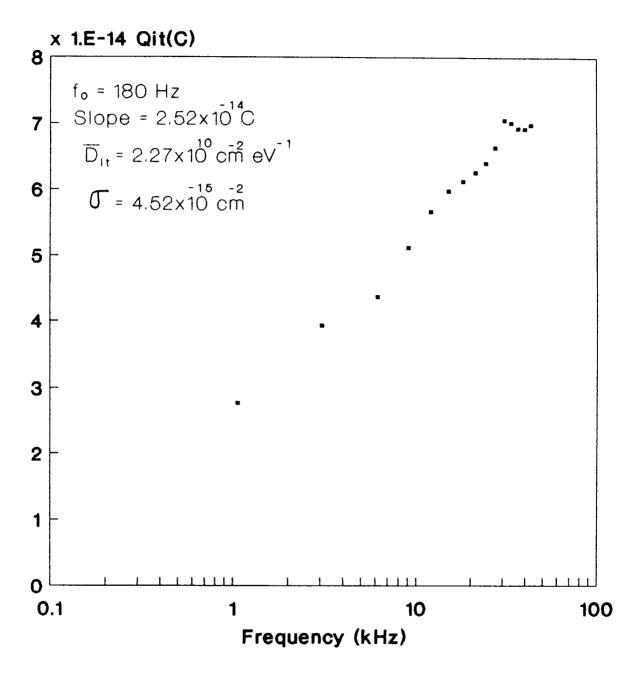

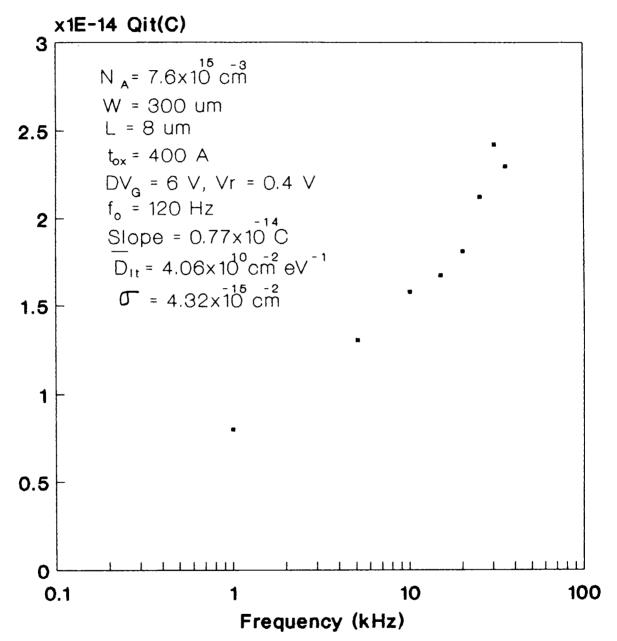

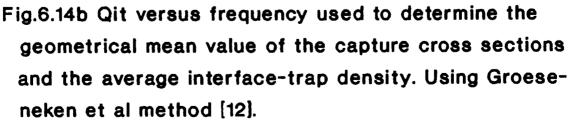

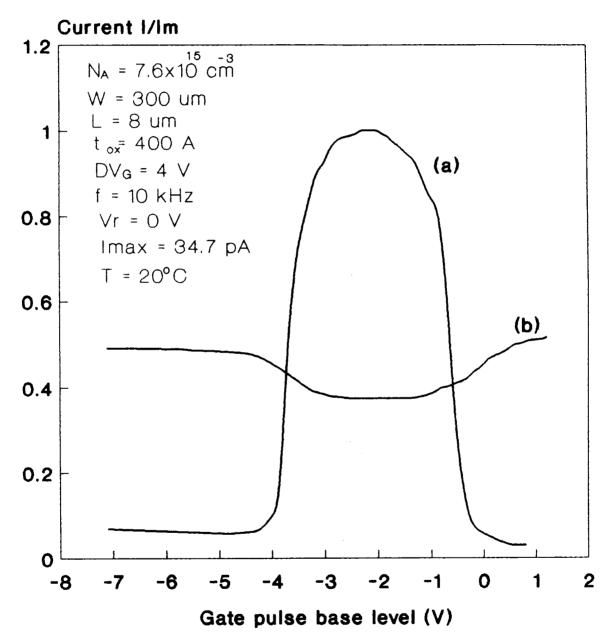

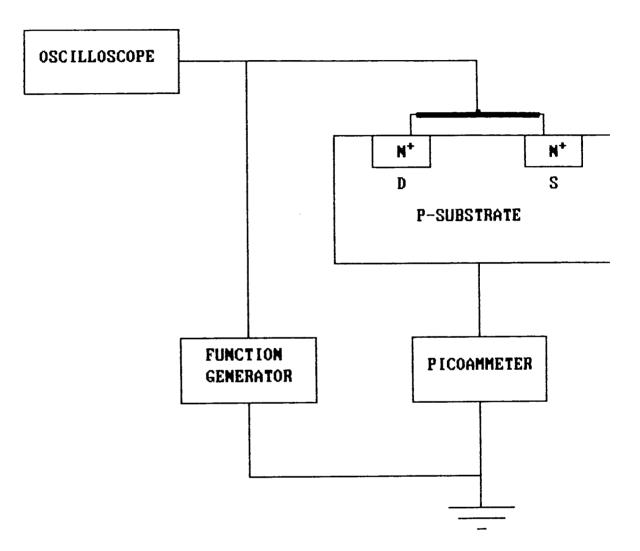

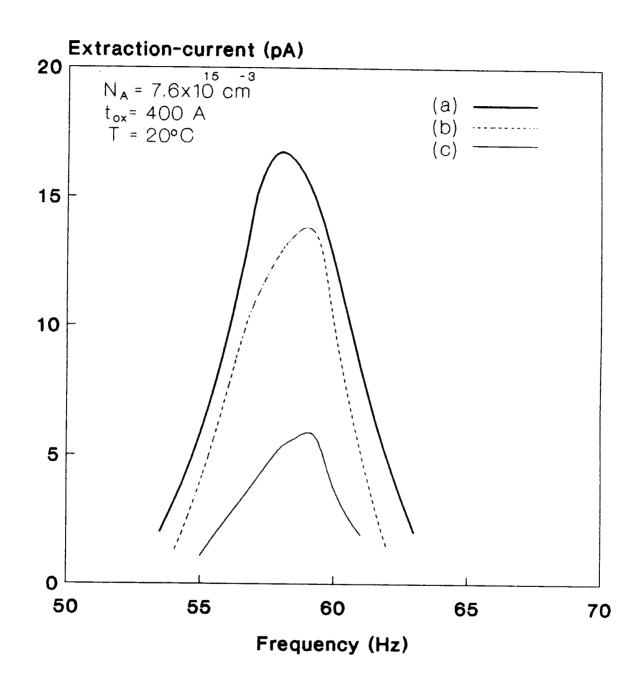

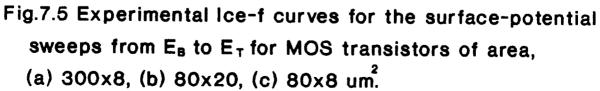

$$S(T) = \exp\left(-\frac{t_1}{\tau}\right) \left(1 - \exp\left(-\frac{\Delta t}{\tau}\right)\right) , \qquad (4.33)$$