# PEOPLE'S DEMOCRATIC REPUBLIC OF ALGERIA MINISTERY OF HIGHER EDUCATION AND SCIENTIFIC RESEARCH UNIVERSITY M'HAMED BOUGARA-BOUMERDES

# Institute of Electrical and Electronic Engineering

# **Doctorate Thesis**

Presented by:

## ZITOUNI Abdelkader

For a **PhD Degree** in:

### Filière : Génie électrique et électrotechnique

**Option :** Electronique

# **Title: Protective System Enhancement Using Optimization Technique in Power Grid**

To be defended before the jury composed of :

| Mr | BENAZZOUZ Djamel | Prof | (UMBB)         | President  |

|----|------------------|------|----------------|------------|

| Mr | BENTARZI Hamid   | Prof | (UMBB)         | Supervisor |

| Mr | KARA Kamel       | Prof | (Univ. Blida1) | Examiner   |

| Mr | MELIANI Hamza    | Prof | (Univ. Blida1) | Examiner   |

Année Universitaire 2017/2018

#### ABSTRACT

Nowadays, Phasor measurement units (PMU) may be used to enhance power grid protection due to their flexibility, security and dependability properties. The decision of the digital protective relay highly depends on the digital signal filtering computing the fundamental phasors of line voltages and currents. However, during a transient condition, line current and voltage may include unwanted components such as dc exponentially decaying associated with the harmonics and sub-harmonics especially in the smart grid. The used digital algorithms always need few cycles for obtaining the accurate fundamental phasors which are undesirable in the protection field. The first approach proposed in this research work for reliable phasor estimation algorithm is to remove disturbance signals using optimized digital filter (ODF) and DFT algorithm. The obtained phasor algorithm has the required characteristics to remove the dc component and dump the sub-harmonic as well as harmonic components. The performance of the developed digital relay is tested using estimated disturbance test signals or generated signal obtained from the power system network simulator with thyristor-controlled switched capacitor (TCSC) compensator that has been developed for this purpose.

In this research thesis, Root Cause Analysis based on fault tree technique is used to identify disturbances first and root cause of false trips of a protective relay which may lead in cascading to blackout. Once the critical root causes are identified, conventional mitigation measures have been used first and then blocking and unblocking functions and digital filters in view of increasing the reliability of the considered protection system are proposed.

The placement of phasor measurement units (PMUs) in electric transmission systems has also gained much attention for enhancing the control as well as the protection scheme. In this research work, a binary teaching learning based optimization (BTLBO) algorithm for the optimal placement of phasor measurement units (PMUs) is proposed. The optimal PMU placement problem is formulated to minimize the number of PMUs installation subject to full network fault observability at the power system buses. The effectiveness of the proposed method is verified by the simulation of the IEEE14-bus.

**Key-words:** Power grid, Protection System, digital filter, PMU, Placement, Teaching Learning optimization, smart grids, observability, phasors, wide area measurement systems, IEEE-bus systems.

### خلاصة

في الوقت الحاضر ، يمكن استخدام وحدات قياس (PMU) لتعزيز حماية شبكة الطاقة بسبب مرونتها وأمنها وخواص اعتماديتها . يعتمد قرار المرحل الوقائي الرقمي بشكل كبير على ترشيح الإشارة الرقمية لحساب القيم الأساسية للتوترات والتيارات. ومع ذلك ، خلال حالة عابرة ، قد يشمل التيار والجهد مكونات غير مرغوب فيها مثل المكونات المستمرة DC المتحللة بشكل أسي المرتبطة، التوافقيات والتوافقيات الفرعية وخاصة في الشبكة الذكية. تحتاج الخوارزميات الرقمية المستخدمة دائمًا إلى بعض الدورات للحصول على القيم الأساسية الدقيقة للجهود الفولتية والتيارات sors وهذا غير مرغوب فيها في مجال الحماية. يتمثل المنهج الأول المقترح في هذا البحث في خوارزمية تقدير موثوق للطور لإزالة إشارات الاضطراب باستخدام مرشح رقمي محسن ( ODF) وخوارزمية تقدير موثوق للطور لإزالة إشارات عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية التي تم الحصول عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية والتيارات عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية إلى التي تمار تعاري ال عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية إلى المكونات عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية بالإضافة إلى المكونات عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية بالإضافة إلى المكونات عليها على الخصائص المطلوبة لإزالة مكون التيار المستمر وتفريغ المكونات التوافقية الفرعية بالإضافة إلى المكونات

في هذه الرسالة البحثية ، تم استخدام تحليل السبب الجذري المستند إلى تحليل الشجرة الصدئة لتحديد الأسباب الأولى والسبب الجذري للإنقطاعات الخاطئة لترحيل الحماية التي قد تؤدي بالتتالي إلى التعتيم التام للشبكة. وبمجرد تحديد الأسباب الجذرية الحرجة ، تم استخدام تدابير التخفيف التقليدية أو لأ ثم تم اقتراح وظائف الحجب والمرشحات الرقمية من أجل زيادة موثوقية نظام الحماية المدروس.

كما اكتسب وضع PMUs في أنظمة نقل الكهرباء الكثير من الاهتمام لتعزيز السيطرة وكذلك مخطط الحماية. في هذا البحث ، تم اقتراح خوارزمية تحسين القائمة على التعليم الثنائي (BTLBO) من أجل الوضع الأمثل لوحدات قياس PMUs. تم صياغة المشكلة المثلى لوضع وحدات PMU لتقليل عددها اللازم لمراقبة الشبكة بالكامل وقد تم التحقق من فعالية الطريقة المقترحة من خلال محاكاة الأنظمة IEEE14-bus.

كلمات مفتاحيه : شبكة الكهرباء ، نظام الحماية ، المرشح الرقمي ، وحدة إدارة المشروع ، التنسيب ، تحسين التعلم التعليم ، الشبكات الذكية ، إمكانية الملاحظة ، أنظمة قياس الواسعة ، أنظمة والعلم .

#### Résumé

De nos jours, les unités de mesure Phasor (PMU) peuvent être utilisées pour améliorer la protection du réseau électrique en raison de leurs propriétés de flexibilité, de sécurité et de fiabilité. La décision du relais de protection numérique dépend fortement du filtrage numérique des signaux pour le calcule des phaseurs fondamentaux des tensions et des courants de ligne. Cependant, pendant un régime transitoire, le courant et la tension de ligne peuvent inclure des composants indésirables tels que la composante DC décroissance exponentiellement, harmoniques et aux sous-harmoniques, en particulier dans les réseaux intelligents. Les algorithmes numériques utilisés ont toujours besoin de quelques cycles pour obtenir avec la précision requise les phaseurs fondamentaux. Ceci engendre par conséquent un temps de retard au traitement de l'information non souhaitable dans le domaine de la protection. La première approche proposée dans ce travail de recherche est le développement d'un algorithme fiable pour l'estimation des phaseurs en supprimant les signaux de perturbation à l'aide d'un filtre numérique optimisé (ODF) et d'un

algorithme DFT. L'algorithme d'extraction des phaseurs ainsi obtenu possède les caractéristiques requises pour éliminer la composante DC et atténuer les composantes harmoniques ainsi que les sous-harmoniques des signaux acquis par les circuits de mesure. Les performances du relais numérique développé sont testées en utilisant des signaux de test de perturbation estimés ou par application de signaux générés obtenus à partir d'un simulateur de réseau compensé par condensateur commuté commandé par thyristor (TCSC) qui a été développé à cet effet. Dans cette thèse de recherche, l'analyse des causes principales basée sur l'analyse des arbres de défaillances est utilisée pour identifier les perturbations en premier lieu et en second lieu de trouver la cause derrière les faux déclenchements des relais de protection qui peut conduire à une cascade de pannes et l'arrêt total du réseau. Une fois les causes critiques identifiées, des mesures d'atténuation conventionnelles ont d'abord été utilisées, puis des fonctions de blocage et de déblocage et des filtres numériques en vue d'accroître la fiabilité du système de protection considéré sont proposés.

Le placement d'unités de mesure de phaseurs (PMU) dans les systèmes de transmission électrique a également beaucoup attiré l'attention des spécialistes pour améliorer le contrôle ainsi que le système de protection. Dans ce travail de recherche, un algorithme d'apprentissage basé sur l'apprentissage binaire (BTLBO) pour le placement optimal des unités de mesure de phaseurs (PMU) est proposé. Le problème de positionnement optimal du PMU est formulé pour minimiser le nombre d'installations de PMU en vue d'une observabilité totale des bus du réseau. L'efficacité de la méthode proposée est vérifiée par simulation sur les systèmes IEEE 14 bus.

**Mots clés:** Réseau électrique, Système de protection, filtre numérique, PMU, Placement, Optimisation de l'apprentissage de l'enseignement, réseaux intelligents, observabilité, phaseurs, systèmes de mesure étendus, systèmes de bus IEEE.

Ш

#### ACKOWLEDGEMENTS

My first thanks go to my God, and secondly my sincere thanks go to my supervisor Pr. H. Bentarzi at IGEE for his technical and tireless support, fruitful discussions, scientific criticisms and helpful suggestions.

My profound appreciation goes to the jury members; Pr. BENAZZOUZ Djamel, Pr. KARA Kamel and Pr. MELIANI Hamza, who accepted to evaluate this modest work.

I wish to acknowledge IGEE staff for providing support and suitable environment. Besides, I would like to extend thanks to all colleagues at IGEE and particularly to A. Ouadi, A. Recioui and R. NAMANE for their meaningful comments and valuable suggestions.

Finally, this acknowledgement will not be complete if I do not extend the most sincere thanks to my family members (my wife in particular) for their support and encouragement, the patience they have shown throughout this work.

# Thesis outline

| Abstract     |                                                                       | Ι   |

|--------------|-----------------------------------------------------------------------|-----|

| Acknowledg   | ment                                                                  | III |

| List of symb | ols                                                                   | XI  |

| Chapter1     | Introduction                                                          | 1   |

| 1.1          | Context                                                               | 1   |

| 1.2          | Importance of measurement in protective relays enhancement            | 3   |

| 1.3          | Reliability Analysis and Testing System for Protection<br>Enhancement | 4   |

| 1.4          | PMU placement Optimization                                            | 6   |

| 1.5          | Research objectives                                                   | 7   |

| 1.6          | Thesis Organization                                                   | 8   |

| 1.7          | Publications List                                                     | 9   |

| Chapter2     | Disturbances Effects on SynchroPhasor Measurement and<br>Protection   | 10  |

| 2.1          | Introduction                                                          | 11  |

| 2.2          | Disturbances                                                          | 13  |

| 2.3          | Synchrophasor Measurements                                            | 24  |

| 2.4          | Disturbances Effects on Protection                                    | 38  |

| 2.5          | Disturbances Mitigation Techniques                                    | 39  |

| 2.6          | Phasor Algorithm using Fourier filter evaluation                      | 44  |

| 2.7          | Conclusion                                                            | 51  |

| Chapter3     | Protection System Reliability Analysis                                | 52  |

.

| 3.1      | Introduction                                   | 53 |

|----------|------------------------------------------------|----|

| 3.2      | Distance relay                                 | 57 |

| 3.3      | Root Cause Analysis                            | 59 |

| 3.4      | Relaying System Reliability                    | 61 |

| 3.5      | Distance Relay Reliability Enhancement         | 63 |

| 3.6      | Conclusion                                     | 68 |

| Chapter4 | Protective Relay Evaluation and Testing System | 69 |

| 4.1      | Introduction                                   | 70 |

| 4.2      | Testability                                    | 71 |

| 4.3      | Tester Implementation                          | 72 |

| 4.4      | Hardware Part                                  | 75 |

| 4.5      | Performance Evaluation of the Tester           | 76 |

| 4.6      | Conclusion                                     | 78 |

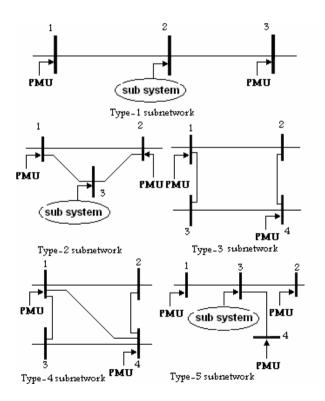

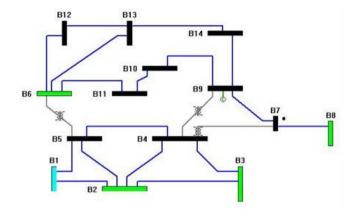

| Chapter5 | PMU Placement Optimization                     | 80 |

| 5.1      | Introduction                                   | 81 |

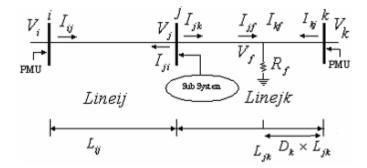

| 5.2      | Fault Analysis using PMUs                      | 82 |

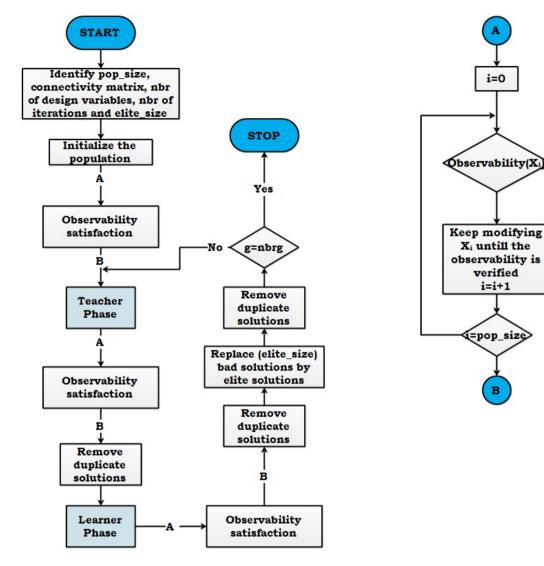

| 5.3      | BTLBO Optimization Algorithm                   | 86 |

| 5.4      | Simulation results and discussion              | 90 |

| 5.5      | Conclusion                                     | 92 |

| Chapter6 | Conclusions                                    | 93 |

|          | References                                     | 97 |

# List of Acronyms and Symbols

| ADC                             | Analog/Digital Converter                           |

|---------------------------------|----------------------------------------------------|

| BS                              | Blocking Scheme                                    |

| СВ                              | Circuit Breaker                                    |

| СТ                              | Current Transformer                                |

| D                               | Dependability                                      |

| DAC                             | Data Acquisition Card                              |

| DFT                             | Discrete Fourier Transform                         |

| DSP                             | Digital Signal Processing                          |

| FACTS                           | Flexible Alternating Current Transmission System   |

| FCDFT                           | Full Cycle DFT                                     |

| HCDFT                           | Half Cycle DFT                                     |

| HRC                             | High Rupturing Capacity                            |

| HV                              | High Voltage                                       |

| I <sub>2h</sub>                 | Second harmonics of the operating current,         |

| I <sub>3h</sub>                 | Third harmonic of the operating current            |

| I <sub>mpu</sub>                | Minimum pickup current                             |

| I <sub>op</sub>                 | the fundamental component of the operating current |

| I <sub>rt</sub>                 | unfiltered restraint current                       |

| k <sub>1</sub> , k <sub>2</sub> | constant coefficients                              |

| N <sub>e</sub>                  | total number of events of disturbances             |

| N <sub>f</sub>                  | Number of Failures to operate                      |

| N <sub>i</sub>                  | Number of incorrect trips (false trip),            |

| NSC                             | Negative Sequence Compound                         |

| N <sub>t</sub>                  | total number of trips                              |

| ODF                             | Optimized Digital Filter                           |

|                                 |                                                    |

| OLTC                                                                         | Over Load Tap Changer                                                                                                                                                                                           |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDC                                                                          | Phasor Data Concentrator                                                                                                                                                                                        |

| PDT                                                                          | Probability of occurrence of disturbances leading to tripping                                                                                                                                                   |

| PF                                                                           | Post Fault                                                                                                                                                                                                      |

| P <sub>ft</sub>                                                              | False trips causes' probability                                                                                                                                                                                 |

| P <sub>in</sub>                                                              | Input power                                                                                                                                                                                                     |

| PLC                                                                          | Programmable Logic Controller                                                                                                                                                                                   |

| PMU                                                                          | Phasor Measurement Unit                                                                                                                                                                                         |

| P <sub>out</sub>                                                             | Output Power                                                                                                                                                                                                    |

| PQA                                                                          | power quality analyzer                                                                                                                                                                                          |

| PS                                                                           | Power Swing                                                                                                                                                                                                     |

| PS                                                                           | Power System                                                                                                                                                                                                    |

| PSB                                                                          | Power Swing Block                                                                                                                                                                                               |

| PT                                                                           | Potential Transformer                                                                                                                                                                                           |

|                                                                              |                                                                                                                                                                                                                 |

| P <sub>un</sub>                                                              | Probability of occurrence of disturbances leading to unnecessary tripping                                                                                                                                       |

| P <sub>un</sub><br>R                                                         | Probability of occurrence of disturbances leading to unnecessary tripping<br>Reliability                                                                                                                        |

|                                                                              |                                                                                                                                                                                                                 |

| R                                                                            | Reliability                                                                                                                                                                                                     |

| R<br>ROCOF                                                                   | Reliability<br>Rate of Change Of Frequency                                                                                                                                                                      |

| R<br>ROCOF<br>RS                                                             | Reliability<br>Rate of Change Of Frequency<br>Relay System                                                                                                                                                      |

| R<br>ROCOF<br>RS<br>RTU                                                      | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit                                                                                                                              |

| R<br>ROCOF<br>RS<br>RTU<br>RWG                                               | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group                                                                                                       |

| R<br>ROCOF<br>RS<br>RTU<br>RWG<br>S                                          | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group<br>security                                                                                           |

| R<br>ROCOF<br>RS<br>RTU<br>RWG<br>S<br>S <sub>e</sub>                        | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group<br>security<br>existing security                                                                      |

| R<br>ROCOF<br>RS<br>RTU<br>RWG<br>S<br>Se<br>SEL                             | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group<br>security<br>existing security<br>Schweitzer Engineering Laboratories, Inc.                         |

| R<br>ROCOF<br>RS<br>RTU<br>RWG<br>S<br>S<br>S<br>E<br>L<br>SLP               | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group<br>security<br>existing security<br>Schweitzer Engineering Laboratories, Inc.                         |

| R<br>ROCOF<br>RS<br>RTU<br>RWG<br>S<br>S<br>S<br>E<br>L<br>S<br>LP<br>S<br>n | Reliability<br>Rate of Change Of Frequency<br>Relay System<br>Remote Terminal Unit<br>Relay Working Group<br>security<br>existing security<br>Schweitzer Engineering Laboratories, Inc.<br>Slop<br>new security |

### IGEE/UMBB

| ΤΤ         | Grounding system Type |  |

|------------|-----------------------|--|

| TVE        | Total vector error    |  |

| UBS        | Un-Blocking Scheme    |  |

| Фм         | Steady state Flux, Wb |  |

|            |                       |  |

| UP         | Unknown Phenomenon    |  |

| Фм         | Steady state Flux, Wb |  |

| <b>•</b>   |                       |  |

| $\Psi_{R}$ | reminisce Flux, Wb    |  |

## **Chapter 1**

## Introduction

#### 1.1 Context

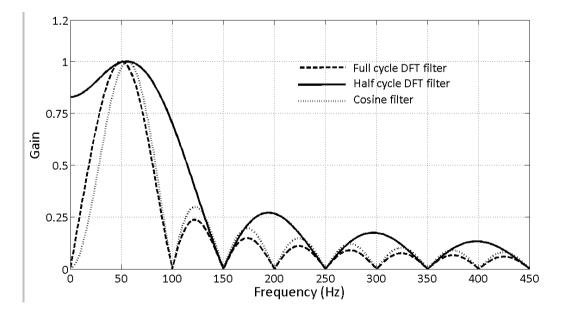

In latest years, electrical power technology throughout the world is quickly developed, which leads to smart power grid where some modern components may be used such as the thyristor-controlled switched capacitor (TCSC) compensated lines [1]. However, some transient disturbances may be produced in a transmission line, such as a DC offset, harmonics and sub-harmonics. These transient disturbances may cause negative effects on the measurement of currents and voltages and hence on the control and protection schemes in the power grid. Since there is a much likelihood that some failures may occur due to disturbances neither evaluated by simulation nor field tested under unforeseen measurement conditions of the system. This may occur in particular in a smart power grid that is interconnected with different types of energy sources, including new type of flexible alternating current transmission (FACT) devices having nonlinear elements and complex controlling functions. Improvement in measurement reliability for non predicted disturbance having a requested accuracy in digital relaying and control systems can be obtained through designing a bandpass filter to reject undesired signal components. One of approaches proposed in this research work for reliable phasor estimation algorithm first removes disturbance signals using designed digital filter then use HCDFT or FCDFT algorithm to compute phasors with required accuracy and convergence speed. The digital filtering design issue based on optimization approach is aimed to achieve different perspectives. The first point of view is to develop a unified accurate phasor measurement algorithm that immunes nearly all disturbances in power grid, (including other type of FACT devices) by introducing considerable and different kind of waveform distortions affecting on both line voltage and current signals, simultaneously with required speed of convergence. However, only the line current waveform distortion filtering is of concern and considered in this work. The second point focuses on reducing the computational resources and algorithm complexity through designing recursive digital filter with reduced order.

Since the functional security of the power system depends upon the successful operation of the thousands of relays that may be used in these schemes for preventing the power grids from cascading abnormal operations and failures. The failure of one relay of these systems to operate as intended may jeopardize the stability of the entire power grid and hence it may lead the whole blackout. In fact, major power system failures after a transient disturbance appearance are more likely to be caused by unnecessary protective relay tripping rather than by the failure of a relay to take action. In other words, the performance of protective relay or system is measured by several criteria including reliability, selectivity, speed of operation, etc. However, reliability which has two aspects: dependability and security is very important especially in smart power grid. Dependability is a degree of certainty that the protective relay will operate correctly when there is a fault in the power system. However, security relates to the degree of certainty that the protective relay or scheme will operate unnecessary when there is transient distribution in the power grid. Thus, appropriate relay testing provides a first defense against relay mal-operations and hence improve power grid stability and prevent catastrophic bulk power system failures. Relay testing can help to validate the design of relay logic, compare the performance of different relays, verify relay settings, identify system conditions that might cause unintended relay operation, and carry out post-event analysis to understand the causes of unintended or incorrect relay actions. Relay testing system improvements need to continue because of the use of relays in smart power grids where the conditions that are not the same as in the conventional power system.

Placing the PMU at every substation would certainly provide all the necessary realtime voltage magnitudes and angles for full system observability. However, by knowing a bus's voltage magnitude and angle, all current phasors, and the connecting line parameters, then all connecting bus voltages and angles can be calculated. This significantly reduces the number of PMUs (and therefore cost) needed for complete observability. Engineers and mathematicians have developed many algorithms to determine the best PMU locations for observability of the whole power system. To be practical, a PMU strategy should aim for full observability (depends on the nature of power system topology and system configuration). Research work [2,3] estimated that for a real system, PMUs are required to be on a minimum of 1/5th-1/4th (20-30%) buses to achieve full system observability.

#### 1.2 Importance of measurement in protective relays enhancement

An accurate and fast measurement of the phasors of the fundamental components (current and voltage) and frequency may be required in an intelligent, flexibly controllable power grid. This high quality of measurement may be obtained using of a Phasor measurement unit (PMU) that is very important in modern power grid instrumentations/meters, digital relays, control apparatus, and power quality analyzer (PQA). In such PMU instrumentation or digital relay, Discrete Fourier Transform (DFT) is the most widely used filtering algorithm [4, 5] for computing the fundamental components and frequency. However, lines currents disturbances in a transmission line may contain a dc offset which decays exponentially, and/or a large number of unwanted significant harmonics and sub-harmonics. Besides, the thyristor-controlled switched capacitor (TCSC), which may be used to enhance and optimize the use of the transmission network facilities, may generate this decaying dc components and harmonics [6]. This latter always needs few cycles (10-20 cycles) for obtaining accurate fundamental phasors by DFT algorithm. Such waveform distortion caused by the insertion of TCSC, may affect the reliability of digital protective relays and may cause relays to operate improperly. In most cases, the waveform distortion of the load current has little effect on the lines current disturbances. However, for low magnitude disturbances, the load may consist of a large part of the load current and distortion can become a significant factor. Since the relay must function properly even with distorted load currents [7]. This underlines the importance of a good quality measurement. Moreover, protective relays must easily discriminate among fault, normal and transient abnormal conditions when power quality is good. When power quality is poor in such grid including TCSC, the threshold between normal and transient fault conditions becomes imprecise. In the relaying application, engineers can no longer rely on the performance of the relay under conventional normal system conditions. However, under conditions of poor power quality especially in the smart grid case, they have improved the relay performance by designing

filters which in turn make the relay more secure and dependable. In several cases, transmission line protective relays have undesirably operated in response to harmonics or dc offset in the power grid.

#### 1.3 Reliability Analysis and Testing System for Protection Enhancement

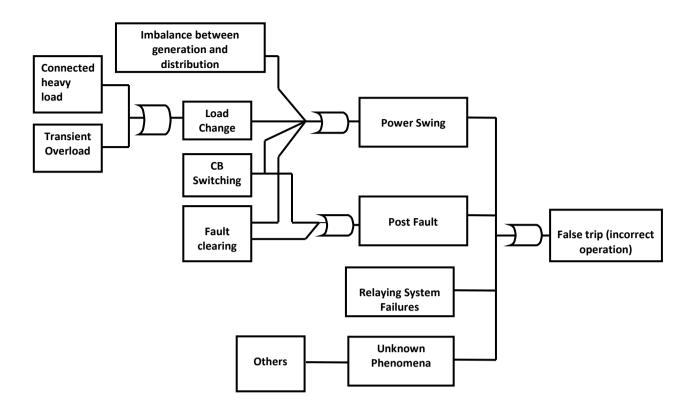

A Cigré study found that 27 % of bulk power system failure (blackout) resulted from false trips of protection system. Besides, an analysis of 17 years data provided in NERC reports revealed that 63% of major disturbances are protection related protective relaying which suffers from two types of problem: false trip (unnecessary tripping) and fail to operate [8-10].

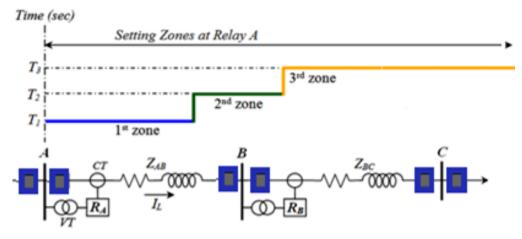

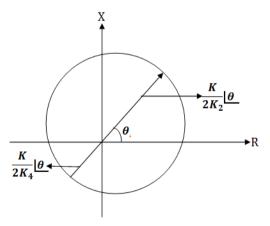

The mal-operation of this relay is generally due to not only unnecessary tripping during power swing that reduces the security of protection system and hence its reliability but also unnecessary blocking when symmetrical fault occurs accompanying a power swing [11]. This latter action may affect the dependability of the relay and hence its reliability. Many techniques have been developed to unblock the operation of the relay during power swing associated with a fault condition such as a negative sequence current magnitude and a derivative of current angle [12], and a combination of waveform of swing center's voltage (WSCV) and synthetic negative vector [13]. A more advanced new blocking and unblocking function based on power swing detector using Phasor Measurement Units (PMUs) has been proposed [11,14,15]. In addition to the local phasors information, the proposed scheme uses remote phasors information from different locations for power swing detection, which can be provided at high speed by PMUs. These measurements are used for calculating the apparent power absorbed by power line and the difference in phase angles of voltages that may be used for detecting power swings and faults. Hence, the proposed scheme blocks tripping signal during the power swing and unblocks it during fault condition.

Major power system disturbances are more likely to be caused by unnecessary tripping rather than by the failure of a relay to take action [10]. In fact, a major cause of power system instability is due to the relative long time delay for fault clearance of zone three backup relays. In order to overcome the drawbacks of these relaying systems, many techniques have been developed such as a blinder that blocks the relay to operate during the power swing [11].

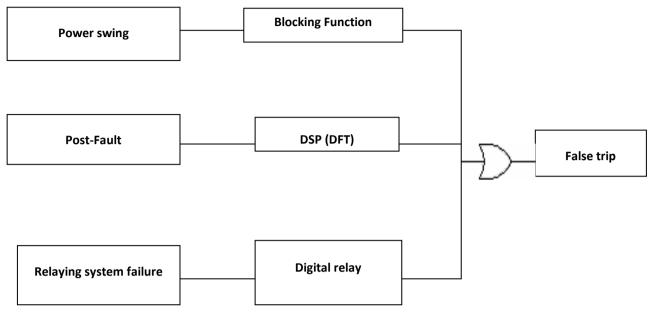

#### 1.3.1 Reliability Analysis

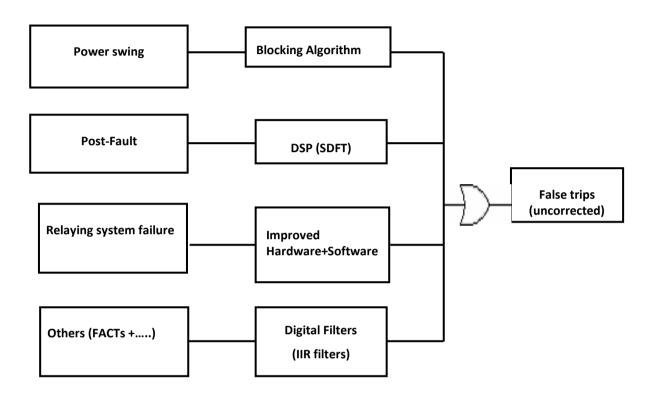

In this research work, Root Cause Analysis based on fault tree analysis is used to identify disturbances first and root cause of false trips of a protective relay which may lead in cascading to blackout. Once the critical root causes are identified, conventional mitigation measures have been used first and then blocking and unblocking functions and digital filters in view of increasing the reliability of the considered protection system are proposed. Previous works [1, 16] proposed some efficient solutions (based mainly on using digital filters) to obtain accurate and disturbance-free phasor measurements. As a result, the reliability of the measuring block of the protection system has been significantly improved. However, this improvement concerns the reliability of one part (the phasor measurement block) of the protection system. In the present work the reliability of the global protection system is considered. This new approach has many advantages compared to those published in previous works as it allows obtaining an important quantitative figure (security). This permits to selectively reinforce the elements of the protecting system which are most likely apt to failure and hence the impact on the overall system's cost is significant. Another main advantage is that unlike former works, our approach takes also into account the reliability of the software part of the system which is considered to have a significant contribution in the overall reliability of the protecting system.

#### 1.3.2 Protective Relays Testing Systems

Appropriate relay testing is very important to reduce relay false-tripping rate. Relay testing can aid to confirm the design of relay, compare the performance of different relays, verify relay settings, classify system conditions that might cause unplanned relay operation, and carry out post-event analysis to understand the causes of unintentional or incorrect relay actions. Relay tester enhancements need to continue because of the use of relays in smart power grids where the conditions that are not the same as in the conventional one. A Relay Tester should be able to emulate in laboratory most of disturbances that may appear in real operating conditions.

Disturbances include transient distortion in the voltage due to post fault, potential transformer saturation or compensator switching may affect on transmission line relays and relaying systems in various ways. The mal-operation of this relay is generally unnecessary tripping during post fault or compensator connection which produces DC offset and harmonics. This may reduce the security of protection system and hence its reliability.

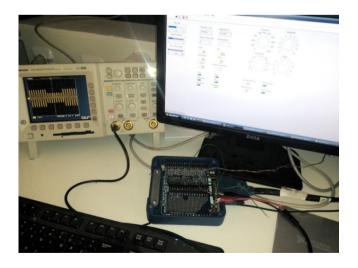

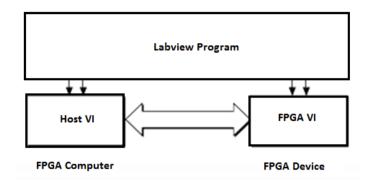

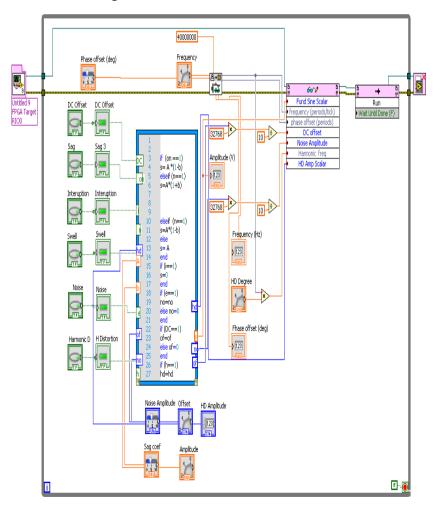

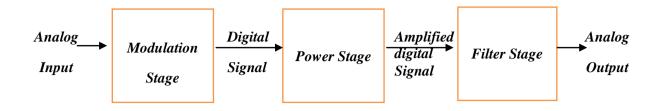

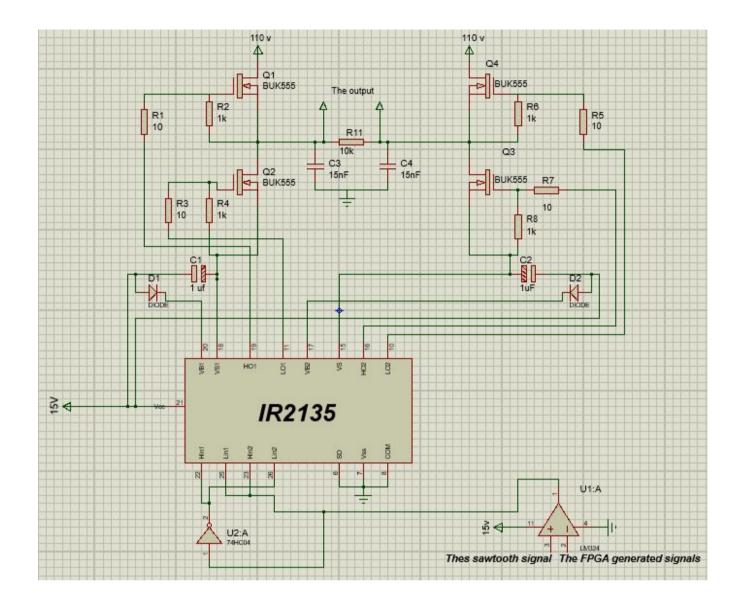

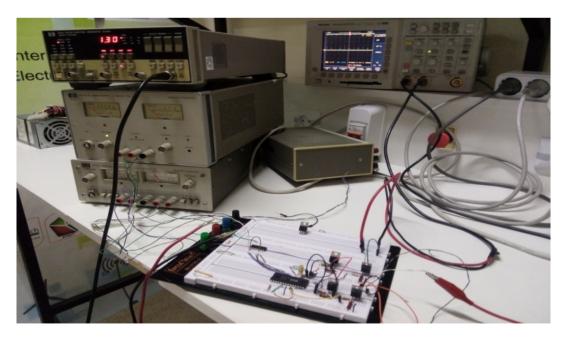

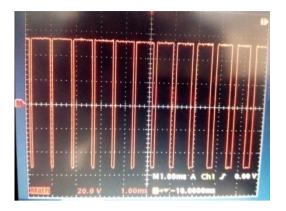

This part focuses mainly on the design and the implementation of the Class D amplifier which is the amplification part of the testing system. The Class D amplifier has been used in this work to amplify the simulated disturbances that are generated by Simulink power system model to be then injected to the protective relay and monitor its response. Labview has been used for developing the graphical user interface and controlling the NI 7851Board

We have used new technology that allow designing an enhanced relay testing system which in turn can be used for improving the performance of protective relay. In order to test both security and dependability and hence the reliability, this work propose a new frame work of tester based on FPGA associated with a NI (National Instruments) acquisition card.

#### 1.4 PMU placement Optimization

Installing PMUs for full system observability is a large investment. The strategy used needs to be practical, adaptable, and cover the entire process from preparation to installation schedule. Three steps such as placement model, placement algorithm, and phased installation in order to cover the entire process.

-The placement algorithms such Spanning Tree based on graph theory developed by Reynaldo Nuqui [2] and Integer Programming developed by Ali-Abur [3] require a list of busses, a list of branches or incidence matrix, and a list of which busses have injection. The placement algorithms do not take into account physical locations, component states, or the number of transformers in a substation. Thus the person running the placement algorithm must interpret the real system into a very simplified format, determining what exactly qualifies as a bus and how to modify existing models for certain situations. -The integer programming method can work very well and fast. The amount of result variance and run time will depend on the specific algorithm used by the optimization toolbox.

-Installation Schedule: In reality however, fully observable placement sets may not be immediately attainable or even necessary at all. By preparing an implementation schedule that takes observability into account, the PMU planner can make the most of the available PMUs long before full observability is reached.

Even when the goal is to attain full observability, it is unlikely that a system owner will purchase and install all the PMUs at once. This large investment will likely be spread out over several years by installing a subset of the PMUs each year in steps or phases. How to choose which PMU locations selected in each step should depend on the operator's most urgent need and gradually increasing the overall observability with each phase.

In this research work, a binary teaching learning based optimization (BTLBO) algorithm for the optimal placement of phasor measurement units (PMUs) is proposed. The optimal PMU placement problem is formulated to minimize the number of PMUs installation subject to full network observability at the power system buses. The effectiveness of the proposed method is verified by the simulation of IEEE14-bus.

#### 1.5 Research objectives

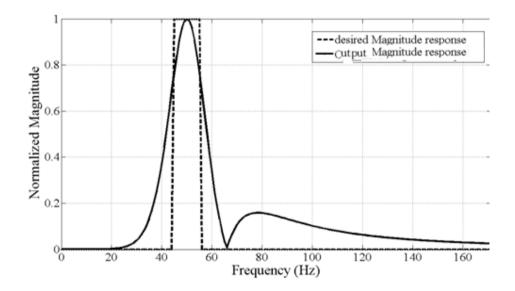

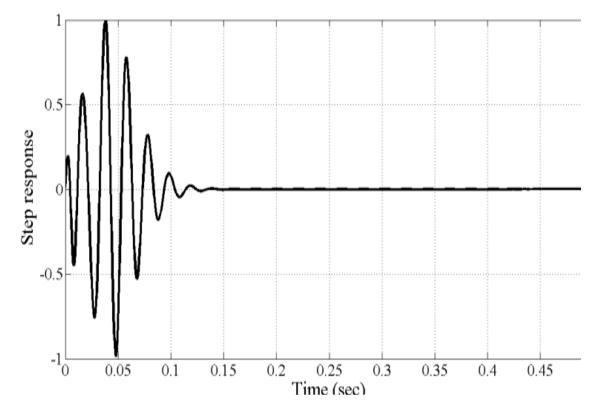

The first objective of this research is to develop an approach for reliable phasor estimation algorithm for removing disturbance signals using optimized digital filter (ODF) and DFT algorithm. The developed phasor algorithm may have the required characteristics to remove the dc component and dump the harmonic as well as sub-harmonic components. The performance of the developed digital relay may be tested using estimated disturbance test signals or generated signal obtained from the simulator of thyristor-controlled switched capacitor (TCSC) compensated power system network that has been developed for this purpose. An optimization technique is used for the design of digital filter with simultaneous objective functions. The discrete time transfer function of the desired recursive digital filter is first developed. The second step of the design, an error function between the desired ideal response and the desired filter transfer function is formulated. A norm of the error function is minimized by changing the practical filter coefficients considered as optimization design variable. A compromise or a trade-off between the different objective function must be made to satisfy filter design. The combined optimized digital filter (ODF) and DFT algorithm are therefore successfully used to quickly and accurately calculate the phasors. Moreover, the obtained phasor algorithm has the required characteristics to remove the dc component and dump the sub-harmonic as well as harmonic components. The phasor filter dynamic performances are tested using either data obtained from simulated network faults and specific test signals including undesired components. To assess the phasor Measurement filter, several indices have been used to evaluate the performances of the designed filter.

The second objective of this research thesis is first to perform Root Cause Analysis based on fault tree analysis for identifying disturbances first and then to study root cause of false trips of a protective relay which may lead in cascading to blackout. Once the critical root causes are identified, conventional mitigation measures have been used first and then blocking and unblocking functions and digital filters in view of increasing the reliability of the considered protection system are proposed.

The third objective of the research work is the placement of phasor measurement units (PMUs) in electric transmission systems for enhancing the protection scheme. In this research work, a binary teaching learning based optimization (BTLBO) algorithm for the optimal placement of phasor measurement units (PMUs) is proposed. The optimal PMU placement problem is formulated to minimize the number of PMUs installation subject to full network observability at the power system buses. The effectiveness of the proposed method is verified by the simulation of IEEE14-bus.

#### 1.6 Thesis Organization

The outlines of this thesis may be organized as follows. Chapter 2 deals with an extensive literature review of related research, especially in the areas of smart power grid, causes of disturbances and their effects on the measurement quality, measurement system based on digital filters and protection system based on synchronized phasor measurement. The study of the reliability of protective system is presented in Chapter 3 through the analysis of the power network with digital filters. The testing system that may be used for reliability evaluation is discussed in chapter 4. Chapter 5 presents the importance of the PMU placement optimization in power system is emphasized by a brief review. In addition, the

optimization techniques such as the teaching learning based optimization (TLBO) that is used for optimal PMU placement is discussed. A summary of the contributions, implications, and limitations of the study and future research directions is given in Chapter 6.

#### **1.7 Publications List**

The thesis is developed from the peer-reviewed journal and conference papers which are listed below.

- 1. H Bentarzi, A Zitouni, « Field-Programmable Gate Array Based Tester for Protective Relay », International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, Vol.11, N°7, pp. 791-796, WASET, 2017.

- 2. **Abdelkader Zitouni**, Abderrahmane Ouadi, Hamid Bentarzi, Mahfoud Chafai , "Distance relay reliability enhancement using false trip root cause analysis », Springer International Journal of System Assurance Engineering and Management, pp.1-9, 2018.

- 3. H. Bentarzi, A. **Zitouni**, "FPGA Based Tester for Protective Relay", 19th International Conference on Power Electronics and Power Engineering, ICPEPE Istanbul 2017.

- 4. Abdelkader **Zitouni**, Mahfoud Chafai; Hamid Bentarzi, Abderrahmane Ouadi, False Trip Root Cause Analysis and Mitigation in Electrical Power System Protection, International Conference on Production, Energy & Reliability (ICPER2016), 15 - 17 August 2016; Kuala Lumpur, Malaysia.

- H.Bentarzi, Abdelkader Zitouni, Ayache Mati, Abderrahmane Ouadi, Dependability and Security Enhancement of Distance Relay in Power System; International Conference on Production, Energy & Reliability (ICPER2016), 15 - 17 August 2016; Kuala Lumpur, Malaysia. <u>http://www.utp.edu.my/icper2016</u>

- 6. A. Zitouni, A. Ouadi, and H. Bentarzi, (2015) "Measurement Quality Enhancement using Digital Filter in Power Grid integrating TCSC", EPE2015, Kouty nad Desnou, Czech Republic, May 20 – 22 2015, (IEEE explorer) DOI: <u>10.1109/EPE.2015.7161175</u>..

- 7. Mahfoud Chafai, Hamid Bentarzi and A. **Zitouni**, PC based Testing System for Protective Relay, 4<sup>Th</sup> International Conference on Power Engineering, Energy and electrical drive (Power engineering), Istanbul, Turkey, may 13-17, 2013. (IEEE explorer)

- 8. H.BENTARZI, A. OUADI, M. CHAFAI and A. **ZITOUNI** "Distance Protective System Performance Enhancement Using Optimized Digital Filter", presented in The 10th WSEAS International Conference on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING (CSECS '11), Montreux University, Switzerland, December, 29-31, 2011. <u>URL:http://www.wseas.us/elibrary/conferences/2011/Montreux/MECHICSE/MECHICSE-15.pdf</u>

- **9.** A. OUADI, H.BENTARZI, M. CHAFAI and A. **ZITOUNI**, Microcontroller Based Protective Relay Testing System, The 10<sup>th</sup> WSEAS International Conference on CIRCUITS, SYSTEMS, ELECTRONICS, CONTROL & SIGNAL PROCESSING (CSECS '11), Montreux University, Switzerland, December, 29-31, 2011

## **Chapter 2**

# Disturbances Effects on Measurement and Protection

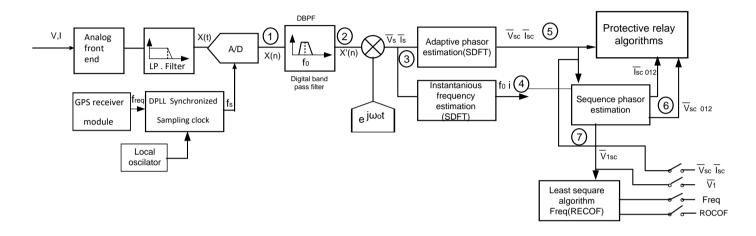

Measurements of the instantaneous amplitude and phase angle of the fundamental current or voltage components and frequency that may be needed in three-phase power grid instrumentations/meters and relays may be affected by several encountering disturbances. These disturbances may be due to an abrupt heavy load changes and post-faults resulting in frequency deviation, DC offsets decaying, and harmonics especially in the power grid including TCSC devices. To study these effects on the quality of measurements, this research work presents a new approach using the data generated by Simulink/MATLAB software. The obtained simulation results show that the unwanted DC offset and harmonics as well as sub-harmonics cannot be removed completely by conventional filters such as anti-aliasing and DFT filtering but they can be eliminated by inserting before DFT algorithm a digital filter.

#### **2.1 Introduction**

Power systems are the largest manmade dynamic system. They are highly nonlinear and involve complicated electromagnetic and electromechanical phenomena. To operate the system reliably and economically, system conditions may be monitored using voltages and currents phasors. So, an accurate and fast measurement of these phasors of the fundamental components (current and voltage) and frequency may be required in a power grid such as one. This high quality of measurement may be investigated through the use of a Phasor measurement unit (PMU) that is very important in an intelligent, flexibly controllable modern power system (smart grid) instrumentations/meters, digital relays, control apparatus, and power quality analyzer (PQA). In such PMU instrumentation or digital relay, Discrete Fourier Transform (DFT) is the most widely used filtering algorithm [4,5] for computing the fundamental components and frequency. However, lines currents disturbances in a transmission line may contain a dc offset which decays exponentially, and/or a large number of unwanted significant harmonics and sub-harmonics. Besides, the thyristor-controlled switched capacitor (TCSC), which may be used to enhance and optimize the use of the transmission network facilities, may generate this decaying dc components and harmonics [6]. This latter always needs few cycles (10- 20 cycles) for obtaining accurate fundamental phasors by DFT algorithm. Such waveform distortion caused by the insertion of TCSC, may affect the reliability of digital protective relays and may cause relays to operate improperly. In most cases, the waveform distortion of the load current has little effect on the lines current disturbances. However, for low magnitude disturbances, the load may consist of a large part of the load current and distortion can become a significant factor. Furthermore, the relay must function properly even with distorted load currents [5]. This can be achieved only by a good quality measurement. Moreover, protective relays can easily discriminate between fault and non-fault conditions when power quality is good. When power quality is poor, the threshold between normal and fault conditions becomes imprecise. In the relaying application, engineers can no longer rely on the performance of the relay under conventional normal system conditions. However, under conditions of poor power quality especially in the smart grid case, they have improved the relay performance by designing filters which in turn make the relay more secure and dependable. In several cases, transmission line protective relays have undesirably operated in response to harmonics or dc offset in the power grid.

From the obtained evaluation using the ideal network [6], the DC offset may have an effective impact on the Fourier algorithm and if no correction is taken on, the relative error of the real amplitude from the Fourier algorithm may attain 20%, which is mainly caused by this decaying dc offset. In SCADA and protection applications, such large relative error is not permissible. The performances of these techniques employed directly establish the functions of these systems and affect their behaviors under various service conditions. Hence, the real-time accurate phasor measurement of the fundamental component and/or symmetrical components is essential and crucial to the safe and economic running of smart electric power grid [5, 7, 8].

For an ac input signal that is associated with an exponentially decaying dc offset component, some authors [12] propose a modified Fourier filter algorithm using a data window of one cycle plus two samples to compute and perform compensation to remove the unwanted dc offset [9]. The idea behind this algorithm is that the decaying DC component can be completely removed from the original signal once its parameters are determined. The weakness of the previous algorithms is that more calculation is needed to eliminate the dc offset. Many other works can be found in the literature [10-14] devoted to remove the DC-component and associated unwanted signals.

Conventionally, static state estimation has been used to estimate the steady-state power and voltage magnitudes. However, for dynamic applications, measurements are time-skewed without a time reference. Digital computer based measurements; protection and control have become common features of electric power substations. These systems use sampled data to compute various quantities such as voltage and current phasors.

The advent of satellite-based time-keeping system, such as high accurate atomic clocks used in global position system (GPS), with lowest cost GPS receiver providing high precision timing sources, measurements are made with a common time reference, usually GPS clock. The advances of computer, synchronization and communication technologies have made synchronized phasor measurement in power system applications such as protective relay and phasor measurement unit (PMU) within 1µs. Even the measurements accomplished at various sites, are synchronized to each other using the same common time base. Synchronized phasors measurement set provides a vastly improved method for tracking power system dynamic phenomena. They facilitate a number of wide area applications including wide area measurement systems. (WAMS), a power system protection, monitoring and control applications such as wide-area measurement protection and control system (WAMPAC) which utilizes these measurements.

Stand alone phasor measurement units (PMU) have been used on critical systems, for providing synchronized phasor measurement data. They are only in developed countries because they are relatively expensive, this has conveyed some manufacturers to design modern protective relay includes phasor measurement function and capabilities. The addition of synchrophasor measurement in a protective relay results in increased power system reliability and provides easier disturbance analysis, protection, and control capabilities.

For phasor measurement, the discrete Fourier transform (DFT) algorithm is used to calculate the phasors providing the phasor magnitude and angle estimation. When the power system frequency is at off nominal frequency, the DFT phasors estimators are no longer accurate, and the frequency compensation algorithm based on the smart DFT algorithm is used to correct the phasors. The power system frequency is accurately estimated by using the least square algorithm based on instantaneous angles and frequency measurements obtained by the SDFT algorithm.

The phasor measurement is tested under different power system disturbances. This is due to the fact that power system voltage and current waveforms are not steady state sinusoids, particularly during system disturbances. They frequently contain sustained harmonic and nonharmonic components. In addition, because of faults and other switching action transients, there may be step changes in the magnitude and phase angles of the waveforms. Other disturbances are the relatively slow changes in phase angles and magnitudes due to oscillations of machine rotors during electromechanical disturbances. This chapter includes general background information about disturbances causes and their effects on measurements, synchro-phasor measurements technology and how to mitigate the harmonics and subharmonics that may be initiated in the smart grid.

#### 2.2 Disturbances

A Power transmission network plays a very important role in transporting and delivering power over a wide geographical area. Due to the rapidly increasing power demand and in order to drive the high voltage transmission lines up to the optimum limits, new methods have been developed to improve transmission line capacity. Transmission lines are included with FACT series compensated devices to increase the power transfer capability. However these FACT devices introduce nonlinearities in the power system transmission network and particularly during power system disturbances where the occurrences of faults are more likely and security of the supply became a critical issue. Therefore, it is necessary to study effects of FACTS devices on the power systems measurement quality in protective devices and PMUs during disturbances. Both voltage and current may contain a considerable exponentially decaying DC component, and significant harmonics in line voltages and sub-harmonic in line currents components. This causes significant error in voltage and current phasor determination as has been studied by many authors [12], [20-23] for a power system transmission line fault analysis.

#### 2.2.1 Series Compensator

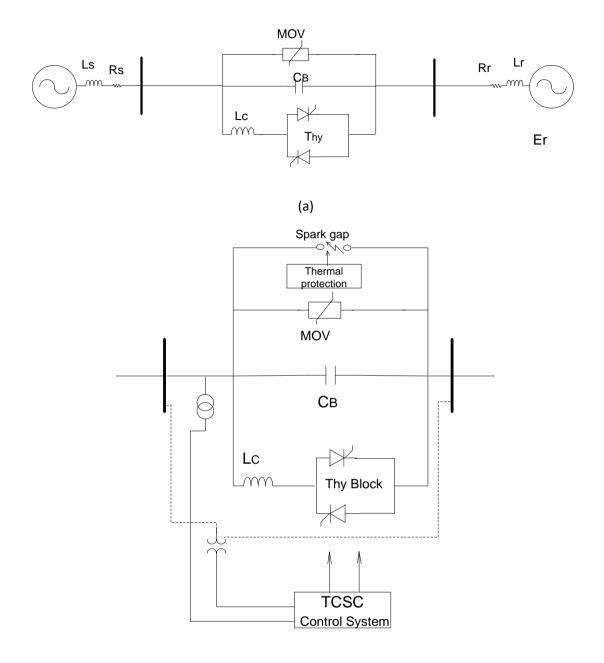

Among the actually known FACT devices are series compensated devices, which have been used successfully for many years to enhance stability and load capability for HV and EHV transmission networks. They work by inserting capacitive voltage to compensate for the inductive voltage drop in the line, i.e they reduce the effective reactance of the transmission line. Series compensation can be classified into switched capacitor systems and thyristor controlled switched capacitor (TCSC) systems. The Capacitors bank is installed in series with the transmission line as shown in Fig.2.1a, for a single phase diagram. On the same installation platform, the main capacitor is located together with TCSC controller. TCSC compensated scheme consists of controlled reactors in parallel with sections of capacitor banks, as illustrated in Fig.2.1b. A metal-oxide varistor (MOV) is connected across the capacitor to prevent capacitor overvoltage. Further, a bypass switch in parallel with gap automatically closes the abnormal circuit condition that causes prolonged current flow through the gap. A snuber circuit connected in series is used to limit the current that may flow through the air-gap switch. Also connected is an air-type induction with a thyristor which can be used to short-up or bypass the capacitor when a fault occurs. The TCSC can operate in two modes when a fault occurs.

#### (b)

Fig.2.1 Series compensated scheme used in transmission network: (a) Single circuit diagram of a capacitor bank used in transmission network, (b) TCSC compensated scheme.

a) **Blocking mode**: The TCSC will operate in blocking mode, where the thyristors are not triggered and the thyristors remain in non-conducting state. Line current passes through the capacitor bank only.

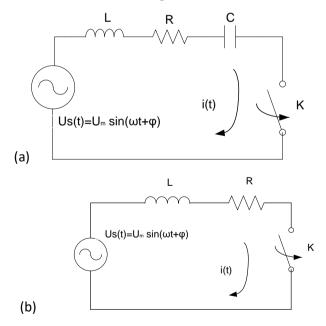

A primary overvoltage protection typically involves non-linear metal-oxide varistors, a spark gap with a snuber circuit. In this mode the MOV will conduct to limit the capacitor over voltage during the fault. If the overvoltage is frequently repeated, the energy dissipated by MOV grows and when reaching a certain threshold a spark gap, a fast switch, is activated to bypass the MOV and hence protect the MOV from overheating. During this mode, the power transmission network can be modeled as an RLC circuit, as shown in Fig.2.2-a, for short line consideration.

**b**) **Bypass mode** (Fig.2.2-b): During severe short circuit or high current, the thyristor controlled (TCR) reactor is connected by continuously triggering the thyristor switch that bypass the capacitor for conducting fault currents. The TCSC will behave like a parallel connection of the series capacitor bank and the inductor of the thyristor switch branch. The inductor whose purpose is to limit the rate of rise of current through the thyristor and to prevent resonance with the network (normally 6% with respect to Xc). The capacitor may be switched with a minimum of transients if the thyristor is turned on at the instant when the capacitor voltage and the network voltage have the same value. In this mode, the capacitor voltage is much lower than in the blocking mode.

Fig.2.2 Equivalent power transmission network model using TCSC: (a)- switched capacitor bank connected, (b)- switched capacitor bank bypassed by TCR

#### 2.2.2Fault Analysis

During a severe fault, the power system transmission can be modeled using the ideal network shown in Fig.2.2.b. It can be used to reveal how the source of the decaying DC offset that is induced in the current. In the network, the L or R is variable according to the power system operation conditions as well as the fault. If the switch k is closed at t=0, and through the use of the Kirchhof voltage law it leads to the following differential equation:

$$V_{\rm m}\sin(\omega t + \varphi) = {\rm Ri} + L\frac{{\rm di}}{{\rm dt}}$$

(2.1)

By solving Eq.(2.1), the fault current i(t) is given as follows:

$$i(t) = -\frac{V_{\rm m}e^{-\frac{R}{L}t}}{\sqrt{R^2 + (L\omega)^2}}\sin\left[\phi - \tan^{-1}\left(\frac{L\omega}{R}\right)\right] + \frac{V_{\rm m}}{\sqrt{R^2 + (L\omega)^2}}\sin\left[\omega t + \phi - \tan^{-1}\left(\frac{L\omega}{R}\right)\right]$$

(2.2)

The DC component needs 0.5 to 5 cycles for decaying. In the case where a relatively high short resistance, between phase and ground, the capacitor bank model takes place and the ideal network includes a series capacitor C, in addition to the RL model, as shown in Fig.2.2.a. This model can be used for the purpose of determining the power flow transfer, but also to analyze the transient switching for some fault, which is considered at once. During this mode, when a relatively high fault resistor ranging between  $10\Omega$  and  $200 \Omega$ , a slow decaying with sub-synchronous frequency will appear in transient fault current. This can be modeled by the following differential equation as:

$$U_{s}(t) = Ri + L\frac{di}{dt} + u_{c}(t)$$

(2.3)

For a heavily short circuits the capacitor are shorted, so the following are added to Eq.(2.3)

$$u_c(t) = 0, \quad i_c(t) = 0$$

(2.4)

The solution will be the same as given in Eq.(2.2). When the short is not severe, the capacitors bank are not bypassed, in addition to Eq.(2.3), the capacitor voltage should include following additional equation with initial condition as:

$$\begin{cases} u_{c}(t) = \frac{1}{c} \int_{t_{o}}^{t_{n}} i_{c}(t) dt + u_{c}(t_{o}) \\ i_{c}(t) = c \frac{du_{c}(t)}{dt} \end{cases}$$

(2.5)

By solving Eqs. (2.3) and (2.5) simultaneously, the fault current i(t) will be as follows:

$$i(t) = \frac{V_{m}}{\sqrt{R^{2} + \left(L\omega - \frac{1}{C\omega}\right)^{2}}} e^{-\frac{R}{2L}t} \sin\left(\omega_{n}t + \varphi - \tan^{-1}\left(\frac{R}{L\omega_{n}}\right)\right) + \frac{V_{m}}{\sqrt{R^{2} + \left(L\omega - \frac{1}{C\omega}\right)^{2}}} \sin\left(\omega t + \varphi - \tan^{-1}L\omega R\right)$$

$$(2.6)$$

Where,  $\omega_n = 1/\sqrt{LC}$ .

During this mode, when a relatively high fault resistor ranging between  $10\Omega$  and  $200\Omega$  a slow decaying with sub-synchronous frequency will appear in transient fault current.

In Eqs.(2.2) and (2.6), the first term is a transient decaying DC offset component that depends on the parameters R,  $L,\omega,\phi$  and Vm. The effect of this term has been evaluated and concluded that the DC offset may have a severe impact on the Fourier algorithm [7]. The relative error of the amplitude from the Fourier algorithm may reach 20% due to this decaying DC offset.

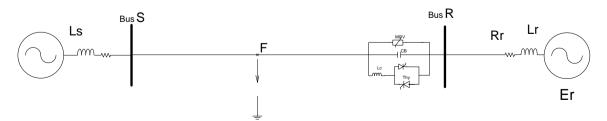

#### 2.2.3 Simulink M odel of Electrical Network integrating TCSC

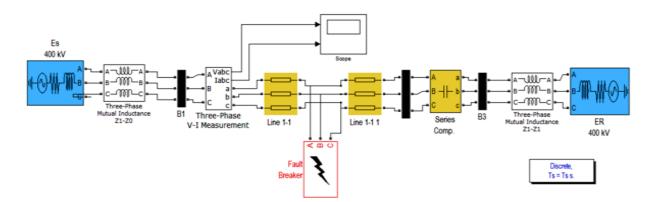

The power transmission lines circuit to be simulated as shown in Fig.2.3 with a base voltage of 400kV, and 50Hz frequency for a 300km distance compensated of 40% at the receiving end of the line. The PSB with Simulink simulator is used to simulate the power system components including a series capacitor compensator (TCSC) placed in the right end of the power line, as previously modeled, to evaluate and generate voltages and current before and after the fault. The related parameters of the simulation are given in table 2.I.

Fig.2.3 Studied Power system transmission including switched capacitor

| Elements    | Parameters        | Values                   |

|-------------|-------------------|--------------------------|

|             | Resistance        | 1.31 (Ω)                 |

| Sources     | Inductance        | <b>0.3008</b> (H)        |

|             | Frequency         | 50 (Hz)                  |

|             | R0 and R1         | 0.0275 and 0.0275Ω/km    |

| T.L.        | L0 and L1         | 3.3 and 0.1591 (mH/km)   |

|             | C0 and C1         | 8.5 and 13 (nF/km)       |

|             | R0 and R1         | <b>2.33 and 1.31</b> (Ω) |

| Receiver    | L0 and L1         | 0.0477 and 0.0847 (H)    |

|             | Reference voltage | 300 kV                   |

| Series Cap. | Reference current | 2 kA                     |

TABLE 2.I DIFFERENT ELEMENTS PARAMETERS OF POWER NETWORK

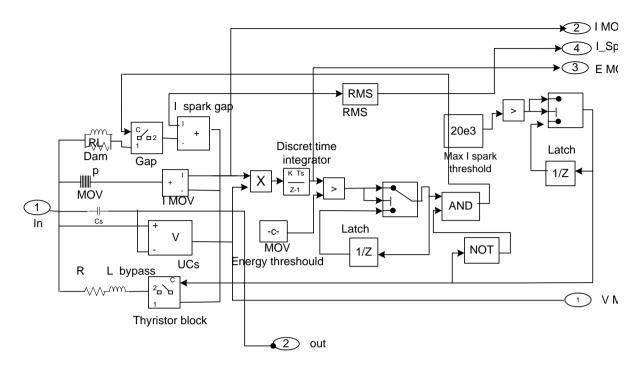

The power transmission network shown in Fig.2.3 includes a power transmission line connecting two generators at two busses S and R, and a TCSC line compensation system at the receiving end. A MATLAB/SIMULINK simulator associated with power system block set (PSB), are used to perform a time domain simulation of this power system network. The main components of the TCSC are modeled in this section, as required by the SIMULINK time domain solver, as follows: - the spark gap, and hence both the capacitor bank and the MOV, is protected when any unwanted spark over the spark gap. This is performed by measuring spark gap current continuously. This in turn is compared to a maximum current that the spark gap can withstand.

Figure 2.4 shows a simulation model of one phase compensator with protection block subsystem and its typical protection functions including the main protective elements and their appropriate models that have impact on transient behavior of the TCSC in its conventional operation. Several other protections functions are not considered to facilitate the simulation modeling, but they are essential for a correct operation of a hole TCSC as capacitor unbalance protection, line current supervision, MOV high temperature protection, MOV failure protection, flash over to platform protection, trigger circuit supervision, bypass breaker failure protection, thyristor overvoltage protection, thyristor thermal overload protection etc.

$Fig. 2.4 \ TCSC \ compensator-protection \ SIMULINK \ block \ component \ for \ one \ phase$

(from Simulink Power System Blockset documentation)

#### 2.2.4 Fault Simulation of the Power Network Integrating TCSC

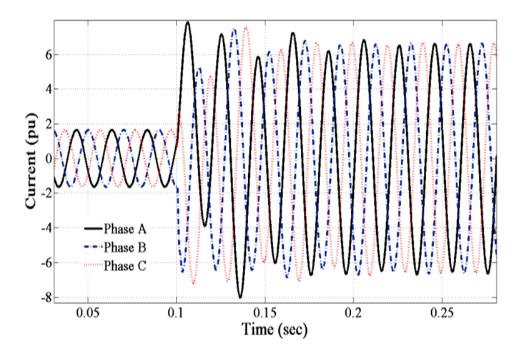

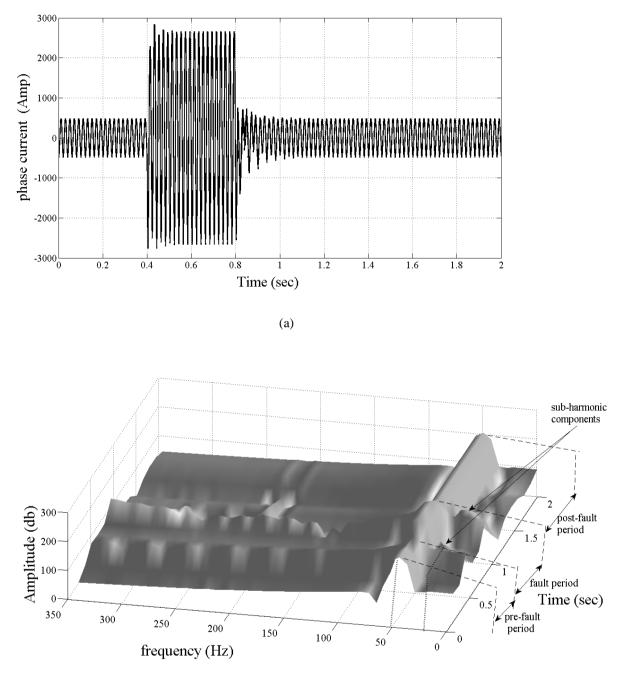

Two fault resistances are simulated as shown in Fig.2.5. The simulation results show that the faulted signals are associated with DC decaying signals, harmonic and sub-harmonic components. The voltage waveform is corrupted by harmonic components and fast decaying DC components for small resistance faults. The current waveform may be significantly affected, depending on the inception angle, by decaying DC components for small resistance faults. Besides, the sub-harmonic component may also be added in the case of the series compensated transmission line associated with relatively

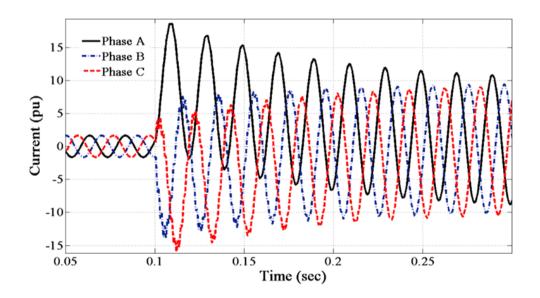

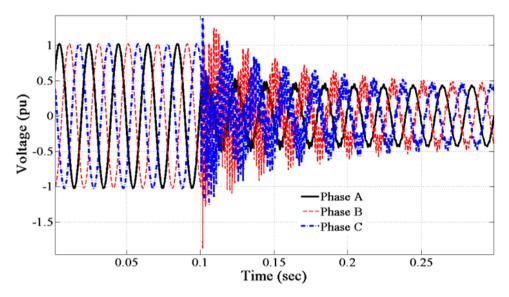

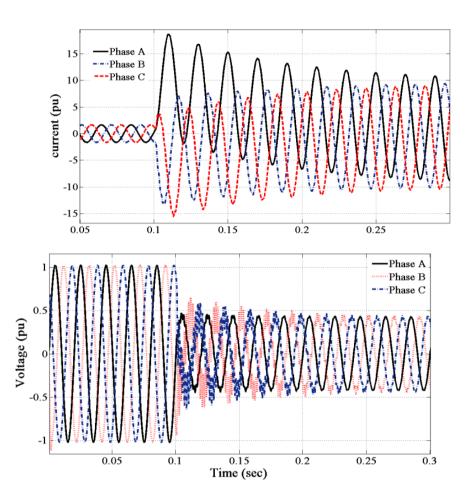

A line-to-ground fault is applied on phases A, B and C at t = 100ms. The sampling time Ts= 5.556 10<sup>-6</sup> s is used in the power system simulation (3600 samples per cycle) so that a down sampling process generates a 36 sample per cycle. The Simulink time domain solver generates the different voltage and current waveforms at the corresponding bus.

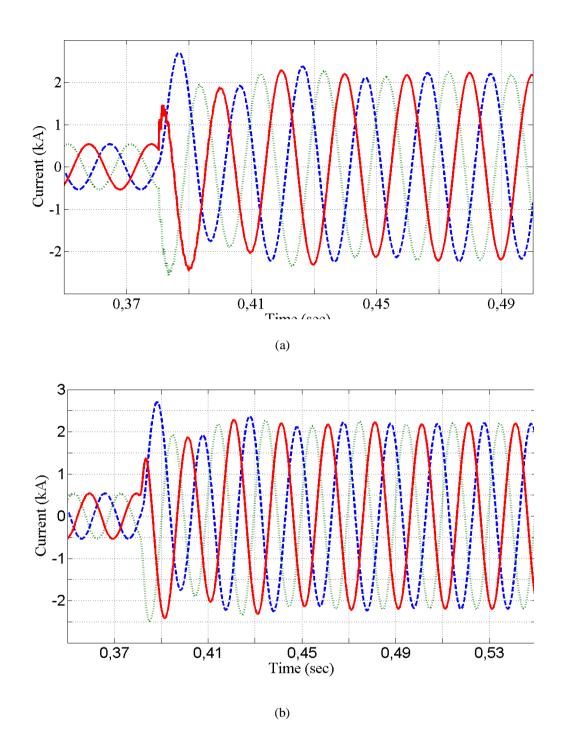

Fig.2.5 Simulink model of power network with TCSC

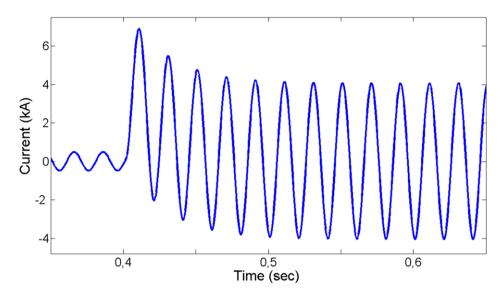

In order to show the DC decaying and the sub-harmonics waveform components, two fault resistances are simulated. For a severe short-circuit (R-short is nearly zero) condition initiates the state of the TCSC in bypass mode where the capacitor is shorted by an inductor, and induce the transient DC decaying waveform that is added to the lines current, whose magnitude also depends on the inception angle as stated in Eq.(2.4). When the short-circuit resistance R-short is relatively high, the TCSC is operating in the blocking mode where the capacitors bank are connected, and causes an additive decaying sub-harmonic component to the fundamental one. As stated in Eq.(2.5), the magnitude of the sub-harmonics component depends on the inception angle, its frequency is related to the capacitor bank and the distance to the fault, while its decaying time is two times the one of the severe short circuit [11].. These facts are illustrated and confirmed by the simulation results as shown in Figs 2.6-2.9.

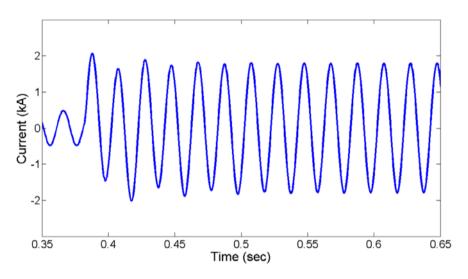

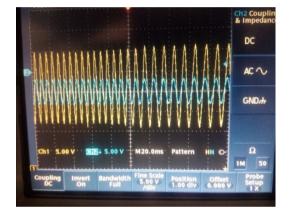

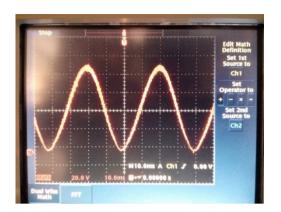

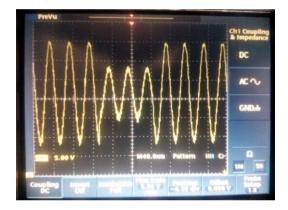

Fig.2.6 Current phasor for solid short circuit

Fig.2.7 Current transient waveforms in pu for three phase to ground faults (Rs= $0.01\Omega$ )

Fig.2.8 Voltage transient waveforms in pu for three phase to ground faults (Rs= $0.01\Omega$ )

Fig.2.9 Current in pu after fault for short circuits Rs=100  $\Omega$ .

The obtained simulation results show that the faulted signals are associated with DC decaying signals, harmonic and sub-harmonic components. The voltage waveform is corrupted by harmonic components and fast decaying DC components for small resistance faults. The current waveform may be significantly affected, depending on the inception angle, by decaying DC components for small resistance faults. Besides, the sub-harmonic component may also be added in the case of the series compensated transmission line

associated with relatively high fault resistance. The DFT algorithm may induce significant errors if it is directly used for phasors computation of these generated signals [33]. To eliminate these unwanted components, many efforts have been developed using different approaches to mitigate the effect of these components on phasor computations.

#### 2.3 Synchrophasor Measurements

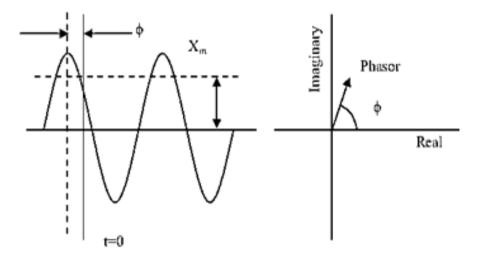

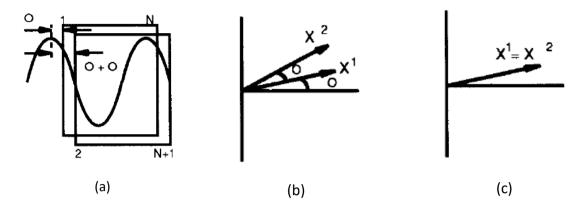

During steady state in an electric power system, the voltage and current signals are virtually sinusoidal waveforms. A phasor is a vector consisting of magnitude and angle that represents a sinusoidal waveform as illustrated in Fig2.10. The phasor of a signal can be derived using Fourier transforms utilizing the data samples of the signal within a selected time window. For a steady state signal, the magnitude is a constant, while the value of the angle depends on the starting point of samples. The angle is a relative quantity and a reference has to be selected.

A pure sinusoidal waveform can be represented by a unique complex number known as a phasor. Consider a sinusoidal signal:

$$x(t) = X_m \cos(\omega t + \varphi) \tag{2.7}$$

......

Where, X<sub>m</sub> : maximum value of the input signal,

$\Delta$ f:the frequency offset,

$\varphi$ : the initial phase angle of the input signal.

The phasor representation of this sinusoidal is given by:

$$x(t) = \frac{X_m}{\sqrt{2}} e^{j\varphi} = \frac{X_m}{\sqrt{2}} (\cos\varphi + j\sin\varphi)$$

(2.8)

f<sub>0</sub>: the nominal frequency,

The signal frequency  $\omega$  is not explicitly stated in the phasor representation. The term  $e^{j\omega}$  is customary suppressed in the expression above, with the understanding that the frequency is  $\omega$ . The magnitude of the phasor is the rms value of the sinusoid  $\frac{Xm}{\sqrt{2}}$  and its phase angle is  $\varphi$ , the phase angle of the signal in Eq.2.7. The sinusoidal signal and its phasor representation given by Eq.2.7 and Eq.2.8 are illustrated in Fig. 2.11.

Figure 2.10 Phasor representation of a Sinusoidal signal (left) Sinusoidal signal, (right) Phasor representation.

Measurement devices are placed at different locations in a power grid to capture voltage and current waveforms, from which phasors can be calculated. If the samples obtained by the measurement devices are not synchronized to a common timing reference, the angles of the phasors computed at different locations will not be comparable.

This may delay the understanding and analysis of certain power system phenomena and hence the development of certain power system applications. To remove this barrier, phasors measured across the power grid should have a common timing reference such that direct comparison is feasible.

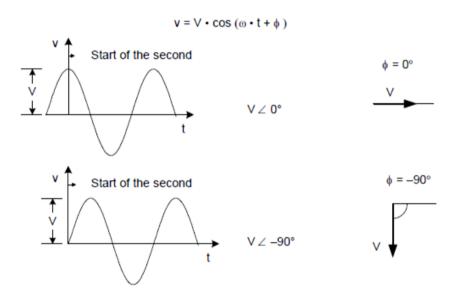

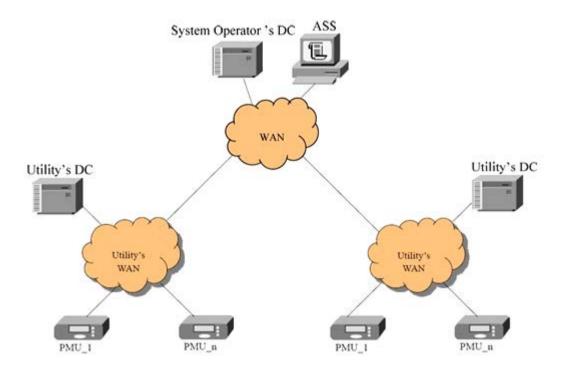

A synchrophasor is defined according the IEEE standard C37.118 as "A phasor calculated from data samples using a standard time signal as the reference for the measurement; however, synchronized phasors from remote sites have a defined common phase relationship." (C37.118-2005, March 2006.) Thus, synchrophasors measured across an interconnected power grid will have a common timing reference and thus can be compared directly as illustrated in Fig.2.12.

According to the same standard, a synchronizing source that provides the common timing reference may be local or global. The synchronizing signal may be distributed by broadcast or direct connection, and shall be referenced to Coordinated Universal Time (UTC). One commonly utilized synchronizing signal is the satellite signal broadcast from the Global Positioning System (GPS).

The definition of a real-time or synchronized Phasor provided in the IEEE Standard 1344-1995 [2] (1344-1995, 2001) corresponds to the conventional definition described earlier, at least at rated frequency (50 Hz or 60 Hz). With real-time waveforms, it is necessary to define a time reference to measure phase angles synchronously [3]. The IEEE Standard 1344-1995 [2] (1344-1995, 2001) defines the start of the second as the time reference for establishing the phasor phase angle value. The synchronized phasor measurement convention is shown in Fig.2.12.

Figure 2.12 Synchrophasor measurement conventions with respect to time.

The instantaneous phase angle measurement remains constant at rated frequency when using the start of the second phase reference. If the signal is at off-nominal frequency, the instantaneous phase varies with time. It can be seen later that the choice of this reference has an impact on the phasor phase angle measurement at off-nominal frequency.

#### 2.3.1 Phasor measurement principle

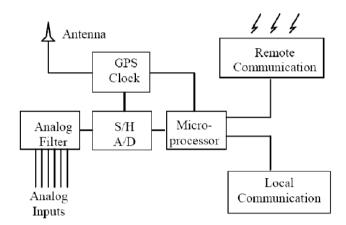

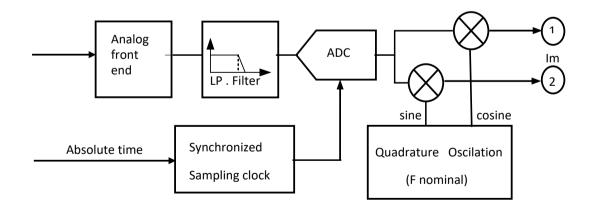

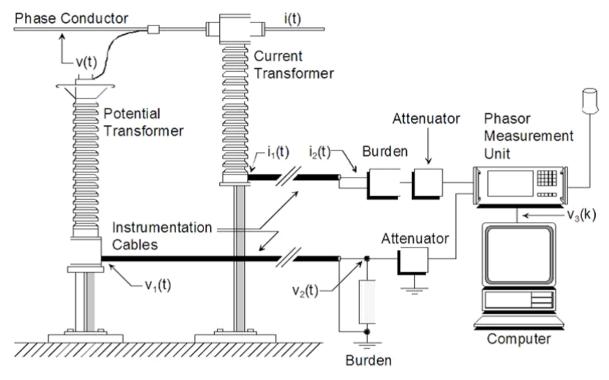

A PMU is a standalone device that measures 50/60 Hz AC voltage and current signals and provides them in phasor form with their frequency. The analog AC waveforms are digitized by an analog to digital converter for each phase and a phase-lock oscillator and a GPS reference time source, often called pulse per second (PPS) provides high-speed time synchronized sampling as illustrated in Fig.2.13. A PMU calculates line frequency, as well as voltage and current phasors at a high sampling rate and streams those data, along with the associated GPS time stamp, via networked communication lines. The synchrophasors can be phase or symmetrical component values.

Figure 2.13 PMU block diagram.

At present, phasor measurement units (PMUs) are the most accurate and advanced synchronized phasor measurement equipment. It measures 50/60 Hz sinusoidal waveforms of voltages and currents at a high sampling rate, up to 1200 samples per second and with high accuracy. From the voltage and current samples, the magnitudes and phase angles of the voltage and current signals are calculated in the phasor microprocessor of the PMU. As the PMUs use the clock signal of the Global Positioning System (GPS) to provide synchronized phase angle measurements at all their measurement points, the measured phasors are often referred to assynchrophasors.

Fig 2.13 illustrates a functional block diagram of a typical PMU. The GPS receiver provides the 1 pulse-per-second (pps) signal, and a time tag consisting of the year, day, hour, minute, and second. The 1-pps signal is usually divided by a phase-locked oscillator into the number of pulses per second required for the sampling of the analogue signals. The analog signals are derived from three-phase voltage and current transformers with appropriate antialiasing filtering. The microprocessor calculates the positive sequence voltage and current phasors, and determines the timing message from the GPS, along with the sample number at the beginning of a window.

#### 2.3.2 Phasor measurement algorithm

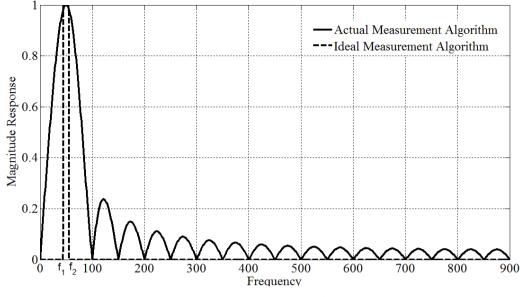

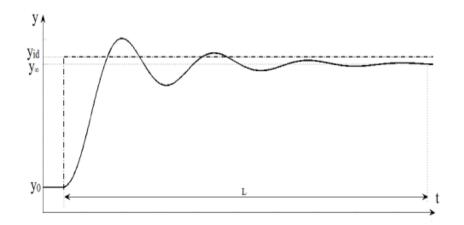

Synchrophasor finds wide use in wide area measurements, while the actual trends are increasingly considered in power system protection applications. During power system electromechanical disturbances and electromagnetic transient faults, the protective devices must have shorter response time for making a decision. This requires lower overshoot/under shoot measurement response.

The actual need in such application is designing phasor measurement and filtering algorithms suitable for protection applications while satisfying all the steady state and dynamic performance criteria of the IEEE standard c37.118.2011 [14]. The motivation of the work is presenting the synchrophasor estimation algorithm based on the DFT filter and introducing improvement that makes it suitable for both phasor measurement unit and protective devices.

## 2.3.3 Different Phasor Measurement Techniques

In the power system phasor, amplitude, phase angle and frequency are variables which may be critical and used by many power system control and protection applications. The fast and accurate measurements of these variables are still considered in a contemporary topic of research interest. Many phasor estimation algorithms as the Newton method [49], Kalman filtering[50] and level tracking[51], least square algorithm techniques have also been proposed for synchro-phasor computations in[52], a raised cosine filter (RCF) is used to compute phasors during power oscillations and dynamics. The RCF filter needs a comparatively large (4cycles) computational time windows. This algorithm has a very slow time response.

Discrete Fourier Transform (DFT) is widely used as phasor estimation algorithm of fundamental frequency [91, 92]. Due to their good harmonic rejection property conventional DFT algorithm achieve excellent performance when the signal contains only fundamental frequency and integer harmonic frequency components.

# 2.3.4 DFT Measurement technique

Assuming that the signal x(t) is sampled N times per fundamental period (50Hz or 60Hz) waveform to generate the sample set:

$$x_{k} = X_{m} \cos\left[\left(\frac{2\pi}{Nf_{o}}k + \varphi_{i}\right)\right]$$

(2.9)

The phasor  $\overline{X}$  is given by:

$$\overline{X} = \frac{\sqrt{2}}{N} (X_c - jX_s)$$

(2.10)

Where:

$$X_{c} = \sum_{k=1}^{N} x_{k} \cos\left(\frac{2\pi}{N}k\right)$$

(2.11)

And

$$X_{s} = \sum_{k=1}^{N} x_{k} \sin\left(\frac{2\pi}{N}k\right)$$

(2.12)

Fig.2.15 shows a signal processing steps performed for generating the synchronized phasors provided that the power system frequency is operating at nominal frequency. This is based on the fixed frequency sampling synchronized to an absolute time reference, followed by multiplication of the cosine and sine nominal frequency carrier.

Figure 2.15 PMU Phasor signal processing model.

The conventional phasor representation of a sinusoidal signal is related to the fundamental component by its DFT as follows:

$$\overline{\mathbf{X}} = \frac{1}{\sqrt{2}} (\mathbf{X}_{\mathrm{s}} - \mathbf{j}\mathbf{X}_{\mathrm{c}})$$

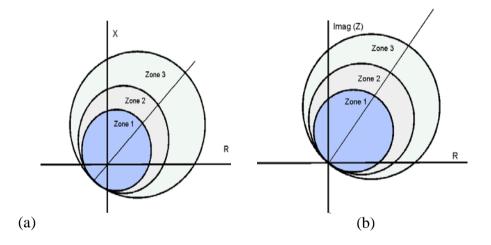

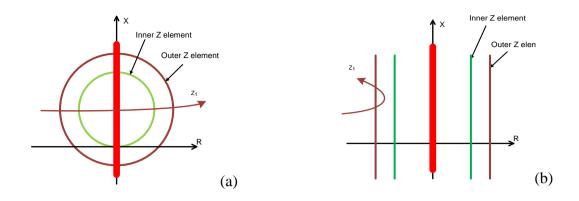

(2.13)