#### **REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE**

#### MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### **UNIVERSITE M'HAMED BOUGARA-BOUMERDES**

## Institut de Génie Electrique et Electronique

## Thèse de Doctorat

Présentée par : CHENOUF Amel

En vue de l'obtention du diplôme de DOCTORAT en SCIENCES

#### Filière : Génie électrique

#### **Option : Microélectronique**

## RELIABILITY AWARE DESIGN OF INTEGRATED CIRCUITS

#### Soutenue le : 08 Avril 2021

#### Devant le jury composé de :

| M. RAHMOUNE   | Fayçal     | Professeur              | UMBB  | Président             |

|---------------|------------|-------------------------|-------|-----------------------|

| M. BENTARZI   | Hamid      | Professeur              | UMBB  | Directeur de thèse    |

| M. DJEZZAR    | Boualem    | Maitre de recherche A   | CDTA  | Co-directeur de thèse |

| M. SLIMANE    | Abdelhalim | Directeur de recherche  | CDTA  | Examinateur           |

| M. BENNAAMANE | Kamel      | Maitre de conférences A | UMMTO | Examinateur           |

2020/2021

# AKNOWLEDGEMENT

Then all the praises and thanks are to ALLAH, lord of the worlds, for his blessings and mercy! Without ALLAH willing, this PhD thesis would never have been achieved!

This PhD research work has been carried out at Microelectronics & Nanotechnology Division of Centre de Développement des Technologies Avancées; CDTA in collaboration with Institut de Genie Electrique et Electronique; IGEE of Universite M'hamed BOUGARA Boumerdès UMBB.

I would like to express my deep gratitude to a number of people who supported me during my work, in scientific, and in personal form.

First of all, I want to thank Prof. Hamid Bentarzi for giving me the opportunity to work on a PhD theme of my choice, for his guidance, support, and for his empathy.

I want to thank my thesis committee members: Prof. Fayçal RAHMOUNE, Dr. Abdelhalim SLIMANE, and Dr. Kamel BENNAAMANE for devoting time to evaluate this research work and writing feedback on my PhD thesis.

I am thankful to the editors and reviewers of both IEEE TDRM and IET Circuits and Systems journals for their peer reviewing of my submitted papers, and whose constructive remarks and recommendations allowed us to further discuss the obtained results and enrich our papers to get them published.

I cannot thank enough Dr. Boualem Djezzar for his scientific support, proof reading my papers and PhD thesis. I am thankful to him for encouraging me to achieve a goal I thought unreachable! I owe him respect for the high standards, he established in FCS team, for conducting research work!

I am fully grateful to the whole FCS research team: Without their scientific discussions, technical assistance, this work would not have been possible! I would like to thank, in particular, Mr. Abdelmadjid Benabdelmoumene and Mr. Boumediene Zatout who were always there, for helping and encouraging me. We can see that we are in brotherhood!

I want to thank all my colleagues and friends in CDTA who were of a great support for me, who stood by me, and who, when I felt discouraged and losing enthusiasm, came to push me! I would like to thank in particular Karima Ait Saadi and her husband Redha Hamoudi who came always to help me, prayed for me. "How can I help you to get your thesis done" is my favorite encouraging and compassion words I heard from them!

Amel Azzouz with whom I start my journeys, in CDTA, around a good coffee, and leave to go working in my office with her best wishes of luck and success!

Assia Smaali & Slimane Lafane, Farida Hamadi for their help, encouragements, shared concerns, and for the all great journeys we spent together in Algiers!

Fayçal Hadj-Larbi, Hakim Tahi, Mohamed Boubaaya, Abderrazak Smatti, Ahmed Liacha, Rafik Serhane, Noureddine Derguini, Abdelkrim Kamel Oudjida, Messaoud Bengherabi, Khadidija Messaoudi, Khalida Ghanem, Hadjira Haridi, Ratiba Touati, Kahina Mahdi, Yasmina Belaroussi, Majda Kahli, Nadjet Bouhlel, Safia Ben Ahmed, Maouïa Bentlemsan, Amina Ghazli, Samia Fouzar, Souhila Mazighi, Samia Aggoune, Karima, Annou, Amel Bounekta for their encouragements.

I am grateful to my friends and mates who supported me, encouraged me, and shared with me the stressful time I went through along my PhD studies and for the funny time we spent together in particular:

Fouzia Guessab, the person who shared with me joy and sadness over more than 13 years! And who was concerned by my thesis achievement more than anyone else!

Nadjat Hamdaoui, who cared for me like my little sister! Who stood for me, preparing meals, when I was overwhelmed! And who kept awake to encourage me, and to print the whole thesis copies.

Fatima Zohra Bouchibane, who softened my hard moments by making jokes, who is the best person to ask for preparing tea to keep awake working overnight!

Mounira Bitchikh, who kept advising me on the way to get things done, how to manage time to be more efficient at work!

Leila Souadkia, for her support and wise advices! For her believe in me. "You can do it Amel, you deserve it" were always her words that encouraged me a lot!

Nabila Dib, who never stopped supporting me, her availability and that of her family to help me along theses years in Algiers, cannot be thanked enough!

Above all, I want to pay tribute to my family whom I owe them all my achievements! My parents: who raised me with unconditional love! My father, who passed away in 2009 "Allah Yerhamou" was always proud of me. May ALLAH grant him Paradise! My mother, may ALLAH bless her, who brought me through the hard times, and keeps me always in her thoughts and prayers!

My brothers and sisters, who never stopped taking care of me! Caring about my career! And who were always there to support and encourage me to pursue my PhD studies!

The list of people to thank won't end if I were to mention all of them here. So, I want to thank all people who I have not mentioned, here, for inspiring, helping, and praying for me!

### الملخص

مهدت التطورات المذهلة في مجالى تصميم الدارات المدمجة بمساعدة الحاسوب وتقنيات التصنيع الطريق لهندسة وتصنيع دارات معقدة للغاية وعالية الأداء، تدمج أكثر من 100 مليون ترانز ستور في رقاقة سيليكون مساحتها بضع مليمترات مربعة . إلا أن هذه الكثافة العالية جلبت معها المزيد من التحديات لمصممي هذه الدارات المدمجة من منظور ضمان موثوقيتها. في الواقع ، نظرًا للتصغير الشديد للدارات ، وبسبب تأثيرات الإهتراء، تتغير خصائص مكوناتها الشبه الناقلة بمرور الوقت ، مما يتسبب في فشلها في الإيفاء بالمواصفات التي صممت من أجلها. بيد أن الحل القائم على التكنولوجيا ليس دائمًا ممكنًا ، ويرجع ذلك أساسًا إلى أن مهندسي عناصر أشباه النواقل يركزون عادةً على تطوير ترانزستورات أصغر وأسرع وأقل استُهلاكًا للطاقة. هذا يجبر المصممين على تخفيف هذا التدهور لضمان الأداء المنوط بداراتهم. وبالتالي ، تصبح محاكاة الشيخوخة ضرورية للتنبؤ بتدهور أداء الدارات المدمجة بسبب التغيرات الزمنية. علاوة على ذلك ، فإن إدخال تقنيات تصميم جديدة و التي تعتبر الموثوقية كشرط لا يقل أهمية عن السرعة والمساحة واستهلاك الطاقة ، أصبحت أكثر من ضرورية لضمان تقديم دارات وأنظمة موثوقة وفقًا لمفهوم التصميم من أجل الموثوقية. في هذا الصدد ، نقترح ، من ناحية، نقل تحليل الموثوقية من مستوى التر انسستور إلى مستوى أعلى من التجريد. هذا يسمح بتقييم أفضل للتدهور المستحث في أداء الدارات. ومن ناحية أخرى ، نقدم تقنية جديدة لتصميم دارات موثوقة بالنسبة لدراسة الحالة لأطروحة الدكتوراه هذه ، إخترنا التعامل مع ،أحد أكثر آليات الإهتراء التي تتسبب في الشيخوخة المبكرة للدارات عالية الدمج، ألا و هو عدم الإستقرار الناجم عن الإسقتطاب السلبي المتزامن مع الحرارة المرتعة في الدارات. نقدم نتائج تحليل أثره على مستوى الدارة مباشرة ونقدم نموذجا له يمكن إدماجه في جهاز محاكاة تجارى. ومن ناحية أخرى ، نقدم منهجية لتصميم دارات مدمجة تأخذ بعين الإعتبار هذه المشكل وتستند على الإختيار الأمثل لحجم الترانز ستور من أجل إستحداث خلايا ذاكرة للحاسوب ذات مناعة أكبر للإهتراء.

الكلمات المفتاحية: تصميم الدارات المدمجة، الإهتراء في أنصاف النواقل، الشيخوخة المبكرة للدارات، العمر الإفتراضي للدارات المدمجة المحاكات الإلكترونية، تصميم الدارات المدمجة من أجل الموثوقية.

# RÉSUMÉ

Les progrès impressionnants de la conception assistée par ordinateur et des procédés de fabrication de circuits intégrés ont permis de produire de puces très complexes, hautes performances intégrant plus de 100 millions de transistors dans quelques millimètres carrés de silicium. Cependant, cette densité élevée a entraîné plus de défis pour les concepteurs de circuits intégrés en termes de garantie de fiabilité de leurs circuits.

En fait, en raison de cette forte intégration, et des effets d'usure, les paramètres électriques des dispositifs à semi-conducteurs dérivent plus rapidement avec le temps, ce qui fait que les circuits intégrés échouent à satisfaire les spécifications pour lesquelles ils ont été conçus.

Or une solution basée sur la technologie n'est pas toujours réalisable, du fait que les industriels des semi-conducteurs se concentrent plus sur le développement de transistors plus petits, plus rapides et moins gourmands en énergie. Cela contraint les concepteurs à modérer cette dégradation et à améliorer la durée de vie de leurs circuits durant la phase de conception. Une simulation du vieillissement s'avère alors indispensable pour prédire la dégradation des performances des circuits intégrés due aux variations temporelles. De plus, l'introduction de nouvelles techniques de conception qui considèrent la fiabilité comme une contrainte de conception aussi importante que la vitesse, la surface et la consommation d'énergie, devient plus que nécessaire pour garantir la délivrance de circuits et de systèmes fiables conformément au concept de conception en vue de la fiabilité (DFR). Dans cette perspective, nous proposons, d'une part, de migrer l'analyse de fiabilité du niveau dispositif vers un niveau d'abstraction supérieur. Cela permettrait une meilleure évaluation de la dégradation induite sur les performances des circuits. D'autre part, nous proposons une approche DFR pour concevoir des circuits fiables.

Pour cette de doctorat, nous avons choisi de traiter l'instabilité due à la polarisation négative à haute température dite NBTI. NBTI est le mécanisme d'usure réduisant le plus la durée de vie des circuits intégrés submicroniques profonds. Nous présentons nos résultats de caractérisation au niveau du circuit NBTI, la mise en œuvre d'une interface de simulation intégrant notre modèle NBTI sur un simulateur commercial. D'autre part, nous présentons une approche de mitigation d'NBTI basée sur le dimensionnement des transistors que nous proposons pour la conception de cellules 6T-SRAM robustes.

#### Mots clés:

Conception de circuits intégrés, fiabilité des CIs. Vieillissement des dispositifs semi-conducteurs, mécanismes d'usure, NBTI, simulation de fiabilité, NBTI. Conception de circuits intégrés en vue de la fiabilité.

# ABSTRACT

The striking advances in both computer-aided integrated circuit design and manufacturing technologies have paved the way for designing and manufacturing highly complex, high-performance chips integrating more than 100 million transistors into a few square millimeters of silicon. However, this high density has brought with it more challenges for IC designers in terms of their circuits reliability sign-off.

In fact, due to the aggressive scaling, and to wear out effects, the electrical parameters of semiconductor devices are shifting over time, causing for ICs the failure to meet the specifications for which they were designed. However, a technology-based solution is not always feasible, mainly because semiconductor engineers usually focus on developing smaller, faster, and less energy-intensive transistors. This compels designers to moderate this degradation and to improve the lifetime of their circuits during the design phase. A simulation of aging becomes therefore essential to predict the performance degradation of the ICs due to temporal variations. Moreover, the introduction of new design techniques which consider reliability as a design constraint as important as speed, area, and power consumption, becomes more than necessary to warranty delivering reliable circuits and systems by adopting design for reliability (DFR) concept. In this prospect, we propose, on one hand, to migrate reliability analysis from device-level to a higher level of abstraction. This allows a better assessment of the induced degradation on the circuits' performance. On the other hand, we propose a DFR approach to deign reliable circuits.

For this PhD thesis we choose, to deal with NBTI, which is one of the most wear-out mechanisms shrinking the lifetime of deep submicron ICs. We present our NBTI circuit-level characterisation results, the implementation of our NBTI model on a commercial simulator. On the other hand, we present an NBTI mitigation approach based on transistor sizing we propose for designing robust 6T-SRAM cells.

#### **Keywords:**

IC design, Semiconductors Reliability, wear-out mechanisms, NBTI, reliability simulation, NBTI mitigation. IC Design for Reliability

# LIST of ACRONYMS

| ABB      | Adaptive Body Biasing                                     |

|----------|-----------------------------------------------------------|

| AHT      | As-grown Hole Traps                                       |

| ANPC     | Anti-Neutralization Positive Charge                       |

| BEOL     | Back-End Of Life                                          |

| BERT     | BErkeley Reliability Tools                                |

| BSIM     | Berkeley Short-channel IGFET Model                        |

| BTI      | Bias Temperature Instability                              |

| CAD      | Computer Aided Design                                     |

| CHC      | Channel Hot Carrier                                       |

| CMOS     | Complementary Metal Oxide Semiconductor                   |

| CPC      | Cyclic Positive Charge                                    |

| CPU      | Central Processing Unit                                   |

| CR       | Cell Ratio                                                |

| CUT      | Circuit Under Test                                        |

| DAC      | Digital Analog Converter                                  |

| DFR      | Design For Reliability                                    |

| DIBL     | Drain-Induced Barrier Lowering                            |

| DLHT     | Deep-Level Hole Traps                                     |

| DRAM     | Dynamic Random Access Memory                              |

| DVFS     | Dynamic Voltage and Frequency Scaling                     |

| DVS      | Dynamic Voltage Scaling                                   |

| EDA      | Electronic Design Automation                              |

| EM       | Electro Migration                                         |

| FBB      | Forward Body Bias                                         |

| FEOL     | Front-End Of Line                                         |

| FF       | Fast nMOS and Fast pMOS                                   |

| FS       | Fast nMOS and Slow pMOS                                   |

| GAA      | Gate-All-Around                                           |

| HCI      | Hot Carrier Injection                                     |

| HKMG     | High-K Metal Gate                                         |

| HSPICE   | Hailey Simulated Program with Integrated Circuit Emphasis |

| IBM      | International Business Machines Corporation               |

| IC       | Integrated Circuit                                        |

| IEEE     | Institute of Electrical and Electronics Engineers         |

| IGFET    | Insulated-Gate Field-Effect Transistor                    |

| IoT      | Internet of Things                                        |

| ISCAS'85 | 1985 International Symposium on Circuits & Systems        |

| ISCAS'89 | 1989 International Symposium on Circuits & Systems        |

| ISiT     | Institute for Silicon Technology of Fraunhofer            |

| ITC'99   | 1999 International Test Conference                        |

| ITRS     | International Technology Roadmap for Semiconductors       |

| LDD      | Lightly Doped Drain                                       |

| LER      | Line Edge Roughness                                       |

|          |                                                           |

| LWR             | Line Width Roughness                           |

|-----------------|------------------------------------------------|

| MCNC'91         | 1991 Microelectronics Center of North Carolina |

| MFCP            | Multi Frequency Charge Pumping                 |

| MNOS            | Metal Nitride Oxide Semiconductor              |

| MPE             | Multi-Phonon Emission                          |

| MPFAT           | Multi-Phonon-Field-Assisted Tunneling          |

| MPW             | Multi Project Wafer                            |

| MOS             | Metal Oxide Semiconductor                      |

| MOSFET          | Metal Oxide Field Effect Transistor            |

| MRAM            | Magnetic RAM                                   |

| MTCMOS          | Multi Threshold CMOS                           |

| N <sub>IT</sub> | Interface Traps                                |

| NMH             | Noise Margin High                              |

| NML             | Noise Margin Low                               |

| nMOS            | n-type MOSFET                                  |

| N(P)BTI         | Negative (Positive) BTI                        |

| Op-Amp          | Operational Amplifier                          |

| OPC             | Optical Proximity Correction                   |

| OTFM            | On-The-Fly Measurement                         |

| PDN             | Pull-Down Network                              |

| PCRAM           | Phase-Change Random Access Memory              |

| pMOS            | p-type MOSFET                                  |

| PNO             | Plasma Nitride Oxide                           |

| PPAC            | Performance Power Area Cost                    |

| PR              | Pull-up Ratio                                  |

| PTM             | Predictive Technology Model                    |

| PUN             | Pull-Up Network                                |

| PVT             | Process Voltage Temperature                    |

| RAM             | Random Access Memory                           |

| RBB             | Reverse Body Bias                              |

| R-D             | Reaction-Diffusion                             |

| RDF             | Random Dopant Fluctuation                      |

| ReRAM           | Resistive RAM                                  |

| RTN             | Random Telegraph Noise                         |

| SCE             | Short Channel Effect                           |

| SF              | Slow nMOS and Fast Pmos                        |

| SILC            | Stress Induced Leakage Current                 |

| SINM            | Static current Noise Margin                    |

| SiON            | Silicon Oxynitride                             |

| SNM             | Static Noise Margin                            |

| SRAM            | Static Random Access Memory                    |

| SS              | Slow nMOS and Slow pMOS                        |

| STA             | Static Timing Analysis                         |

| STT-MRAM        | Spin-Torque Transfer Magnetic RAM              |

| SVNM            | Static Voltage Noise Margin                    |

| TCAD            | Technology Computer Aided Design               |

|                 |                                                |

## LIST of ACRONYMS

| T-D  | Trapping -Ditrapping                       |

|------|--------------------------------------------|

| TDDB | Time-Dependent Dielectric Breakdown        |

| TDDS | Time-Dependent Defect Spectroscopy         |

| TNO  | Thermal Nitride Oxide                      |

| TSMC | Taiwan Semiconductor Manufacturing Company |

| TTL  | Transistor-Transistor Logic                |

| UDVS | Ultra Dynamic Voltage Scaling              |

| UFM  | Ultra-Fast Measurement                     |

| ULSI | Ultra Large Scale Integration              |

| URI  | Unified Reliability Interface              |

| VFB  | Flat Band Voltage                          |

| VIH  | Input Voltage High                         |

| VIL  | Input Voltage Low                          |

| Vinv | Inverter logic threshold                   |

| VOH  | Output Voltage High                        |

| VOL  | Output Voltage Low                         |

| VTC  | Voltage Transfer Curve                     |

| VTH  | Threshold Voltage                          |

| WNM  | Write Noise Margin                         |

| WRM  | WRite Margin                               |

| WTI  | Write Trip current                         |

| WTV  | Write Trip Voltage                         |

| WWL  | Write WordLine                             |

## Figures List

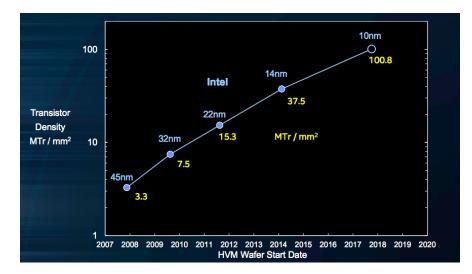

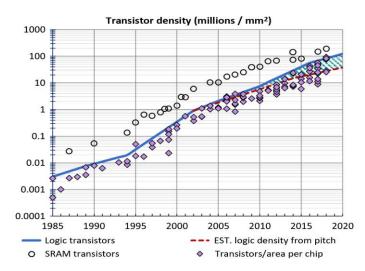

| Fig. 1.1   | Logic transistor density in Intel chips1                                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

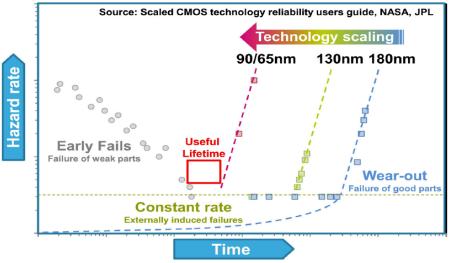

| Fig. 1.2   | Lifetime shrinking with technology scaling                                                                                                                                                    |

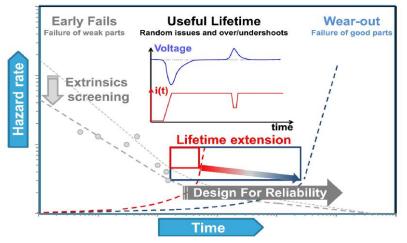

| Fig. 1.3   | Design for Reliability enhancing the circuits useful lifetime                                                                                                                                 |

| Fig. 2.1   | Big data and instant data9                                                                                                                                                                    |

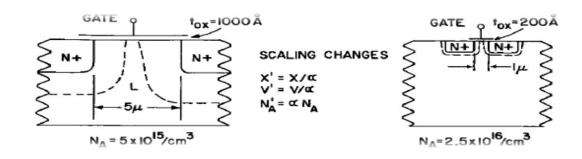

| Fig. 2.2   | Technology scaling theory of Dennard10                                                                                                                                                        |

| Fig. 2.3   | The trend of the density of logic and 6T-SRAM chips over the last 3 decades11                                                                                                                 |

| Fig. 2.4   | Scaling trends of technology node, oxide thickness, and supply voltage12                                                                                                                      |

| Fig. 2.5   | Short channel transistors associated effects                                                                                                                                                  |

| Fig. 2.6   | Electronic components failure versus service life14                                                                                                                                           |

| Fig. 2.7   | Taxonomy of variations in integrated circuits14                                                                                                                                               |

| Fig. 2.8   | Source of local variations in CMOS devices15                                                                                                                                                  |

| Fig. 2.9   | Process corners                                                                                                                                                                               |

| Fig. 2.10  | Schematic illustration of a field effect transistor (FET) in (a). pMOS-FETwith silicon dioxide (SiO2) as insulator for CMOS bulk technology in (b source IBM), interface states roughness (c) |

| Fig. 2.11  | NBTI configuration of the pMOS transistor within CMOS Inverter19                                                                                                                              |

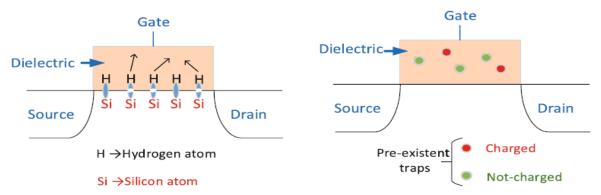

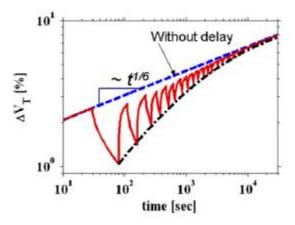

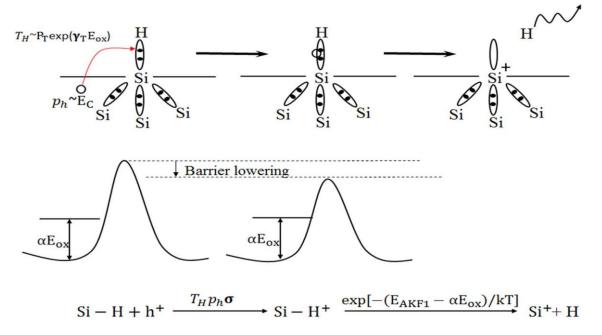

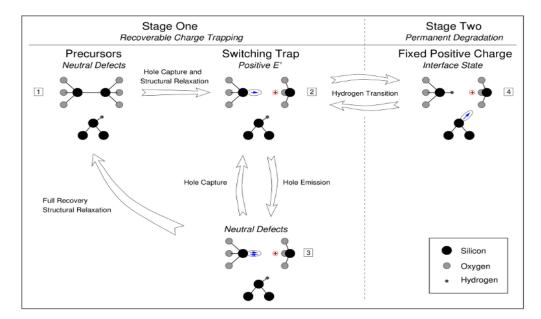

| Fig. 2.12  | NBTI mechanisms: (a) Reaction-Diffusion (R-D) mechanism. (b) Trapping-<br>Detrapping (TD) mechanism                                                                                           |

| Fig. 2.13  | Correction done by RD model to suppress observed saturation in experiments23                                                                                                                  |

| Fig. 2.14  | R-D model mechanism principle                                                                                                                                                                 |

| Fig. 2. 15 | Two-stage NBTI model25                                                                                                                                                                        |

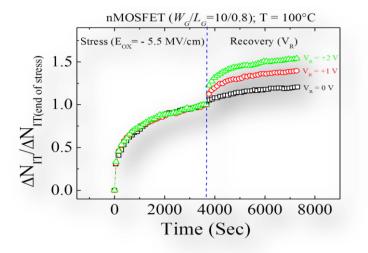

| Fig. 2.16  | Normalized Nit degradation to end of stress for different electric fields during recovery                                                                                                     |

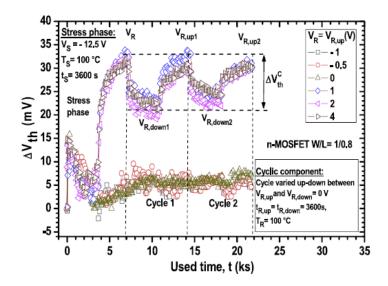

| Fig. 2.17  | NBTI-induced cyclic component in the gate oxide of n-MOSFET28                                                                                                                                 |

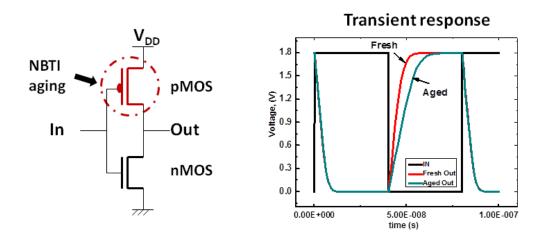

| Fig. 2.18  | Illustration of the Impact of NBTI on the CMOS inverter performance                                                                                                                           |

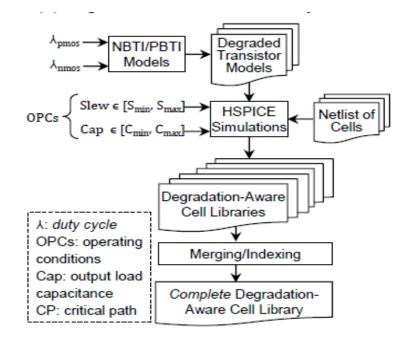

| Fig. 2.19  | Degradation-aware cell library creation                                                                                                                                                       |

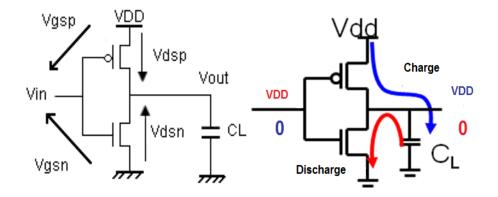

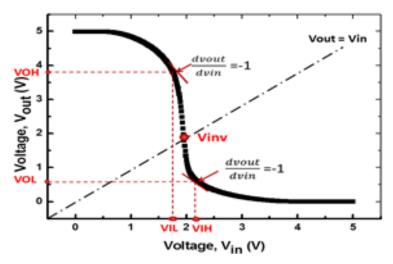

| Fig. 2.20  | CMOS inverter input and output voltages                                                                                  | .33 |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 2.21  | CMOS Inverter DC characteristics                                                                                         | .34 |

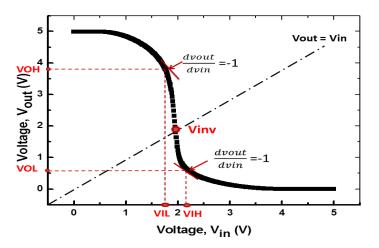

| Fig. 2.22  | CMOS Inverter logic Levels and Noise margins                                                                             | 35  |

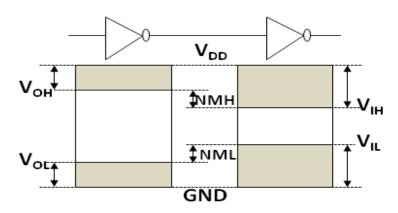

| Fig. 2.23  | Typical memory hierarchy                                                                                                 | 36  |

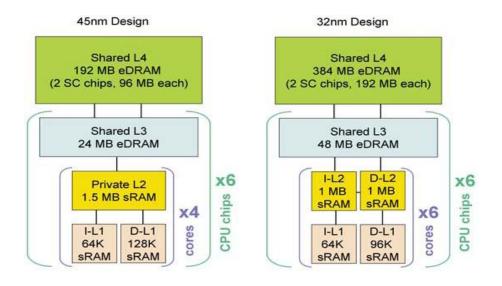

| Fig. 2.24  | Processor with 3 level cache                                                                                             | .37 |

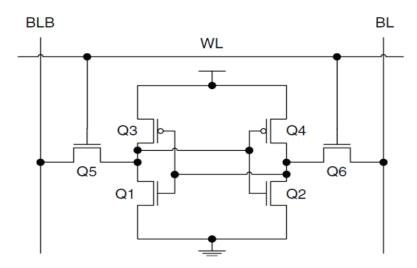

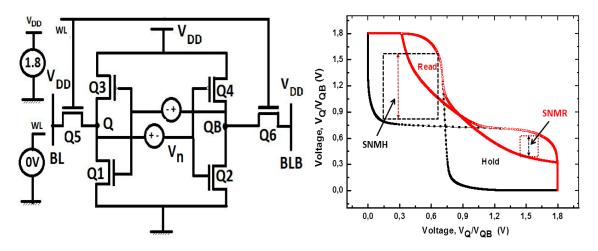

| Fig. 2.25  | 6T-SRAM Cell schematic                                                                                                   | .38 |

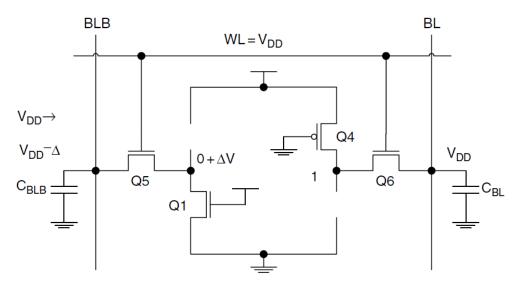

| Fig. 2.26  | 6T-SRAM during read operation                                                                                            | .39 |

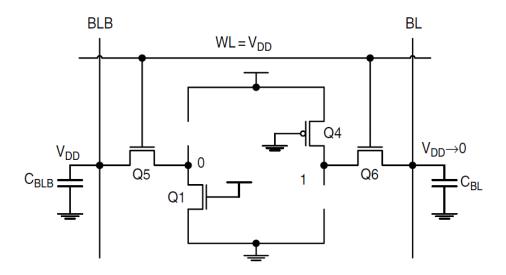

| Fig. 2.27  | 6T-SRAM during write operation                                                                                           | 40  |

| Fig. 2.28  | 6T-SRAM SNM setup and butterfly                                                                                          | 40  |

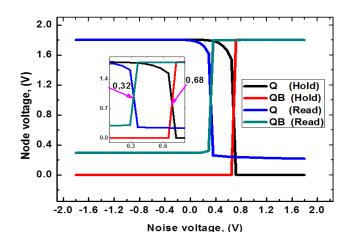

| Fig. 2.29  | Example of hold and read SNM of a 0.18µm 6T-SRAM cell                                                                    | 41  |

| Fig. 2.30  | Example write margin of a 0.18µm 6T-SRAM cell                                                                            | 42  |

| Fig. 3.1   | Circuit under test: CMOS inverter                                                                                        | 51  |

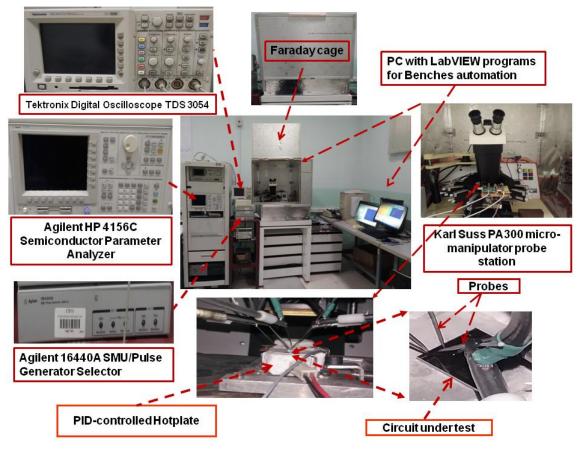

| Fig. 3.2   | NBTI Characterization test bench for the CMOS inverter                                                                   | .52 |

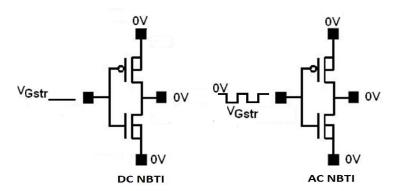

| Fig. 3.3   | CMOS inverter configuration under DC & AC NBTI stresses                                                                  | .53 |

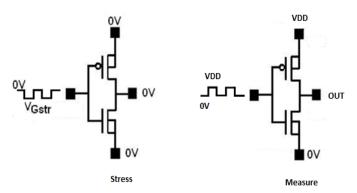

| Fig. 3.4   | Stress & measure configurations used to characterize the CMOS inverter tempor<br>performance under AC NBTI stress        |     |

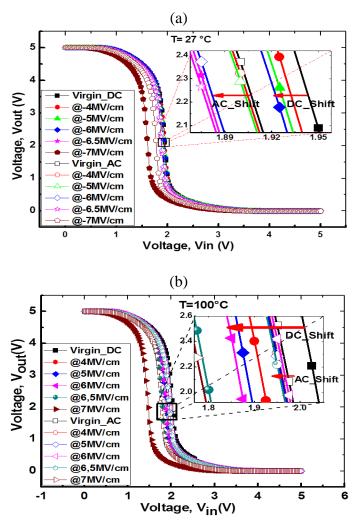

| Fig. 3.5   | CMOS Inverter VTC shift subjected to DC&AC NBTI stresses at room temperation (a) and at elevated temperature in (b).     |     |

| Fig. 3.6   | The critical voltages of the CMOS inverter VTC                                                                           | .55 |

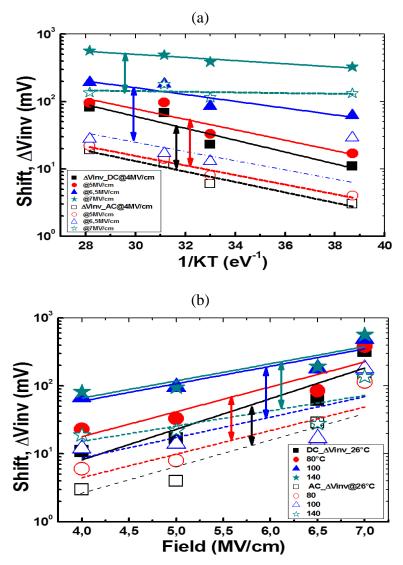

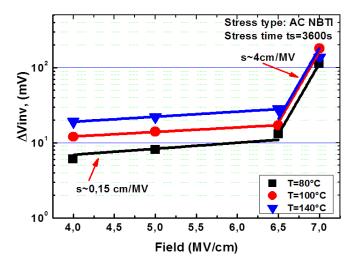

| Fig.3.7    | Inverter switching threshold shift under DC & AC-type NBTI stresses with respect<br>energy (a) and the applied field (b) |     |

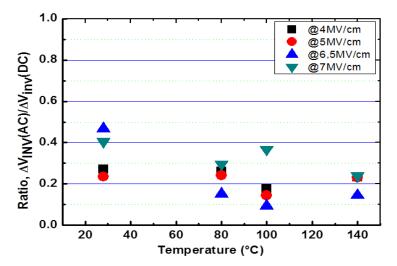

| Fig. 3.8   | AC/DC ratio of the Inverter switching threshold voltage shift                                                            | 57  |

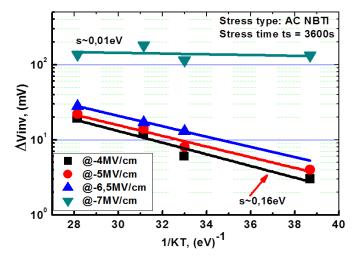

| Fig. 3.9   | Inverter switching threshold shift due to AC NBTI with respect to activat energy.                                        |     |

| Fig. 3.10  | Inverter logic threshold shift due to AC NBTI with respect to the applied field                                          | 58  |

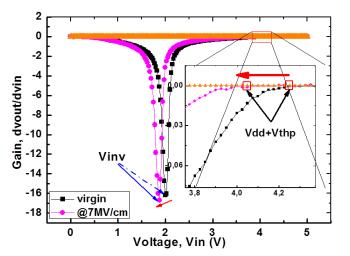

| Fig. 3.11: | Method of extracting PMOS threshold (Vthp) from the inverter DC gain                                                     | 59  |

## Figures List

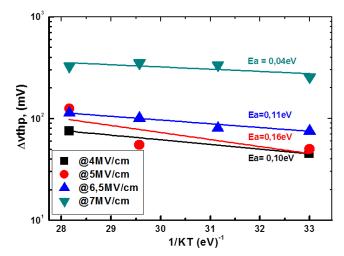

| Fig. 3.12 | The shift of the extracted PMOS threshold voltage under AC NBTI with respect to the energy under different electric field                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

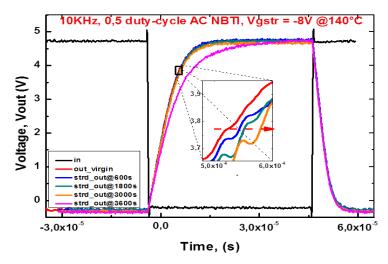

| Fig. 3.13 | CMOS inverter temporal response subjected to AC NBTI stress                                                                                                   |

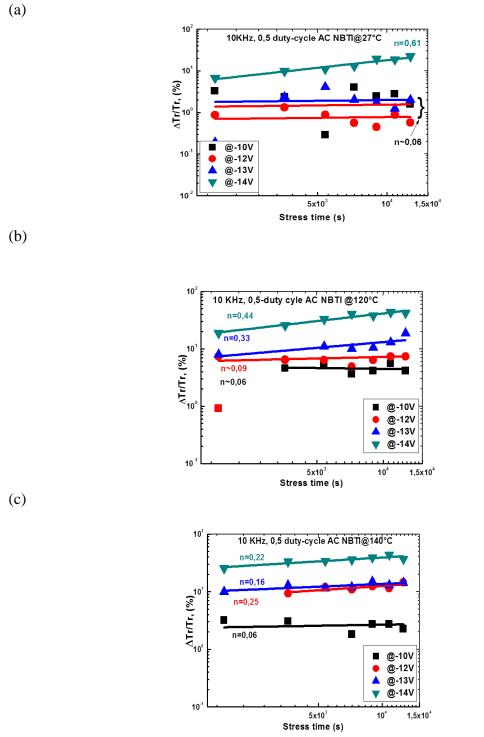

| Fig. 3.14 | The shift CMOS inverter risetime with respect to stress time under a series of electric field at different temperatures                                       |

| Fig. 3.15 | CMOS inverter risetime shift with respect to the energy under different AC NBTI stress voltages                                                               |

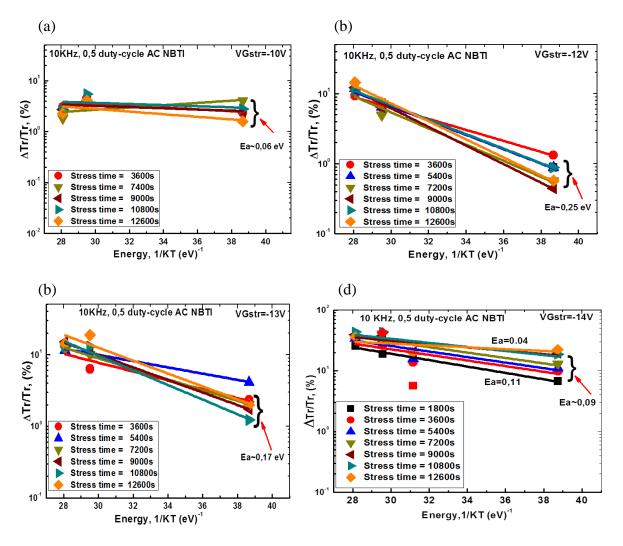

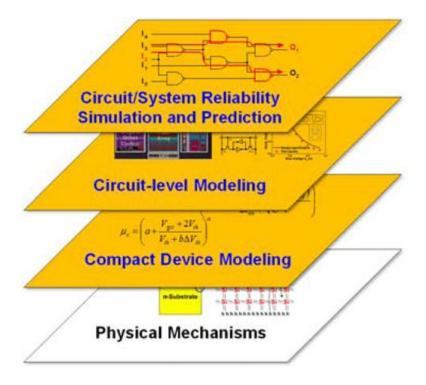

| Fig. 4.1  | Cross-layer approach of circuit reliability analysis                                                                                                          |

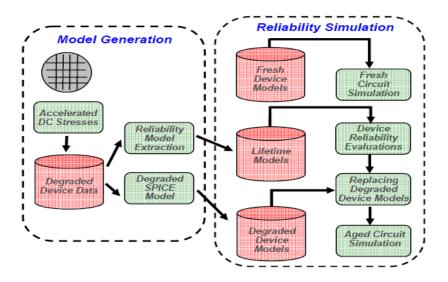

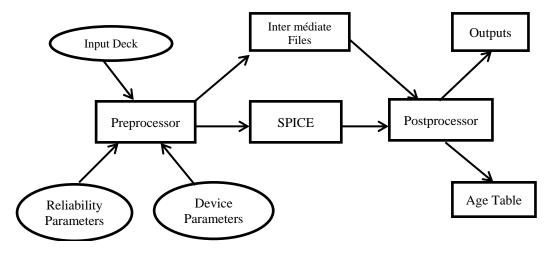

| Fig. 4.2  | Typical reliability modeling and simulation framework                                                                                                         |

| Fig. 4.3  | BERT structure                                                                                                                                                |

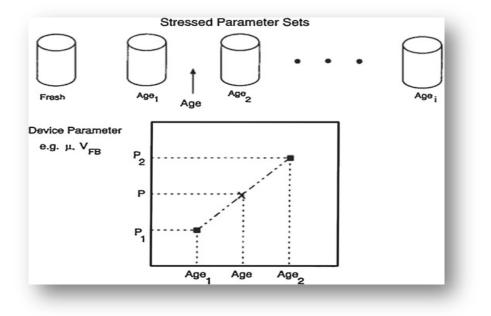

| Fig. 4.4  | Calculation of the aged parameter from pre-stressed model parameter sets75                                                                                    |

| Fig. 4.5  | Cadence Ultrasim reliability URI                                                                                                                              |

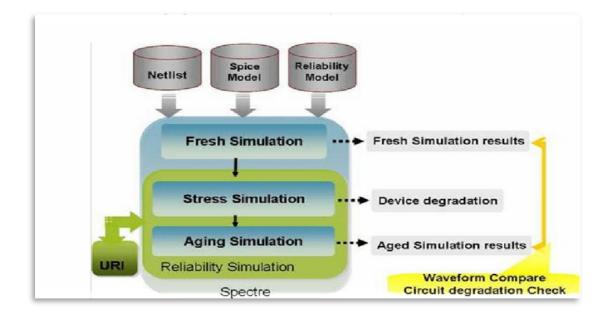

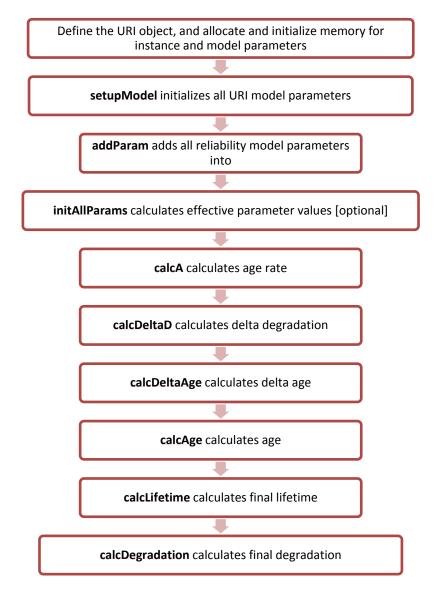

| Fig. 4.6  | Unified Reliability Interface Call Sequence77                                                                                                                 |

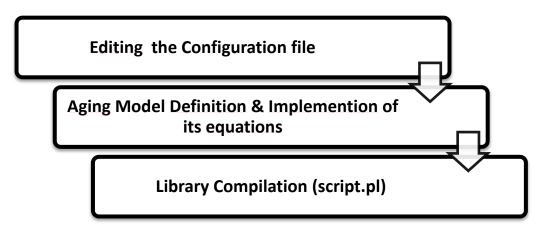

| Fig. 4.7  | Shared library creation steps                                                                                                                                 |

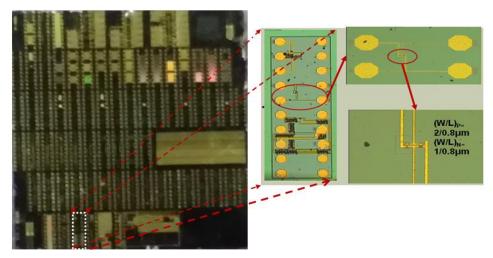

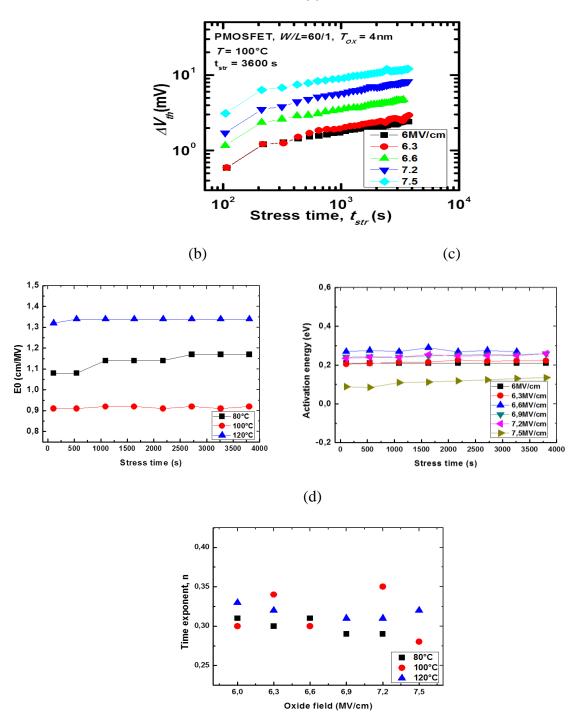

| Fig. 4.8  | OTFOT-based NBTI characterization of a $0.18\mu$ m pMOS Vth in (a), and the extracted NBTI Model parameters E0 in (b), Ea in (c), and the n exponent in (d)80 |

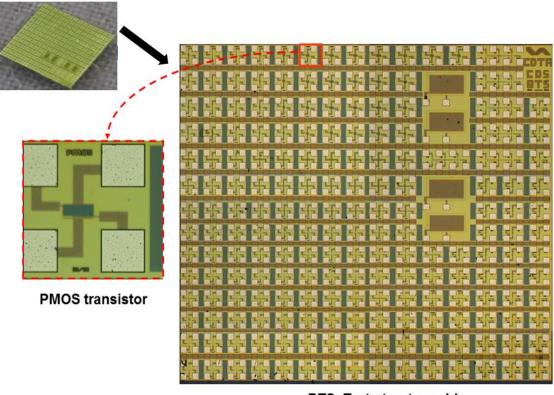

| Fig. 4.9  | BTS_Test structures chip implemented in TSMC 0.18µm CMOS technology81                                                                                         |

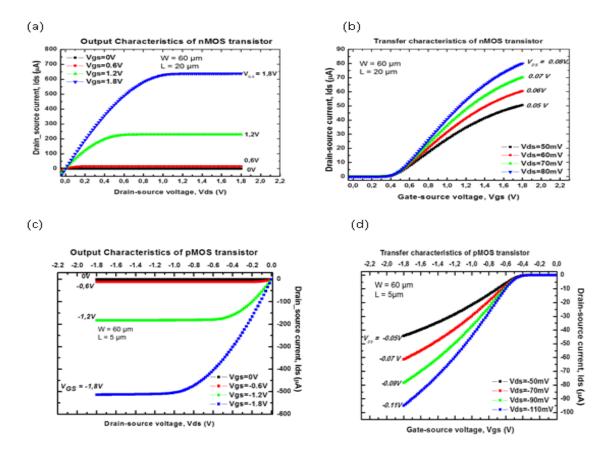

| Fig. 4.10 | Characterisation results of two nMOS and pMOS devices belonging to BTS_test structures                                                                        |

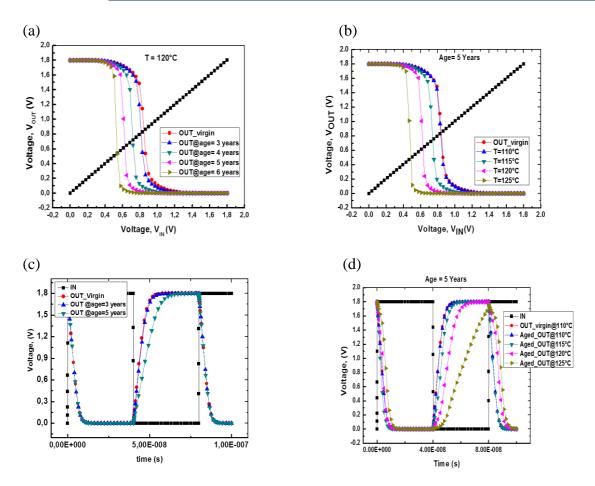

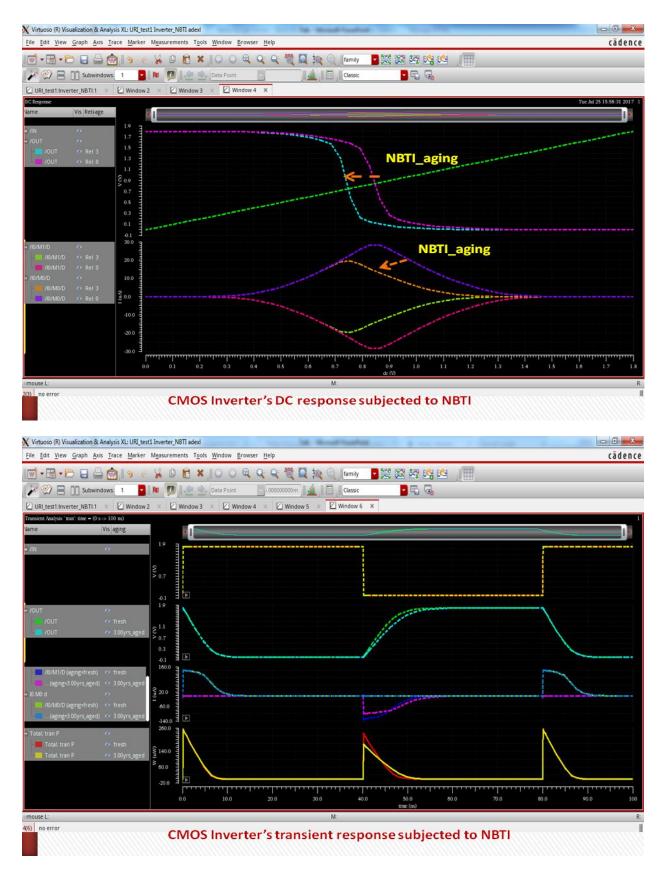

| Fig. 4.11 | Simulated CMOS Inverter DC and transient response subjected to NBTI (a) for different ages (b) at different temperatures                                      |

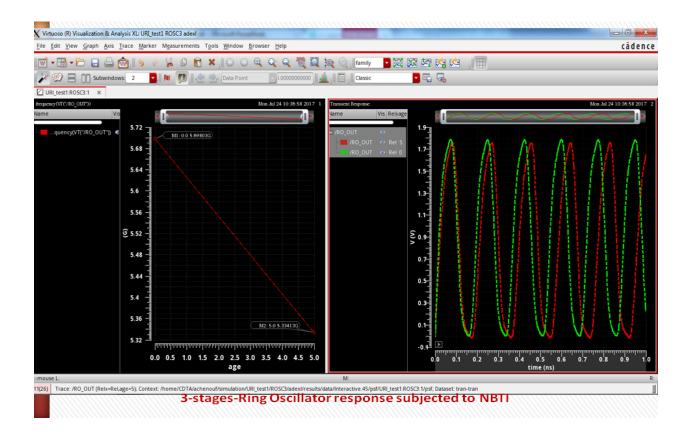

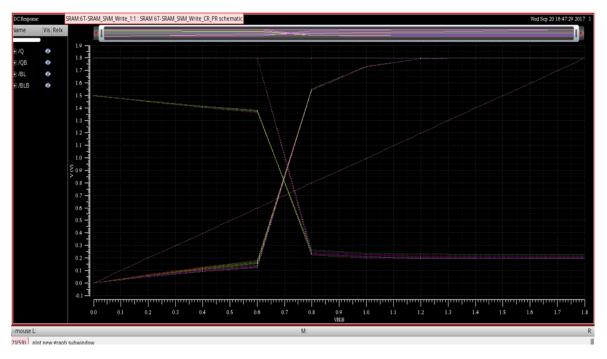

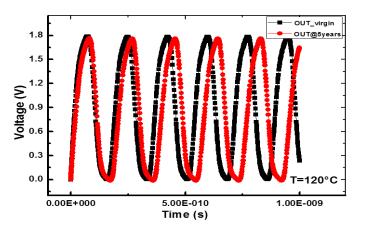

| Fig. 4.12 | Aging simulation of 15-Stages Ring Oscillator83                                                                                                               |

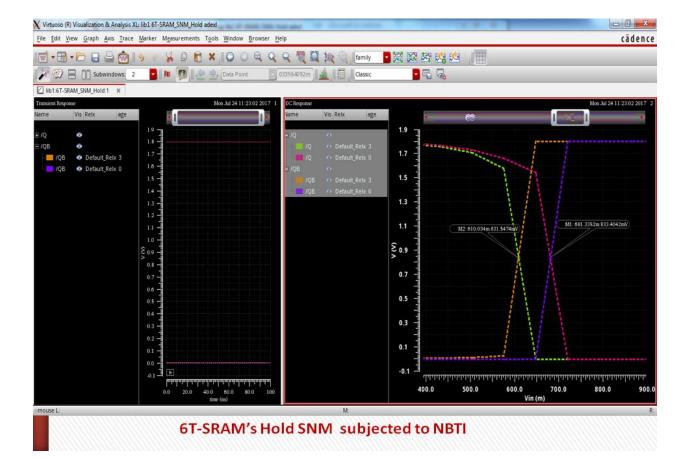

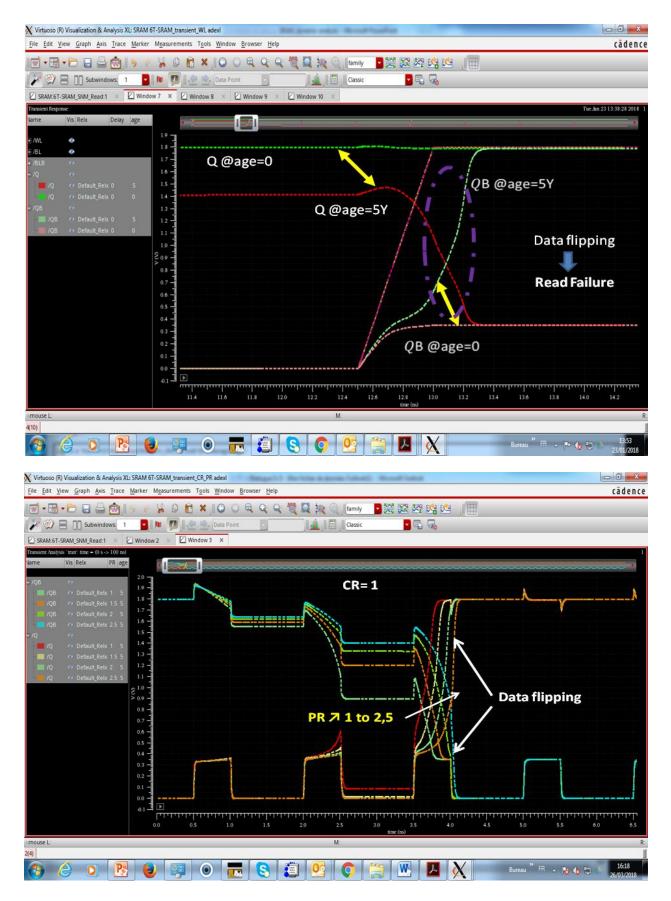

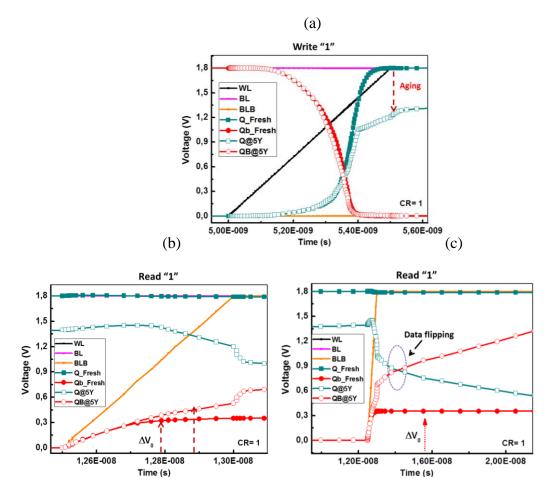

| Fig. 4.13 | 6T-SRAM aging simulation results                                                                                                                              |

| Fig. 4.14 | NBTI aware transistor sizing                                                                                                                                  |

| Fig. 4.15 | 6T-SRAM simulation setup for hold (a) read & write operations using n-curve method (b)                                                                        |

| Fig. 4.16 | The trend of hold SNM of the 6T-SRAM fresh and aged cell for different transistor sizes                                                                       |

## Figures List

| Fig. 4.17 The shift of Hold SNM of a symmetric 6T-SRAM cell subjected to NBTI for different transistor widths                                                              |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

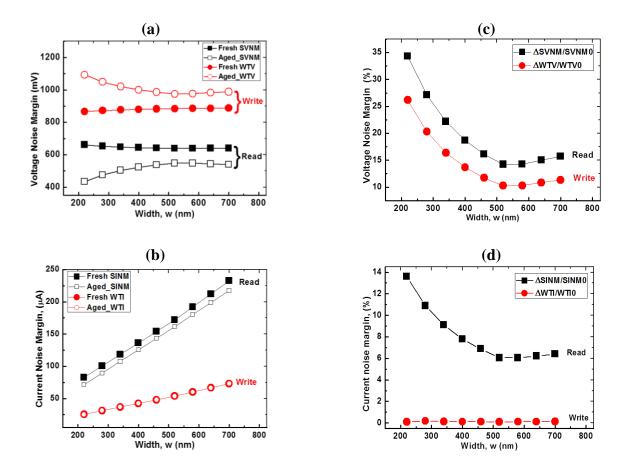

| Fig. 4.18 N-curves of fresh and aged 6T-SRAM for different transistors' width and the corresponding extracted read & write features                                        |   |

| Fig. 4.19 6T-SRAM read stability and write-ability features subjected to NBTI for different transistor widths                                                              |   |

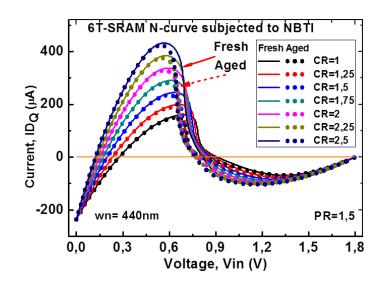

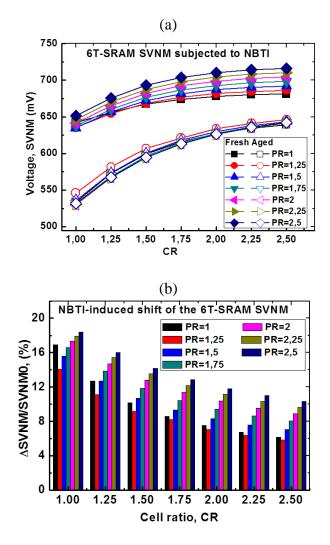

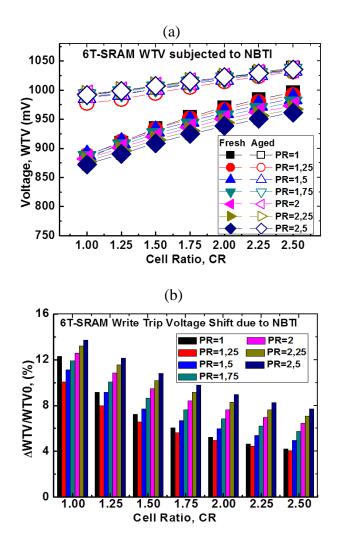

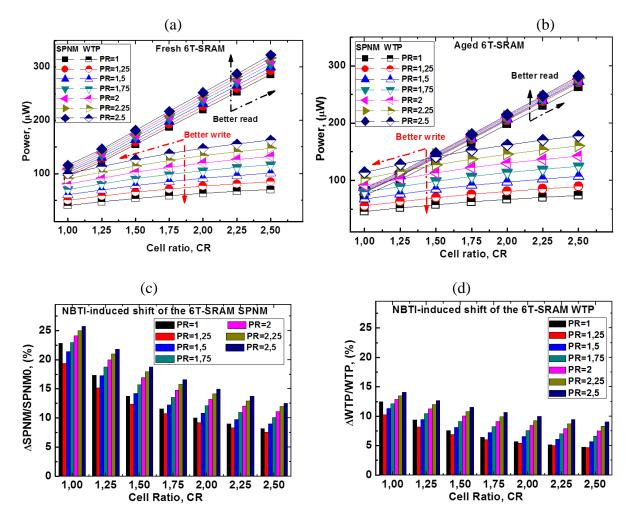

| Fig. 4.20 The 6T-SRAM n-curve subjected to NBTI for different cell ratios10                                                                                                | 1 |

| Fig. 4.21: The trend of 6T-SRAM cell read stability (the static voltage noise margin in (a) and i corresponding NBTI- induced shift ratio in (b)) with transistor sizing10 |   |

| Fig. 4.22 The trend of 6T-SRAM cell write-ability (the write trip voltage in (a) and i corresponding NBTI- induced shift ratio in (b)) with transistor sizing10            |   |

| Fig. 4.23. 6T-SRAM power metrics for read stability and write-ability degradation due NBTI a a function of cell sizing (CR and PR ratios)10                                |   |

## **CONTENTS**

| Acknowledg   | gment - |                                                     | i           |

|--------------|---------|-----------------------------------------------------|-------------|

| الملخص       |         |                                                     | iii         |

| Résumé       |         |                                                     | iv          |

| Abstract     |         |                                                     | ······ V    |

| List of Acro | onyms   |                                                     | wi          |

| Figures List | ······  |                                                     | ······ix    |

| Contents     |         |                                                     | ······ xiii |

| Chapter 1    | Intro   | duction                                             | 1           |

|              | 1.1     | Scope                                               | 4           |

|              | 1.2     | Motivations                                         | 4           |

|              | 1.3     | Contributions                                       | 5           |

|              | 1.4     | Thesis Outline                                      | 5           |

| Chapter 2    | Back    | ground                                              |             |

|              | 2.1     | Introduction                                        | 8           |

|              | 2.2     | Technology Scaling Impact On IC Variability         |             |

|              |         | 2.2.1 Process Voltage Temperature (PVT) variability |             |

|              |         | 2.2.2 Aging effects                                 |             |

|              |         | 2.2.2.1. Time-Dependent Dielectric Breakdown        |             |

|              |         | 2.2.2.2. Hot Carrier Injection                      | 18          |

|              |         | 2.2.2.3. Negative Bias Temperature Instability      |             |

|              | 2.3     | NBTI Modeling & Simulation                          | 20          |

| Device-level NBTI models 20               |

|-------------------------------------------|

| A. The R-D model21                        |

| B. Hole trapping-detrapping (T-D) model24 |

| C. Composed model 26                      |

| Circuit-level NBTI modeling29             |

|                                           |

| 2.4 | Desig | Design benchmarks                              |    |  |

|-----|-------|------------------------------------------------|----|--|

|     | 2.4.1 | The CMOS Inverter                              | 32 |  |

|     |       | A. The Inverter logic threshold voltage (Vinv) | 33 |  |

|     |       | B. The Inverter logic levels                   |    |  |

|     |       | C. The Inverter noise immunity                 |    |  |

|     | 2.4.2 | The 6T-SRAM                                    | 35 |  |

|     |       | A. Hold operation                              | 38 |  |

|     |       | B. Read operation                              | 38 |  |

|     |       | C. Write operation                             |    |  |

|     |       | D. 6T-SRAM stability                           |    |  |

| Chapter 3 | Circ | cuit-level NBTI Characterization                                                                         | 48 |

|-----------|------|----------------------------------------------------------------------------------------------------------|----|

|           | 3.1  | Introduction                                                                                             | 48 |

|           | 3.2  | Experimental setups for reliability analysis of the CMOS Inverter                                        | 51 |

|           |      | <ul><li>A. The circuit under test (CUT)</li><li>B. The test protocol for NBTI characterization</li></ul> | 51 |

|           |      | of the Inverter DC feaures<br>C. The test protocol for NBTI characterization                             | 52 |

|           |      | of the Inverter transient response                                                                       | 53 |

|           | 3.3  | NBTI impact on CMOS Inverter DC Features                                                                 | 54 |

|           | 3.4  | NBTI Impact on CMOS Inverter temporal Performance                                                        | 61 |

|           | 3.5  | Correlation between device-level and circuit-level NBTI                                                  | 64 |

|           | 3.6  | Conclusion                                                                                               | 67 |

| Chapter 4 | Agi  | ng-aware SRAM Design                                                                                     | 71 |

| <u> </u>  | 4.1  | Introduction                                                                                             |    |

| 7.1 |                                 |

|-----|---------------------------------|

| 4.2 | Aging Reliability Simulation 72 |

|                        |                           | 4.2.1 Our develope   | ed NBTI simulation interface on Cadence | 76                   |

|------------------------|---------------------------|----------------------|-----------------------------------------|----------------------|

|                        |                           | 4.4.2 Our NBTI de    | egradation model                        | 79                   |

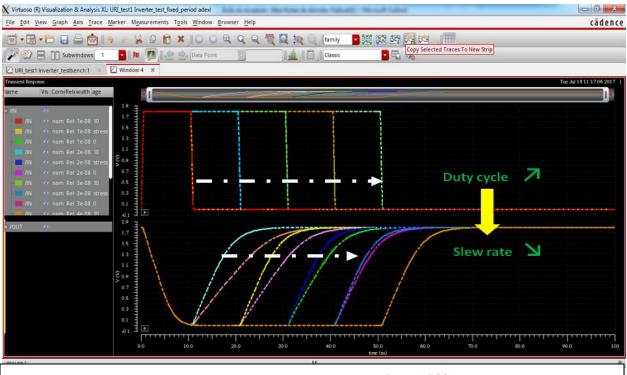

|                        |                           | 4.2.3 NBTI aging     | simulation examples                     | 81                   |

|                        | 4.3                       | NBTI Aging mitigat   | ion techniques                          | 85                   |

|                        |                           | 4.3.1 Guard-Bandi    | ng                                      | 85                   |

|                        |                           | 4.3.2 Power gating   | 5                                       | 87                   |

|                        |                           | 4.3.3 Duty-cycle tu  | ining                                   |                      |

|                        |                           | 4.3.4 Vth tuning     |                                         | 89                   |

|                        |                           | 4.3.5 Transistor siz | zing                                    | 90                   |

|                        | 4.4                       | Aging-Aware 6T-SF    | RAM Design Approach                     | 93                   |

|                        |                           | 4.4.1 Simu           | lation setup & NBTI model               | 94                   |

|                        |                           | 4.4.2 Simu           | lation results                          | 94                   |

|                        |                           | 4.4.2.1              | Hold operation                          |                      |

|                        |                           | 4.4.2.2              | Read & Write operations                 | 98                   |

|                        |                           | 4.4.2.3              | NBTI-aware Cell sizing                  |                      |

|                        | 4.5                       | Discussion           |                                         |                      |

|                        | 4.6                       | Conclusion           |                                         | 107                  |

| Chapter 5              | Conclusion & Perspectives |                      |                                         | 112                  |

| Appendix1<br>Appendix2 |                           |                      |                                         | ·····114<br>·····127 |

- 1.1 Scope

- **1.2** Motivations

- **1.3** Contributions

- 1.4 Thesis outline

The striking advance in both integrated circuit (IC) design flows and manufacturing processes have led to design very complex chips compacting more than 100 million of transistors on a few square millimeter area running at very high speed (see Fig. 1.1) [1]

Yet, this advent in the era of ultra large scale integration (ULSI) has brought new challenges to IC designers, in addition to the design perspective, validation, test, and reliability aspects have been taken into consideration. In fact, one of the major medium to long-term design issues, which have been reported by the ITRS for IC design, is their increasing variability [2].

IC performance variability can be due to the manufacturing process (lot-to-lot, die-to die, intra-die variations (spatial variation), to the environment, and to the intrinsic nature of the devices themselves and their wear-out (temporal variation) [3].

Fig. 1.1: Logic transistor density in Intel chips [1]

Governed by technology scaling, the important shrinking of the gate oxide makes circuits' devices to undergo a high vertical electric field. Moreover, the large scale integration has resulted

### **INTRODUCTION**

in a considerable heating of modern chips operating at high frequencies. Therefore, the high electric field and/or elevated temperature are exacerbating circuits' aging.

Due to wear-out effects, MOS devices' parameters shift, over time, altering thereby the performance and stability of the circuits integrating them, and which causes their failures to meet the specification targets for which they have been designed. Consequently, deep submicron CMOS ICs are prone to accelerate aging and make their lifetime shorter (see Fig. 1.2) [4]. Therefore, aging is among the critical reliability issues which faces present and future deeply downscaled CMOS devices, and the major aging concern is the so-called Bias Temperature Instability (BTI) [5].

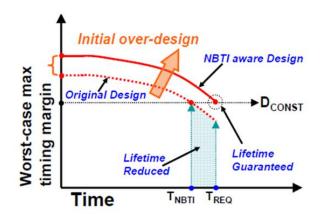

Fig. 1.2: Lifetime shrinking with technology scaling [4]

So far, lifetime reliability analysis has been mainly confined within the community of reliability physics at device level using accelerated stresses of single transistors. Failure criterions have been usually chosen as a shift of 10 % of  $I_{DS}$  or a shift of 30-50 mV of the transistor threshold voltage  $V_{th}$ . However, analyzing the device aging impact on circuit lifetime has not been well studied. Consequently, IC designers have been obliged to introduce large design margins called guard bands to avoid timing violation due to process and temporal reliability variations. Frequency reduction, supply voltage over-rating and transistors over sizing represent typical guard band concepts that designers adopt during the IC design step to mitigate aging effect appearing once the circuits are fabricated and during their lifetime [6]. However, Guard bands can be very pessimistic as they are based on the worst-case degradation and consequently

### **INTRODUCTION**

result in important overheads in silicon area and power consumption [6] [7]. Henceforth, addressing reliability issues during the early stages of IC design becomes more than an option to design reliable circuits including unreliable devices. Such design approach is known as Design For Reliability « DFR » (and Design-in-reliability) where reliability is considered as a design constraint as important as performance, area, and power consumption.

DFR is twofold research objective. One deals with the analysis/assessment of the aginginduced degradation on the circuit performance reliability while the other with combating/alleviating the predictable degradation and enhances the useful lifetime of the circuit (see Fig. 1.3) [4].

Hence, the research work conducted in this PhD thesis has been motivated by the willing to contribute to the reliability aware IC design. For this aim, we propose, on one hand, to migrate reliability analysis from device- to circuit-level to better assess the reliability degradation of circuits performance due to the aging of their device. On the other hand, we propose a circuit-level aging mitigation technique.

The circuit-level reliability study has been conducted through both experimental characterisation and simulation. In this latter, we have implemented an At<sup>n</sup> model of NBTI degradation in an industrial simulator using a unified reliability interface (URI).

The proposed circuit-level design-aware approach is based on transistor sizing technique to ensure SRAM cell reliability during its useful lifetime.

Fig. 1.3: Design for Reliability enhancing the circuits useful lifetime [4]

#### 1.1 Scope

To better understand the PhD project research work, two main points have been taken in consideration:

- Among the multiple variations and reliability issues to which are prone deep submicron ICs, we are interested in studying aging effects due to negative bias temperature instability (NBTI).

- Among the different types of integrated circuits (digital analog and mixed), we are interested in digital circuits and in particular in memory structures.

Such choices have been steered, on one hand, by the objectives of the R&D project: "Bias Temperature Stress" of the FCS team within Microelectronics division of CDTA and, on the other hand, by the following motivations.

#### **1.2 Motivations**

#### Why NBTI?

It has been shown that NBTI is the major reliability challenge when gate dielectric thickness becomes thinner than 2 nm [8] [9] [10], and that for gate oxide thinner than 4 nm, the shift of threshold voltage caused by NBTI for the PMOS is more important than that caused by hot-carrier induced degradation (HCI) of the NMOS transistor [11]. Furthermore, and contrary to HCI that occurs only during dynamic switching, NBTI is caused during static stress on the oxide even without current flow. Besides, compared to positive bias temperature instability (PBTI), it has been revealed that NBTI causes 2.3 times more degradation to the PMOS transistors than PBTI causes to the NMOS transistors [12].

#### Why SRAM?

CMOS SRAM (Static Random Access Memory) continues to be the technology of the choice for cache memory in high performance processors [13]. Yet, with the advances of process technology, SRAMs are more vulnerable to device parameters variability due to the process, the environment, and device aging. In fact, whatever the stored data, one of the SRAM cell's PMOS transistor is found to be under NBTI stress.

#### **1.3** Contributions

- 1. By migrating the analysis of NBTI degradation from device to circuit level, we have been able to show experimentally that:

- ✓ NBTI degradation is workload dependent and that the focus on the low-level details does not provide insight about the circuit degradation due to NBTI on a larger scale.

- ✓ The degradation induced by NBTI on the CMOS inverter performances under AC NBTI stress is less pronounced than under DC NBTI stress.

- ✓ The NBTI-induced degradation is voltage, temperature, and time dependent.

- ✓ A correlation between circuit-level and device-level NBTI revealed some aspects about the NBTI degradation.

- 2. By considering reliability during the design stage, we have been able to:

- ✓ Simulate and analyze circuits' behavior under aging effects and assess the induced degradation on the circuits' performance and reliability.

- ✓ Propose a design technique to mitigate NBTI degradation in 6T-SRAM. The technique is based on transistor sizing. It ensures better cell stability in terms of hold and read noise margins and write-ability to enhance its lifetime.

#### **1.4** Thesis outline

Following this introductory chapter, three chapters come expanding the statement made here about reliability aware IC design circuits. Accordingly, chapter 2 presents the background of the variability problems that have emerged with increasing CMOS technology scaling and the challenges and implication of these new process technologies to IC design. A particular interest is given to NBTI as one of the main reliability issues in deep submicron ICs. We review its analysis and modelling at different design flow abstraction levels. Besides, we present the basics of two CMOS circuits which served as benchmarks for circuit-level aging analysis and NBTI mitigation conducted in this work. Subsequently, chapter 3 presents our experimental analysis of NBTI degradation at circuit level where we report the results of CMOS inverter behavior under DC and AC NBTI stresses, and we draw some conclusion on the correlation between the degradation at device-and circuit-level. Being aware of the NBTI degradation, we present in chapter 4 a DFR approach to mitigate NBTI degradation in the 6T-SRAM. We show how to

optimize its design for a better reliability. Finally, we end-up with concluding remarks and perspectives for future work.

It is worth to note that chapters 3 and 4 are based respectively on the following publications:

- A. Chenouf, B. Djezzar, A. Benabdelmoumene and H. Tahi, "On the Circuit-Level Reliability Degradation Due to AC NBTI Stress," in IEEE Transactions on Device and Materials Reliability, vol. 16, no. 3, pp. 290-297, Sept. 2016, doi: 10.1109/TDMR.2016.2578040.

- A. Chenouf, B. Djezzar, H. Bentarzi and A. Benabdelmoumene, "Sizing of the CMOS 6T-SRAM cell for NBTI ageing mitigation," in IET Circuits, Devices & Systems, vol. 14, no. 4, pp. 555-561, 7 2020, doi: 10.1049/iet-cds.2019.0307.

#### References

- [1] R. Courtland. (2017) Intel Now Packs 100 Million Transistors in Each Square Millimeter. *IEEE Spectrum*. Available: https://spectrum.ieee.org/nanoclast/semiconductors/processors /intel-now-packs-100-million-transistors-in-each-square-millimeter

- [2] IRDS. (2018). *Update More Moore*. Available: https://irds.ieee.org/images/files/pdf/2018/ 2018IRDS\_MM.pdf

- [3] S. Ghosh, "Effect of Variations and Variation Tolerance in Logic Circuits," in *Low-Power Variation-Tolerant Design in Nanometer Silicon*, S. Bhunia and S. Mukhopadhyay, Eds., ed Boston, MA: Springer US, 2011, pp. 83-108.

- [4] V. Huard, S. Mhira, F. Cacho, and A. Bravaix, "Enabling robust automotive electronic components in advanced CMOS nodes," *Microelectronics Reliability*, vol. 76-77, pp. 13-24, 2017/09/01/ 2017.

- [5] T. Nigam and A. Kerber, "Enabling Scaling of Advanced CMOS Technologies: A Reliability Perspective," in 2015 IEEE Computer Society Annual Symposium on VLSI, 2015, pp. 199-199.

- [6] K. Jeong, A. B. Kahng, and K. Samadi, "Impact of Guardband Reduction On Design Outcomes: A Quantitative Approach," *IEEE Transactions on Semiconductor Manufacturing*, vol. 22, pp. 552-565, 2009.

- [7] L. Zhang and R. P. Dick, "Scheduled voltage scaling for increasing lifetime in the presence of NBTI," in *2009 Asia and South Pacific Design Automation Conference*, 2009, pp. 492-497.

- [8] S. P. Park, K. Kang, and K. Roy, "Reliability Implications of Bias-Temperature Instability in Digital ICs," *IEEE Design & Test of Computers,* vol. 26, pp. 8-17, 2009.

- [9] R. Degraeve, M. Aoulaiche, B. Kaczer, P. Roussel, T. Kauerauf, S. Sahhaf, and G. Groeseneken, "Review of reliability issues in high-k/metal gate stacks," in *2008 15th International Symposium on the Physical and Failure Analysis of Integrated Circuits*, 2008, pp. 1-6.

- [10] L. L. Lewyn, T. Ytterdal, C. Wulff, and K. Martin, "Analog Circuit Design in Nanoscale CMOS Technologies," *Proceedings of the IEEE*, vol. 97, pp. 1687-1714, 2009.

- [11] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai, and T. Horiuchi, "The impact of bias temperature instability for direct-tunneling ultra-thin gate oxide on MOSFET scaling," in 1999 Symposium on VLSI Technology. Digest of Technical Papers (IEEE Cat. No.99CH36325), 1999, pp. 73-74.

- [12] S. Khan, S. Hamdioui, H. Kukner, P. Raghavan, and F. Catthoor, "BTI impact on logical gates in nano-scale CMOS technology," in 2012 IEEE 15th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), 2012, pp. 348-353.

- [13] M. Marinella, "The future of memory," in *2013 IEEE Aerospace Conference*, 2013, pp. 1-11.

- 2.1 Introduction

- 2.2 Technology scaling impact on variability

- 2.3 NBTI modeling & simulation

- 2.4 Design benchmarks

#### 2.1 INTRODUCTION

In 1965, Gordon E. Moore predicted that the number of transistors that can be packed into an integrated circuit (IC) will double every year for the next ten years [1]. That prediction called afterwards "Moore law" has moved the innovation in the direction of integrating more devices on a single chip which sets the pace for the modern digital revolution. From careful observation of an emerging trend, Moore extrapolated that computing would dramatically increase in power, and decrease in relative cost, at an exponential pace [2].

The ability to improve performance while decreasing power consumption has made the complementary metal oxide semi-conductor (CMOS) architecture the dominant technology for integrated circuits. As such, CMOS technology downscaling has been needed to meet more requirements of speed, complexity, circuit density, power consumption and ultimately the cost imposed by many advanced applications.

Today's applications such as high performance computing, mobile computing, and autonomous sensing and computing (Internet of things (IoT)) (see Fig. 2.1) drive the requirements of "More Moore" technologies to bring the PPAC value from node-to-node scaling every 2-3 years[3]:

- (P)erformance: >15% more maximum operating frequency at constant energy,

- (P)ower: >30% less energy per switching at a given performance,

- (A)rea: >30% area reduction,

- (C)ost: < 30% wafer cost 30-40% less die cost for scaled die.

Fig. 2.1: Big data and instant data [3]

This impressive progress has been made possible thanks to the technology scaling.

Historically, MOS scaling has been achieved by following two principles: constant field scaling and constant voltage scaling. The story behind constant field technology scaling has its roots in the 1970s when IBM was searching for a technology to fill the cost/performance "file gap" between movable head magnetic disks (which had low cost/bit but high latency time) and random access main memory (RAM) which had high performance but high cost/bit) for transaction based systems [4]. Bob Dennard, among others who were working on alternatives, proposed a preliminary design based on his 1-Transitor- DRAM cell. Yet, many advances were required to achieve the technical and cost goals such as shrinking the dimensions on the chip to about 1 $\mu$ m, improving the yield to allow larger chips and higher resolution lithography, and providing a means of sensing the very small signals on the bit lines [4]. Once the problems related to the lithography, the process and the sensor were resolved, a 5X shrink of the existing technology was needed to achieve 1 $\mu$ m dimensions. At that time, Bob Dennard and Dale Critchlow decided, that rather than designing the 1 $\mu$ m technology from scratch, they would scale from some wellcharacterized devices which had channel lengths of about 5  $\mu$ m and could be operated along with voltages up to 20 V. They observed that if the electric fields were kept constant, the reliability of

### **BACKGROUND**

the scaled devices would not be compromised. The key to that scaling was to scale down all dimensions including wiring and depletion layers and all voltages including threshold voltage. Consequently, Dennard and Fritz Gaensslen derived the constant-field scaling theory and its limitations (see Fig. 2.2) known as the "Scaling paper" [5] and which was presented at IEDM 1972 and published in IEEE Journal of Solid-State Circuits in 1974 [5]. It was this realization of scaling theory and its usage in practice which has made possible the better-known "Moore's Law". In 1975, with more data, Moore revised the estimate of the doubling period of devices to be roughly two years [2].

New depletion thickness =

$$x'_D = \sqrt{\frac{2\varepsilon_{si}(V/\alpha + \Psi)}{q(\alpha N_A)}} \cong \frac{x_D}{\alpha}$$

New threshold voltage =  $V'_t = \frac{1}{\varepsilon_{ox}} \left(\frac{t_{ox}}{\alpha}\right) \left[ \left( -Q_{eff} + \sqrt{2\varepsilon_{si}q(\alpha N_A)\left(\frac{V_{s-sub}}{\alpha}\right)} + \Psi_s \right) \right] + \left( \Delta w_f + \Psi_s \right) \cong \frac{v_b}{\alpha}$

New current =

$$I'_D = \frac{\mu \varepsilon_{ox}}{t_{ox}/\alpha} \left(\frac{W/\alpha}{L/\alpha}\right) \left(\frac{V_g - V_t - V_d/2}{\alpha}\right) \left(\frac{V_d}{\alpha}\right) = \frac{I_D}{\alpha}$$

Where:  $x_D$  is the depletion thickness,  $\varepsilon_{si} \varepsilon_{ox}$  the dielectric constant for silicon and silicon dioxide, V the supply voltage,  $\alpha$  the scaling factor, q the electron charge,  $N_A$  the substrate accepter density,  $t_{ox}$  the gate oxide thickness,  $Q_{eff}$  the effective oxide charge Vs-sub the source voltage relative to substrate,  $\Psi$ s the band bending in silicon at the onset of strong inversion for zero substrate voltage,  $\Delta w_f$  the work function difference between gate and substrate,  $\mu$  the mobility, W and L the transistor width and length, Vg, Vd are the gate and drain voltages and Vt the transistor threshold voltage, and  $I_D$  the drain current.

#### Fig. 2.2: Technology scaling theory of Dennard [4]

By applying the scaling theory, the structure of the next-generation process could be known in advance, easing the process development task and the performance of circuits in the next generation could be predicted in a straightforward fashion from that in the present generation.

It is worth to note even though the device density is increased by  $\kappa^2$ , the power density remains constant due to the reduced power dissipation per device by  $\kappa^2$  (see table 1). Following field constant scaling (in other words: the full scaling), ICs became smaller by a factor of ~ 0.8

corresponding to a density increase of 56%, making the number of the integrated transistors to roughly double every 2 years to exceed, recently, 100 million transistors/mm<sup>2</sup> (see Fig. 2.3) [6]. Table 1 Scaling results for device characteristics

| Performance of the device            | Symbol             | Expression                                                   | Scaling factor |  |

|--------------------------------------|--------------------|--------------------------------------------------------------|----------------|--|

| Number of device per unit area       | N <sub>tr</sub>    | α 1/(W.L)                                                    | $k^2$          |  |

| Gate oxide capacitance per unit area | C <sub>ox</sub>    | $\alpha 1/t_{ox}$                                            | k              |  |

| Gate oxide capacitance               | C <sub>gate</sub>  | C <sub>ox</sub> .W.L                                         | 1/k            |  |

| Drain saturation current             | $I_D$              | $\frac{1}{2}\mu C_{ox}\cdot \frac{W}{L} (V_{gs} - V_{th})^2$ | 1/k            |  |

| Intrinsic delay per device           | τ                  | $C_{gate} \cdot V_{DD} \cdot I_D$                            | 1/k            |  |

| Power dissipation per device         | Р                  | $V_{DD} \cdot I_D$                                           | $1/k^2$        |  |

| Power density                        | $\mathbf{P}_{den}$ | P.N <sub>tr</sub>                                            | 1              |  |

| Power delay product                  | PDP                | Ρ. τ                                                         | $1/k^3$        |  |

Fig. 2.3: The trend of the density of logic and 6T-SRAM chips over the last 3 decades [6].

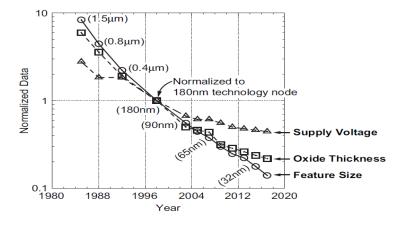

Unfortunately, a problem came out with constant field scaling made supply voltage scaling, from a generation to another, undesirable from a system point of view. Besides, interfacing CMOS with 5 V TTL technologies imposed the supply voltage to be maintained at 5V for many years. This has led to a constant voltage scaling where all dimensions but not voltages are scaled (see Fig. 2.4) [7]. The obtained results were quite different. In fact, the circuits became faster by  $k^2$ , but the power/unit area increases by  $k^3$ . Consequently, constant voltage scaling had brought new challenges and issues [7].

Fig. 2.4: Scaling trends of technology node, oxide thickness, and supply voltage [7]

#### 2. 2 TECHNOLOGY SCALING IMPACT ON IC VARIABILITY

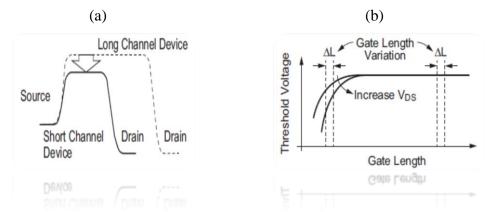

Governed by technology scaling, and in order to achieve high current drive (see table 1) and attain low power operation, the gate oxide thickness has been aggressively reduced. Yet, going to these ultra-scaled CMOS devices also brings some drawbacks. The problem at small gate lengths is that the drain voltage reduces the barrier height at the source, which causes a low source-to-channel barrier height even with the gate voltage off, and hence leads to the decrease of the threshold voltage ( $V_{th}$ ) and an undesirable large off-state leakage. This phenomenon is referred to as drain-induced barrier lowering (DIBL) (see Fig. 2.5 (a)) [7]. This is due to the phenomenon known as short channel effect (SCE) (see Fig. 2.5)[7]. SCE stands for the fact that  $V_{th}$  of the scaled transistor exhibits gate length dependence [7]. SCE makes  $V_{th}$  to vary as the channel length and applied voltage change, thereby causing the degradation of circuit performance.

On the other hand, the exponential increase in the gate leakage current when scaling the gate

Fig. 2.5: Short channel tranasitors associated effects: DIBL in (a) and SCE in (b) [7]

oxide thickness of CMOS transistors, forced device engineers to introduce new gate materials with a higher dielectric constant compared to traditional  $SiO_2$  or SiON gate dielectrics [8]. This allows further increase of the gate oxide capacitance while keeping the physical gate thickness sufficiently large [8].

Actually, scaling targets have driven the industry toward a number of major technological innovations, including material and process changes such as high- $\kappa$  gate dielectrics and strain enhancement, new structures such as gate-all-around (GAA); alternate high-mobility channel materials, and new 3D integration schemes allowing heterogeneous stacking/integration [3]. Unfortunately, the introduction of new materials and devices associated with the further reduction of the lateral transistor dimensions reduces circuit reliability [9].

In the general sense, reliability is the "ability of an item to perform a required function under stated conditions for a stated period of time". As such, reliability is an important requirement for almost all users of integrated circuits. This challenge is exacerbated due to (1) aggressive scaling, (2) the introduction of new materials and devices, (3) more demanding mission profiles (higher temperatures, extreme lifetimes, high currents), and (4) increasing constraints of time and money [3].

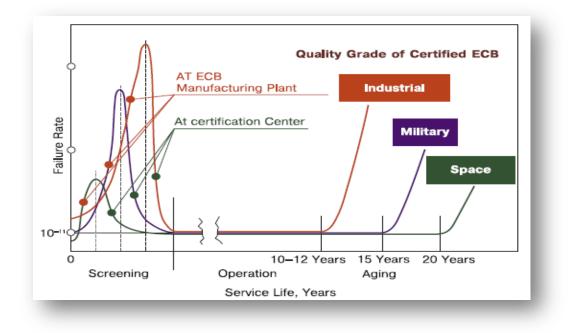

Reliability requirements are highly application dependent. Applications in harsh environments that require higher reliability levels, and/or longer lifetimes are more difficult than the mainstream office and mobile applications [10]. In fact, safety-critical applications, such as sensor interfaces embedded to monitor vital parameters in a car or biomedical products such as a pacemaker, require reliable circuit operation with a lifetime of ten to twenty years [10]. In such applications, circuits endure large temperature variations and electromagnetic interferences. Moreover, when they are used in harsh environment conditions such as those on satellites or in nuclear reactors, ICs suffer from radiation effects. Such applications impose more severe reliability requirements on ICs compared to consumer electronics where a short time to market is required to survive in a very competitive market. Despite the applications where they are used, circuits always need to operate correctly over their lifetime (see Fig. 2.6) [10].

Fig. 2.6: Electronic components failure versus service life [10]

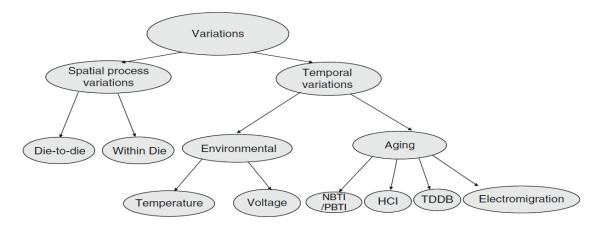

The reliability of ICs can be affected by: 1) process variations, during their manufacturing, 2) temporal variations of the devices they enfold, caused by the fluctuations of the voltage and temperature due to high density of the chips, their switching activities, and noise integrity of their different blocks during their runtime, and to 3) their wear-out mechanisms at the end of their useful lifetime. As such, the device parameters variations can be spatial (t=0), or time dependent (t>0). The taxonomy of variations of semiconductor device parameters is shown on Fig. 2.7[11].

Fig. 2.7: Taxonomy of variations in integrated circuits [11]

#### 2.2.1. Process Voltage Temperature (PVT) variability

Due to the technology process, device parameters can vary globally (inter-die) from: lot-tolot, wafer-to-wafer, die-to-die, or locally (intra-die) between adjacent devices within the same die. Local variability results in parametric variations of identically designed transistors across a short distance known as mismatch while global variability causes a shift in the mean value of design parameters such as channel length (L), channel width (W), gate oxide thickness (Tox), resistivity or doping density, and body effect [12, 13].

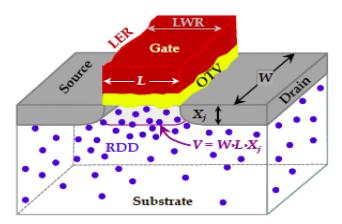

Local variability can be caused by optical proximity correction (OPC), layout-induced strain and well-proximity effects, random dopant fluctuation (RDF) effects, line edge and width roughness (LER and LWR), fixed charges in the gate dielectric and interface roughness (see Fig. 2.8) [13].

While process variations are immediately noticeable just after production and are fixed in time, temporal unreliability effects, on the other hand, they are time varying and change depending on operating conditions such as the operating voltage, temperature, switching action, presence and activity of neighboring circuits. Temporal variations can be due to the environment or to aging effects.

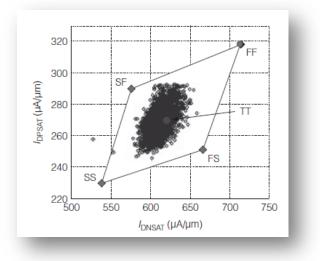

In circuit design, circuits are usually simulated with PVT corners to account for both process and environment induced variability. For the process variability, four worst-case corners are modeled to know: SS, FF, SF, and FS. On one hand, SS stands for slow nMOS and slow pMOS while FF stands for fast nMOS and fast pMOS. On the other hand, FS stands for fast nMOS and

Fig. 2.8: Source of local variations in CMOS devices [13]

slow pMOS while SF stands for slow nMOS and fast pMOS. The first two corners model the worst case for speed and power for analog applications whereas the two other corners model the worst-case `1,' the worst-case `0' for digital applications (see Fig. 2.9) [12].

Fig. 2.9: Process corners [12]

For voltage fluctuations, circuits are usually simulated to account for fluctuations of the supply voltage within  $\pm 10\%$  of the nominal voltage V<sub>DD</sub>. For temperature fluctuations, a range of -40°C-125 °C is considered.

Thus, IC designers being aware of device parameters variability, due to process and environment, still need to know about the variability caused by wear out effects and its impact on the useful life of their circuits.

#### 2.2.2. Aging effects

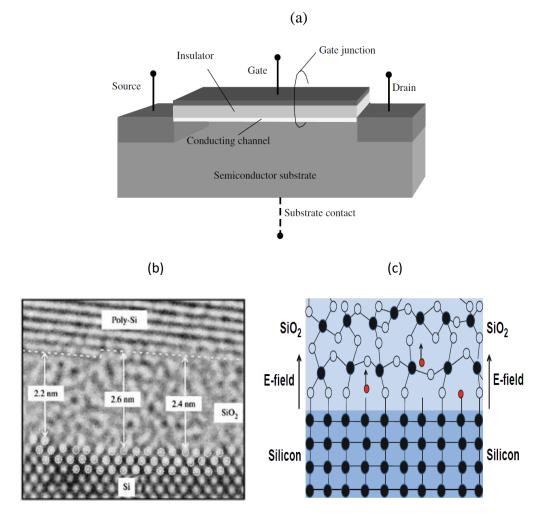

The correct operation of a MOS transistor (see Fig. 2.10) relies on the insulating properties of the dielectric layer below the gate electrode of the transistor (the insulator in bulk CMOS is  $SiO_2$ ). The stability of the  $Si/SiO_2$  interface is of a great importance.

The two most critical factors that have been limiting the scaling of the thickness of  $SiO_2$  are: the gate leakage current which is increasing the standby power consumption and the intrinsic reliability of the oxide.

Fig. 2.10: Schematic illustration of a field effect transistor (FET) in (a). pMOS-FET with silicon dioxide (SiO<sub>2</sub>) as insulator for CMOS bulk technology in (b source IBM), interface states roughness (c)

As such, failure mechanisms associated with the MOS transistor also known as front-end of line (FEOL) reliability continue to be one of the main reliability challenges for ICs and systems [3]. FEOL failure mechanisms are influenced by the operating conditions of the circuit including temperature, voltage bias, and current density. The failure could be caused by either breakdown of the gate dielectric or threshold voltage change beyond the acceptable limits. The main IC aging phenomena observed in sub-90nm CMOS technologies are: hot carrier injection (HCI), time-dependent dielectric breakdown (TDDB), and bias temperature instability (BTI) [11].

#### 2.2.2.1. Time-Dependent Dielectric Breakdown

The correct operation of a MOS transistor relies on the insulating properties of its dielectric material. Each dielectric material has a maximum electric field that can bear, and when this limit is reached, the oxide breaks down and the device fails [11]. This is known as hard breakdown. Before the hard breakdown happens, the device might undergo a soft breakdown. This latter leads to a partial loss of the dielectric properties, resulting in a small increase of the gate current and a significant increase of the gate current noise [14].

It is generally assumed that due to the applied voltage or the resulting tunneling electrons create defects in the volume of the oxide film, these defects accumulate with time and eventually reach a critical density triggering for a sudden loss of dielectric properties. A flow of current produces a large localized rise in temperature leading to permanent structural damage in the silicon-oxide film [15]. The defects generation rate (which strongly depends on the stress conditions) and the critical defect density (which mainly depends on the oxide thickness and area) are the main elements required to relate the generation of defects to the breakdown [15]. The time to a first breakdown event is decreasing with scaling. However, depending on the circuit it may take more than one soft breakdown to produce an IC failure, or the circuit may function for longer time until the initial "soft" breakdown spot has progressed to a "hard" failure [14].

#### 2.2.2.2. Hot Carrier Injection

Hot carriers are particles (electrons and holes) with a high kinetic energy which can be accelerated in a high electric field (in the pinch-off region during saturation mode). Hot carriers can gain enough energy and be injected into the gate oxide, then they cause interfacial damage and introduce instabilities in the electrical characteristics of a MOSFET device [16, 17]. They can lead to shifts in V<sub>th</sub>, transconductance (g<sub>m</sub>), and the drain current I<sub>D</sub>. The  $\Delta V_{th}$  and  $\Delta I_D/I_D$  usually follow a power law time dependence with stress (At<sup>n</sup>). The time exponent n of HCI degradation is found to be in the range of [0.5-0.7] for long channel bulk CMOS and at V<sub>G</sub> = V<sub>D</sub>/2 when the impact ionization is maximal, and in the range [0.2-0.3] for short channel devices where the hot carriers injection (HCI) condition changes to be V<sub>G</sub> = V<sub>D</sub>[18].

#### 2.2.2.3. Negative Bias Temperature Instability

Negative bias temperature instability (NBTI), is usually observed in p-channel metal-oxidesemiconductor field-effect transistors (pMOSFETs) when they are stressed with negative gate

voltage at elevated temperature [19] [20] . NBTI has been important when threshold voltages have been scaled down [19] and silicon oxy-nitride has replaced silicon dioxide in order to reduce Boron penetration in the gate insulator [21] [22]. Burn-in options (usually conducted at 125°C with +30 %  $V_{DD}$ ) to enhance reliability of end-products may be impacted, as it may accelerate negative bias temperature instability (NBTI) shifts [23, 24] . Introduction of high- $\kappa$  gate dielectric may impact on both the insulator failure modes (e.g., breakdown and instability) as well as the transistor failure modes such as hot carrier effects, positive and negative bias temperature instability. The replacement of polysilicon with metal gates also impacts insulator reliability, raises new thermo-mechanical issues and makes NBT-stress lifetime of copper/low-k interconnects shorter than that of aluminum/Si0<sub>2</sub> interconnects. The simultaneous introduction of high- $\kappa$  and metal gate (HK/MG) makes it even more difficult to determine reliability mechanisms [25] [26]. In fact, the introduction of HK/MG has been associated with the emergence of positive bias temperature instability (PBTI) aging mechanism affecting on nMOS transistors.

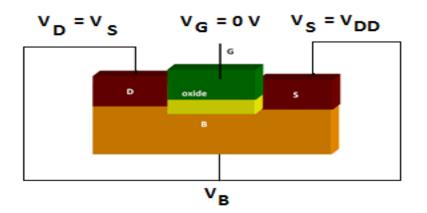

NBTI is triggered in negatively biased p-channel MOSFETs within a CMOS inverter as shown in Fig. 2.11 or with (VG < 0 V, VS = VD = 0 V) configuration during accelerated stress. In fact, typical stress temperatures lie within the 100–250 °C range with the oxide electric fields

Fig. 2.11: NBTI configuration of the pMOS transistor within CMOS Inverter

typically below 6 MV/cm, i.e., electric fields beyond this value may lead to hot carrier degradation [19].

NBTI has been associated with the Si–H bond breaking along the silicon-oxide interface leading to interface traps and positive charge in the oxide [20]. Under NBTI stress, carriers

(holes) injected from the channel are captured by the traps. In large devices with many traps, this results in a well-defined change in the threshold voltage ( $\Delta V_{th}$ ), which is characterized by a positive shift in the absolute value of the pMOS threshold voltage  $|V_{th}|$  [27] leading to a decrease in drain current  $I_{DS}$  and consequently to the performances degradation of CMOS integrated circuits [20] [28].

#### 2.3 NBTI MODELING & SIMULATION

To design an IC, designers usually perform many circuit simulations, make design changes and apply optimizations to evaluate the performance of their circuits before implementation using silicon materials. Therefore, it would be inconceivable to bypass the analysis of the circuit until it is fabricated and rely exclusively on the physical test of manufactured circuit to discover the errors of non-compliance of performance to specifications. Yet, it has been mainly the way in which the reliability of ICs has been treated so far. In fact, the non-deterministic of device parameters with scaling prevent circuits to fulfill their function. Hence, to improve design predictability to properly meet its specification during its lifetime, accurate modeling, and simulation tools for reliability are indispensable for both digital and analog circuits [29]. We review in the following sections NBTI aging models and simulation tools dedicated to digital circuits.

#### 2.3.1.1. Device-level NBTI models

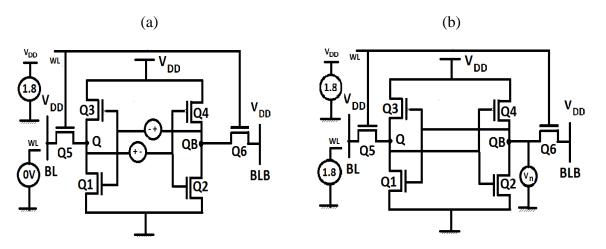

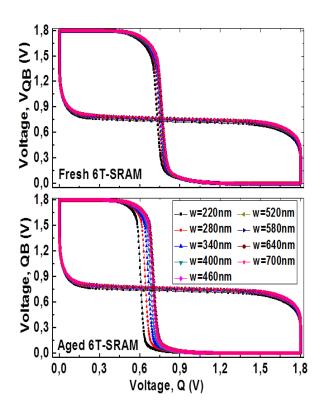

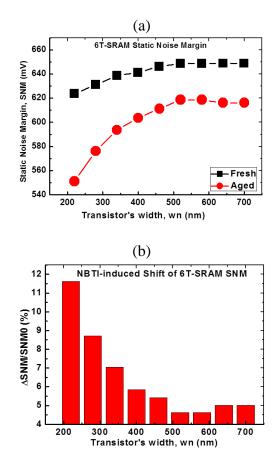

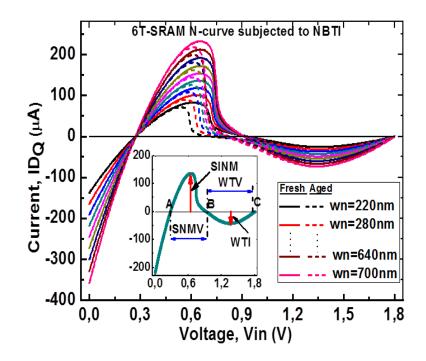

At device level, despite the tremendous effort made by scientists on how to properly measure the effect and to explain the microscopic behavior of NBTI, no consensus has been formed yet on the physical mechanisms governing the kinetics of NBTI (see Fig. 2.12 [30]) during stress and recovery, in large and small area devices [31-35]. Nevertheless, two classes of models have emerged as the strongest competitors: the reaction-diffusion (R-D) model [36] and hole trapping/detrapping (TD) model to explain the phenomena [37].