## People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

**University M'Hamed BOUGARA – Boumerdes**

# Institute of Electrical and Electronic Engineering Department of Electronics

Final Year Project Report Presented in Partial Fulfilment of

the Requirements of the Degree of

# 'MASTER'

# In Electrical and Electronic Engineering

**Option: Computer Engineering**

Title:

# FPGA-based Arabic LCD Display Controller IP Design

Presented By:

- RAHIL Lillia

- AGGOUNE Khedidja

Supervisor:

**Dr. A.KHOUAS**

Registration Number:...../2016

### Acknowledgement

First and foremost, we would like to thank **Almighty ALLAH** for giving us the courage and the determination, as well as guidance in conducting this project study, despite the difficulties.

Our sincere thanks and gratitude goes to our supervisor "**Dr. KHOUAS**", for proposing and directing this work.

Next, we owe a special thanks to the **members of the jury** who have agreed to evaluate our work.

Finally; we would like to thank all those who helped us accomplish this modest work, near or far.

## RAHIL & AGGOUNE

## Dedication

"To the light of my world, my precious dad, To the apple of my eye, my loving mom, To my brother and sisters, To my special friend who has never left my side, To all the ones who helped me accomplish this work, To all friends and computer classmates This work is dedicated."

## Dedication

"I am deeply grateful to my family, especially my parents, brothers and sister, you are the light that shows me the way.

To the memory of my grandmother I dedicate this work, and to all my friends over the world."

Khedidja

#### Abstract

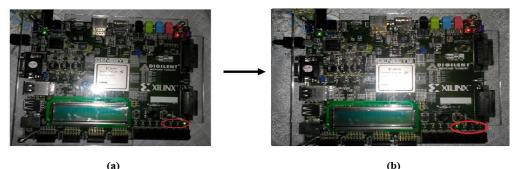

A 2x16 character Liquid Cristal Display (LCD) is one of the most common Input/Output (I/O) devices. It allows designers to communicate with the outside world. Alphanumeric LCD can display English and some other special characters. However, Arabic characters cannot be displayed since the Arabic fonts are not embedded in the LCD controller, thus there are no corresponding American Standard Code for Information Interchange (ASCII) codes for it. To allow Arabic display on an LCD module and reduce designs' time, we suggest to create an Intellectual Property (IP) core for Arabic character LCD display controller. The design was done by creating a block diagram of the LCD controller and interface it to a clock divider module and an IP core memory namely a Block Random Access Memory (BRAM). The whole design was initialized and tested using VHDL codes. The LCD initialization is done using some specific commands. These commands allow Arabic characters to be generated and read from the Character Generator RAM (CG RAM) which is one of the controller's memory regions. The complete LCD module was described and synthesized using Xilinx Integrated Synthesis Environment (ISE) design suite tools, and implemented and tested using Xilinx Virtex 5 Field Programmable Gate Array (FPGA) and Digilent Genesys board. After creating the needed design, a simulation of each component has been made using a test bench VHDL code. However, Displaying Arabic characters using FPGA couldn't be achieved due to lack of time and some problems, mainly changing the FPGA board, wasting time in working on some other Xilinx tools and lack of the needed documentations. Moreover, once we implemented the design LCD displayed just a cursor blinking to show clearly that the generated character couldn't be displayed .It has not been well introduced in the CGRAM of the controller. What we suggest is to try to reuse those commands and test it once again since the same method works once we tested it on a microcontroller.

## Table of contents

| Acknowledgementi                                |

|-------------------------------------------------|

| Dedicationii                                    |

| Dedicationiii                                   |

| Abstractiv                                      |

| List of figuresvii                              |

| List of tablesviii                              |

| Acronymsix                                      |

| CHAPTER I: Introduction to FPGA                 |

| I.1. Introduction                               |

| I.2. Field Programmable Gate Array              |

| I.2.1. Overview of general FPGA device          |

| I.2.2. FPGA's applications                      |

| I.2.3. Important Factors for comparing FPGAs    |

| I.2.4. FPGA Xilinx Virtex 5 LXT family          |

| I.3. Hardware development platform and tools    |

| I.3.1. Hardware development platform            |

| I.3.2. Hardware development tools               |

| a. ISE design suite                             |

| b. Design flow7                                 |

| I.4. IP core                                    |

| I.4.1. Advantages and Disadvantages of IP cores |

| I.4.3. IP cores type                            |

| I.4.4. Core Generator software tool             |

| a. Overview9                                    |

| b. Block Memory Generator (BMG)10               |

| I.6. Conclusion                                 |

| CHAPTER II: Character LCD Display Background13  |

| II.1. Introduction                              |

| II.2. Character LCD display                     |

| II.2.1. Overview of an LCD                      |

| II.2.2. LCD pins configuration14                |

| II.2.3. LCD controller                          |

| II.2.4. LCD control and display commands        |

| II.2.5. LCD display modes                       |

| II.3. conclusion                                |

| CHAPTER III: LCD Controller Design              |

| III.1. Introduction                             |

| III.2. LCI         | O controller design                           | 23 |  |  |  |  |  |

|--------------------|-----------------------------------------------|----|--|--|--|--|--|

| III.2.1.           | III.2.1. Design of LCD module                 |    |  |  |  |  |  |

| III.2.2.           | Block memory LCD interfacing                  |    |  |  |  |  |  |

| a.                 | a. Single port block memory                   |    |  |  |  |  |  |

| b.                 | SDP block memory                              |    |  |  |  |  |  |

| III.2.3.           | Arabic Character Display                      |    |  |  |  |  |  |

| a.                 | Microcontroller design                        |    |  |  |  |  |  |

| b.                 | FPGA design                                   |    |  |  |  |  |  |

| III.3. Con         | clusion                                       |    |  |  |  |  |  |

| CHAPTE             | R IV: Implementation and Experimental Results |    |  |  |  |  |  |

| IV.1. Intro        | oduction                                      |    |  |  |  |  |  |

| IV.2. Exp          | IV.2. Experimental results                    |    |  |  |  |  |  |

| IV.2.1.            | IV.2.1. LCD interfacing                       |    |  |  |  |  |  |

| IV.2.2.            | IV.2.2. Block memory LCD interfacing          |    |  |  |  |  |  |

| IV.2.3.            | IV.2.3. FPGA Arabic characters on LCD         |    |  |  |  |  |  |

| IV.3. Con          | clusion                                       |    |  |  |  |  |  |

| General Conclusion |                                               |    |  |  |  |  |  |

| Reference          | Referencesxi                                  |    |  |  |  |  |  |

# List of figures

| Figure I. 1: FPGA structure[1]                                                       | 3  |

|--------------------------------------------------------------------------------------|----|

| Figure I. 2: Virtex 5 FPGA LXT family members[8]                                     | 6  |

| Figure I. 3: Genesys board's architecture [3]                                        | 7  |

| Figure I. 4: Xilinx FPGA design flow [8]                                             | 8  |

| Figure I. 5: BMG signals pinout [8]                                                  | 12 |

| Figure II. 1: 2x16 LCD module [14]                                                   | 13 |

| Figure II. 2: Structure of an LCD module [11].                                       | 14 |

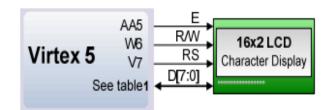

| Figure II. 3: Xilinx Virtex 5 FPGA interfaced with a character LCD [3]               | 15 |

| Figure II. 4: 2 lines by 16 characters display [5]                                   | 17 |

| Figure II. 5: The CG ROM patterns used by the ST7066U-0A controller [5]              | 17 |

| Figure II. 6: Block diagram of the Sitronix ST7066U LCD controller [5]               | 18 |

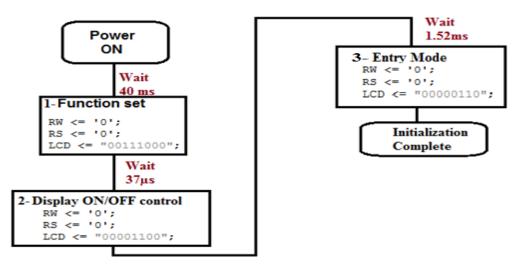

| Figure III. 1: Transition diagram of LCD module initialization                       | 24 |

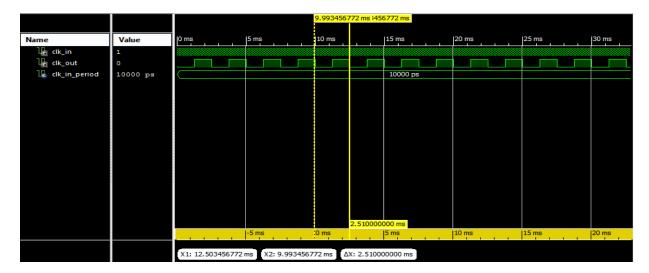

| Figure III. 2: Simulation of the clock divider used                                  | 24 |

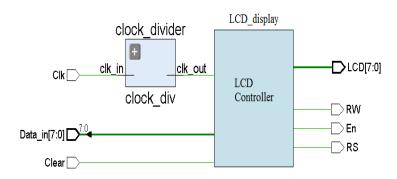

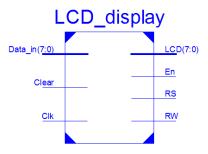

| Figure III. 3: Block diagram for LCD module                                          | 25 |

| Figure III. 4: Pinout of LCD display                                                 | 25 |

| Figure III. 5: Simulation of LCD module.                                             | 25 |

| Figure III. 6: Example of COE file to display "Master students".                     | 27 |

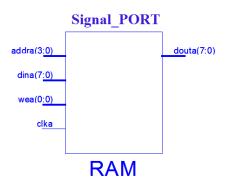

| Figure III. 7: Single port RAM pinout                                                | 27 |

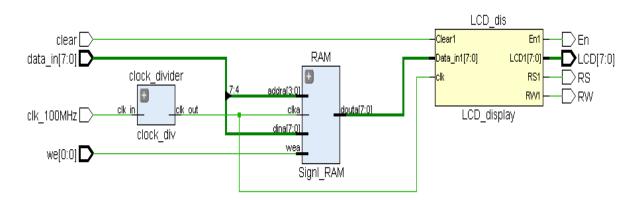

| Figure III. 8: Block diagram of a 16x8 single port RAM interfaced with LCD           | 28 |

| Figure III. 9: The simulation of single port RAM using COE file.                     | 28 |

| Figure III. 10: The COE file used for SDP RAM design.                                | 29 |

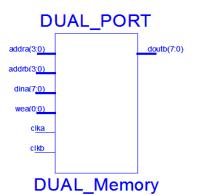

| Figure III. 11: Simple SDP RAM pinout                                                | 30 |

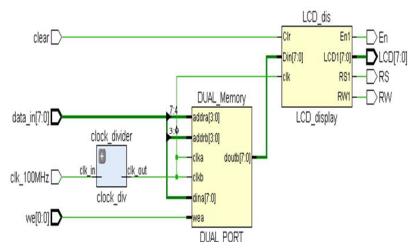

| Figure III. 12: Block diagram of a 16x8 SDP RAM interfaced with LCD                  | 30 |

| Figure III. 13: Simulation results for LCD display using COE file                    | 31 |

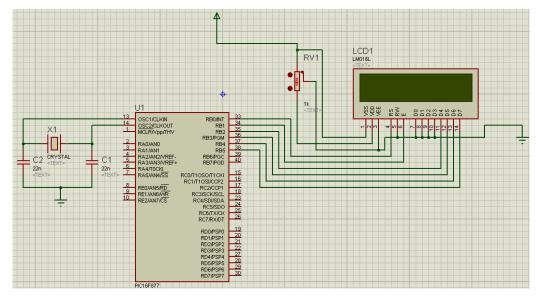

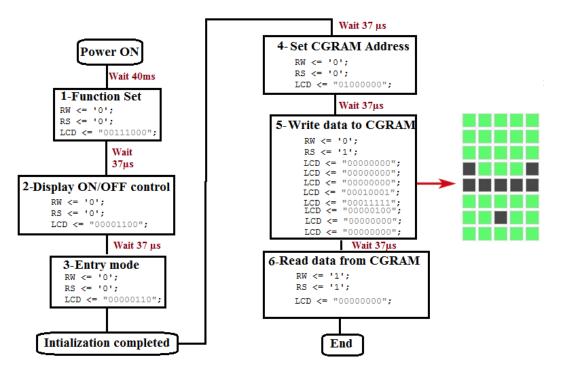

| Figure III. 14: Design of a PIC 16F877 interfacing with 2x16 LCD module              | 32 |

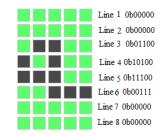

| Figure III. 15: Example of 5x8 dot matrix representation for an Arabic character (•) | 32 |

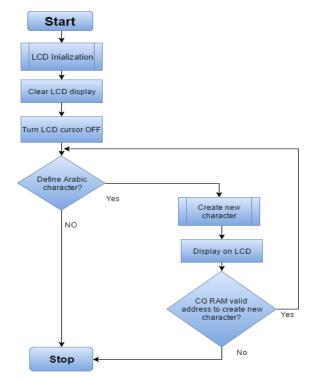

| Figure III. 16: Flowchart of LCD custom character display                            | 33 |

| Figure III. 17: Custom characters LCD displays.                                      | 33 |

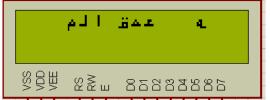

| Figure III. 18. Transition diagram of LCD module initialization for Arabic display   | 34 |

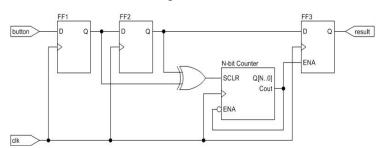

| Figure IV. 1: Counter Output after (a) one pushbutton's press and (b) three presses  | 37 |

| Figure IV. 2: Digital circuit for debouncing a push button                           | 38 |

| Figure IV. 3: Counter output after (a) one push button press and (b) two pressed     | 38 |

| Figure IV. 4: LCD module display using a simple VHDL.                                | 40 |

# List of tables

| Table I. 1: Basic factors for FPGA's comparison.                          | 4  |

|---------------------------------------------------------------------------|----|

| Table I. 2: Memory types included in BMG.                                 | 10 |

| Table II. 1: Corresponding LCD pins on Genesys board [3].                 | 15 |

| Table II. 2: IR and DR Registers operation.                               | 16 |

| Table II. 3: Example of custom character at the first location in CG RAM. | 19 |

| Table II. 4: Instructions and codes of some LCD commands.                 | 21 |

| Table III. 1: The Content of the CG RAM for an Arabic character display.  | 35 |

| Table IV. 1: Pins configuration of the LCD display.                       | 36 |

| Table IV. 2: Pins configuration for the 16 bit up counter.                | 37 |

| Table IV. 3: ASCII code of the characters to be used.                     | 39 |

| Table IV. 4: BRAMs LCD interfacing implementation.                        | 40 |

## Acronyms

| μC     | Microcontroller                                    |

|--------|----------------------------------------------------|

| A/D    | Analog to Digital converter                        |

| AC     | Address Counter                                    |

| ASCII  | American Standard Code for Information Interchange |

| ASIC   | Application Specific Integrated Circuit            |

| В      | Blink                                              |

| BF     | Busy Flag                                          |

| BMG    | Block Memory Generator                             |

| BRAM   | Block Random Access Memory                         |

| С      | Cursor                                             |

| CAD    | Computer Aided Design                              |

| CG RAM | Character Generator Random Access Memory           |

| CG ROM | Character Generator Read Only Memory               |

| CLB    | Configurable Logic Block                           |

| CMT    | Clock Management Tile                              |

| COE    | Coefficient                                        |

| CPLD   | Complex Programmable Logic Device                  |

| D      | Display                                            |

| DB     | Data Bus                                           |

| DCM    | Digital Clock Manager                              |

| DD RAM | Display Data Random Access Memory                  |

| DL     | Data Length                                        |

| DLL    | Delay Locked Loop                                  |

| DP RAM | Dual Port Random Access Memory                     |

| DR     | Data Register                                      |

| DSP    | Digital Signal Processing                          |

| Ε      | Enable                                             |

| EDA    | Electronic Design Automation                       |

| EDK    | Embedded Development Kit                           |

| FF     | Flip Flop                                          |

| FIFO   | First Input First Output                           |

| FPGA   | Field Programmable Gate Array                      |

| FSM    | Finite State Machine                               |

|        |                                                    |

| GPIO    | General Purpose Input Output               |  |  |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|--|--|

| HDL     | Hardware Description Language              |  |  |  |  |  |  |

| I/O     | Input/Output                               |  |  |  |  |  |  |

| IC      | Integrated Circuit                         |  |  |  |  |  |  |

| IOB     | Input Output Block                         |  |  |  |  |  |  |

| IOE     | Input Output Element                       |  |  |  |  |  |  |

| IP      | Intellectual Property                      |  |  |  |  |  |  |

| IR      | Instruction Register                       |  |  |  |  |  |  |

| ISE     | Integrated Synthesis Environment           |  |  |  |  |  |  |

| ISim    | Integrated Synthesis Environment Simulator |  |  |  |  |  |  |

| LAB     | Integrated Synthesis Environment           |  |  |  |  |  |  |

| LC      | Liquid Crystal                             |  |  |  |  |  |  |

| LCD     | Liquid Cristal Display                     |  |  |  |  |  |  |

| LED     | Light-Emitting Diode                       |  |  |  |  |  |  |

| LUT     | Look-Up Tables                             |  |  |  |  |  |  |

| MIF     | Memory Initialization File                 |  |  |  |  |  |  |

| MSB     | Most Significant Bit                       |  |  |  |  |  |  |

| PC      | Personal Computer                          |  |  |  |  |  |  |

| PIC     | Programmable Interface Controller          |  |  |  |  |  |  |

| PLL     | Phase Locked Loop                          |  |  |  |  |  |  |

| RAM     | Random Access Memory                       |  |  |  |  |  |  |

| ROM     | Read Only Memory                           |  |  |  |  |  |  |

| RS      | Register Select                            |  |  |  |  |  |  |

| RTL     | Register Transfer Level                    |  |  |  |  |  |  |

| RW      | Read/Write                                 |  |  |  |  |  |  |

| SDP RAM | Simple Dual Port Random Access Memory      |  |  |  |  |  |  |

| SIMPRIM | Simulation Primitive                       |  |  |  |  |  |  |

| SoC     | System on Chip                             |  |  |  |  |  |  |

| UCF     | User Constraints File                      |  |  |  |  |  |  |

| VHDL    | VHSIC Hardware Description Language        |  |  |  |  |  |  |

| VHSIC   | Very High-Speed Integrated Circuit         |  |  |  |  |  |  |

| XST     | Xilinx Synthesis Technology                |  |  |  |  |  |  |

|         |                                            |  |  |  |  |  |  |

# **General Introduction**

### **General Introduction**

In the world of digital design, a major revolution has taken place over the past period. Field programmable gate arrays (FPGAs) can contain over a million equivalent logic gates and tens of thousands of flip flops (FFs). This means that it is not possible to use traditional methods of logic design involving the drawing of logic diagrams when the digital circuit may contain thousands of gates, traditional integrated circuits design has been replaced by the design flow based on hardware description languages (HDL) such as VHDL, Verilog, and tools for logic synthesis. FPGAs can be reprogrammed to desired applications or functionality requirements after manufacturing. It is integrated inside a specific board to achieve the required system's objectives. In fact, Input/output (I/O) devices are very useful in such system such as Liquid Crystal Device (LCD). The character LCD display is the most common device which is attached to Genesys Virtex 5 FPGA board, that LCD can display only English/Japan characters ASCII codes. Due to the systems development Arabic displaying is needed, however, ASCII codes do not include any Arabic characters.

HDL is used to describe complex logic function, these are included in design suites such as Xilinx's Integrated Synthesis Environment (ISE) and similar tools. HDL based design flow offers portability, reduction of the design cycle, independence of technology, and automatic synthesis and logic optimization. However, if design engineers had to code commonly used complex digital circuits in large projects, they would end up wasting more time and money. Because of this, a new generation of methodology, intellectual property (IP) core is provided. An IP core is a block of logic or data to perform a specific function that is used in making an FPGA or an application specific integrated circuit (ASIC). IP cores can be used in a complex design where a designer wants to save time. The CORE Generator System is suggested as an ISE design tool that delivers parameterized cores optimized for Xilinx FPGAs. These include Digital Signal Processing (DSP) function, memories, storage elements, math functions and other basic elements. However, the core library of ISE tool does not contain a core for character LCD controller.

In our project, mainly we have introduced some designs based on Genesys' 2x16 character LCD display by using a single port and simple dual port RAM including in the block memory generator (BMG) which is an existed IP and make comparison with them, in

order to allow a later IP design for that LCD. In addition, we displayed Arabic characters on LCD display using microcontroller and FPGA.

The main objectives of our project are to display Arabic characters on LCD display in the Genesys board and suggest a design of IP core for FPGA-based LCD controller to integrate it with ISE design suite tool.

Our report is divided into four chapters. Chapter one describes the FPGA's technology. Chapter two presents a 2x16 character LCD display. Chapter three explains the design of LCD controller integrating Arabic characters. Chapter four presents implementation and experimental results. Finally in the general conclusion, a summary of the work is presented, with suggestions for future work.

# **CHAPTER I Introduction to FPGA**

### **CHAPTER I: Introduction to FPGA**

#### **I.1. Introduction**

In today's digital world, FPGA has become one of the major technologies used to create sophisticated digital systems based on schematic designs or HDL languages; mainly VHDL or Verilog languages. Actually, custom hardware functionality can be implemented using FPGA without need to use a breadboard or soldering iron. Xilinx Virtex 5 FPGA has been used in our project. In this chapter, some FPGA features will be introduced.

#### I.2. Field Programmable Gate Array

In the following sections, FPGA is going to be described with details.

#### I.2.1. Overview of general FPGA device

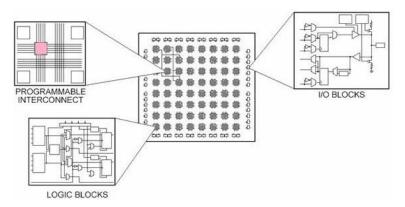

FPGA is a two dimensional logic array that can be programed and reconfigured by the user in the field after manufacturing, hence field programmable. It allows the implementation of complex digital circuits. This device has been around since 1980s. This semiconductor chip is made up of different logic blocks named Configurable Logic Blocks (CLBs) by Xilinx or Logic Array Blocks (LABs) by Altera. Each one of these logic blocks; seen in gray in **Figure I.1**; is surrounded by reconfigurable interconnections (the spacing between gray blocks) to allow the routing of all these blocks together. These blocks are surrounded by a configurable General Purpose Input/Output pins (GPIO). These pins are named as Input/Output Blocks (IOBs) by Xilinx whereas Altera suggests Input/Output Elements (IOEs) as a name.

Figure I. 1: FPGA structure[1].

#### **I.2.2. FPGA's applications**

FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing. This feature distinguishes FPGAs from ASICs, which are custom manufactured for specific design tasks. They can cover an extremely wide range of applications including DSP, speech recognition, defense system, face detection, ASIC prototyping, medical imaging, industrial applications...etc.

#### I.2.3. Important Factors for comparing FPGAs

FPGAs are similar to Complex Programmable Logic Devices (CPLDs). The only difference is that CPLDs are much smaller in size and compatibility than FPGAs. They are manufactured by many different companies like Xilinx, Altera, Actel, Lattice, QuickLogic and Atmel. These companies use some specific factors to distinguish between FPGAs. These factors are described in **Table I.1**.

| Factor              | Description                                                           |  |  |  |

|---------------------|-----------------------------------------------------------------------|--|--|--|

| Fabrication process | It is clear that more advanced fabrication process brings higher      |  |  |  |

|                     | integration, and thus higher density and/or reduced size of chips.    |  |  |  |

| Logic density       | The unit used to express the logic capability of an FPGA.             |  |  |  |

| Clock management    | Clock management comprises two basic functions: removing clock        |  |  |  |

|                     | skew and propagation delay and generating new clock signals with      |  |  |  |

|                     | different frequencies. Generally, this can be done using either Delay |  |  |  |

|                     | Locked Loops (DLLs), or Phase Locked Loops (PLLs).                    |  |  |  |

| On-chip memory      | As FPGA applications grow in complexity so does their need for        |  |  |  |

|                     | memory. Using Look-Up Tables (LUTs) as registers for storing data     |  |  |  |

|                     | couldn't possibly provide enough space for serious applications.      |  |  |  |

|                     | Especially if these applications require numerous arithmetical        |  |  |  |

|                     | computations to be performed, and are time dependent. As this is      |  |  |  |

|                     | often the case, the outside memory could not produce desired          |  |  |  |

|                     | efficiency. This is why, with every new generation of FPGAs, more     |  |  |  |

|                     | and more memory gets embedded into FPGA. [8]                          |  |  |  |

| DSP capabilities    | The majority of FPGA applications require some sort of DSP in order   |  |  |  |

|                     | to reduce the time and increase efficiency of computations.           |  |  |  |

Table I. 1: Basic factors for FPGA's comparison.

| I/O compatibility     | As FPGAs continue to grow in size and capacity, the larger and more |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------|--|--|--|--|--|

|                       | complex systems designed for them demand an increased variety of    |  |  |  |  |  |

|                       | Input/Output standards. Furthermore, as system-clock speeds         |  |  |  |  |  |

|                       | continue to increase, the need for high-performance I/O becomes     |  |  |  |  |  |

|                       | more important.                                                     |  |  |  |  |  |

| Software support and  | Developing an FPGA-based hardware system is a complex process.      |  |  |  |  |  |

| other design services | Designers divide this process into different stages (Design flow),  |  |  |  |  |  |

|                       | providing a complete software solution for each of them.            |  |  |  |  |  |

In fact, Xilinx and Altera are the current market leaders and long-time industry rivals. Both of these two companies provide a proprietary Windows and Linux design software mainly ISE design suite or Vivado as Xilinx tools and Quartus for Altera to allow the user to design, analyze, simulate and compile his design in an easy way.

Since FPGA Virtex 5 is the one used in our project, it will be discussed in the following section.

#### I.2.4. FPGA Xilinx Virtex 5 LXT family

This FPGA family offers an advanced platform that meets the growing need for programmable systems with higher performance, higher density, lower power consumption, and lower overall system cost. It is available in -3, -2, -1 speed grades, with -3 having the highest performance.

**Figure I.2** shows a summary of the available resources for different Virtex 5 LXT FPGAs family. It incorporates LUTs with six independent inputs, with a new diagonal interconnect structure. In addition, a PLL have been added to each clock management tile (CMT), which now contains two digital clock managers (DCMs) and one PLL. The CMT thus offers the best of both worlds: the robust versatility and precise incremental phase shift capability of a digital clock manager combined with the jitter reduction from the analog PLL. The largest device in the family has six CMTs capable of generating and manipulating 550-MHz clocks, supporting the performance of Virtex-5 logic and block functions. Moreover, synchronous dual-ported block Random Access Memory (RAM) is an important block memory. The size of each block RAM has been increased to 36 Kb, but you can also use it as two independent 18-Kb block RAMs. Furthermore, the DSP48Eslice contains a 25x18 multiplier, an adder, and an accumulator, thus it is dedicated to arithmetic operations[8].

|            | Configurable Logic Blocks (CLBs) |                    |                                |                  | Block RAM Blocks |       |             |      | PowerPC             | Endpoint                     |                  | Max RocketIO |     | Total        | Max         |

|------------|----------------------------------|--------------------|--------------------------------|------------------|------------------|-------|-------------|------|---------------------|------------------------------|------------------|--------------|-----|--------------|-------------|

| Device     | Array<br>(Row x Col)             | Virtex-5<br>Slices | Max<br>Distributed<br>RAM (Kb) | DSP48E<br>Slices | 18 Kb            | 36 Kb | Max<br>(Kb) | CMTs | Processor<br>Blocks | Blocks for<br>PCI<br>Express | Ethernet<br>MACs | GTP          | GTX | I/O<br>Banks | User<br>I/O |

| XC5VLX20T  | 60 x 26                          | 3,120              | 210                            | 24               | 52               | 26    | 936         | 1    | N/A                 | 1                            | 2                | 4            | N/A | 7            | 172         |

| XC5VLX30T  | 80 x 30                          | 4,800              | 320                            | 32               | 72               | 36    | 1,296       | 2    | N/A                 | 1                            | 4                | 8            | N/A | 12           | 360         |

| XC5VLX50T  | 120 x 30                         | 7,200              | 480                            | 48               | 120              | 60    | 2,160       | 6    | N/A                 | 1                            | 4                | 12           | N/A | 15           | 480         |

| XC5VLX85T  | 120 x 54                         | 12,960             | 840                            | 48               | 216              | 108   | 3,888       | 6    | N/A                 | 1                            | 4                | 12           | N/A | 15           | 480         |

| XC5VLX110T | 160 x 54                         | 17,280             | 1,120                          | 64               | 296              | 148   | 5,328       | 6    | N/A                 | 1                            | 4                | 16           | N/A | 20           | 680         |

| XC5VLX155T | 160 x 76                         | 24,320             | 1,640                          | 128              | 424              | 212   | 7,632       | 6    | N/A                 | 1                            | 4                | 16           | N/A | 20           | 680         |

| XC5VLX220T | 160 x 108                        | 34,560             | 2,280                          | 128              | 424              | 212   | 7,632       | 6    | N/A                 | 1                            | 4                | 16           | N/A | 20           | 680         |

| XC5VLX330T | 240 x 108                        | 51,840             | 3,420                          | 192              | 648              | 324   | 11,664      | 6    | N/A                 | 1                            | 4                | 24           | N/A | 27           | 960         |

Figure I. 2: Virtex 5 FPGA LXT family members[8].

After dealing with all these information about FPGA technology, it is recommended to describe briefly the hardware development platform and all the needed tools used to for digital system design.

#### I.3. Hardware development platform and tools

In our project Xilinx Virtex 5 FPGA integrated with the Genesys board have been used. This FPGA development board will be presented in the following sections.

#### I.3.1. Hardware development platform

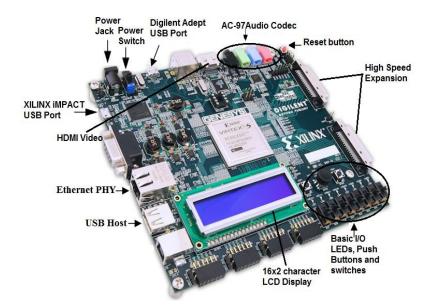

The Digilent's Genesys board seen in **Figure I.3** brings the power of the Xilinx VIRTEX 5 FPGA to a surprisingly uncomplicated design platform. With gigabit ethernet, high speed memory, high resolution audio and video circuits, and a host of USB connectivity options, the Genesys board includes proven circuits used in the most demanding designs. From complex systems to dedicated high performance applications, the Genesys board brings workable solutions to complex problems. Genesys is fully compatible with all Xilinx Computer Aided Design (CAD) tools, including ChipScope, Embedded Development Kit (EDK), and the free WebPack, so designs can be completed with no extra costs. The Virtex5 LX50T is optimized for high performance logic. It includes Digilent's newest Adept USB2 system that offers device programming, real time power supply monitoring, automated board tests, virtual I/O, and simplified user data transfer facilities. A second USB programming port (iMPACT USB2), based on the Xilinx programming cable, is also built into the board [3].

Figure I. 3: Genesys board's architecture [3].

Genesys Virtex 5 includes different inputs and outputs that can be used to perform specific tasks. The major ones are pushbuttons, eight switches, and eight LEDs for basic digital input and output. It also contains a standard 2x16 character LCD which is of our interest to deal with it later on.

The upcoming sections will discuss the tool used to program the FPGA device.

#### I.3.2. Hardware development tools

Xilinx offers different tools to interact with the Xilinx FPGA devices. These tools are described below.

#### a. ISE design suite

Some tools are needed to design digital systems so that they perform the required tasks. In our case, it is necessary to use Xilinx ISE design suite as a tool to program the Virtex 5 integrated in the Genesys board, so that it converts the HDL or Schematic design into bits stream (machine language). The HDL used in this project is VHDL. Before creating any VHDL module it is really important to understand the design flow described in the next section.

#### **b.** Design flow

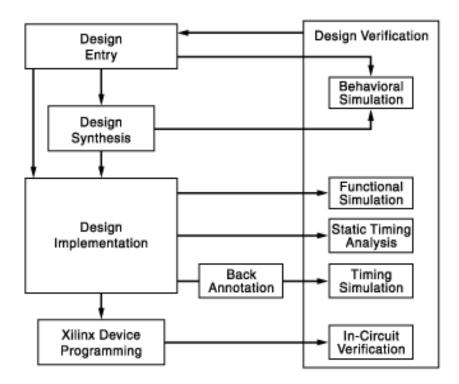

Designing a digital system in Xilinx ISE tools goes through different steps before the designer himself can test the functionality of that system and download it in the FPGA (Virtex 5 in our case). The ISE design flow seen in **Figure I.4** comprises the following steps: design entry, design synthesis, design implementation, and Xilinx device programming. Design verification, which includes both functional verification and timing verification, takes places at different points during the design flow[8]. The main steps are described below:

- **Design Entry:** is required to create design files using hardware description language (In our case VHDL) or schematic editor.

- **Functional verification:** is used to test functionality of the design at different points in the design flow as follows:

- ✓ Before synthesis, run behavioral simulation (also known as Register Transfer Level (RTL) simulation).

- ✓ After Translate, run functional simulation (also known as gate-level simulation), using the SIMPRIM library.

- ✓ After device programming, run in-circuit verification[8].

- **Design Synthesis :** During synthesis, the synthesis engine compiles the design to transform HDL sources into an architecture specific design netlist. The ISE software supports the use of Xilinx Synthesis Technology (XST), which is delivered within it[8].

- **Design Implementation :** Partition, place, and route to create bit stream file, called bit file.

- **Timing verification:** is performed during after Map and place & route implementation.

- Xilinx Device Programming: After generating a programming file, it is possible to configure the used device by generating configuration files and downloading the programming files from a host computer to a Xilinx device using iMPACT Xilinx tool.

Figure I. 4: Xilinx FPGA design flow [8].

The following section explains the IP core in details. In fact, existing IP cores have been used in our designs.

#### I.4. IP core

IP core is a ready-made function that can be inserted in any digital design as a block diagram with user's specifications. In other words, it is a block of logic or data that is used in making a FPGA or ASIC for a product. As essential elements of design reuse.

#### I.4.1. Advantages and Disadvantages of IP cores

Like any new technologies and tools, IP cores have their advantages and disadvantages. Although they may simplify a given design, the engineer has to design the interfaces to send and receive data from this black box. Moreover, many cores are designed for particular parts but some come free but other cores may cost you thousands of dollars.

#### I.4.3. IP cores type

IP cores split up into three different categories: soft cores, firm cores and hard ones. The difference between the three cores is that the soft core is the one which exists either as a netlist (a list of the logic gates and associated interconnections making up an integrated circuit (IC)) or HDL code, whereas the hard core is a physical manifestations of the IP design. Hard core is the best for plug and play applications, and is less portable and flexible than the other two types of cores. Like the hard core, firm or simply semi-hard core also carry placement data but is configurable to various applications. As a way to create some IP cores it is suggested to use the CORE Generator System as an ISE design tool that delivers parameterized cores optimized for Xilinx FPGAs.

#### **I.4.4.** Core Generator software tool

Some existing IP cores can be generated using a special Xilinx tools described in details in the next coming sections.

#### a. Overview

The CORE Generator software is based on the use of the IP catalog. This IP catalog includes cores that are already defined to perform some specific operations in order to replace many coding lines. One of these IP cores is the Memory and storage elements used to create different block memories.

A memory is a storage element used to hold data and programs in a binary format. It can be found in every electronic device including FPGAs with two main different types:

9

RAM and ROM. RAM is a volatile memory that can be access randomly at any time in any order. Its contents are lost when the power is turned off whereas ROM is a non-volatile memory used to read from it only.

#### **b. Block Memory Generator (BMG)**

Memories and storage Elements IP core; included in the Core Generator; contains three different cores FIFOs, Memory Interface Generators, RAMs and ROMs which contains two memory Generators, Block and Distributed. What is interesting for us is the BMG. The Xilinx LogiCORE IP BMG core, found in the Core Generator is an advanced memory constructor that generates area and performance-optimized memories using embedded block RAM resources in Xilinx FPGAs [1]. Users can quickly create optimized memories to leverage the performance and features of block RAMs and ROMs in Xilinx FPGAs. Actually, BMG provides different types of IP core memories that are described briefly below. Mainly Single port RAM, SDP RAM, True Dual port RAM, Single port ROM, and Dual port ROM. s These memories can be explained in the **Table I.2 seen** below.

| Memory type     | Block diagram                                         | Description                                                                                                                             |  |  |  |  |

|-----------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Single port ROM | ADDRA<br>ENA<br>RSTA<br>REGCEA<br>CLKA                | In single port ROM, only one address<br>port is available for read operation.                                                           |  |  |  |  |

| Single port RAM | DINA<br>ADDRA<br>WEA<br>ENA<br>RSTA<br>REGCEA<br>CLKA | On a single port RAM, the read and<br>write operations share the same address<br>at port A, and the data is read from<br>output port A. |  |  |  |  |

| Simple Dual-Port RAM                             | In SDP RAM mode, a dedicated address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DINA<br>ADDRA<br>WEA<br>ENA<br>BITERR<br>DBITERR | port is available for each read and write<br>operation (one read port and one write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                  | port). A write operation uses write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADDRB DOUTB                                      | address from port A while read operation uses read address and output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                  | from port B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DINA DOUTA DOUTA                                 | In true dual port RAM mode, two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADDRA<br>WEA<br>ENA<br>RSTA                      | address ports are available for read or write operation (two read/write ports).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                  | In this mode, we can write to or read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                  | from the address of port A or port B, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WEB<br>ENB<br>RSTB<br>REGCEB<br>CLKB             | the data read is shown at the output port<br>with respect to the read address port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dual-Port ROM                                    | The dual port ROM has almost similar functional ports as single port ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ENA<br>RSTA<br>REGCEA                            | The difference is dual port ROM has an additional address port for read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                  | operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ENB<br>RSTB<br>REGCEB<br>CLKB                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                  | DINA<br>ADDRA<br>WEA<br>ENA<br>CLKA<br>ADORB<br>ENB<br>RSTB<br>RSTB<br>REGCEB<br>CLKB<br>DUITB<br>ADDRA<br>MUEA<br>ENA<br>RSTB<br>REGCEA<br>CLKA<br>DINB<br>ADDRB<br>WEB<br>ENB<br>RSTB<br>RSTC<br>RSTC<br>RSTC<br>REGCEA<br>CLKA<br>DUITB<br>DUITB<br>ADDRA<br>MUEA<br>ENA<br>RSTB<br>REGCEA<br>CLKB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>CLKB<br>DUITB<br>CLKB<br>DUITB<br>CLKB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>CLKB<br>DUITB<br>DUITB<br>DUITB<br>CLKB<br>DUITB<br>CLKB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>CLKB<br>DUITB<br>CLKB<br>DUITB<br>CLKB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB<br>DUITB |

**Figure I.5** describes the BMG signals. The widths of the data ports (dina, douta, dinb, and doutb) can be selected in logiCORE tool. The address port (addra and addrb) widths are determined by the memory depth with respect to each port. The Write enable ports (wea and web) are buses of width 1 when byte-writes are disabled. When byte-writes are enabled, wea and web widths depend on the byte size and Write data widths selected.

| Name   | Direction | Description                                                                                                                                                                                 |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clka   | Input     | <b>Port A Clock</b> : Port A operations are synchronous to this clock. For synchronous operation, this must be driven by the same signal as CLKB.                                           |

| addra  | Input     | <b>Port A Address</b> : Addresses the memory space for port A Read and Write operations. Available in all configurations.                                                                   |

| dina   | Input     | <b>Port A Data Input</b> : Data input to be written into the memory through port A. Available in all RAM configurations.                                                                    |

| douta  | Output    | Port A Data Output: Data output from Read operations through port<br>A. Available in all configurations except Simple Dual-port RAM.                                                        |

| ena    | Input     | <b>Port A Clock Enable</b> : Enables Read, Write, and reset operations through port A. Optional in all configurations.                                                                      |

| wea    | Input     | Port A Write Enable: Enables Write operations through port A.<br>Available in all RAM configurations.                                                                                       |

| rsta   | Input     | <b>Port A Set/Reset</b> : Resets the Port A memory output latch or output register. Optional in all configurations.                                                                         |

| regcea | Input     | <b>Port A Register Enable</b> : Enables the last output register of port A. Optional in all configurations with port A output registers.                                                    |

| clkb   | Input     | <b>Port B Clock</b> : Port B operations are synchronous to this clock.<br>Available in dual-port configurations. For synchronous operation, this must be driven by the same signal as CLKA. |

| addrb  | Input     | <b>Port B address</b> : Addresses the memory space for port B Read and Write operations. Available in dual-port configurations.                                                             |

| dinb   | Input     | Port B Data Input: Data input to be written into the memory through port B. Available in True Dual-port RAM configurations.                                                                 |

| doutb  | Output    | <b>Port B Data Output</b> : Data output from Read operations through Port B. Available in dual-port configurations.                                                                         |

| enb    | Input     | Port B Clock Enable: Enables Read, Write, and reset operations through Port B. Optional in dual-port configurations.                                                                        |

| web    | Input     | Port B Write Enable: Enables Write operations through Port B.<br>Available in Dual-port RAM configurations.                                                                                 |

Figure I. 5: BMG signals pinout [8].

#### **I.6.** Conclusion

In this chapter we presented some backgrounds and features of FPGAs. We examine Genesys board and gave some needed information about needed tools to be used later on. Also, we presented the general architecture of the FPGA we've used. Moreover, we tried to give brief ideas about the IP cores and the core generator. This tool will be used in the next coming chapters in order to create some needed IP cores in digital design world.

# CHAPTER II Character LCD Display Background

## **CHAPTER II: Character LCD Display Background**

#### **II.1. Introduction**

Most digital systems combine hardware design and software design to achieve the required system's objectives. Actually, each system contains different input and output ports to allow the designer to control and communicate with the outside world. One of these I/O devices is the character LCD display. This chapter introduces the needed information for this module which is attached to Genesys Virtex 5 FPGA board; that is the LCD display.

#### **II.2.** Character LCD display

Genesys board has a 2x16 character LCD display connected to it to allow the designer to display some data and integrate that module in the design of the digital system as required. **Figure II.1** shows a 2x16 character LCD display with its corresponding pins. These pins will be explained later on.

**Figure II. 1:** 2x16 LCD module [14].

For the coming papers, we will describe LCD's features.

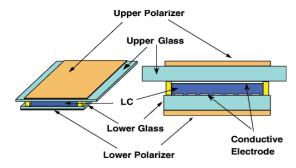

#### II.2.1. Overview of an LCD

An LCD is a very basic electronic module; commonly used in various devices and circuits. This module is preferred over seven segments display and Light-Emitting Diodes (LEDs). The reasons being: LCDs are economical; easily programmable; have no limitation of displaying special and even custom character (unlike seven segments), animations and so on [4]. This I/O device consists of a panel of liquid crystal molecules (LC) illustrated in **Figure II.2** that can be induced by electrical fields to take certain patterns which block light or allow it through, hence Liquid Cristal Display. Liquid crystals do not emit light directly.

Figure II. 2: Structure of an LCD module [11].

LCDs are used all over the world in calculators, digital clocks, CD players...etc. In addition, character LCDs are ideal for displaying text thus alphanumeric LCDs. They can also be configured to display small icons with no more than 5x7 pixels in size.

There exist different types of LCDs display mainly the character LCDs display and the graphical one. Obviously, it is enough to describe the character LCDs display since they are the needed one in this project. Sometimes it is called alphanumeric LCDs. They are inexpensive and easy to use. They range in different sizes including 1x8, 2x8, 1x16, 2x16 characters, 4x16 characters plus many more. What is interesting for us now is the 2x16 character LCD displays, that is, two lines of sixteen characters each.

In fact, it is necessary to understand how a character LCD is configured. The next section deals with pins configuration.

#### **II.2.2.** LCD pins configuration

Genesys board contains a standard 2x16 character LCD, that is, two lines of sixteen characters each connected as seen in **Figure II.3**. Each character is represented in 5x8 pixel dotted matrix (5x7 pixels for character one extra for the cursor). This LCD has sixteen different pins that are connected directly to specific pins on the Xilinx Virtex 5 FPGA. Two of these pins are not used due to the fact that they are used for optional backlight. The rest of pins includes eight data signals D7...D0, three control signals (read and write signal (R/W), Enable signal (E) and Register Select signal (RS)), and three voltage supply signals. E line is used to allow the LCD to send or receive data. RS line is used for data and instructions, when it is low the data is to be treated as a command or special instruction (such as clear screen, position cursor...etc.), but when it is high, the data being sent is text data which should be displayed on the screen. R/W line is used to control operation, when it is low, the information on the data bus is being written to the LCD, and when it is high the program is effectively reading the LCD.

Figure II. 3: Xilinx Virtex 5 FPGA interfaced with a character LCD [3].

The Xilinx Virtex 5 FPGA pins assignment is illustrated in Table II.1.

| Table II. 1: Corresponding LCD | pins on Genesys board [3]. |

|--------------------------------|----------------------------|

|--------------------------------|----------------------------|

| LCD pins | Signal | FPGA pins | Description                                          |

|----------|--------|-----------|------------------------------------------------------|

| 1        | Vss    |           | Ground                                               |

| 2        | Vdd    |           | 5V Power Supply                                      |

| 3        | Vo     |           | Contrast Voltage (typically 100mV-200mV at 20C)      |

| 4        | RS     | V7        | Register select: high for data, low for instructions |

| 5        | R/W    | W6        | Read/write signal: high for read, low for write      |

| 6        | E      | AA5       | Read/write: high for OE; falling edge writes data    |

| 7        | D0     | Y8        | Bidirectional data bus 0                             |

| 8        | D1     | AB7       | Bidirectional data bus 1                             |

| 9        | D2     | AB5       | Bidirectional data bus 2                             |

| 10       | D3     | AC4       | Bidirectional data bus 3                             |

| 11       | D4     | AB6       | Bidirectional data bus 4                             |

| 12       | D5     | AC5       | Bidirectional data bus 5                             |

| 13       | D6     | AC7       | Bidirectional data bus 6                             |

| 14       | D7     | AD7       | Bidirectional data bus 7                             |

#### II.2.3. LCD controller

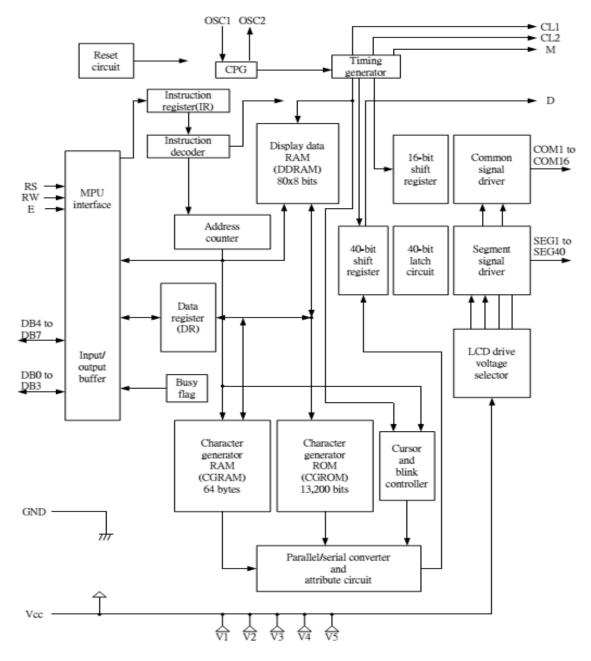

The 2x16 character LCD of Genesys board uses a Sitronix ST7066U as a controller module. It is used to communicate with the FPGA and control the LCD display to perform the required task. Its block diagram seen in **Figure II.6** has two 8 bit registers Instruction Register (IR) and Data Register (DR) to store information sent from FPGA. The operation and selection of the two registers are defined by **Table II.2**. The IR register stores instruction codes, such as display clear, cursor shift, and address information for display data RAM (DD RAM) and character generator RAM (CG RAM). The IR can only be written from FPGA. The DR register temporarily stores data to be written into DD RAM or CG RAM and temporarily stores data

#### **Character LCD Display Background**

read from DD RAM or CG RAM. These memories are going to be explained in the next coming sections. The Busy Flag (BF) seen in that table gives an indication whether the LCD hass finished the previous instruction and ready with the next.

Table II. 2: IR and DR Registers operation.

| RS | R/W | Operation                                                                        |

|----|-----|----------------------------------------------------------------------------------|

| 0  | 0   | Instruction Write operation (IR writes an internal operation like clear display. |

| 0  | 1   | Read Busy Flag (DB7) and address counter (DB0 DB6).                              |

| 1  | 0   | Data Write operation to DD RAM or CG RAM (DR to CG RAM or DD RAM).               |

| 1  | 1   | Data Read operation from DD RAM or CG RAM to DR.                                 |

It also includes an address counter (AC) which receives an initial address through IR based on a command/instruction code, assigns and updates addresses to both DDRAM and CGRAM. The DDRAM is used to store the display data represented in 8 bit character codes and sent from FPGA. Each address of DDRAM corresponds to a position on the LCD [5].

As it has been mentioned earlier, the LCD Controller has three internal memory regions, which are described in this section. A character generator ROM (CG ROM) with 208 preset 5x8 character patterns, these preset patterns are identified by their American Standard Code for Information Interchange (ASCII) codes (up through 7F are standard ASCII which includes all normal alphanumeric characters ). In fact, the Sitronix ST7066U uses English / Japan ASCII table (ST7066U-0A). The leftmost column on **Figure II.5** represents CG RAM. CG RAM custom character pattern is programmed line by line.

Also has two RAMs, naming DD RAM and CG RAM. CG RAM allows user to define their eight custom 5x8 characters. The DD RAM can hold up to 80 character codes at a time. Each byte of DD RAM represents each unique position on the LCD display. The LCD controller reads the information from the DD RAM and displays it on the LCD screen by mapping the locations 00H to 0FH to the first display row, and locations 40H to 4FH map to the second row seen in **Figure II.4**. Normally, DD RAM location 00H maps to the upper left display corner, and 40H to the lower left. Shifting the display left or right can change this mapping. The display uses a temporary data register (DR) to hold data during DD RAM /CG RAM reads or writes, and an internal address register to select the RAM location. Address register contents, set via the IR, are automatically incremented after each read or write operation. RAM read/write requests will be directed to DD RAM or CG RAM, depending on which address register was most recently accessed [3].

#### Character LCD Display Background

| Display<br>Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11         | 12 | 13 | 14 | 15 | 16 |

|---------------------|----|----|----|----|----|----|----|----|----|----|------------|----|----|----|----|----|

| DDRAM<br>Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | <b>0</b> A | 0B | 0C | 0D | 0E | 0F |

|                     | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A         | 4B | 4C | 4D | 4E | 4F |

Figure II. 4: 2 lines by 16 characters display [5].

| Upper          |                  |      |      |      |                         |      |           |               |      |      |                  |            |            |             |                 |             |

|----------------|------------------|------|------|------|-------------------------|------|-----------|---------------|------|------|------------------|------------|------------|-------------|-----------------|-------------|

| 4 bit<br>Lower | LLLL             | LLLH | LLHL | LLHH | LHLL                    | LHLH | LHHL      | LHHH          | HLLL | HLLH | HLHL             | HLHH       | HHLL       | HHLH        | HHHL            | нннн        |

| 4 bit          |                  |      |      |      |                         |      | <u> </u>  |               |      |      |                  | <u> </u>   |            |             |                 |             |

| LLLL           | CG<br>RAM<br>(1) |      |      |      | a                       | -    | -         |               |      |      |                  |            |            | ₩,          | ĊĊ              | ¦∷          |

| LLLH           | (2)              |      |      | 1    |                         |      | .==       | -:            |      |      |                  | Ţ          | ņ.         | ÷.,         | - <b>E</b> h    | -           |

| LLHL           | (3)              |      | 11   | 2    |                         |      | b         | ŀ             |      |      | 1                | T          | Ņ          | "::         | l≣⊧             | e           |

| LLHH           | (+)              |      | ₩    |      | <u> </u>                | 5    |           | ·=-           |      |      |                  | ņ          | Ť          | Ţ           | ≝-              | s:-:3       |

| LHLL           | (3)              |      | \$   | 4    | $\square$               | Ĩ    | $\square$ | t.            |      |      | •••              |            | ŀ          | <b>†</b> ?  | ·I              | 52          |

| LHLH           | (6)              |      |      |      | <u></u>                 |      | ÷         | II            |      |      |                  | 7          | ; <b>!</b> | ].          | œ               | <u></u> j   |

| LHHL           | (7)              |      | 8.   | 6    |                         | U    | ÷.        | ų,            |      |      | ÷                | Ţ          | ••••       |             | p               | 2           |

| LHHH           | (\$)             |      | 2    | ŕ    | 0                       |      | 9         | Ļ.,           |      |      |                  | ÷          |            | 7           | B               | 3.6         |

| HLLL           | (1)              |      | Ć    | 8    | $\left  \cdots \right $ | ×    | ŀ'n       | $\geq$        |      |      | ·•] <sup>•</sup> | - ]        |            | •           | . J <sup></sup> | ×.          |

| HLLH           | (2)              |      | )    | 9    | ]                       | Ŷ    | 1.        | '::: <b>!</b> |      |      | <u>ر:</u>        | Ţ          |            | <u>ا</u> [: | 1               | <u>ا</u> ا  |

| HLHL           | (3)              |      | :+:  | ::   |                         | 2    | .]        | 2             |      |      | ::::             |            | i ÌI       | Ŀ           | j               | =p:         |

| HLHH           | (4)              |      |      | :    | K                       | Ľ    | k:        | ÷             |      |      | ;=†              | Ţ          | t:::       |             | :-:             | <u>j</u> =q |

| HHLL           | (3)              |      | 3    |      | l                       | ÷    |           |               |      |      | ·]::             | <u>.</u> , |            | 7           | 4:-             | 1::i        |

| HHLH           | (6)              |      |      |      | ŀſ                      | .]   | Γ'n       | 2             |      |      | .::.             |            | ·`•        | <br>•       | ŧ               | <u>i</u>    |

| HHHL           | (7)              |      | ::   |      | ŀ··                     | -^   | ŀ"ı       | }             |      |      |                  | Ē          |            | ·. ·        | ŀ"ı             |             |

| нннн           | (\$)             |      |      |      | $\square$               |      | $\square$ | ÷             |      |      | • ::•            | <u>.</u>   | •••        |             | ÷               |             |

Figure II. 5: The CG ROM patterns used by the ST7066U-0A controller [5].

Figure II. 6: Block diagram of the Sitronix ST7066U LCD controller [5].

Moving beyond just displaying text, one awesome feature of this LCD display is the possibility to build our own characters in flexible way thus user's defined characters. However, the number of characters to be added are limited. This can be possible done by using the CG RAM. In fact, CG RAM provides space for eight custom characters only. Any character can be made to appear on a 5x8 pixel matrix element without knowledge of its ASCII value. Below in **Table II.3** it can be seen an example of an Arabic character ( $\hookrightarrow$ ) drawn inside a box of a 5x8 pixel grid. The 1's represent a green pixel and the 0's represent a white pixel. Since the data bus is 8 bits wide, the upper 3 bits are not used, and should always be set to zero (Don't care case x). This is used to encode the desired character to be defined in binary.

|                               |    |                      |    |    |      | Upper Nibble Lower Nibble |         |     |    |       |         |        |    |  |

|-------------------------------|----|----------------------|----|----|------|---------------------------|---------|-----|----|-------|---------|--------|----|--|

|                               |    | Write Data to CG RAM |    |    |      |                           |         |     |    |       |         |        |    |  |

| A5                            | A4 | A3                   | A2 | A1 | A0   | D7                        | D6      | D5  | D4 | D3    | D2      | D1     | D0 |  |

| Character Address Row Address |    |                      |    |    | ress | D                         | on't ca | are |    | Chara | acter B | litmap |    |  |

| 0                             | 0  | 1                    | 0  | 0  | 0    | X                         | X       | X   | 0  | 0     | 0       | 0      | 0  |  |

| 0                             | 0  | 1                    | 0  | 0  | 1    | Х                         | X       | X   | 0  | 0     | 0       | 0      | 0  |  |

| 0                             | 0  | 1                    | 0  | 1  | 0    | Х                         | X       | х   | 1  | 0     | 0       | 0      | 1  |  |

| 0                             | 0  | 1                    | 0  | 1  | 1    | Х                         | X       | X   | 1  | 0     | 0       | 0      | 1  |  |

| 0                             | 0  | 1                    | 1  | 0  | 0    | Х                         | X       | X   | 1  | 1     | 1       | 1      | 1  |  |

| 0                             | 0  | 1                    | 1  | 0  | 1    | X                         | X       | X   | 0  | 0     | 0       | 0      | 0  |  |

| 0                             | 0  | 1                    | 1  | 1  | 0    | х                         | X       | х   | 0  | 0     | 1       | 0      | 0  |  |

| 0                             | 0  | 1                    | 1  | 1  | 1    | X                         | X       | X   | 0  | 0     | 0       | 0      | 0  |  |

**Table II. 3**: Example of custom character at the first location in CG RAM.

Note: x stands for don't care case.